Bank

Number

VREFB

Group

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B1

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N0

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB1N1

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N0

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

VREFB2N1

PinName/

Function

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

nSTATUS

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

DCLK

IO

nCONFIG

TDI

TCK

TMS

TDO

nCE

CLK1

CLK2

CLK3

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

DIFFIO_L1p

DIFFIO_L1n

DIFFIO_L2p

DIFFIO_L2n

DIFFIO_L3p

DIFFIO_L3n

DIFFIO_L4p

DIFFIO_L4n

VREFB1N0

DIFFIO_L5p

DIFFIO_L5n

DIFFIO_L6p

DIFFIO_L6n

DIFFIO_L7p

DIFFIO_L7n

DIFFIO_L8p

DIFFIO_L8n

DIFFIO_L9p

DIFFIO_L9n

DIFFIO_L10p

DIFFIO_L10n

DIFFIO_L11p

DIFFIO_L11n

VREFB1N1

DIFFIO_L12p

DIFFIO_L12n

DIFFCLK_0n

DIFFCLK_1p

DIFFCLK_1n

DIFFIO_L13p

DIFFIO_L13n

DIFFIO_L14p

DIFFIO_L14n

DIFFIO_L15p

DIFFIO_L15n

DIFFIO_L16p

DIFFIO_L16n

VREFB2N0

DIFFIO_L17p

DIFFIO_L17n

DIFFIO_L18p

DIFFIO_L18n

DIFFIO_L19p

DIFFIO_L19n

DIFFIO_L20p

DIFFIO_L20n

DIFFIO_L21p

DIFFIO_L21n

DIFFIO_L22p

DIFFIO_L22n

DIFFIO_L23p

DIFFIO_L23n

DIFFIO_L24p

DIFFIO_L24n

DIFFIO_L25p

DIFFIO_L25n

VREFB2N1

DIFFIO_L26p

DIFFIO_L26n

DIFFIO_L27p

DIFFIO_L27n

RUP1

RDN1

DIFFIO_L28p

DIFFIO_L28n

DIFFIO_L29p

DIFFIO_L29n

DIFFIO_L30p

nRESET

nSTATUS

DATA1,ASDO

DCLK

DATA0

nCONFIG

TDI

TCK

TMS

TDO

nCE

H5

B2

B1

G5

E4

E3

C2

C1

D2

D1

H7

H6

J6

FLASH_nCE,nCSO E2

E1

F2

F1

G4

G3

K6

L8

K8

J7

K7

J4

H2

H1

J3

J2

J1

K2

K1

K5

L5

L2

L1

L4

L3

G1

T2

T1

L6

M6

M2

M1

M4

M3

N2

N1

L7

M5

P2

P1

R2

R1

N5

P4

P3

U2

U1

V2

V1

P5

N6

M7

M8

N8

W2

W1

Y2

Y1

T3

N7

P7

AA1

V4

V3

P6

R5

T4

T5

R6

R7

B1

C2

C1

F3

D2

D1

F4

G5

F2

F1

G2

G1

H1

H2

H5

H4

H3

J5

J4

J3

E1

M2

M1

J2

J1

K6

L6

L3

K1

L2

L1

K2

N2

N1

K5

L4

R1

P2

P1

C1

D2

D1

E1

E2

F2

F1

F3

G1

G2

G3

H2

H1

H3

H4

J1

K3

J3

L2

K2

L1

M1

M2

K1

28

30 DQS1L/CQ1L#,DPCLK1

DQ1L

DM1L/BWS#1L

DQ3L

DQ3L

DQ3L

Optional

Function(s)

Configuration

Function

F484

F256/

U256

M164

E144 (4)

DQS for X8/X9 in F484

DQS for X16/X18 in F484

DQS for X32/X36 in F484

DQS for X8/X9 in F256/U256

DQS for X16/X18 in F256/U256 DQS for X8/X9 in M164

DQS for X8/X9 in E144

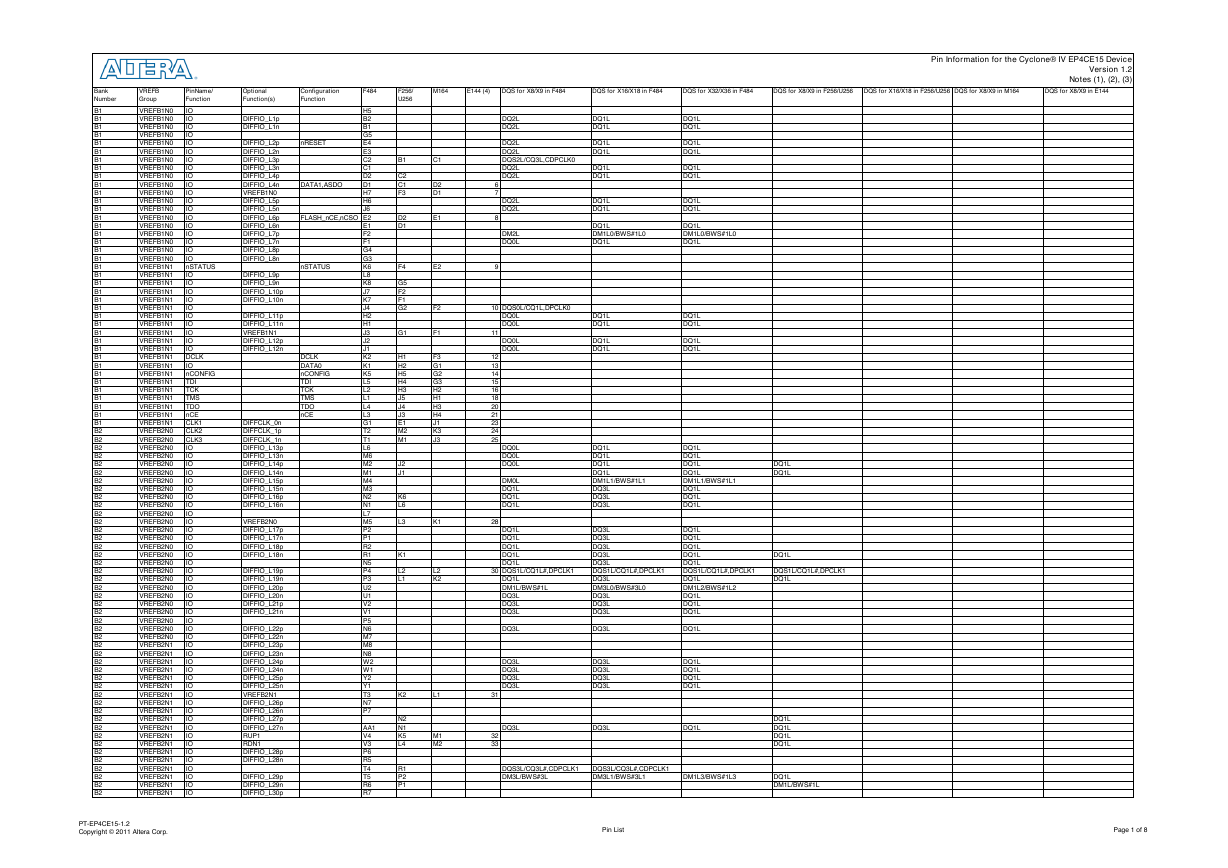

Pin Information for the Cyclone® IV EP4CE15 Device

Version 1.2

Notes (1), (2), (3)

DQ2L

DQ2L

DQ2L

DQ2L

DQS2L/CQ3L,CDPCLK0

DQ2L

DQ2L

DQ2L

DQ2L

DM2L

DQ0L

6

7

8

9

10 DQS0L/CQ1L,DPCLK0

11

12

13

14

15

16

18

20

21

23

24

25

DQ0L

DQ0L

DQ0L

DQ0L

DQ0L

DQ0L

DQ0L

DM0L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DM1L0/BWS#1L0

DQ1L

DQ1L

DM1L0/BWS#1L0

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DM1L1/BWS#1L1

DQ3L

DQ3L

DQ3L

DQ1L

DQ1L

DQ1L

DQ1L

DM1L1/BWS#1L1

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQ3L

DQ3L

DQ3L

DQ3L

DQ3L

DQS1L/CQ1L#,DPCLK1

DQ3L

DM3L0/BWS#3L0

DQ3L

DQ3L

DQ3L

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DQS1L/CQ1L#,DPCLK1

DQ1L

DM1L2/BWS#1L2

DQ1L

DQ1L

DQ1L

DQ1L

DQS1L/CQ1L#,DPCLK1

DQ1L

DQ3L

DQ3L

DQ1L

DQ3L

DQ3L

DQ3L

DQ3L

DQ3L

DQ3L

DQ3L

DQ3L

DQ1L

DQ1L

DQ1L

DQ1L

DQ3L

DQ3L

DQ1L

31

32

33

DQS3L/CQ3L#,CDPCLK1

DM3L/BWS#3L

DQS3L/CQ3L#,CDPCLK1

DM3L1/BWS#3L1

DM1L3/BWS#1L3

DQ1L

DQ1L

DQ1L

DQ1L

DQ1L

DM1L/BWS#1L

PT-EP4CE15-1.2

Copyright © 2011 Altera Corp.

Pin List

Page 1 of 8

�

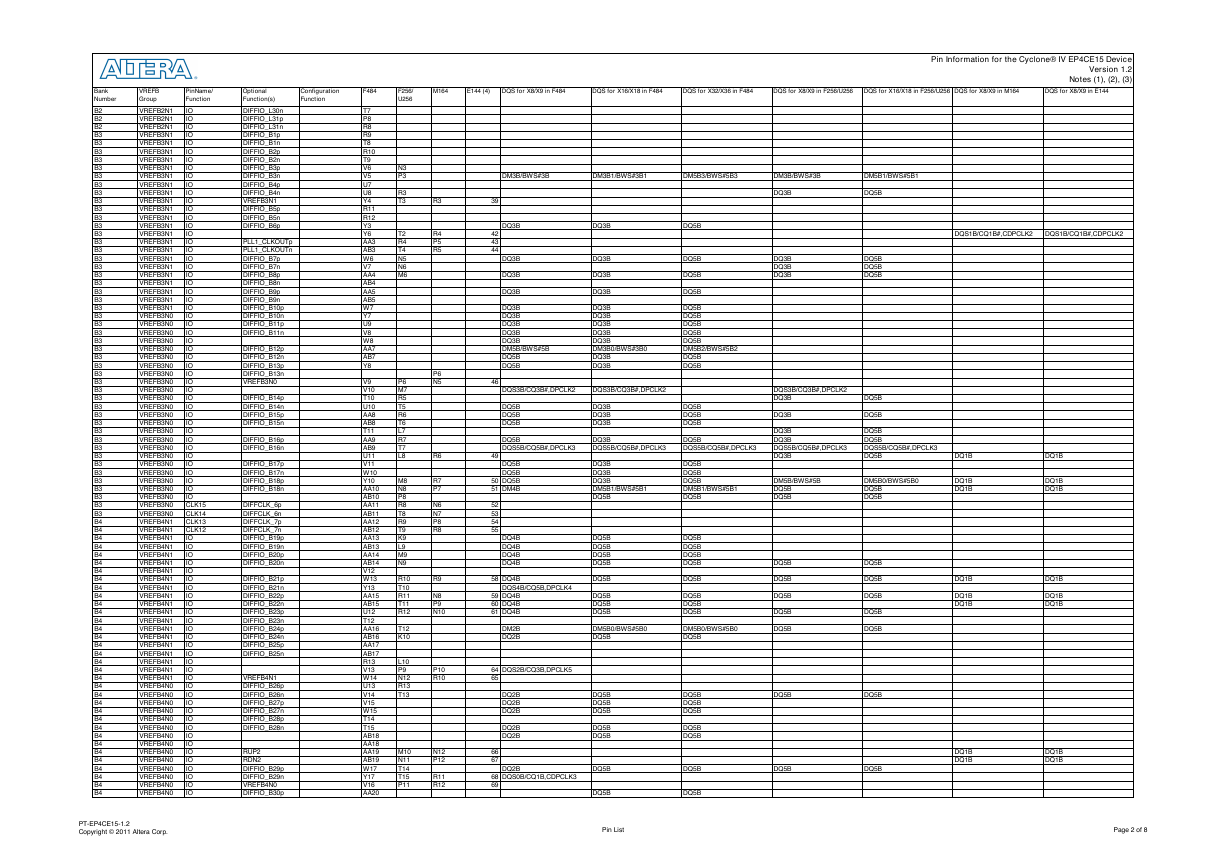

Bank

Number

VREFB

Group

PinName/

Function

Optional

Function(s)

Configuration

Function

F484

F256/

U256

M164

E144 (4)

DQS for X8/X9 in F484

DQS for X16/X18 in F484

DQS for X32/X36 in F484

DQS for X8/X9 in F256/U256

DQS for X16/X18 in F256/U256 DQS for X8/X9 in M164

DQS for X8/X9 in E144

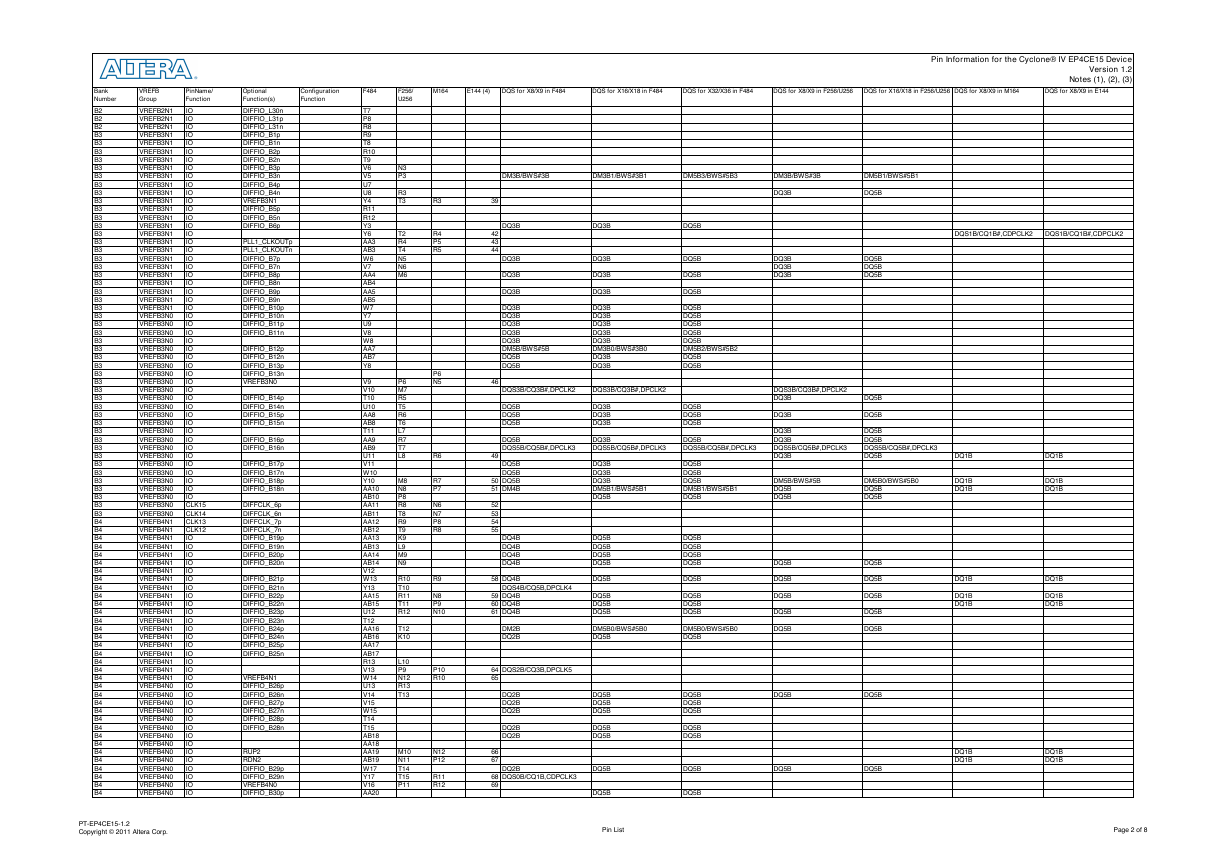

Pin Information for the Cyclone® IV EP4CE15 Device

Version 1.2

Notes (1), (2), (3)

B2

B2

B2

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

B4

VREFB2N1

VREFB2N1

VREFB2N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N1

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB3N0

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N1

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

CLK15

CLK14

CLK13

CLK12

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

PT-EP4CE15-1.2

Copyright © 2011 Altera Corp.

DIFFIO_L30n

DIFFIO_L31p

DIFFIO_L31n

DIFFIO_B1p

DIFFIO_B1n

DIFFIO_B2p

DIFFIO_B2n

DIFFIO_B3p

DIFFIO_B3n

DIFFIO_B4p

DIFFIO_B4n

VREFB3N1

DIFFIO_B5p

DIFFIO_B5n

DIFFIO_B6p

PLL1_CLKOUTp

PLL1_CLKOUTn

DIFFIO_B7p

DIFFIO_B7n

DIFFIO_B8p

DIFFIO_B8n

DIFFIO_B9p

DIFFIO_B9n

DIFFIO_B10p

DIFFIO_B10n

DIFFIO_B11p

DIFFIO_B11n

DIFFIO_B12p

DIFFIO_B12n

DIFFIO_B13p

DIFFIO_B13n

VREFB3N0

DIFFIO_B14p

DIFFIO_B14n

DIFFIO_B15p

DIFFIO_B15n

DIFFIO_B16p

DIFFIO_B16n

DIFFIO_B17p

DIFFIO_B17n

DIFFIO_B18p

DIFFIO_B18n

DIFFCLK_6p

DIFFCLK_6n

DIFFCLK_7p

DIFFCLK_7n

DIFFIO_B19p

DIFFIO_B19n

DIFFIO_B20p

DIFFIO_B20n

DIFFIO_B21p

DIFFIO_B21n

DIFFIO_B22p

DIFFIO_B22n

DIFFIO_B23p

DIFFIO_B23n

DIFFIO_B24p

DIFFIO_B24n

DIFFIO_B25p

DIFFIO_B25n

VREFB4N1

DIFFIO_B26p

DIFFIO_B26n

DIFFIO_B27p

DIFFIO_B27n

DIFFIO_B28p

DIFFIO_B28n

RUP2

RDN2

DIFFIO_B29p

DIFFIO_B29n

VREFB4N0

DIFFIO_B30p

T7

P8

R8

R9

T8

R10

T9

V6

V5

U7

U8

Y4

R11

R12

Y3

Y6

AA3

AB3

W6

V7

AA4

AB4

AA5

AB5

W7

Y7

U9

V8

W8

AA7

AB7

Y8

V9

V10

T10

U10

AA8

AB8

T11

AA9

AB9

U11

V11

W10

Y10

AA10

AB10

AA11

AB11

AA12

AB12

AA13

AB13

AA14

AB14

V12

W13

Y13

AA15

AB15

U12

T12

AA16

AB16

AA17

AB17

R13

V13

W14

U13

V14

V15

W15

T14

T15

AB18

AA18

AA19

AB19

W17

Y17

V16

AA20

N3

P3

R3

T3

T2

R4

T4

N5

N6

M6

P6

M7

R5

T5

R6

T6

L7

R7

T7

L8

M8

N8

P8

R8

T8

R9

T9

K9

L9

M9

N9

R10

T10

R11

T11

R12

T12

K10

L10

P9

N12

R13

T13

M10

N11

T14

T15

P11

R3

R4

P5

R5

P6

N5

R6

R7

P7

N6

N7

P8

R8

R9

N8

P9

N10

P10

R10

N12

P12

R11

R12

DM3B/BWS#3B

DM3B1/BWS#3B1

DM5B3/BWS#5B3

DM3B/BWS#3B

DM5B1/BWS#5B1

DQ3B

DQ5B

39

42

43

44

46

DQ3B

DQ3B

DQ5B

DQ3B

DQ3B

DQ3B

DQ3B

DQ3B

DQ3B

DQ3B

DQ3B

DM5B/BWS#5B

DQ5B

DQ5B

DQ3B

DQ3B

DQ3B

DQ3B

DQ3B

DQ3B

DQ3B

DQ3B

DM3B0/BWS#3B0

DQ3B

DQ3B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DM5B2/BWS#5B2

DQ5B

DQ5B

DQS3B/CQ3B#,DPCLK2

DQS3B/CQ3B#,DPCLK2

DQ5B

DQ5B

DQ5B

DQ3B

DQ3B

DQ3B

DQ5B

DQ5B

DQ5B

DQ5B

DQS5B/CQ5B#,DPCLK3

DQ3B

DQS5B/CQ5B#,DPCLK3

DQ5B

DQS5B/CQ5B#,DPCLK3

49

DQ5B

DQ5B

50 DQ5B

51 DM4B

52

53

54

55

DQ4B

DQ4B

DQ4B

DQ4B

58 DQ4B

DQS4B/CQ5B,DPCLK4

59 DQ4B

60 DQ4B

61 DQ4B

DM2B

DQ2B

64 DQS2B/CQ3B,DPCLK5

65

DQ2B

DQ2B

DQ2B

DQ2B

DQ2B

66

67

DQ2B

68 DQS0B/CQ1B,CDPCLK3

69

DQ3B

DQ3B

DQ3B

DM5B1/BWS#5B1

DQ5B

DQ5B

DQ5B

DQ5B

DM5B1/BWS#5B1

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DM5B0/BWS#5B0

DQ5B

DM5B0/BWS#5B0

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

Pin List

DQS1B/CQ1B#,CDPCLK2

DQS1B/CQ1B#,CDPCLK2

DQ3B

DQ3B

DQ3B

DQ5B

DQ5B

DQ5B

DQS3B/CQ3B#,DPCLK2

DQ3B

DQ3B

DQ5B

DQ5B

DQ3B

DQ3B

DQS5B/CQ5B#,DPCLK3

DQ3B

DQ5B

DQ5B

DQS5B/CQ5B#,DPCLK3

DQ5B

DM5B/BWS#5B

DQ5B

DQ5B

DM5B0/BWS#5B0

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ5B

DQ1B

DQ1B

DQ1B

DQ1B

DQ1B

DQ1B

DQ1B

DQ1B

DQ1B

DQ1B

DQ1B

DQ1B

DQ5B

DQ5B

DQ1B

DQ1B

DQ1B

DQ1B

Page 2 of 8

�

M164

E144 (4)

DQS for X8/X9 in F484

DQS for X16/X18 in F484

DQS for X32/X36 in F484

DQS for X8/X9 in F256/U256

DQS for X16/X18 in F256/U256 DQS for X8/X9 in M164

DQS for X8/X9 in E144

DQ2B

DQ5B

DQ5B

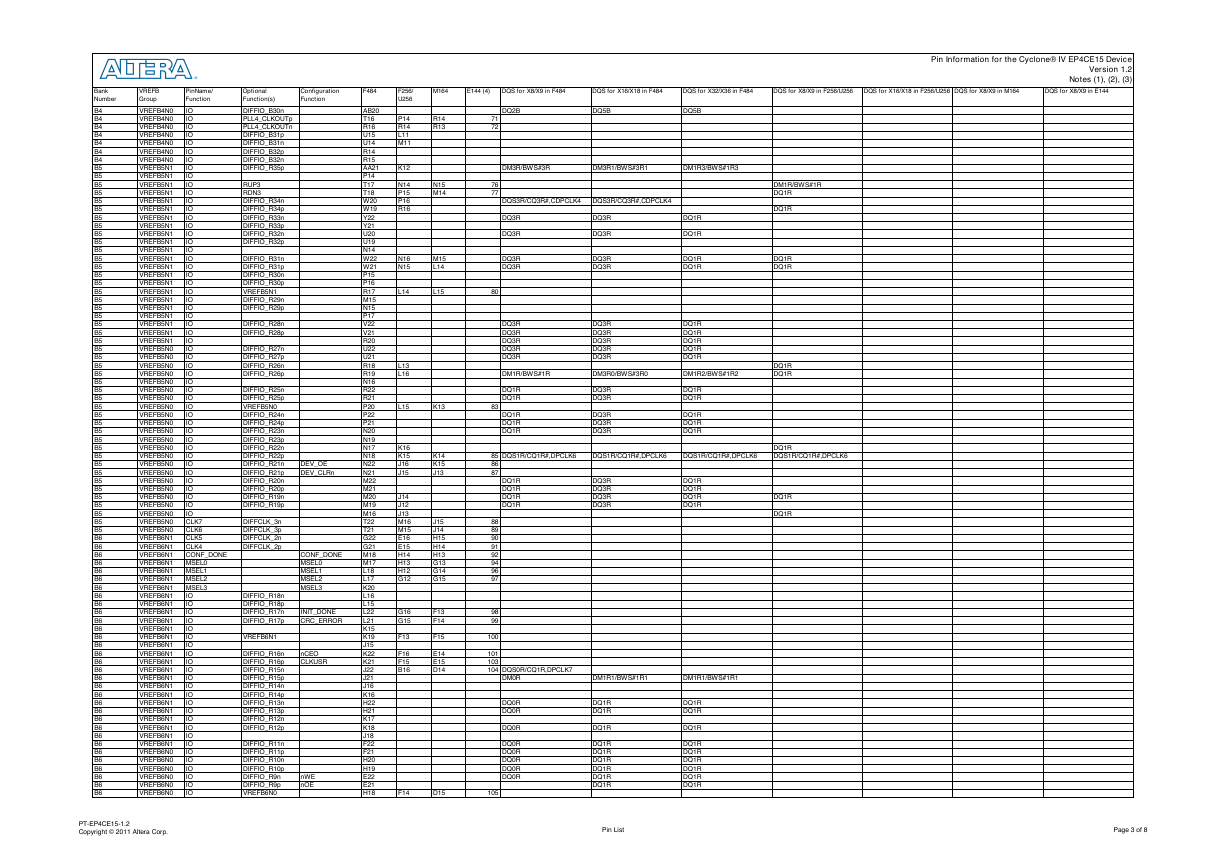

Pin Information for the Cyclone® IV EP4CE15 Device

Version 1.2

Notes (1), (2), (3)

F256/

U256

P14

R14

L11

M11

K12

N14

P15

P16

R16

R14

R13

N15

M14

71

72

76

77

N16

N15

M15

L14

L14

L15

80

DM3R/BWS#3R

DM3R1/BWS#3R1

DM1R3/BWS#1R3

DQS3R/CQ3R#,CDPCLK4

DQS3R/CQ3R#,CDPCLK4

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DM1R/BWS#1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

L13

L16

DM1R/BWS#1R

DM3R0/BWS#3R0

DM1R2/BWS#1R2

L15

K13

83

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ3R

DQ3R

DQ3R

DQ3R

DQ3R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

85 DQS1R/CQ1R#,DPCLK6

86

87

DQS1R/CQ1R#,DPCLK6

DQS1R/CQ1R#,DPCLK6

DQ1R

DQS1R/CQ1R#,DPCLK6

DQ1R

DQ1R

DQ1R

DQ1R

DQ3R

DQ3R

DQ3R

DQ3R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

Bank

Number

VREFB

Group

PinName/

Function

Optional

Function(s)

Configuration

Function

B4

B4

B4

B4

B4

B4

B4

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B5

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB4N0

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N1

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB5N0

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N1

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

CLK7

CLK6

CLK5

CLK4

CONF_DONE

MSEL0

MSEL1

MSEL2

MSEL3

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

DIFFIO_B30n

PLL4_CLKOUTp

PLL4_CLKOUTn

DIFFIO_B31p

DIFFIO_B31n

DIFFIO_B32p

DIFFIO_B32n

DIFFIO_R35p

RUP3

RDN3

DIFFIO_R34n

DIFFIO_R34p

DIFFIO_R33n

DIFFIO_R33p

DIFFIO_R32n

DIFFIO_R32p

DIFFIO_R31n

DIFFIO_R31p

DIFFIO_R30n

DIFFIO_R30p

VREFB5N1

DIFFIO_R29n

DIFFIO_R29p

DIFFIO_R28n

DIFFIO_R28p

DIFFIO_R27n

DIFFIO_R27p

DIFFIO_R26n

DIFFIO_R26p

DIFFIO_R25n

DIFFIO_R25p

VREFB5N0

DIFFIO_R24n

DIFFIO_R24p

DIFFIO_R23n

DIFFIO_R23p

DIFFIO_R22n

DIFFIO_R22p

DIFFIO_R21n

DIFFIO_R21p

DIFFIO_R20n

DIFFIO_R20p

DIFFIO_R19n

DIFFIO_R19p

DIFFCLK_3n

DIFFCLK_3p

DIFFCLK_2n

DIFFCLK_2p

DIFFIO_R18n

DIFFIO_R18p

DIFFIO_R17n

DIFFIO_R17p

VREFB6N1

DIFFIO_R16n

DIFFIO_R16p

DIFFIO_R15n

DIFFIO_R15p

DIFFIO_R14n

DIFFIO_R14p

DIFFIO_R13n

DIFFIO_R13p

DIFFIO_R12n

DIFFIO_R12p

DIFFIO_R11n

DIFFIO_R11p

DIFFIO_R10n

DIFFIO_R10p

DIFFIO_R9n

DIFFIO_R9p

VREFB6N0

DEV_OE

DEV_CLRn

CONF_DONE

MSEL0

MSEL1

MSEL2

MSEL3

INIT_DONE

CRC_ERROR

nCEO

CLKUSR

nWE

nOE

F484

AB20

T16

R16

U15

U14

R14

R15

AA21

P14

T17

T18

W20

W19

Y22

Y21

U20

U19

N14

W22

W21

P15

P16

R17

M15

N15

P17

V22

V21

R20

U22

U21

R18

R19

N16

R22

R21

P20

P22

P21

N20

N19

N17

N18

N22

N21

M22

M21

M20

M19

M16

T22

T21

G22

G21

M18

M17

L18

L17

K20

L16

L15

L22

L21

K15

K19

J15

K22

K21

J22

J21

J16

K16

H22

H21

K17

K18

J18

F22

F21

H20

H19

E22

E21

H18

PT-EP4CE15-1.2

Copyright © 2011 Altera Corp.

K16

K15

J16

J15

J14

J12

J13

M16

M15

E16

E15

H14

H13

H12

G12

G16

G15

F13

F16

F15

B16

K14

K15

J13

J15

J14

H15

H14

H13

G13

G14

G15

F13

F14

F15

E14

E15

D14

F14

D15

105

88

89

90

91

92

94

96

97

98

99

100

101

103

104 DQS0R/CQ1R,DPCLK7

DM0R

DQ0R

DQ0R

DQ0R

DQ0R

DQ0R

DQ0R

DQ0R

DQ0R

DM1R1/BWS#1R1

DM1R1/BWS#1R1

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

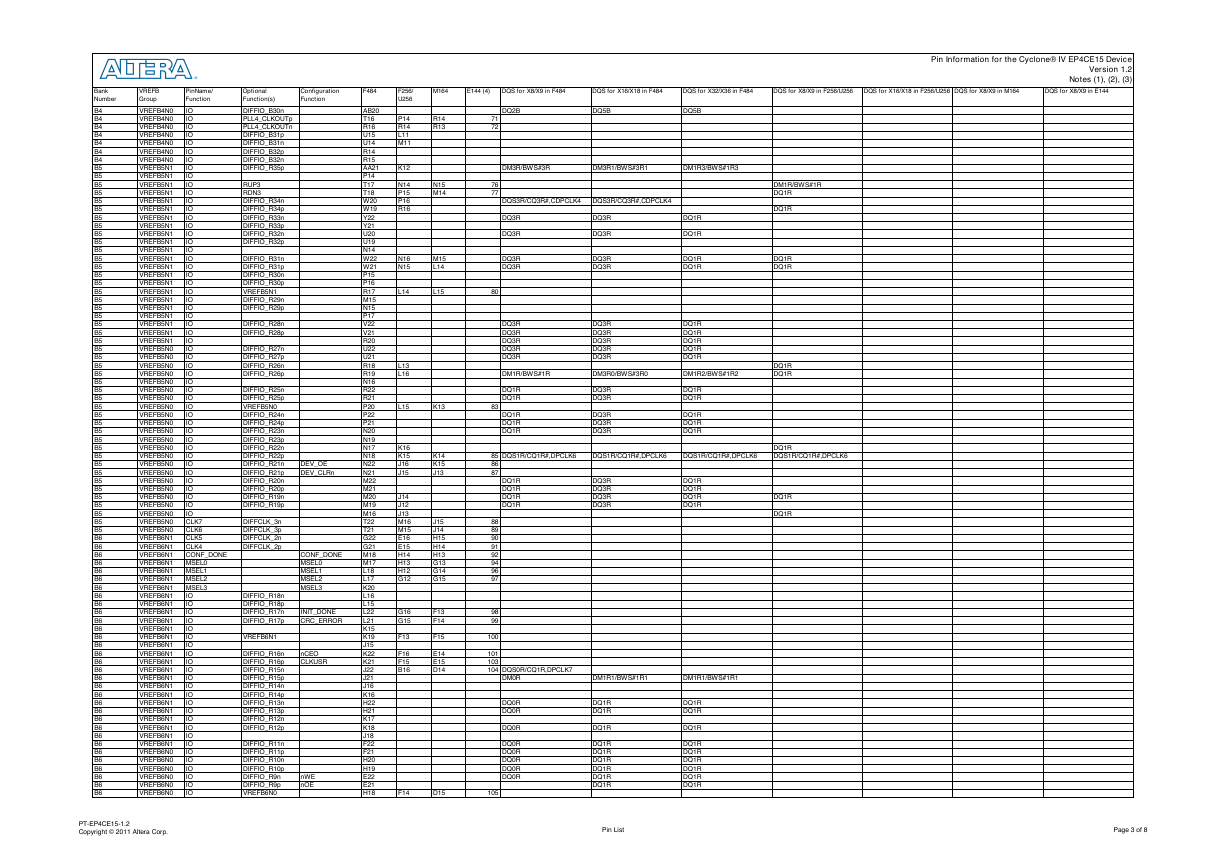

Pin List

Page 3 of 8

�

M164

E144 (4)

DQS for X8/X9 in F484

DQS for X16/X18 in F484

DQS for X32/X36 in F484

DQS for X8/X9 in F256/U256

DQS for X16/X18 in F256/U256 DQS for X8/X9 in M164

DQS for X8/X9 in E144

Pin Information for the Cyclone® IV EP4CE15 Device

Version 1.2

Notes (1), (2), (3)

DM2R

DQ2R

DQ2R

DQ2R

DQ2R

DQ2R

DQ2R

DQ2R

C15

106 DQS2R/CQ3R,CDPCLK5

B13

A14

A13

B12

A12

B11

A11

110

111

112

113

114

115

DQ2R

DQ2T

DQ2T

DQ2T

DQ2T

DQ2T

DQ2T

DQ2T

DQ2T

DM2T

DQ4T

DM1R0/BWS#1R0

DQ1R

DQ1R

DQ1R

DQ1R

DM1R0/BWS#1R0

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ1R

DQ1R

DQ1R

DQ1R

DQ1R

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DM5T0/BWS#5T0

DQ5T

DQ5T

DQ5T

DM5T0/BWS#5T0

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ1T

DQ1T

DQ1T

DQ1T

B10

A10

119

120 DQ4T

DQ5T

DQ5T

DQ1T

DQ1T

C9

121 DQS2T/CQ3T,DPCLK8

DQ4T

DQ4T

DQ4T

DQ4T

DQ4T

DQ4T

E9

A9

125 DQS4T/CQ5T,DPCLK9

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DM5T/BWS#5T

DQ5T

DQ5T

DQ5T

DM5T0/BWS#5T0

F256/

U256

D16

D15

G11

C16

C15

C14

D14

D11

D12

C11

B13

A14

B14

E11

E10

A12

B12

A11

B11

A13

A15

F9

A10

B10

C9

D9

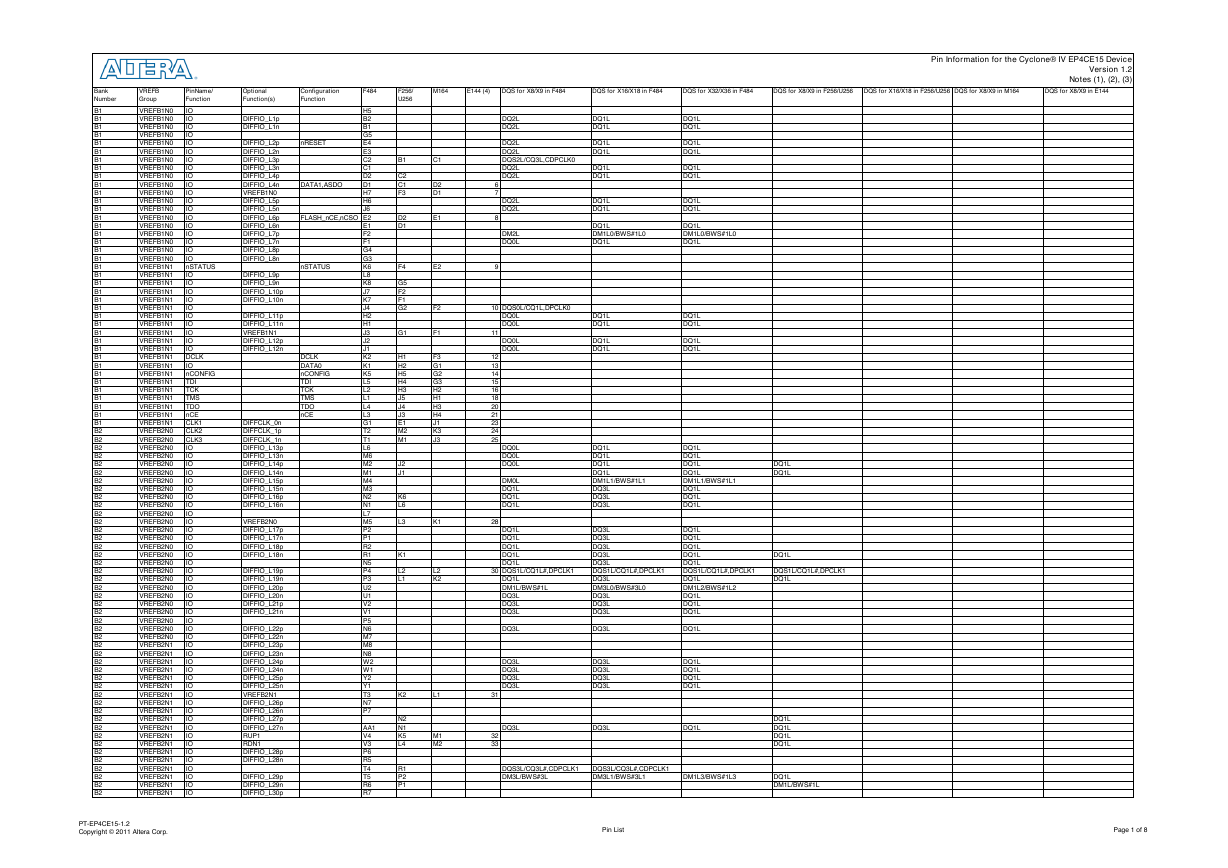

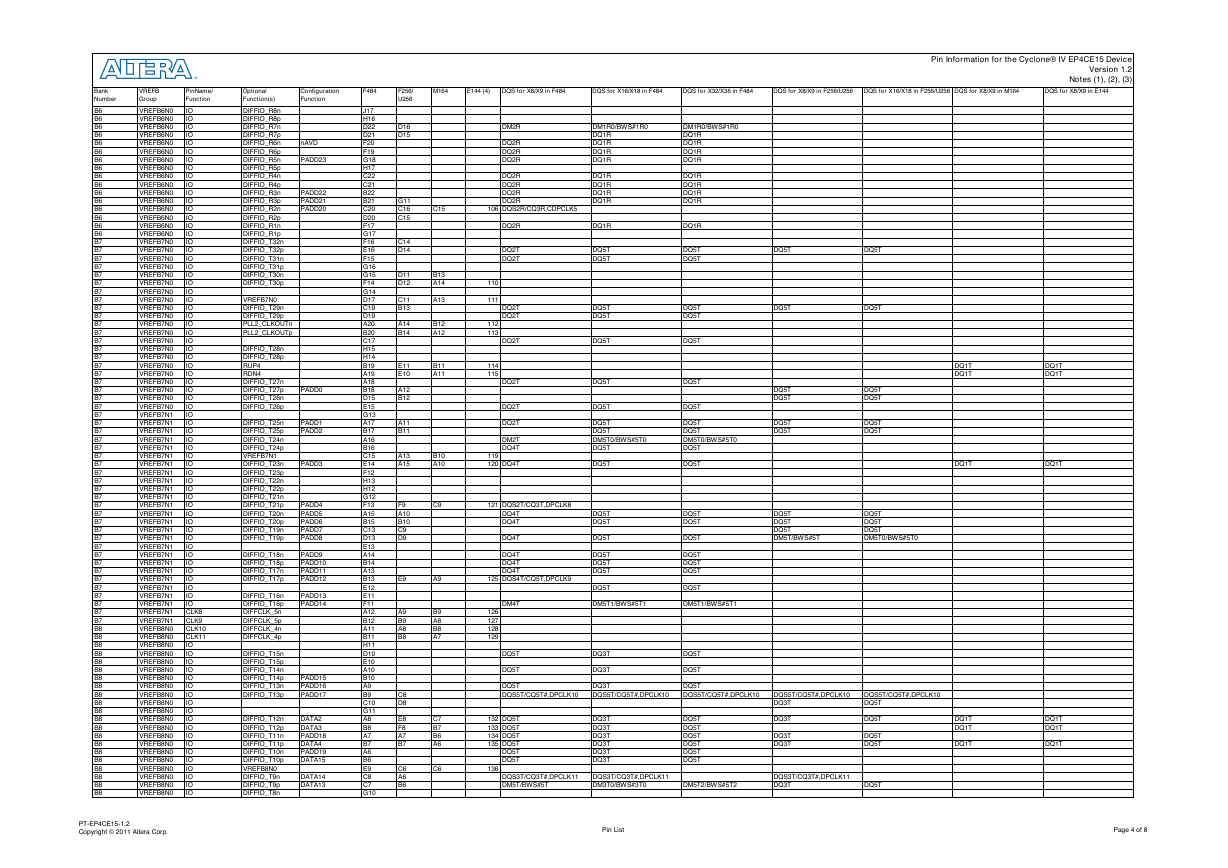

Bank

Number

VREFB

Group

PinName/

Function

Optional

Function(s)

Configuration

Function

F484

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B6

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B7

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB6N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N0

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB7N1

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

CLK8

CLK9

CLK10

CLK11

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

DIFFIO_R8n

DIFFIO_R8p

DIFFIO_R7n

DIFFIO_R7p

DIFFIO_R6n

DIFFIO_R6p

DIFFIO_R5n

DIFFIO_R5p

DIFFIO_R4n

DIFFIO_R4p

DIFFIO_R3n

DIFFIO_R3p

DIFFIO_R2n

DIFFIO_R2p

DIFFIO_R1n

DIFFIO_R1p

DIFFIO_T32n

DIFFIO_T32p

DIFFIO_T31n

DIFFIO_T31p

DIFFIO_T30n

DIFFIO_T30p

VREFB7N0

DIFFIO_T29n

DIFFIO_T29p

PLL2_CLKOUTn

PLL2_CLKOUTp

DIFFIO_T28n

DIFFIO_T28p

RUP4

RDN4

DIFFIO_T27n

DIFFIO_T27p

DIFFIO_T26n

DIFFIO_T26p

DIFFIO_T25n

DIFFIO_T25p

DIFFIO_T24n

DIFFIO_T24p

VREFB7N1

DIFFIO_T23n

DIFFIO_T23p

DIFFIO_T22n

DIFFIO_T22p

DIFFIO_T21n

DIFFIO_T21p

DIFFIO_T20n

DIFFIO_T20p

DIFFIO_T19n

DIFFIO_T19p

DIFFIO_T18n

DIFFIO_T18p

DIFFIO_T17n

DIFFIO_T17p

DIFFIO_T16n

DIFFIO_T16p

DIFFCLK_5n

DIFFCLK_5p

DIFFCLK_4n

DIFFCLK_4p

DIFFIO_T15n

DIFFIO_T15p

DIFFIO_T14n

DIFFIO_T14p

DIFFIO_T13n

DIFFIO_T13p

DIFFIO_T12n

DIFFIO_T12p

DIFFIO_T11n

DIFFIO_T11p

DIFFIO_T10n

DIFFIO_T10p

VREFB8N0

DIFFIO_T9n

DIFFIO_T9p

DIFFIO_T8n

nAVD

PADD23

PADD22

PADD21

PADD20

PADD0

PADD1

PADD2

PADD3

PADD4

PADD5

PADD6

PADD7

PADD8

PADD9

PADD10

PADD11

PADD12

PADD13

PADD14

PADD15

PADD16

PADD17

DATA2

DATA3

PADD18

DATA4

PADD19

DATA15

DATA14

DATA13

J17

H16

D22

D21

F20

F19

G18

H17

C22

C21

B22

B21

C20

D20

F17

G17

F16

E16

F15

G16

G15

F14

G14

D17

C19

D19

A20

B20

C17

H15

H14

B19

A19

A18

B18

D15

E15

G13

A17

B17

A16

B16

C15

E14

F12

H13

H12

G12

F13

A15

B15

C13

D13

E13

A14

B14

A13

B13

E12

E11

F11

A12

B12

A11

B11

H11

D10

E10

A10

B10

A9

B9

C10

G11

A8

B8

A7

B7

A6

B6

E9

C8

C7

G10

B9

A8

B8

A7

C7

B7

B6

A6

C6

A9

B9

A8

B8

C8

D8

E8

F8

A7

B7

C6

A6

B6

DM4T

DM5T1/BWS#5T1

DM5T1/BWS#5T1

126

127

128

129

DQ5T

DQ5T

DQ3T

DQ3T

DQ5T

DQ5T

DQ5T

DQS5T/CQ5T#,DPCLK10

DQ3T

DQS5T/CQ5T#,DPCLK10

DQ5T

DQS5T/CQ5T#,DPCLK10

DQS5T/CQ5T#,DPCLK10

DQ3T

DQS5T/CQ5T#,DPCLK10

DQ5T

132 DQ5T

133 DQ5T

134 DQ5T

135 DQ5T

DQ5T

DQ5T

136

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ3T

DQ3T

DQ3T

DQ5T

DQ5T

DQ5T

DQ1T

DQ1T

DQ1T

DQ1T

DQ1T

DQ1T

DQS3T/CQ3T#,DPCLK11

DM5T/BWS#5T

DQS3T/CQ3T#,DPCLK11

DM3T0/BWS#3T0

DM5T2/BWS#5T2

DQS3T/CQ3T#,DPCLK11

DQ3T

DQ5T

PT-EP4CE15-1.2

Copyright © 2011 Altera Corp.

Pin List

Page 4 of 8

�

M164

E144 (4)

DQS for X8/X9 in F484

DQS for X16/X18 in F484

DQS for X32/X36 in F484

DQS for X8/X9 in F256/U256

DQS for X16/X18 in F256/U256 DQS for X8/X9 in M164

DQS for X8/X9 in E144

Pin Information for the Cyclone® IV EP4CE15 Device

Version 1.2

Notes (1), (2), (3)

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ5T

DQ1T

DQ1T

DQ3T

DQ3T

DQ3T

DQ3T

DQ5T

DQ5T

DQ5T

DQ5T

DM3T/BWS#3T

DM5T1/BWS#5T1

DM3T/BWS#3T

DM3T1/BWS#3T1

DM5T3/BWS#5T3

DQS1T/CQ1T#,CDPCLK7

DQS1T/CQ1T#,CDPCLK7

DQ1T

DM1T

DQ1T

DM1T

137 DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

DQ3T

141

142

143

144

19

27

41

48

57

63

82

95

118

123

131

140

4

22

79

A5

B4

A4

C4

A3

A2

B3

E3

G12

D7

N14

M7

N1

P13

P4

D9

M3

R2

J12

K4

N4

G4

D5

C12

D11

C14

M13

M10

C2

C8

E13

J2

N11

P11

F256/

U256

E7

E6

A5

B5

D6

A4

B4

A2

D5

A3

B3

C3

D3

H7

H8

H9

H10

J7

J8

J9

J10

F6

F10

J11

K8

B2

B15

C5

C12

D7

D10

E4

E13

G4

G13

K4

K13

M4

M13

N7

N10

P5

P12

R2

R15

E2

H16

H15

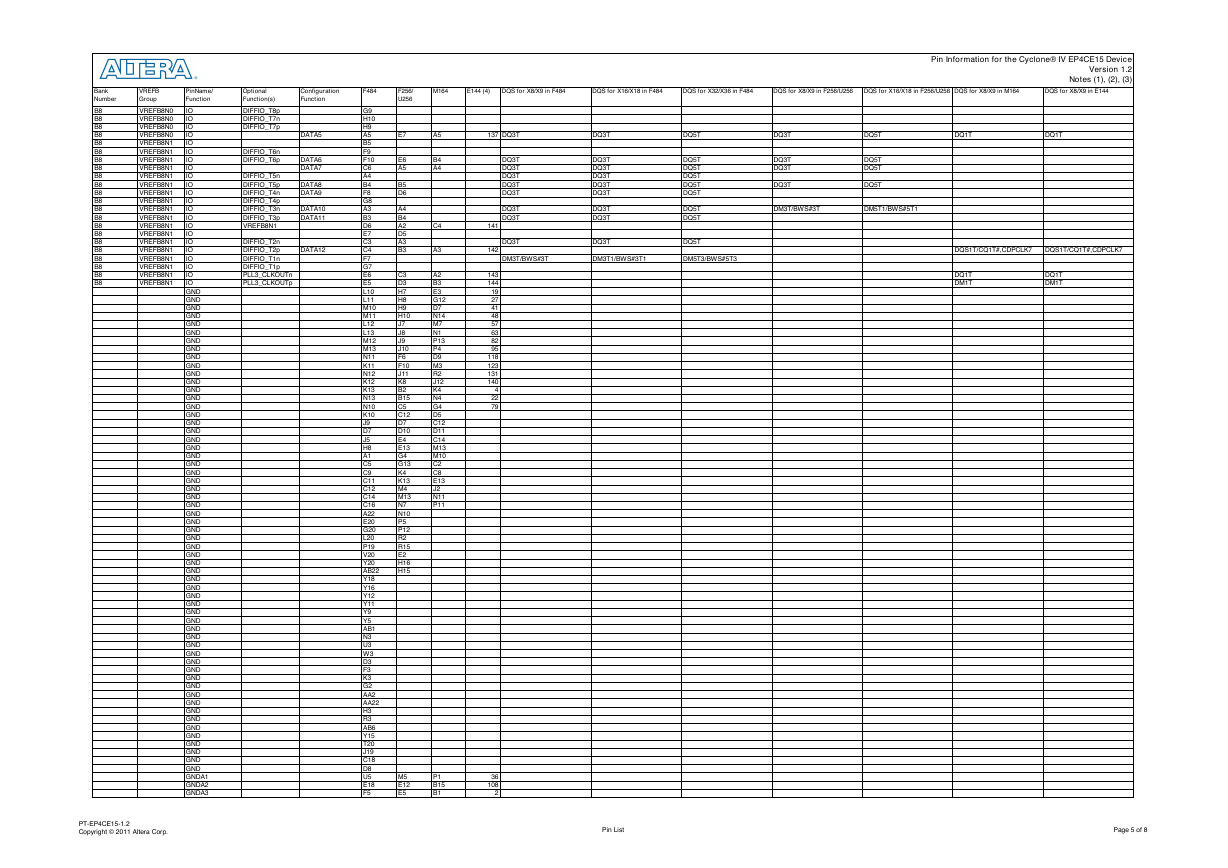

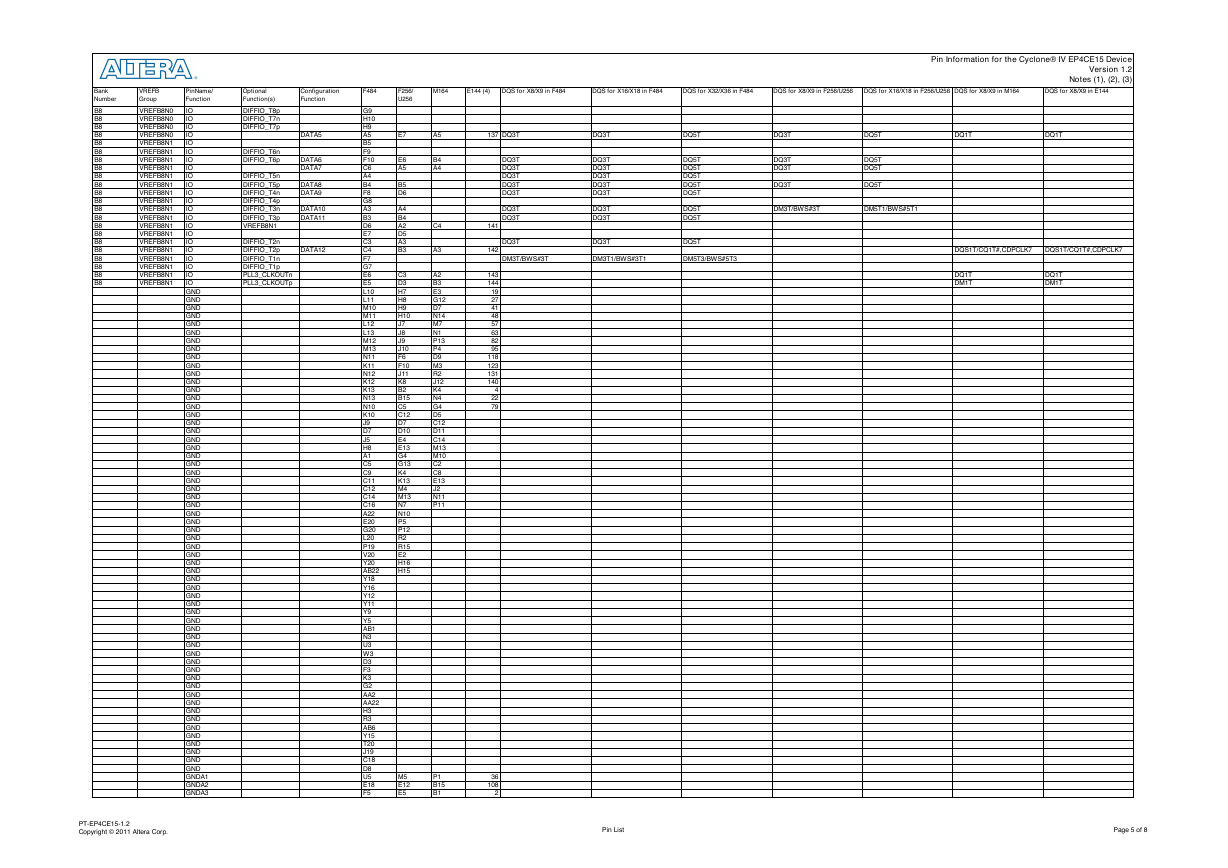

Bank

Number

VREFB

Group

PinName/

Function

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

B8

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N0

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

VREFB8N1

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDA1

GNDA2

GNDA3

Configuration

Function

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

Optional

Function(s)

DIFFIO_T8p

DIFFIO_T7n

DIFFIO_T7p

DIFFIO_T6n

DIFFIO_T6p

DIFFIO_T5n

DIFFIO_T5p

DIFFIO_T4n

DIFFIO_T4p

DIFFIO_T3n

DIFFIO_T3p

VREFB8N1

DIFFIO_T2n

DIFFIO_T2p

DIFFIO_T1n

DIFFIO_T1p

PLL3_CLKOUTn

PLL3_CLKOUTp

F484

G9

H10

H9

A5

B5

F9

F10

C6

A4

B4

F8

G8

A3

B3

D6

E7

C3

C4

F7

G7

E6

E5

L10

L11

M10

M11

L12

L13

M12

M13

N11

K11

N12

K12

K13

N13

N10

K10

J9

D7

J5

H8

A1

C5

C9

C11

C12

C14

C16

A22

E20

G20

L20

P19

V20

Y20

AB22

Y18

Y16

Y12

Y11

Y9

Y5

AB1

N3

U3

W3

D3

F3

K3

G2

AA2

AA22

H3

R3

AB6

Y15

T20

J19

C18

D8

U5

E18

F5

M5

E12

E5

P1

B15

B1

36

108

2

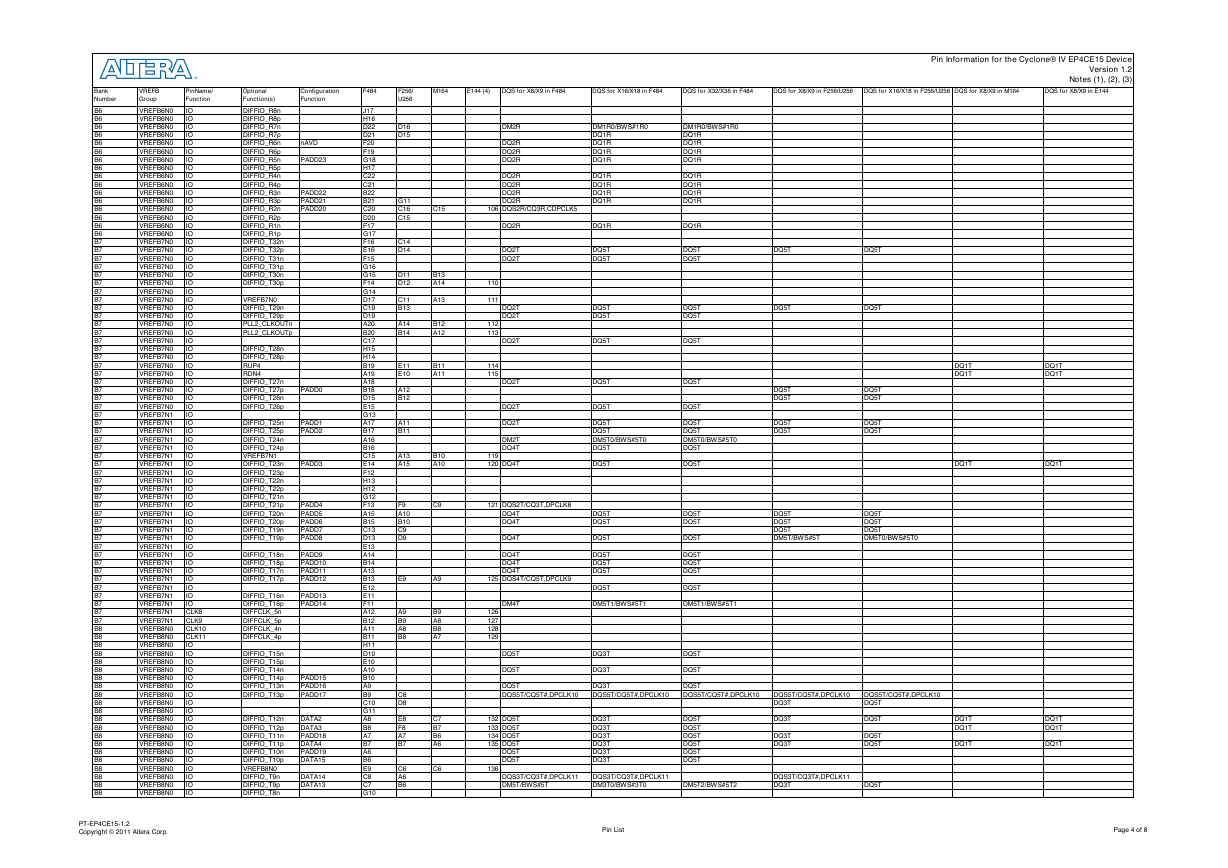

PT-EP4CE15-1.2

Copyright © 2011 Altera Corp.

Pin List

Page 5 of 8

�

Bank

Number

VREFB

Group

PinName/

Function

Optional

Function(s)

Configuration

Function

GNDA4

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCIO1

VCCIO1

VCCIO1

VCCIO1

VCCIO2

VCCIO2

VCCIO2

VCCIO2

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO5

VCCIO5

VCCIO5

VCCIO5

VCCIO6

VCCIO6

VCCIO6

VCCIO6

VCCIO7

VCCIO7

VCCIO7

VCCIO7

VCCIO7

VCCIO8

VCCIO8

VCCIO8

VCCIO8

VCCIO8

VCCA1

VCCA2

VCCA3

VCCA4

VCCD_PLL1

VCCD_PLL2

VCCD_PLL3

VCCD_PLL4

F484

V18

J11

J12

L14

M14

P11

P12

L9

M9

J13

J14

K14

J10

K9

N9

P9

P10

P13

U16

U17

T13

J8

D4

F4

K4

H4

N4

U4

W4

R4

AB2

W5

W9

W11

AA6

AB21

W12

W16

W18

Y14

P18

V19

Y19

T19

E19

G19

L19

J20

A21

D12

D14

D16

D18

A2

D5

D9

D11

E8

T6

F18

G6

U18

U6

E17

F6

V17

F256/

U256

M12

F7

F11

G6

G7

G8

G9

G10

H6

H11

J6

K7

K11

E3

G3

K3

M3

P4

P7

T1

P10

P13

T16

K14

M14

E14

G14

A16

C10

C13

A1

C4

C7

L5

F12

F5

L12

N4

D13

D4

N13

M164

E144 (4)

DQS for X8/X9 in F484

DQS for X16/X18 in F484

DQS for X32/X36 in F484

DQS for X8/X9 in F256/U256

DQS for X16/X18 in F256/U256 DQS for X8/X9 in M164

DQS for X8/X9 in E144

Pin Information for the Cyclone® IV EP4CE15 Device

Version 1.2

Notes (1), (2), (3)

P15

D3

D6

N2

D10

F12

H12

M8

M11

D8

L3

P3

K12

F4

J4

M5

M6

M9

N9

L13

D13

C10

C11

B5

C5

R1

A15

A1

R15

P2

B14

B2

P14

74

5

29

34

38

45

70

78

84

102

116

124

138

17

26

40

47

56

62

81

93

117

122

130

139

35

107

3

75

37

109

1

73

Notes:

(1) If the p pin or n pin is not available for the package, the particular differential pair is not supported.

(2) For DQS pins that do not have the associated DQpins, the particular DQS is not supported.

(3) For more information about pin definition and pin connection guidelines, refer to the

Cyclone IV Device Family Pin Connection Guidelines.

(4) The E144 package has an exposed pad at the bottom of the package. This exposed pad is a ground pad that must be connected to the ground plane on your PCB.

This exposed pad is used for electrical connectivity, and not for thermal purposes.

PT-EP4CE15-1.2

Copyright © 2011 Altera Corp.

Pin List

Page 6 of 8

�

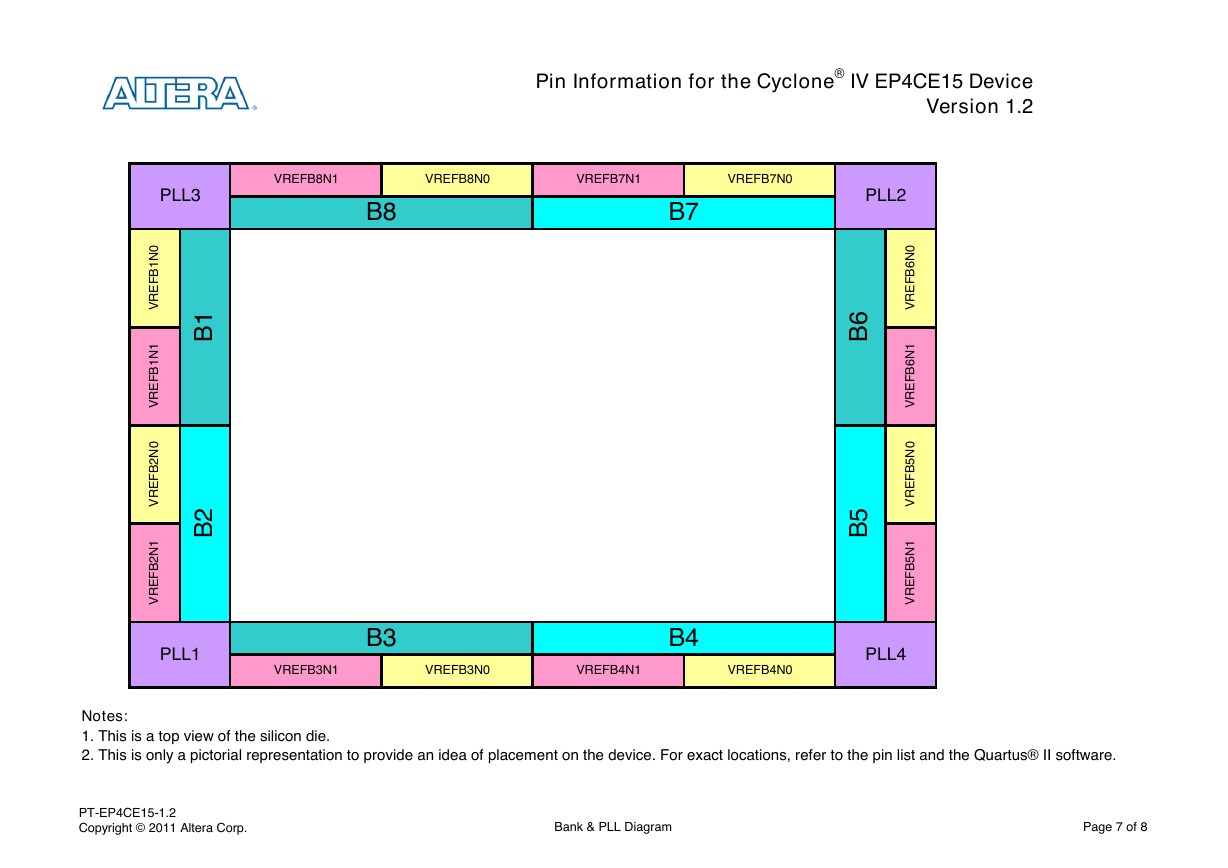

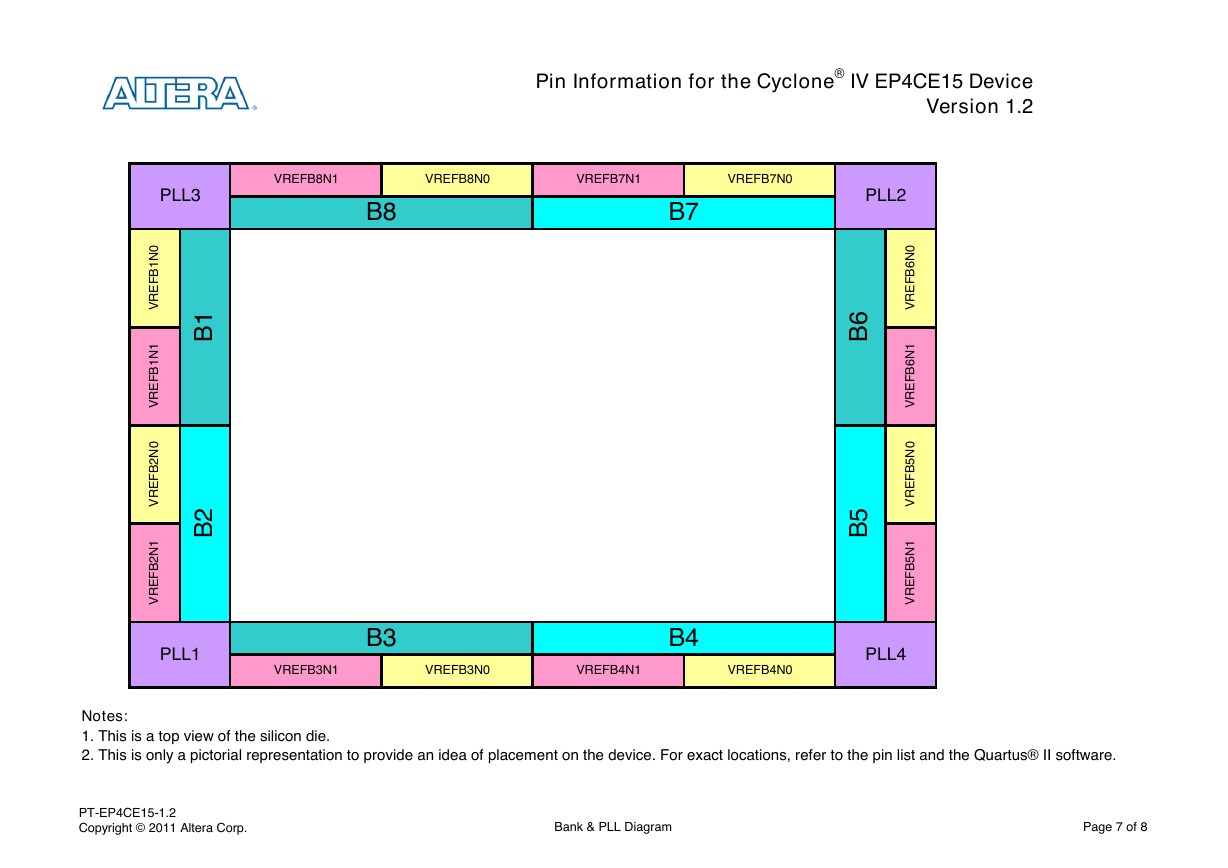

Pin Information for the Cyclone® IV EP4CE15 Device

Version 1.2

VREFB8N1

VREFB8N0

VREFB7N1

VREFB7N0

PLL3

B8

B7

PLL2

0

N

1

B

F

E

R

V

1

N

1

B

F

E

R

V

0

N

2

B

F

E

R

V

1

N

2

B

F

E

R

V

1

B

2

B

6

B

5

B

0

N

6

B

F

E

R

V

1

N

6

B

F

E

R

V

0

N

5

B

F

E

R

V

1

N

5

B

F

E

R

V

PLL1

B3

B4

VREFB3N1

VREFB3N0

VREFB4N1

VREFB4N0

PLL4

Notes:

1. This is a top view of the silicon die.

2. This is only a pictorial representation to provide an idea of placement on the device. For exact locations, refer to the pin list and the Quartus® II software.

PT-EP4CE15-1.2

Copyright © 2011 Altera Corp.

Bank & PLL Diagram

Page 7 of 8

�

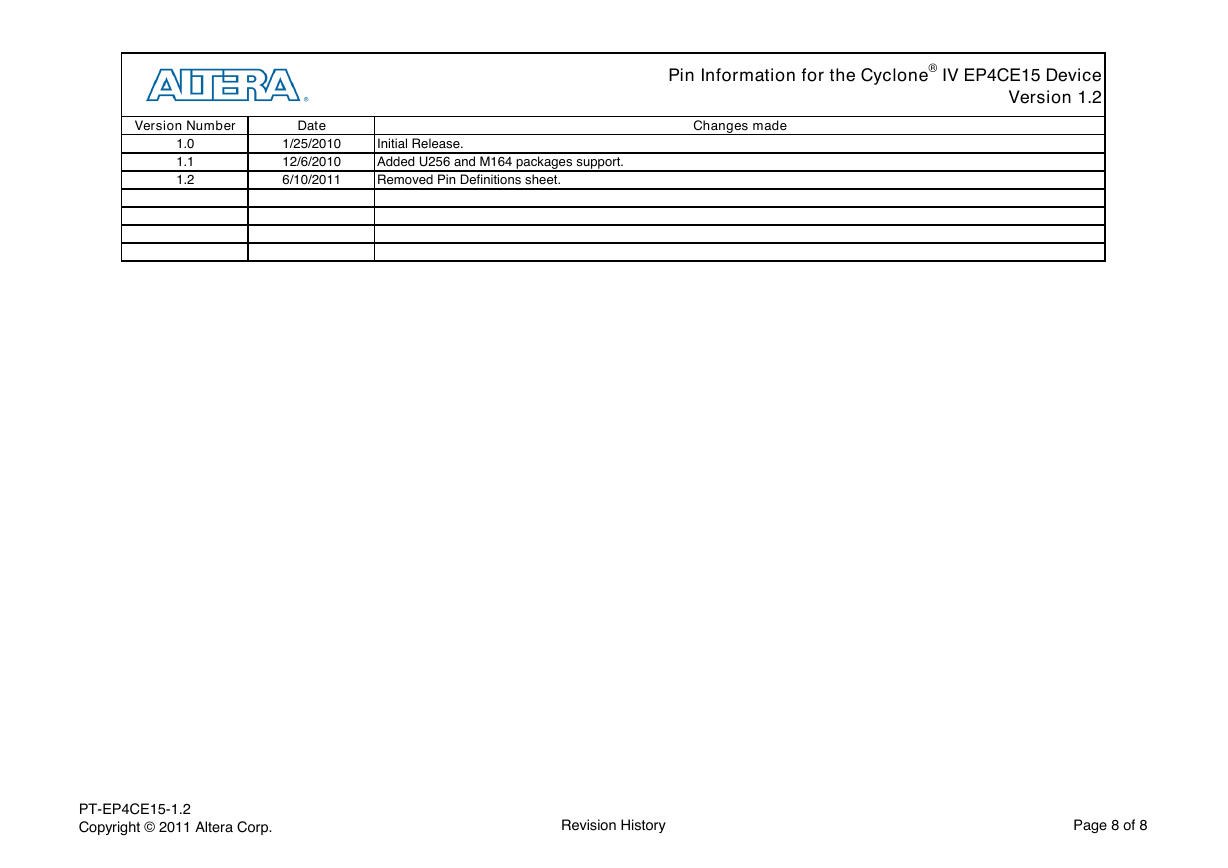

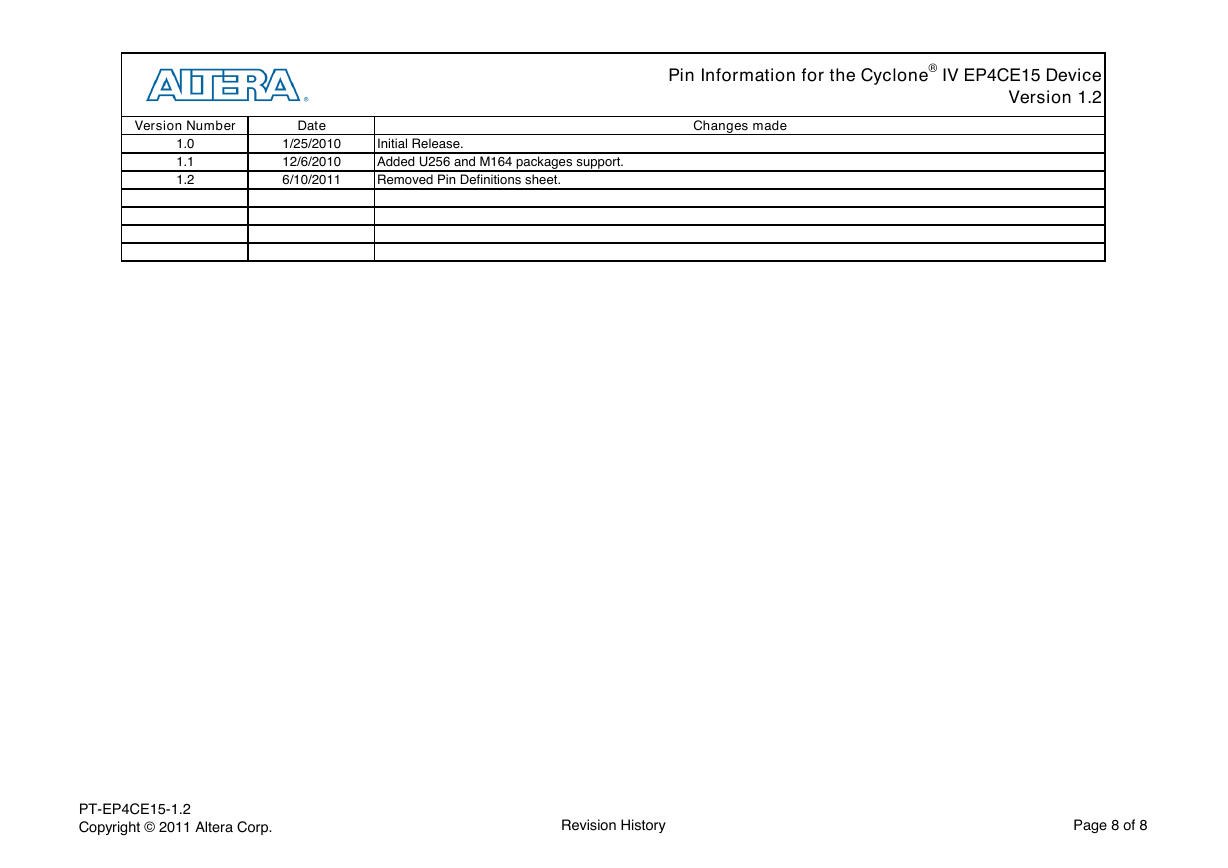

Version Number

1.0

1.1

1.2

Date

1/25/2010

12/6/2010

6/10/2011

Initial Release.

Added U256 and M164 packages support.

Removed Pin Definitions sheet.

Changes made

Pin Information for the Cyclone® IV EP4CE15 Device

Version 1.2

PT-EP4CE15-1.2

Copyright © 2011 Altera Corp.

Revision History

Page 8 of 8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc