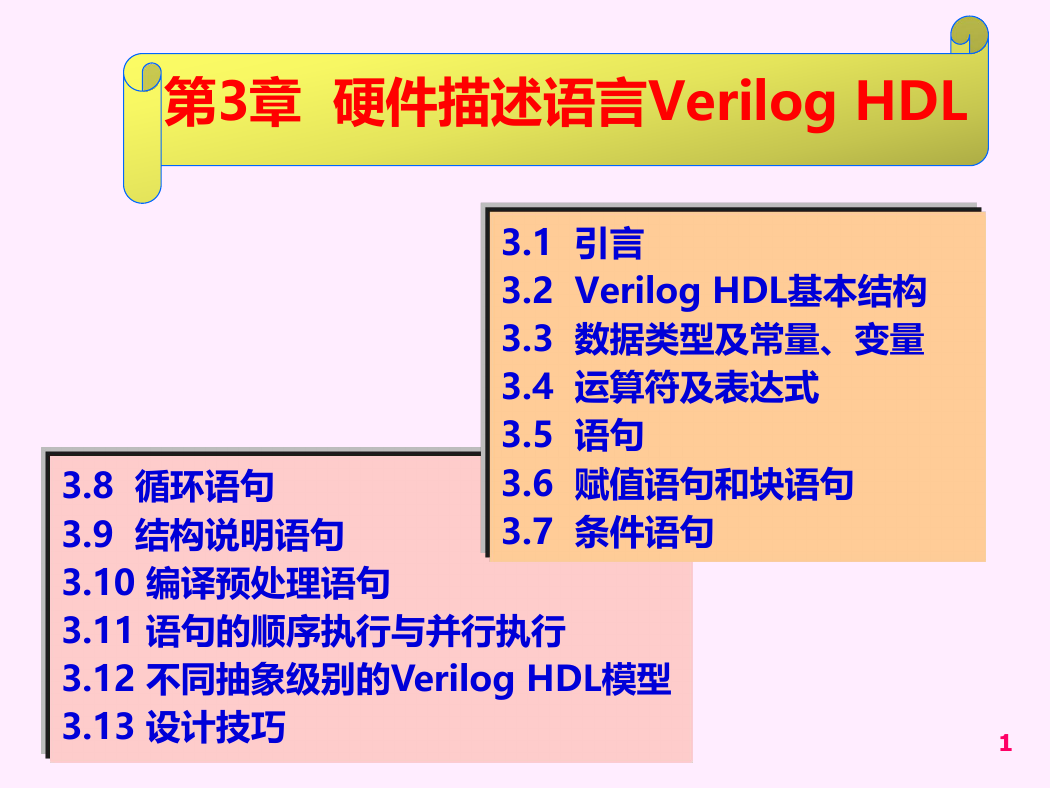

第3章 硬件描述语言Verilog HDL

3.1 引言

3.2 Verilog HDL基本结构

3.3 数据类型及常量、变量

3.4 运算符及表达式

3.5 语句

3.6 赋值语句和块语句

3.7 条件语句

3.8 循环语句

3.9 结构说明语句

3.10 编译预处理语句

3.11 语句的顺序执行与并行执行

3.12 不同抽象级别的Verilog HDL模型

3.13 设计技巧

1

�

3.1 引言

一、什么是Verilog HDL

二、Verilog HDL的发展历史

三、不同层次的Verilog HDL抽象

四、Verilog HDL的特点

2

�

3.1 引言

一、什么是Verilog HDL

§ Verilog HDL是一种用于数字逻辑电路设计的硬件描述

语言(Hradware Description Language ),可以用来进

行数字电路的仿真验证、时序分析、逻辑综合。

Ø 用Verilog HDL描述的电路设计就是该电路的Verilog

HDL模型。

Ø Verilog HDL 既是一种行为描述语言也是一种结构描

述语言。

§ 既可以用电路的功能描述,也可以用元器件及其之间的

连接来建立Verilog HDL模型。

3

�

3.1 引言

二、Verilog HDL的发展历史

§ 1983年,由GDA(GateWay Design Automation)公

司的Phil Moorby首创;

§ 1989年,Cadence公司收购了GDA公司;

§ 1990年, Cadence公司公开发表Verilog HDL;

§ 1995年,IEEE制定并公开发表Verilog HDL1364-

1995标准;

§ 1999年,模拟和数字电路都适用的Verilog标准公开

发表

4

�

3.1 引言

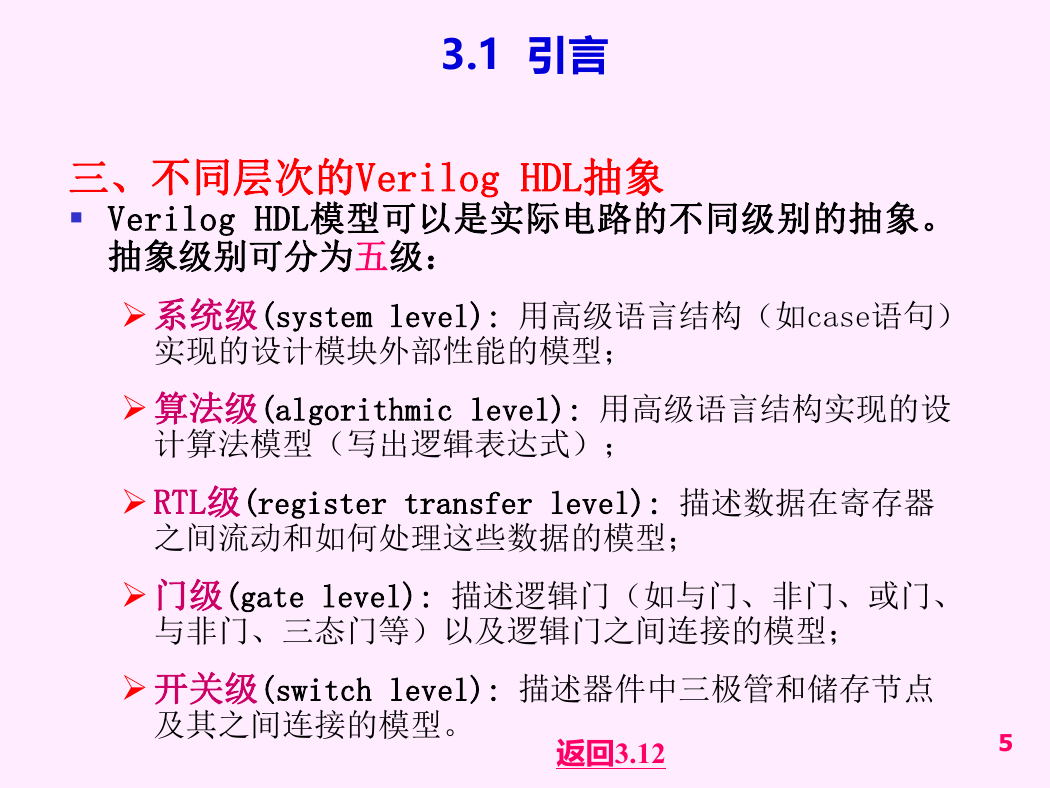

三、不同层次的Verilog HDL抽象

§ Verilog HDL模型可以是实际电路的不同级别的抽象。

抽象级别可分为五级:

Ø 系统级(system level): 用高级语言结构(如case语句)

实现的设计模块外部性能的模型;

Ø 算法级(algorithmic level): 用高级语言结构实现的设

计算法模型(写出逻辑表达式);

Ø RTL级(register transfer level): 描述数据在寄存器

之间流动和如何处理这些数据的模型;

Ø 门级(gate level): 描述逻辑门(如与门、非门、或门、

与非门、三态门等)以及逻辑门之间连接的模型;

Ø 开关级(switch level): 描述器件中三极管和储存节点

及其之间连接的模型。

返回3.12

5

�

3.1 引言

四、Verilog HDL的特点

§ 语法结构上的主要特点:

Ø 形式化地表示电路的行为和结构;

Ø 借用C语言的结构和语句;

与 C 语 言

非 常 相

似 !

Ø 可在多个层次上对所设计的系统加以描述,语言对设计规

模不加任何限制;

Ø 具有混合建模能力:一个设计中的各子模块可用不同级别

的抽象模型来描述;

Ø 基本逻辑门、开关级结构模型均内置于语言中,可直接调

用;

Ø 易创建用户定义原语(UDP,User Designed Primitive) 。

§ 易学易用,功能强

6

�

3.2 Verilog HDL基本结构

一、简单的Verilog HDL例子

二、Verilog HDL模块的结构

三、逻辑功能定义

四、关键字

五、标识符

六、编写Verilog HDL源代码的标

准

7

�

3.2 Verilog HDL基本结构

一、简单的Verilog HDL例子

[例3.2.1] 8位全加器

模块名(文件名)

module adder8 ( cout,sum,a,b,cin );

output cout;

output [7:0] sum;

input [7:0] a,b;

input cin;

assign {cout,sum}=a+b+cin;

endmodule

端口定义

// 输出端口声明

// 输入端口声明

功能描述

I/O说明

assign语句:无论右边表达式操作数何时发生变化,右边表达式都

会重新计算,并且在指定的延迟后给左边表达式赋值。

Ø 整个Verilog HDL程序嵌套在module和endmodule声明语句中。

Ø 每条语句相对module和endmodule最好缩进2格或4格!

Ø // …… 表示注释部分,一般只占据一行。对编译不起作用!

单行注释符

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc