Fast Fourier Transform v9.1

Table of Contents

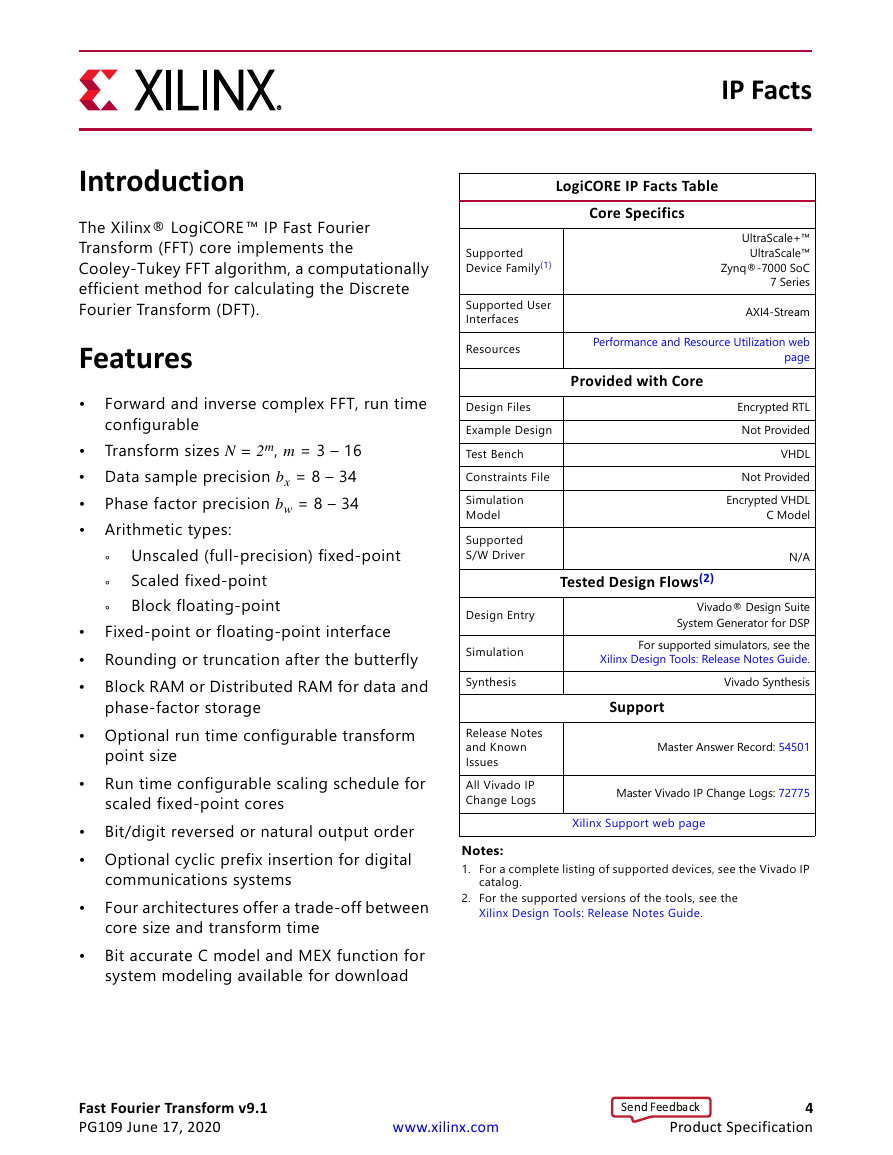

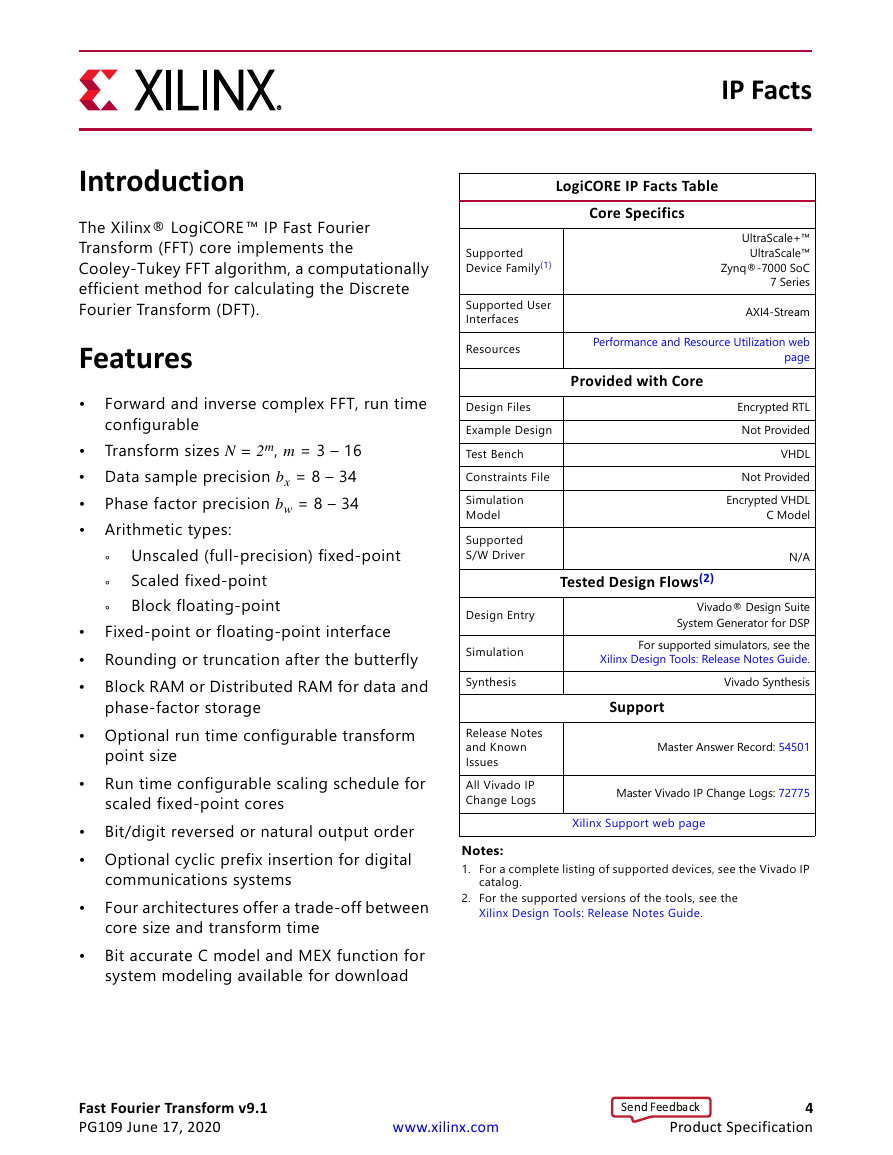

IP Facts

Ch. 1: Overview

Core Overview

Algorithm

Licensing and Ordering

Ch. 2: Product Specification

Resource Utilization

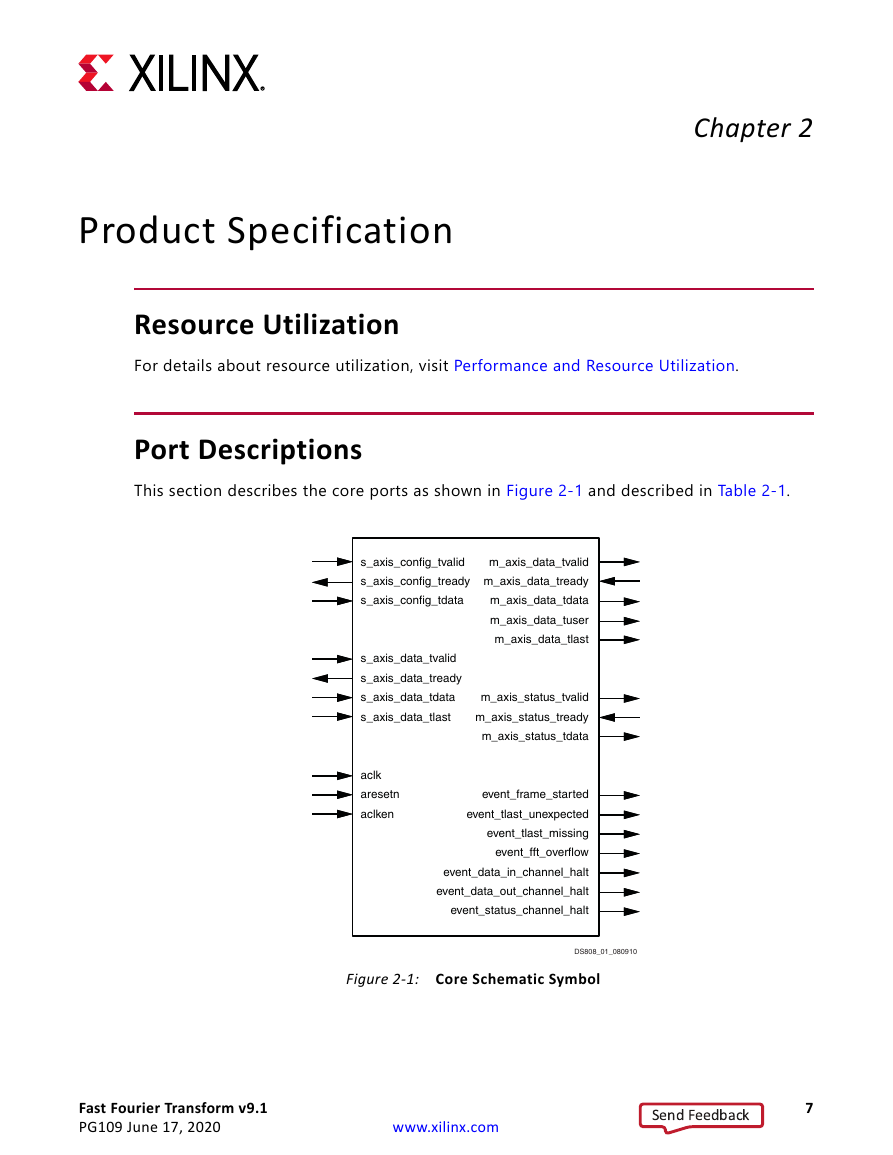

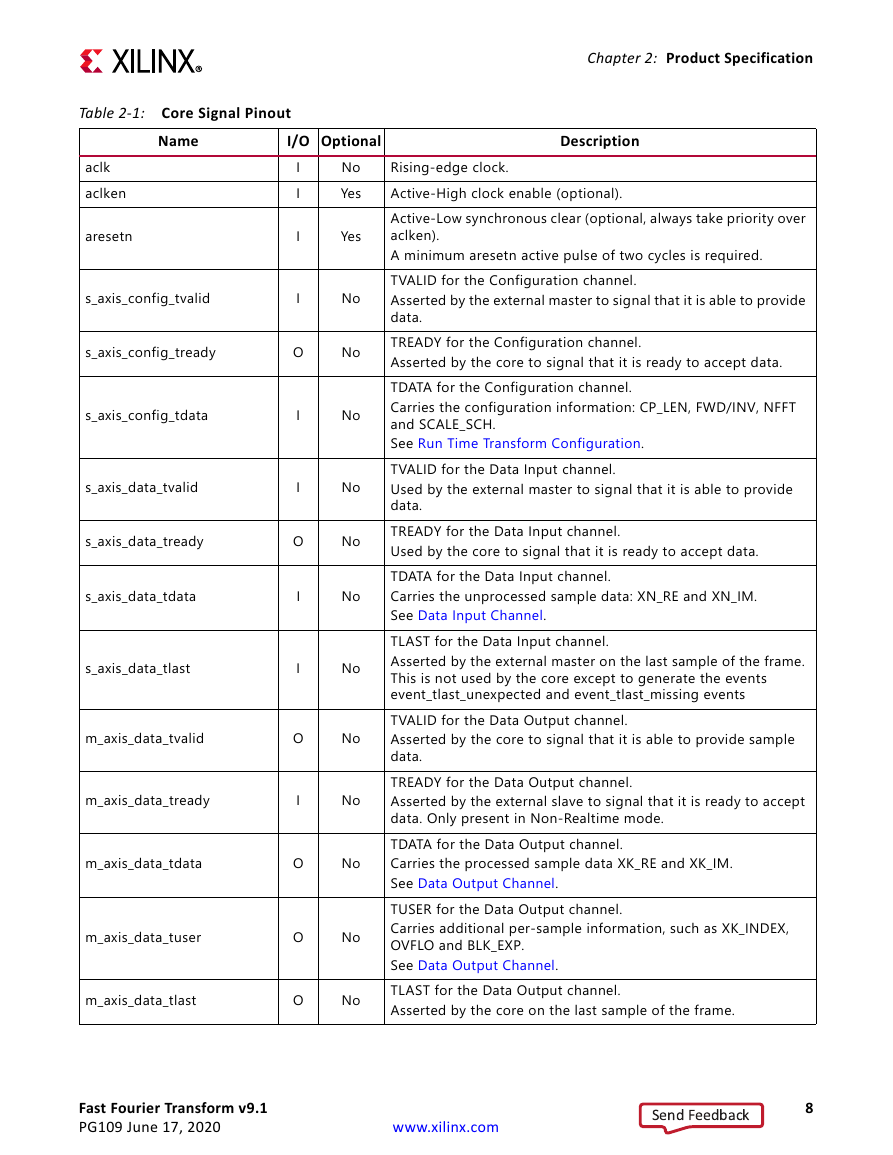

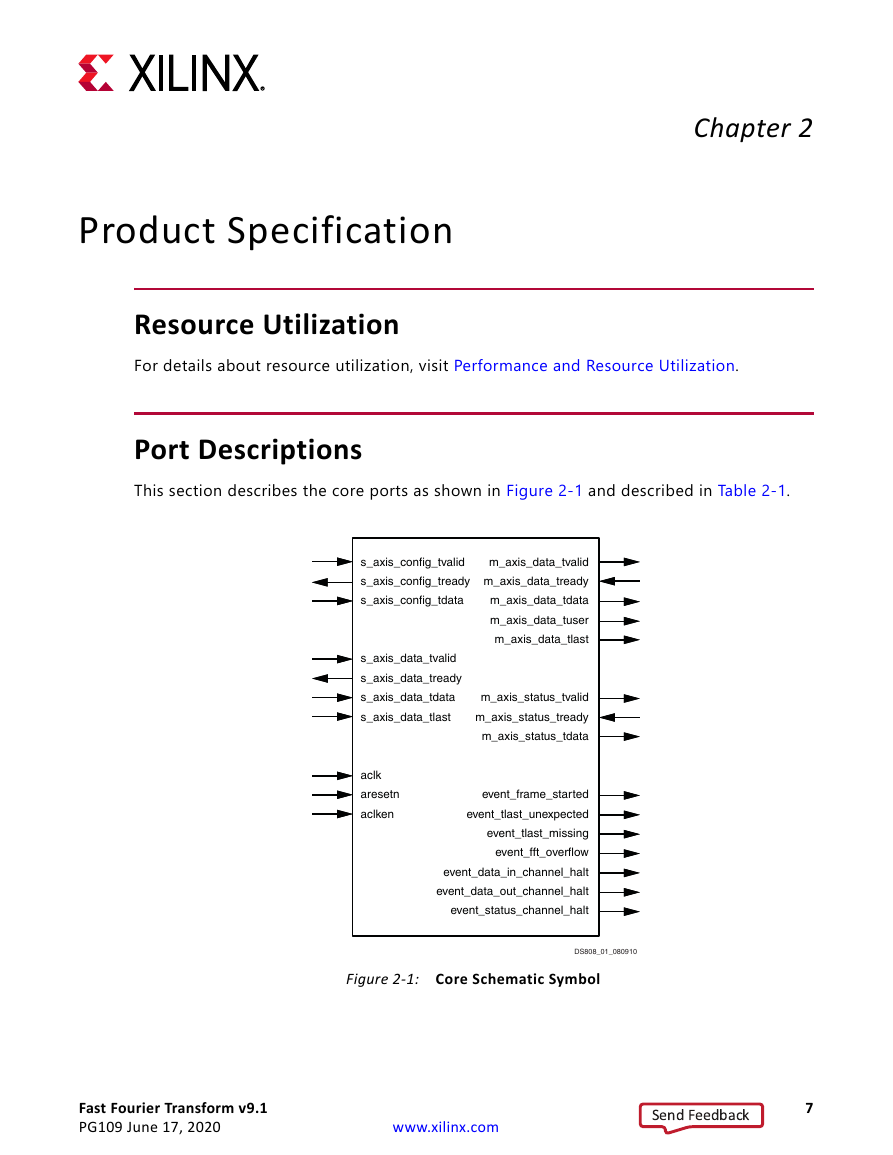

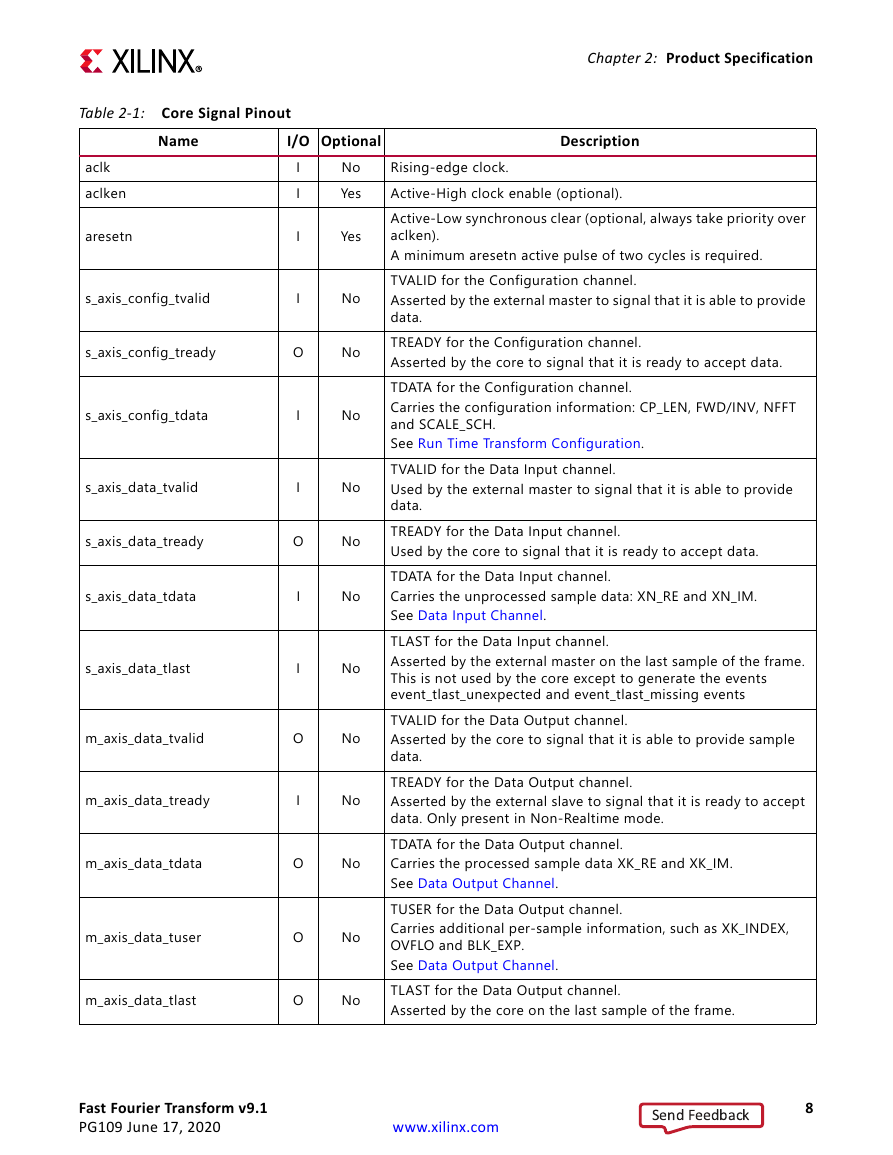

Port Descriptions

Ch. 3: Designing with the Core

Clocking

aclken (Clock Enable)

Resets

aresetn (Synchronous Clear)

Event Signals

event_frame_started

event_tlast_missing

event_tlast_unexpected

event_fft_overflow

event_data_in_channel_halt

event_data_out_channel_halt

event_status_channel_halt

AXI4-Stream Considerations

Basic Handshake

AXI Channel Rules

Configuration Channel

TDATA Fields

TDATA Format

TDATA Example

Data Input Channel

Pinout

TDATA Fields

TDATA Format

TDATA Example

Data Output Channel

Pinout

TDATA Fields

TDATA Format

TDATA Example

TUSER Fields

TUSER Format

TUSER Examples

Status Channel

Pinout

TDATA Fields

TDATA Format

TDATA Example

Theory of Operation

Finite Word Length Considerations

Floating-Point Considerations

Denormalized Numbers

NaNs and ± Infinity

Real-Valued Input Data

Rounding Implementation

Dynamic Range Characteristics

Architecture Options

Bit and Digit Reversal

Pipelined Streaming I/O

Radix-4 Burst I/O

Radix-2 Burst I/O

Radix-2 Lite Burst I/O

Run Time Transform Configuration

Transform Size

Forward/Inverse and Scaling Schedule

Cyclic Prefix Insertion

Transform Status

Overflow

Block Exponent

XK Index

Controlling the FFT Core

Transform Timing

Pipelined Streaming I/O with no Cyclic Prefix Insertion

Pipelined Streaming I/O with Cyclic Prefix Insertion

Burst I/O Architectures

Configuring the FFT

Applying a New Configuration While Idle

Applying a New Configuration While Streaming Frames

How Changing the Configuration Can Change Transform Timing

Ch. 4: Design Flow Steps

Customizing and Generating the Core

Configuration Tab

Implementation Tab

Detailed Implementation Tab

Information Tabs

User Parameters

Output Generation

System Generator for DSP Graphical User Interface

Tab 1: Basic

Tab 2: Advanced

Tab 3: Implementation

Constraining the Core

Required Constraints

Device, Package, and Speed Grade Selections

Clock Frequencies

Clock Management

Clock Placement

Banking

Transceiver Placement

I/O Standard and Placement

Simulation

Synthesis and Implementation

Ch. 5: C Model

Features

Overview

Unpacking and Model Contents

Installation

Software Requirements

FFT C Model Interface

Create a State Structure

Simulate the FFT Core

Destroy the State Structure

C Model Example Code

Compiling with the FFT C Model

Linux

Windows

FFT MATLAB Software MEX Function

Building the MEX Function

Installing and Running the MEX Function

MEX Function Example Code

Modeling Multichannel FFTs

Dependent Libraries

Ch. 6: Test Bench

Demonstration Test Bench

Using the Demonstration Test Bench

Demonstration Test Bench in Detail

Customizing the Demonstration Test Bench

Appx. A: Upgrading

Migrating to the Vivado Design Suite

Upgrading in the Vivado Design Suite

Parameter Changes

Port Changes

Functionality Changes

Latency Changes

Numerical Behavior Changes

Appx. B: Debugging

Finding Help on Xilinx.com

Documentation

Answer Records

Technical Support

Debug Tools

Vivado Design Suite Debug Feature

Reference Boards

C Model Reference

Simulation Debug

AXI4-Stream Interface Debug

Appx. C: Additional Resources and Legal Notices

Xilinx Resources

Documentation Navigator and Design Hubs

References

Revision History

Please Read: Important Legal Notices

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc