ModelSim仿真常用命令以及仿真脚本的编写 | 赛灵思中文社区

页码,1/3

ModelSim仿真常用命令以及仿真脚本的编写

在我们用ModelSim仿真的时候经常是修改一点一点修改代码,这样会造成一个无奈的操作循环:修改代码--->编译代码--->仿真设置--->进入仿真页面--->添加需要观察的波

形--->运行仿真。如果仿真结果不理想,还得需要重新修改代码,重复上述的操作。

计算机擅长做重复的事情,为什么不让计算机代劳呢?

我们可以参照Xilinx ISE是如何调用ModelSim进行仿真的,尤其是脚本的编写。

下面一个脚本是我用ISE10.1建立了一个AES256的工程,然后在调用ModelSim6.5的时候,ISE会生成这几个脚本文件,AES256_tb.fdo, AES256_tb_wave.fdo 和

AES256_tb.udo。

下面的代码是AES256_tb.fdo文件的内容。

1: vlib work #创建名字是work的库,这个仿真之前必须做的

2: vcom -explicit -93 "SBOX_ROM.vhd" #编译vhd代码

3: vcom -explicit -93 "Inv_SBOX_ROM.vhd"

4: vcom -explicit -93 "AES_package.vhd"

5: vcom -explicit -93 "subbytes.vhd"

6: vcom -explicit -93 "SBOX_ROM_reg.vhd"

7: vcom -explicit -93 "round_key_BRAM.vhd"

8: vcom -explicit -93 "Inv_subbytes.vhd"

9: vcom -explicit -93 "Keyexpansion_Yao.vhd"

10: vcom -explicit -93 "AES256_ENC_DEC.vhd"

11: vcom -explicit -93 "AES256_TOP.vhd"

12: vcom -explicit -93 "AES256_tb.vhd"

13: vsim -t 1ps -lib work AES256_tb #进入仿真设置,时间单位为1ps,库指定为work,AES256_tb就是指你的top层设计的名字

14: do {AES256_tb_wave.fdo} #执行*.fdo文件,用来添加信号和变量或者内部的寄存器到波形(WAVE)窗口

15: view wave #打开波形窗口

16: view structure #打开架构(structure)窗口

17: view signals #打开信号列表窗口

18: run 1000ns #运行1000ns

19: do {AES256_tb.udo} #运行用户定义的脚本

只要编译的时候没有出现语法错误或者是找不到定义的库文件等错误提示,一般会很容易的看到仿真的波形,而不用手动进行操作。这样方便了仿真的整个过程,而无需用

很多鼠标点击操作。

现在通过一个具体的实例来说明如何运用脚本来实现ModelSim的仿真。

工具版本:ISE10.1 ,ModelSim 6.5a

1. 创建ISE工程

首先通过ISE创建test.vhd 和test_tb.vhd文件并添加到工程中,这里不细说如何创建HDL源代码。

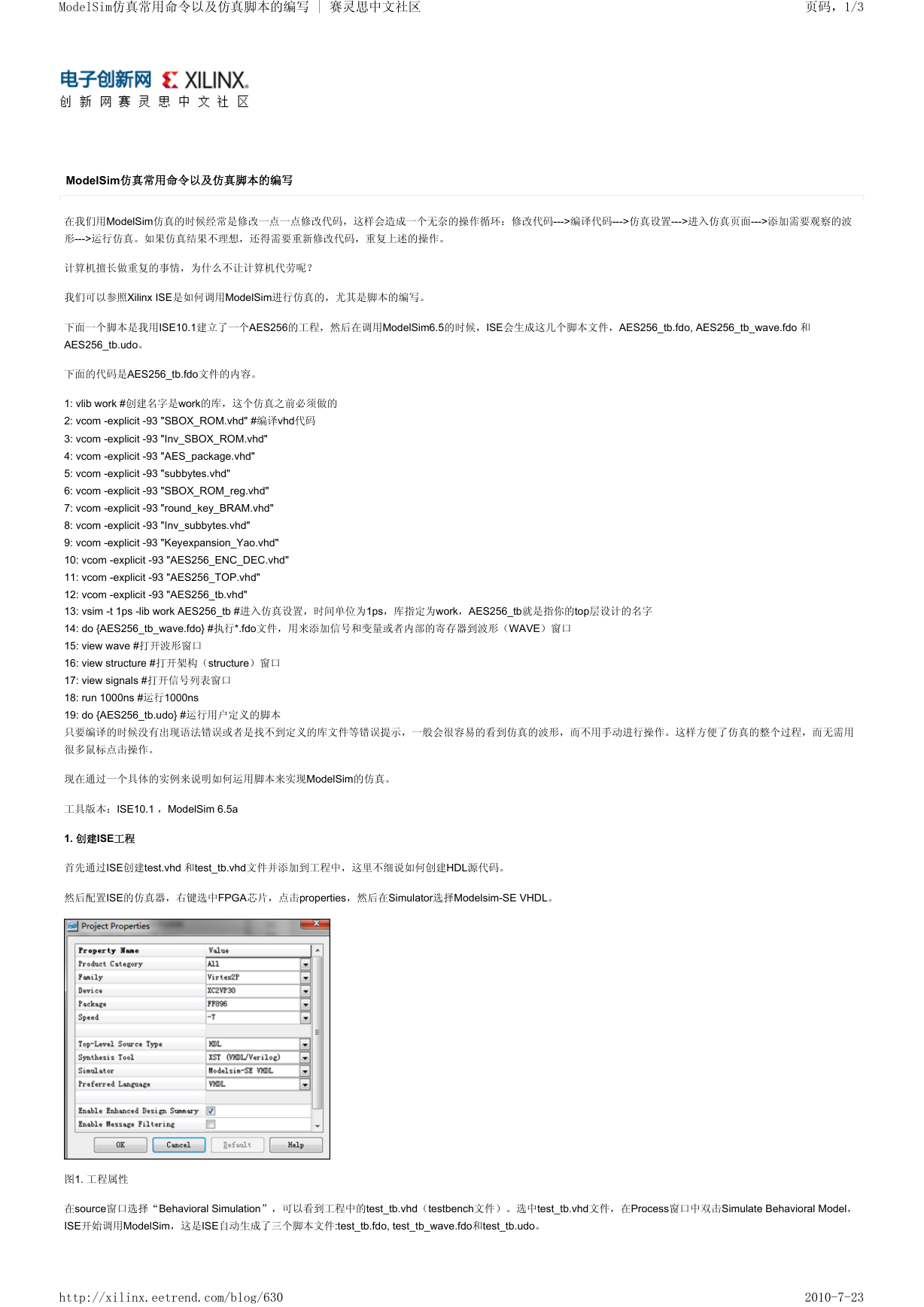

然后配置ISE的仿真器,右键选中FPGA芯片,点击properties,然后在Simulator选择Modelsim-SE VHDL。

图1. 工程属性

在source窗口选择“Behavioral Simulation”,可以看到工程中的test_tb.vhd(testbench文件)。选中test_tb.vhd文件,在Process窗口中双击Simulate Behavioral Model,

ISE开始调用ModelSim,这是ISE自动生成了三个脚本文件:test_tb.fdo, test_tb_wave.fdo和test_tb.udo。

http://xilinx.eetrend.com/blog/630

2010-7-23

�

ModelSim仿真常用命令以及仿真脚本的编写 | 赛灵思中文社区

页码,2/3

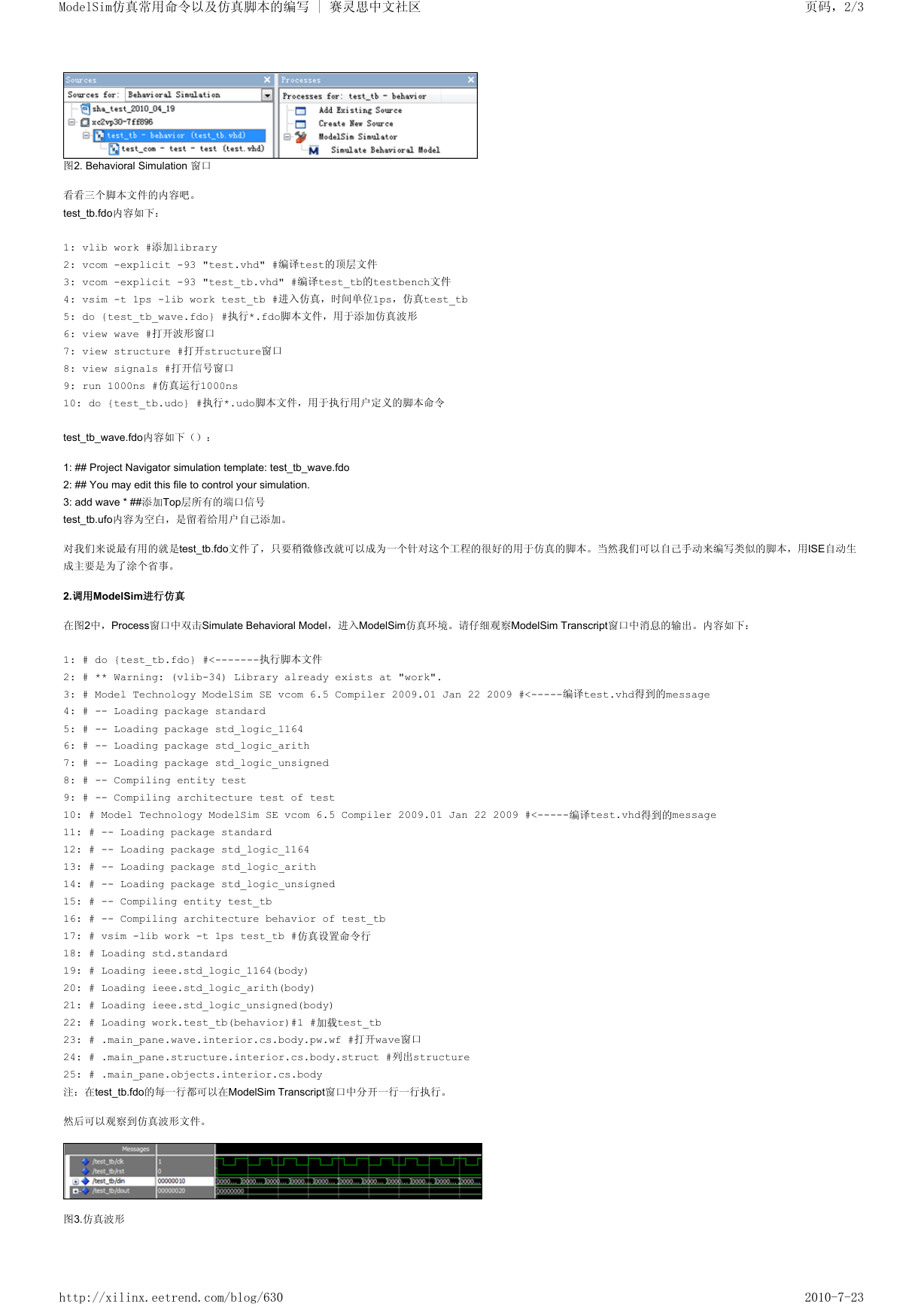

图2. Behavioral Simulation 窗口

看看三个脚本文件的内容吧。

test_tb.fdo内容如下:

1: vlib work #添加library

2: vcom -explicit -93 "test.vhd" #编译test的顶层文件

3: vcom -explicit -93 "test_tb.vhd" #编译test_tb的testbench文件

4: vsim -t 1ps -lib work test_tb #进入仿真,时间单位1ps,仿真test_tb

5: do {test_tb_wave.fdo} #执行*.fdo脚本文件,用于添加仿真波形

6: view wave #打开波形窗口

7: view structure #打开structure窗口

8: view signals #打开信号窗口

9: run 1000ns #仿真运行1000ns

10: do {test_tb.udo} #执行*.udo脚本文件,用于执行用户定义的脚本命令

test_tb_wave.fdo内容如下():

1: ## Project Navigator simulation template: test_tb_wave.fdo

2: ## You may edit this file to control your simulation.

3: add wave * ##添加Top层所有的端口信号

test_tb.ufo内容为空白,是留着给用户自己添加。

对我们来说最有用的就是test_tb.fdo文件了,只要稍微修改就可以成为一个针对这个工程的很好的用于仿真的脚本。当然我们可以自己手动来编写类似的脚本,用ISE自动生

成主要是为了涂个省事。

2.调用ModelSim进行仿真

在图2中,Process窗口中双击Simulate Behavioral Model,进入ModelSim仿真环境。请仔细观察ModelSim Transcript窗口中消息的输出。内容如下:

1: # do {test_tb.fdo} #<-------执行脚本文件

2: # ** Warning: (vlib-34) Library already exists at "work".

3: # Model Technology ModelSim SE vcom 6.5 Compiler 2009.01 Jan 22 2009 #<-----编译test.vhd得到的message

4: # -- Loading package standard

5: # -- Loading package std_logic_1164

6: # -- Loading package std_logic_arith

7: # -- Loading package std_logic_unsigned

8: # -- Compiling entity test

9: # -- Compiling architecture test of test

10: # Model Technology ModelSim SE vcom 6.5 Compiler 2009.01 Jan 22 2009 #<-----编译test.vhd得到的message

11: # -- Loading package standard

12: # -- Loading package std_logic_1164

13: # -- Loading package std_logic_arith

14: # -- Loading package std_logic_unsigned

15: # -- Compiling entity test_tb

16: # -- Compiling architecture behavior of test_tb

17: # vsim -lib work -t 1ps test_tb #仿真设置命令行

18: # Loading std.standard

19: # Loading ieee.std_logic_1164(body)

20: # Loading ieee.std_logic_arith(body)

21: # Loading ieee.std_logic_unsigned(body)

22: # Loading work.test_tb(behavior)#1 #加载test_tb

23: # .main_pane.wave.interior.cs.body.pw.wf #打开wave窗口

24: # .main_pane.structure.interior.cs.body.struct #列出structure

25: # .main_pane.objects.interior.cs.body

注:在test_tb.fdo的每一行都可以在ModelSim Transcript窗口中分开一行一行执行。

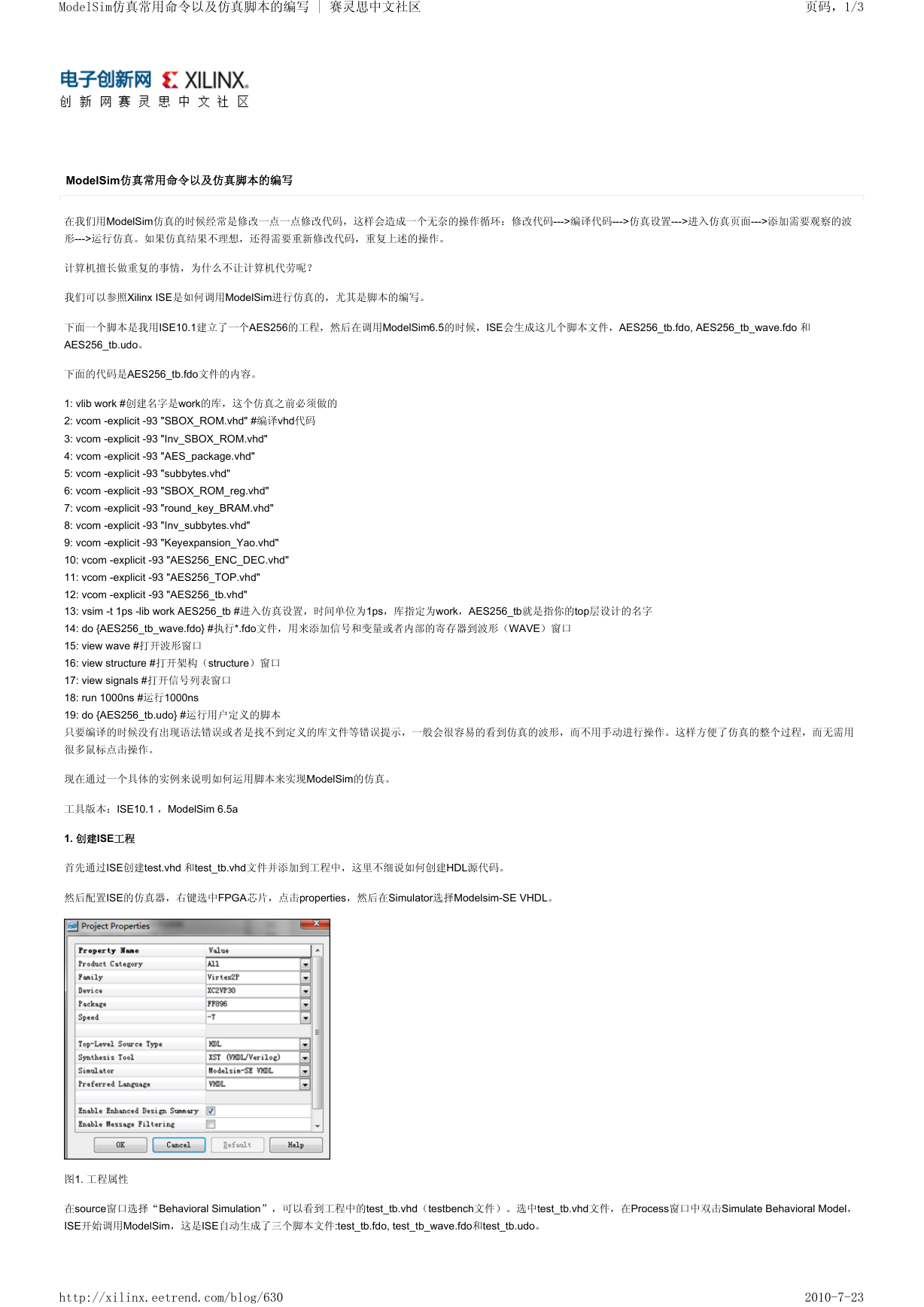

然后可以观察到仿真波形文件。

图3.仿真波形

http://xilinx.eetrend.com/blog/630

2010-7-23

�

ModelSim仿真常用命令以及仿真脚本的编写 | 赛灵思中文社区

页码,3/3

3. 调试代码

或许仿真出来的结果不是我们想要的,必须的修改代码,然后再仿真。那我们应该怎么办呢?

在trasncript窗口输入:

1: quit -sim #退出仿真

2: do test_tb.fdo #修改代码完成后重新执行该脚本进行仿真

在仿真的波形的时候,我们不仅仅希望看到Top层设计的端口信号的波形,还希望能观察到内部信号是如何变化的,所以我们在Sim窗口中找到内部的信号放到wave中进行

观察。但是如果我们重新运行当初test_tb.fdo文件,我们又再一次只能看到Top层设计的端口信号的波形,而内部信号的波形已经被删除。那我们应该如何保存和运用我们仿

真波形文件呢?

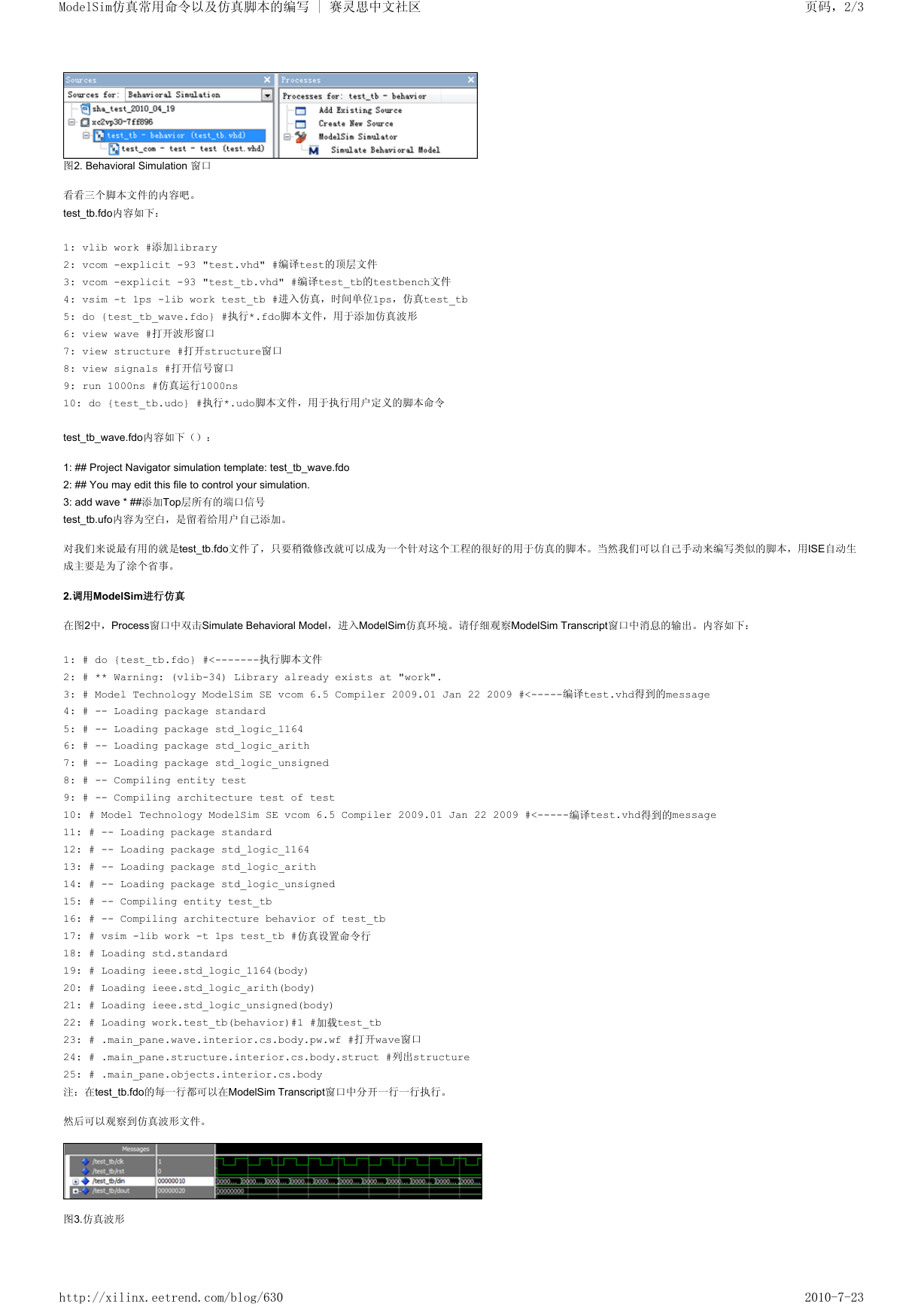

我现在需要观察内部的一个寄存器输出:tmp信号,见图4。Ctrl+S,保存波形文件。默认保存为工程目录下/wave.do,但是我们将用波形文件保存为test_tb_wave.fdo文

件,这样做的好处可以不用修改test_tb.fdo文件。

图4.内部信号观察

我们重新运行test_tb.fdo脚本文件之后,输出的波形是图4,而不是图3。

差不多常用的VHDL仿真命令都用上了,我相信这样做肯定会提高仿真的效率。如果想要熟悉更多的ModelSim的仿真命令,请查看ModelSim的用书手册。

欢迎交流!

yq000cn@gmail.com

Author:Yao Qi

Date:2010.04.24

Ref:

1. ModelSim SE Reference Manual,V6.4a

http://hornad.fei.tuke.sk/predmety/ncs/FPGA_Advantage_Documentation/mode...

“此文为“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛参赛作品

附件

1.png

2.png

3.png

4.png

大小

46.73 KB

28.45 KB

22.42 KB

36.48 KB

yq000cn's blog 要发表评论,请先登录 或 注册

ISE Modelsim 仿真 “安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛

星期二, 05/11/2010 - 16:03 — FPGA菜鸟

谢谢很好!

谢谢很好!

要发表评论,请先登录 或 注册

相关文章

“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛---基于FPGA的电机故障在线诊断方法

“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛------基于FPGA的Sigma-Delta数据采集系统

“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛------Spartan3硬件乘法器使用详解(5)

“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛------Spartan3硬件乘法器使用详解(4)

“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛------Spartan3硬件乘法器使用详解(3)

“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛------Spartan3硬件乘法器使用详解(2)

“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛------Spartan3硬件乘法器使用详解(1)

基于Virtex5的婴幼儿智能监护助理---“安富利杯”赛灵思FPGA设计技巧与应用创新博文

关于我们 | 法律声明 | 采购声明 | 电子创新网

©2006-2010 Xilinx. All rights reserved.

粤ICP备08115057号

http://xilinx.eetrend.com/blog/630

2010-7-23

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc