LogiCORE IP Digital

Pre-Distortion v6.0

Product Guide

PG076 October 16, 2012

�

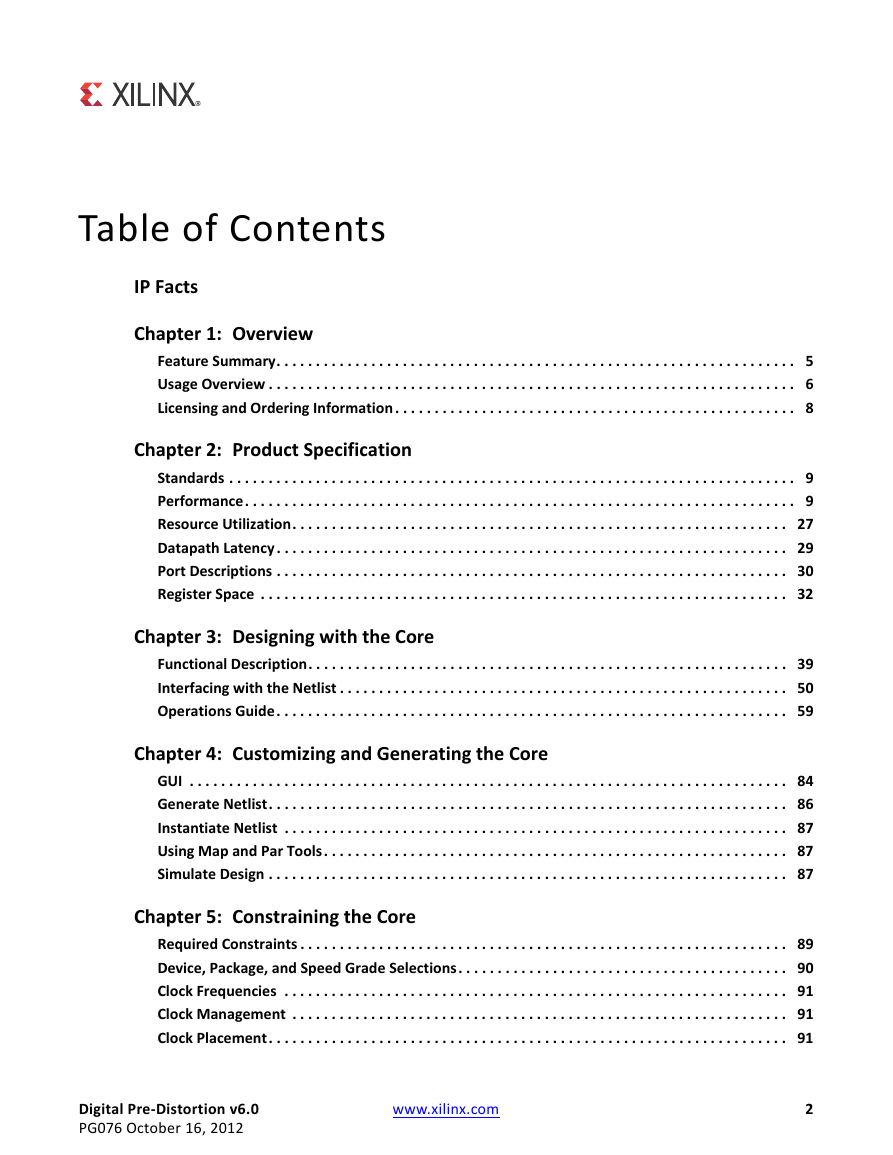

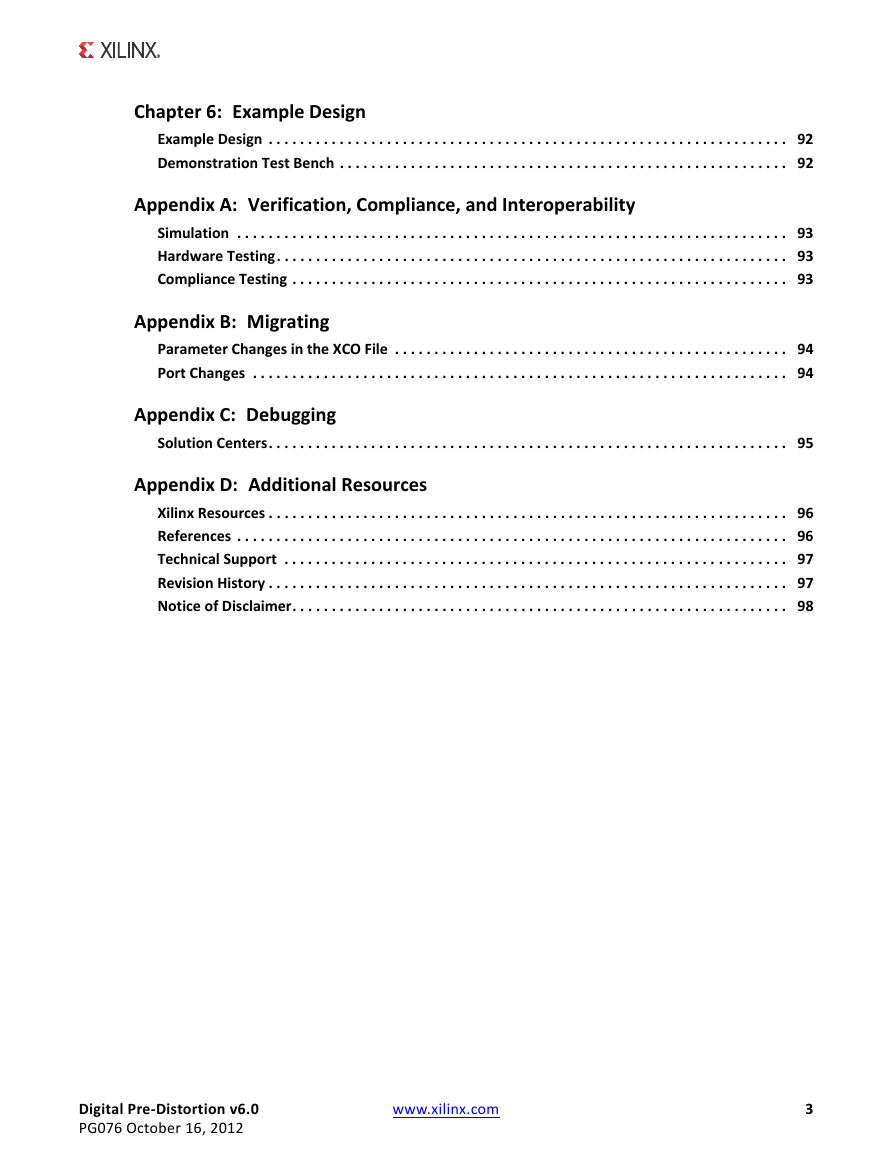

Table of Contents

IP Facts

Chapter 1: Overview

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Usage Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Licensing and Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Chapter 2: Product Specification

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Datapath Latency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Chapter 3: Designing with the Core

Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Interfacing with the Netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Operations Guide. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Chapter 4: Customizing and Generating the Core

GUI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Generate Netlist. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Instantiate Netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Using Map and Par Tools. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Simulate Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Chapter 5: Constraining the Core

Required Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Device, Package, and Speed Grade Selections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Clock Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Clock Placement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Digital Pre-Distortion v6.0

PG076 October 16, 2012

www.xilinx.com

2

�

Chapter 6: Example Design

Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Appendix A: Verification, Compliance, and Interoperability

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Hardware Testing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Compliance Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Appendix B: Migrating

Parameter Changes in the XCO File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Port Changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Appendix C: Debugging

Solution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Appendix D: Additional Resources

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Notice of Disclaimer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Digital Pre-Distortion v6.0

PG076 October 16, 2012

www.xilinx.com

3

�

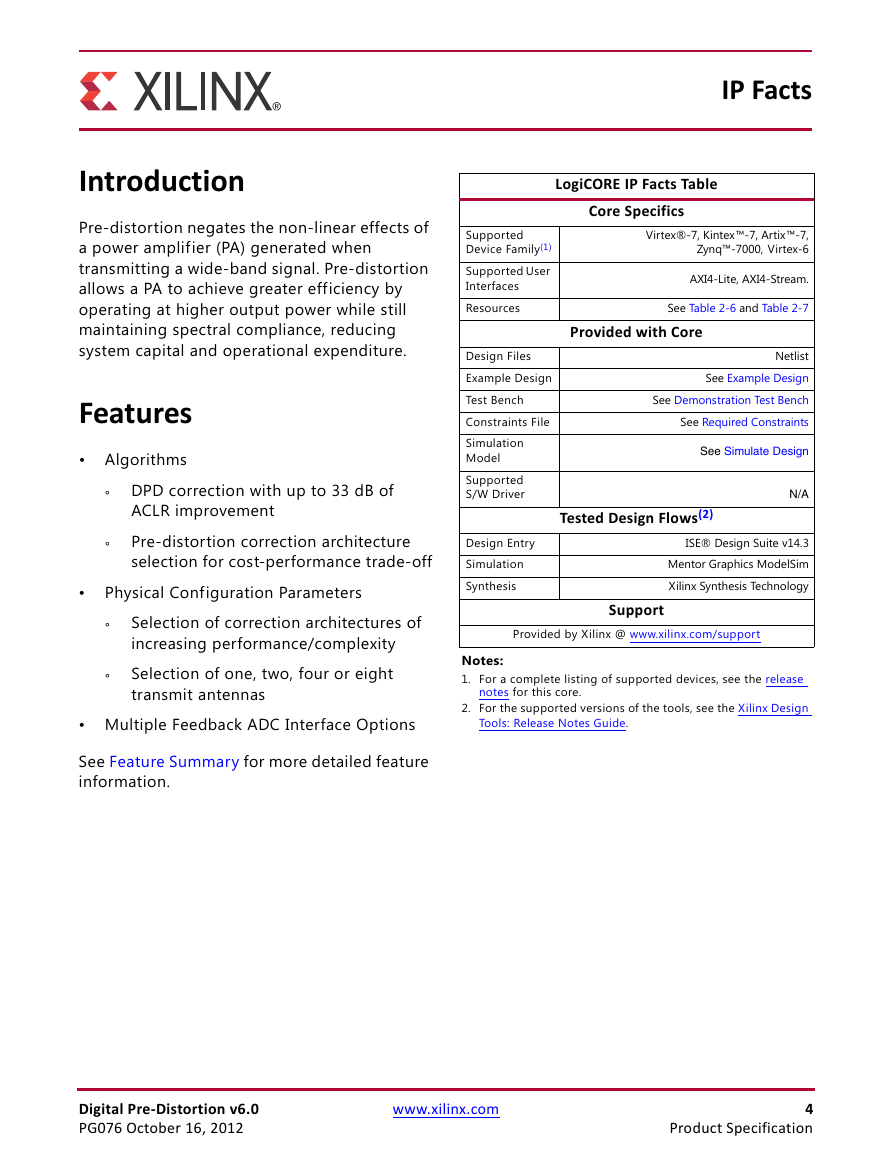

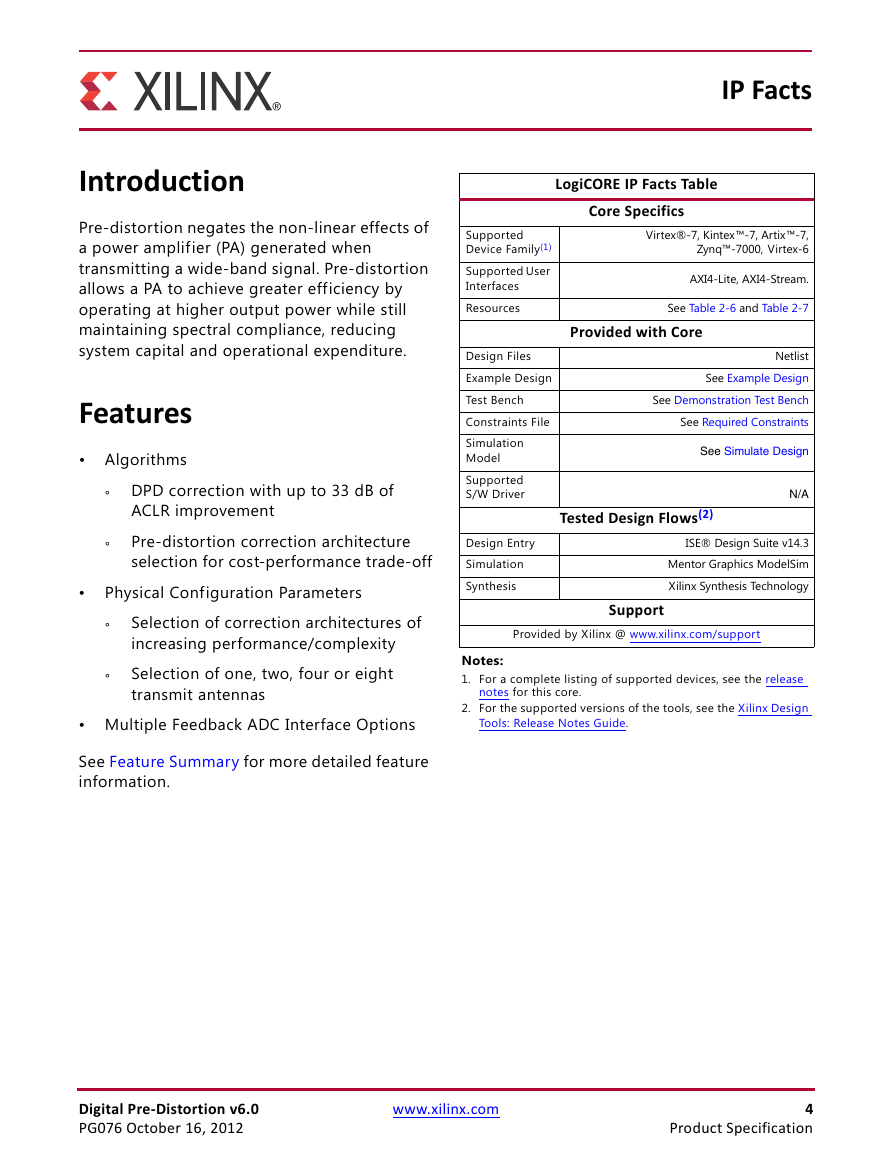

IP Facts

Supported

Device Family(1)

Supported User

Interfaces

Resources

Design Files

Example Design

Test Bench

Constraints File

Simulation

Model

Supported

S/W Driver

Design Entry

Simulation

Synthesis

LogiCORE IP Facts Table

Core Specifics

Virtex®-7, Kintex™-7, Artix™-7,

Zynq™-7000, Virtex-6

AXI4-Lite, AXI4-Stream.

See Table 2-6 and Table 2-7

Provided with Core

Netlist

See Example Design

See Demonstration Test Bench

See Required Constraints

See Simulate Design

Tested Design Flows(2)

N/A

ISE® Design Suite v14.3

Mentor Graphics ModelSim

Xilinx Synthesis Technology

Support

Provided by Xilinx @ www.xilinx.com/support

Notes:

1. For a complete listing of supported devices, see the release

notes for this core.

2. For the supported versions of the tools, see the Xilinx Design

Tools: Release Notes Guide.

Introduction

Pre-distortion negates the non-linear effects of

a power amplifier (PA) generated when

transmitting a wide-band signal. Pre-distortion

allows a PA to achieve greater efficiency by

operating at higher output power while still

maintaining spectral compliance, reducing

system capital and operational expenditure.

Features

• Algorithms

° DPD correction with up to 33 dB of

ACLR improvement

Pre-distortion correction architecture

selection for cost-performance trade-off

°

•

Physical Configuration Parameters

°

°

Selection of correction architectures of

increasing performance/complexity

Selection of one, two, four or eight

transmit antennas

• Multiple Feedback ADC Interface Options

See Feature Summary for more detailed feature

information.

Digital Pre-Distortion v6.0

PG076 October 16, 2012

www.xilinx.com

4

Product Specification

�

Chapter 1

Overview

Pre-distortion negates the non-linear effects of a power amplifier (PA) generated when

transmitting a wide-band signal. Pre-distortion allows a PA to achieve greater efficiency by

operating at higher output power while still maintaining spectral compliance, reducing

system capital and operational expenditure.

The solution is targeted for base stations used in third and fourth generation (3G/4G)

mobile technologies and beyond. It is a combination of hardware and embedded software

processes that between them realize pre-distortion correction along with features that

make for a fully engineered, practical, robust and self-contained solution. It is configurable

both in feature selection and in usage to support several clocking and resource

requirements.

Feature Summary

• Algorithms

° DPD correction with up to 33 dB of ACLR improvement

Pre-distortion correction architecture selection for cost-performance trade-off

°

° Options to support signal dynamics

TDD support with automatic data selection

°

° Quadrature modulator correction

PA saturation (overdrive) detection

Signal capture and analysis

Easy integration and evaluation using the Debug Interface utility [Ref 2]

°

Physical Configuration Parameters

•

°

°

°

°

Selection of correction architectures of increasing performance/complexity

Selection of one, two, four or eight transmit antennas

Clock to sample rate ratios from 0.5 to 4

°

° Optional Quadrature Modulation Correction (QMC) for either the transmitter or

feedback path receiver

Digital Pre-Distortion v6.0

PG076 October 16, 2012

www.xilinx.com

5

�

Chapter 1: Overview

° Optional hardware acceleration of coefficient estimation and signal alignment

Feedback ADC Interface Options

•

°

°

°

Real IF feedback signal sampled at twice the pre-distortion sample rate with

arbitrary IF frequency (optimal performance option)

Real IF feedback signal sampled at one times the pre-distortion sample rate with

arbitrary IF frequency

Zero-IF or Complex-IF baseband feedback signal sampled at one times the

pre-distortion sample rate with integrated QMC

° Optional feedback path support for buffered ADC support

DPD v6.0 supports two parallel TX and SRx input samples. This facilitates wider

pre-distortion bandwidths without a corresponding clock increase and is specified with a

clock to sample ratio of 0.5. This allows, for example, a data rate of 491.52 MSPS with a core

frequency of 245.76 MHz. In most respects this mode is provided transparently, with the

only requirement being that two data samples are provided to, and output from, the core

on every clock. Therefore, for the purposes of the AXI protocol, CPS=0.5 operates as a

CPS=1 case with a double-width data bus.

IMPORTANT: The fully accelerated mode (HWA=3) is not provided with the parallel data

implementation.

Usage Overview

This section briefly summarizes a sequence of events for successful incorporation of DPD

into a radio unit FPGA. Later sections provide the necessary detail.

Instantiation

1. The DPD component is added into your HDL code with appropriate clocks and

interfacing and the optional Debug Interface.

2. The DPD core is placed after Crest Factor Reduction (CFR) in the transmit chain.

3. The design is compiled.

4. A software environment for reading and writing the host interface is established. A

ready made environment is available using the MATLAB ® based Debug Interface for

quick evaluation on the target platform.

Digital Pre-Distortion v6.0

PG076 October 16, 2012

www.xilinx.com

6

�

Chapter 1: Overview

Basic Operational Checks

1. Read the addresses specified in Table 3-10 from the host interface; the stated default

values should be seen.

2. Execute (for example) the RESET_COEFFICIENTS control mode (see Host Interface and

Software Control Modes) to check termination with successful status.

Software Setup and Signal Validation

1. Set up DPD parameters as described in Setting DPD Parameters.

2. Read the DPD monitors detailed in Table 3-11.

3. Determine whether the values for the transmit and receive powers are as expected.

4. Perform required operations as detailed in Signal Analysis to ensure that the signal

inputs conform to the recommendations in Factors Influencing Expected Correction

Performance.

Pre-distortion Operations and Achieving Performance

1. Adjust DPD parameters and external setup with the aid of the single-stepping

2.

commands (see Single Stepping), external measurements, signal analysis operations and

interpretation of diagnostics as required.

In certain circumstances it is desirable to initialize the DPD and QMC coefficients using

a known good set of coefficients. The Xilinx DPD solution allows for the reading and

loading of coefficients to facilitate the initialization feature (see Reading and Loading

Coefficient Set).

Run the DCL (see Running the DCL) with diagnostic monitoring to experience the full

operational capability of DPD.

Digital Pre-Distortion v6.0

PG076 October 16, 2012

www.xilinx.com

7

�

Chapter 1: Overview

Licensing and Ordering Information

This Xilinx LogiCORE IP module is provided under the terms of the Xilinx Core License

Agreement. The module is shipped as part of the ISE® Design Suite. For full access to all

core functionalities in simulation and in hardware, you must purchase a license for the core.

Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the Digital Pre-Distortion product web page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual

Property page. For information on pricing and availability of other Xilinx LogiCORE IP

modules and tools, contact your local Xilinx sales representative.

Evaluation

An evaluation license is available for this core. The evaluation version operates in the same

way as the full version for several hours, depending on clock frequency. The data output

comprises a delayed version of the data input, after the evaluation period ends. The host

interface reports EVAL_LICENSE_TIMEOUT status value (see Table 3-9) when the hardware

times out. If you notice this behavior in hardware, it probably means you are using an

evaluation version of the core. The Xilinx tools warn that an evaluation license is being used

during netlist implementation. If a full license is installed, delete the old XCO file,

reconfigure and regenerate the core.

Digital Pre-Distortion v6.0

PG076 October 16, 2012

www.xilinx.com

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc