AXI Video Direct Memory Access v6.2

Table of Contents

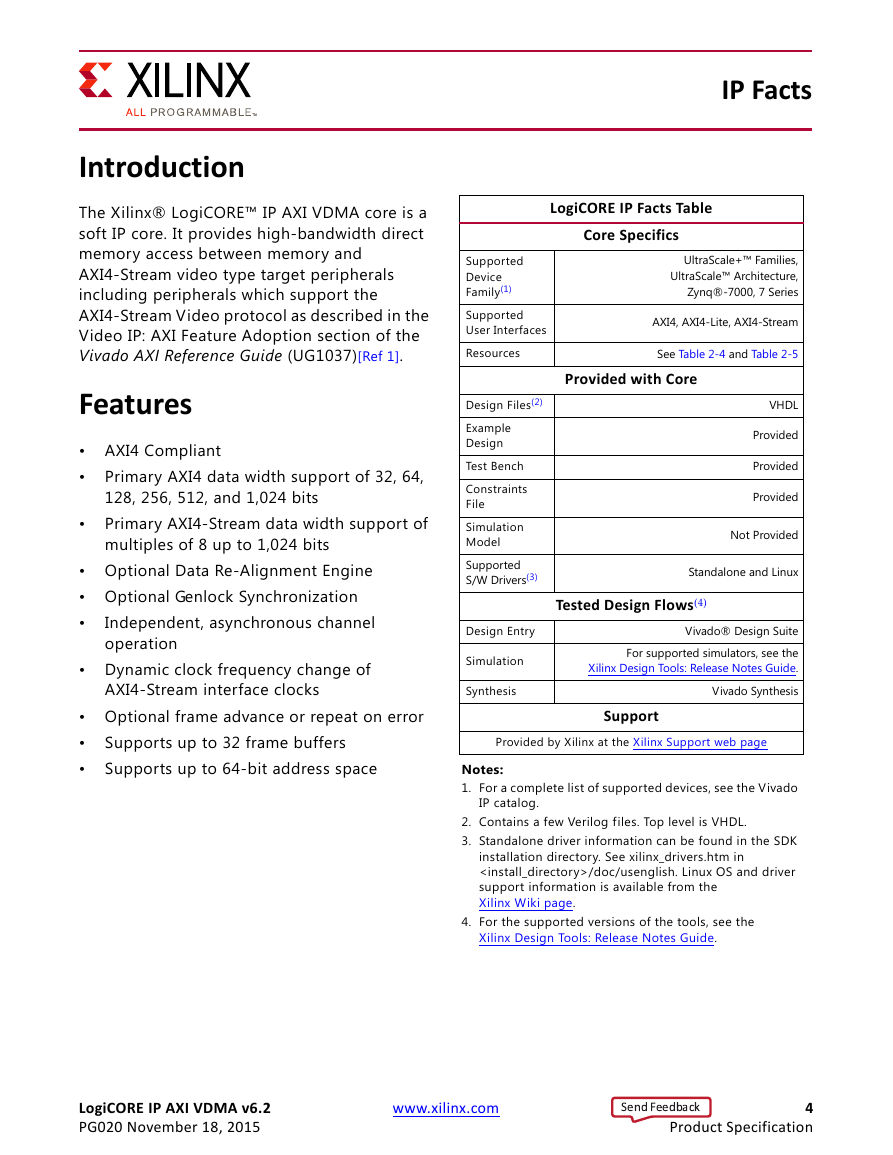

IP Facts

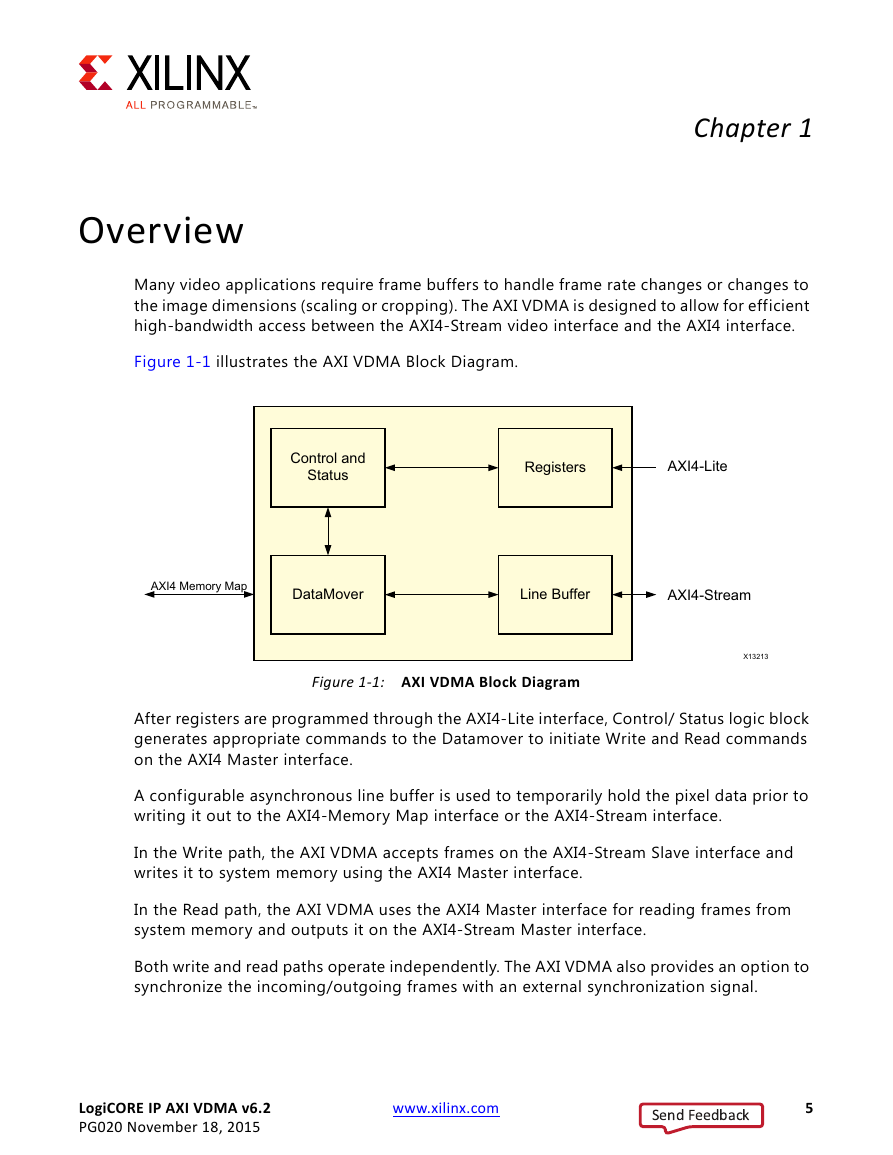

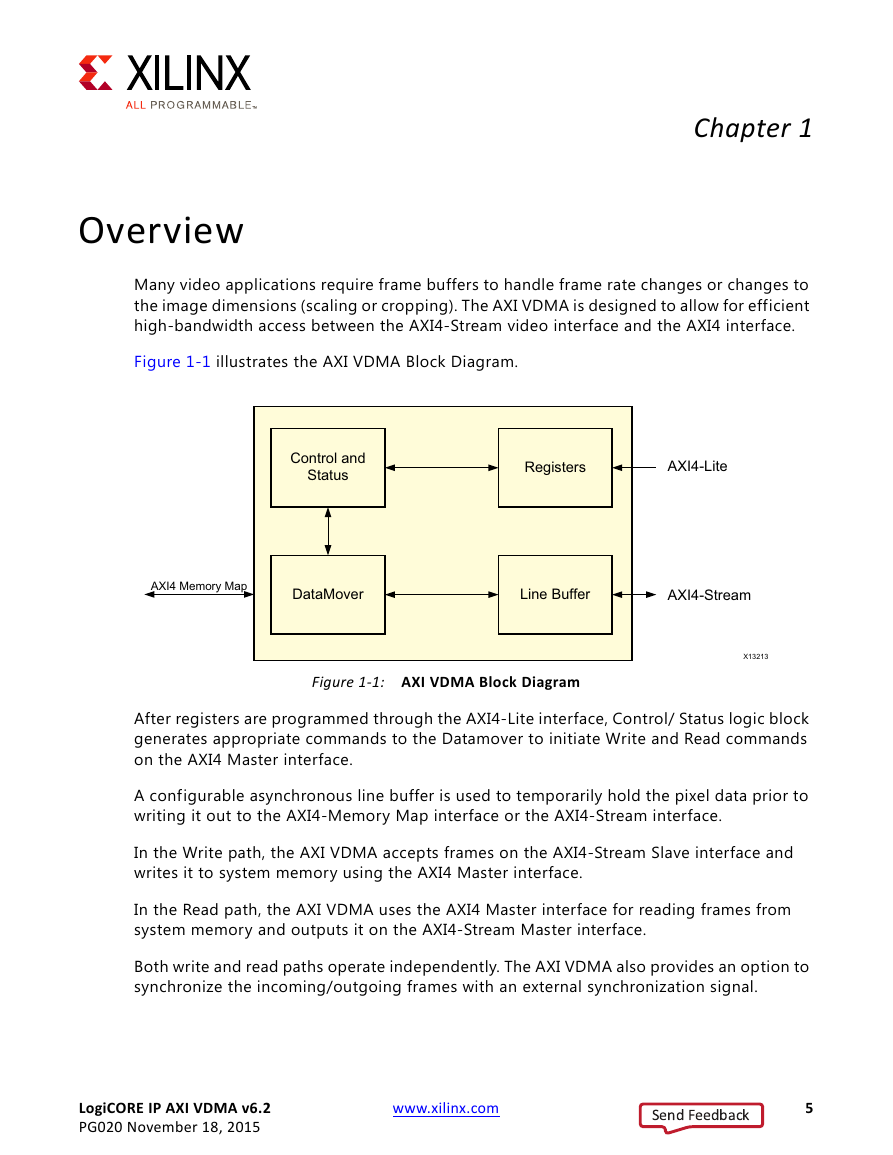

Ch. 1: Overview

Feature Summary

AXI4 Compliant

AXI4 Data Width

AXI4-Stream Data Width

32 Frame Buffers

Data Realignment Engine

Genlock Synchronization

Asynchronous Channels

Frame Sync Options

Dynamic Clock Frequency Change on AXI4-Stream Interface

Frame Advance or Repeat on Error

Applications

Unsupported Features

Licensing and Ordering Information

Ch. 2: Product Specification

Performance

Latency

Throughput

Resource Utilization

Port Descriptions

Timing Diagrams

Example Read (MM2S) Path Timing

Example Write (S2MM) Path Timing

Register Space

Endianess

AXI VDMA Register Address Map

Memory Map to Stream Register Details

Register Access Type Description

MM2S_VDMACR (MM2S VDMA Control Register – Offset 00h)

MM2S_VDMASR (MM2S VDMA Status Register – Offset 04h)

MM2S_REG_INDEX (MM2S Register Index – Offset 14h)

PARK_PTR_REG (Park Pointer Register – Offset 28h)

VDMA_VERSION (AXI VDMA Version Register – Offset 2Ch)

Stream to Memory Map Register Detail

S2MM_VDMACR (S2MM VDMA Control Register – Offset 30h)

S2MM_VDMASR (S2MM VDMA Status Register – Offset 34h)

S2MM_VDMA_IRQ_MASK (S2MM Error Interrupt Mask – Offset 3Ch)

S2MM_REG_INDEX (S2MM Register Index – Offset 44h)

MM2S Vertical Size (MM2S_VSIZE – Offset 0x50)

MM2S Horizontal Size (MM2S_HSIZE – Offset 0x54)

MM2S Frame Delay and Stride (MM2S_FRMDLY_STRIDE – Offset 0x58)

MM2S Start Addresses (Offsets 0x5C to Maximum Offset 0x98)

S2MM Vertical Size (S2MM_VSIZE – Offset 0xA0)

S2MM Horizontal Size (S2MM_HSIZE – Offset 0xA4)

S2MM Frame Delay and Stride (S2MM_FRMDLY_STRIDE – Offset 0xA8)

S2MM Start Addresses (Offsets 0xAC to Maximum Offset 0xE8)

Genlock Synchronization

Genlock Master

Genlock Slave

Dynamic Genlock Master

Dynamic Genlock Slave

Errors

VDMAIntErr

VDMASlvErr

VDMADecErr

Line and Frame Errors

Ch. 3: Designing with the Core

General Design Guidelines

Clocking

Frequency

Dynamic Resolution

Resets

Programming Sequence

Interrupts

Ch. 4: Design Flow Steps

Customizing and Generating the Core

Basic Options

Address Width (32-64)

Frame Buffers

Enable Write Channel

Memory Map Data Width

Enable Read Channel

Advanced Options

Enable Asynchronous Mode

Write Channel Options

Output Generation

Constraining the Core

Required Constraints

Device, Package, and Speed Grade Selections

Clock Frequencies

Clock Management

Clock Placement

Banking

Transceiver Placement

I/O Standard and Placement

Simulation

Synthesis and Implementation

Ch. 5: Example Design

Implementing the Example Design

Test Bench for the Example Design

Simulating the Example Design

Setting up the Simulation

Simulation Results

Ch. 6: General Use Cases

Appx. A: Migrating and Updating

Migrating to the Vivado Design Suite

Upgrading in the Vivado Design Suite

Appx. B: Debugging

Finding Help on Xilinx.com

Documentation

Answer Records

Technical Support

Vivado Design Suite Debug Feature

Hardware Debug

Appx. C: Additional Design Information

FRMPTR_STS (MM2S and S2MM Current Frame Pointer Status – Offset 24h)

S2MM HSIZE Status Register S2MM_HSIZE_STATUS (offset 0xF0h)

S2MM VSIZE Status Register S2MM_VSIZE_STATUS (offset 0xF4h)

Appx. D: Frame Pointers Gray Code Outputs

Appx. E: Additional Resources and Legal Notices

Xilinx Resources

References

Revision History

Please Read: Important Legal Notices

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc