FPGA 课程设计报告

(V1.0)

题目:

班级:

学号:

姓名:

地点:

可配置脉冲发生器

XXXX

XXXX

XXXX

电科实验室

2009 年 12 月 14 日

�

1. 技术规范

1.1. 概述

该技术规范使设计按照合理和规范的流程进行,主要涉及电路的输入输出引脚说明、功

能说明、关键时序说明等。

1.2. 输入输出引脚说明

序

号

1

2

3

4

5

引脚名称

输入/输出 电平

说明

Reset

输入

TTL

输入

Clk_50MHz

Duty_Cycle[7:0] 输入

输入

Cycle[1:0]

TTL

TTL

TTL

pulse_out

输出

TTL

复位信号。高电平有效;高电平时复位整个

系统,低电平时系统正常工作

系统 50MHz 时钟输入

占空比控制信号(1~255)表示 1/256~255/256

周期控制信号(00 表示 40ms、01 表示 80ms、

10 表示 120ms、11 表示 400ms)

可变周期(40ms、80ms、120ms、400ms)、

可变占空比(1/256~255/256)脉冲输出

1.3. 功能说明

复位信号 Reset 有效时(高电平),复位整个系统。

复位信号 Reset 低电平时,系统接收外部时钟 50MHz 输入,输出端 pulse_out 能够产

生受 Cycle[1:0]控制的 4 种不同的周期(40ms、80ms、120ms、400ms),每种周期下

可接受 Duty_Cycle[7:0]输入的 255 种可选占空比(1/256~255/256)。

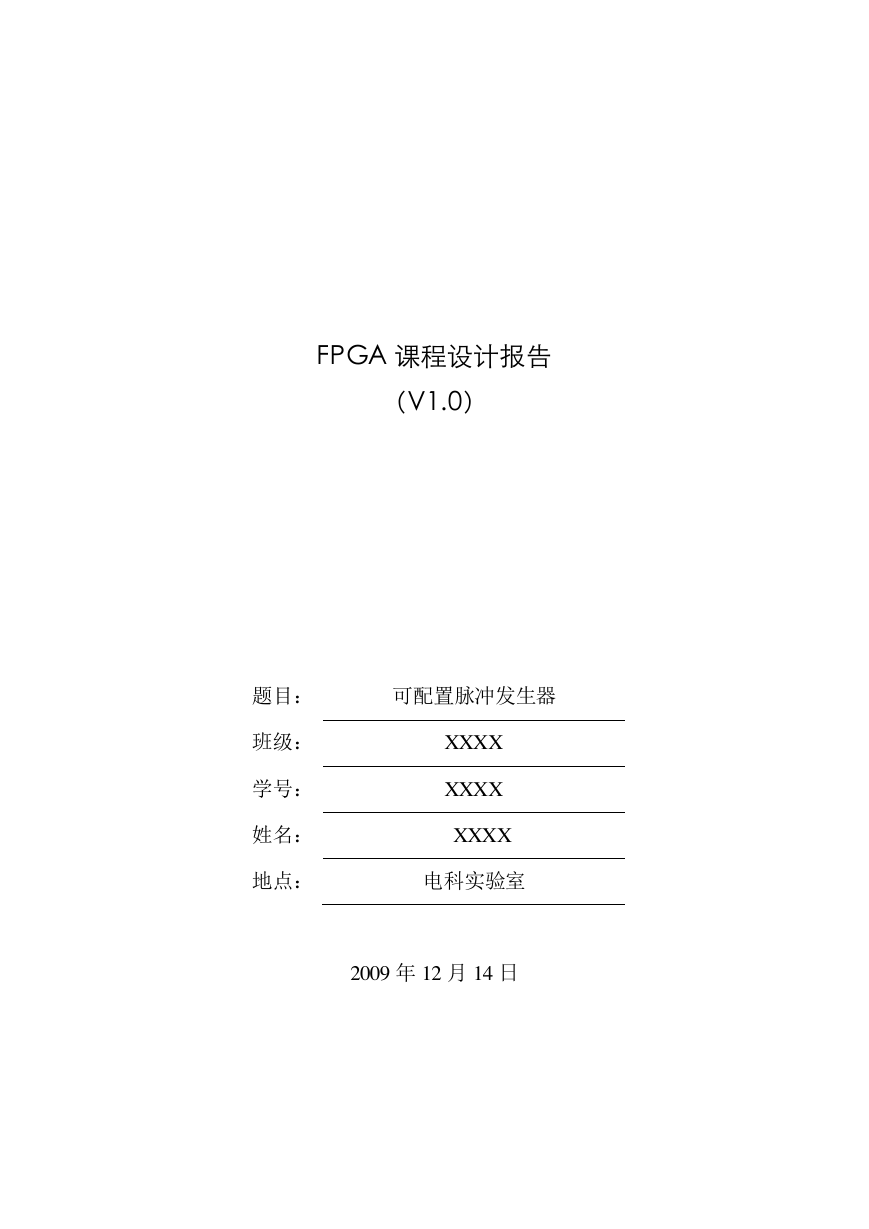

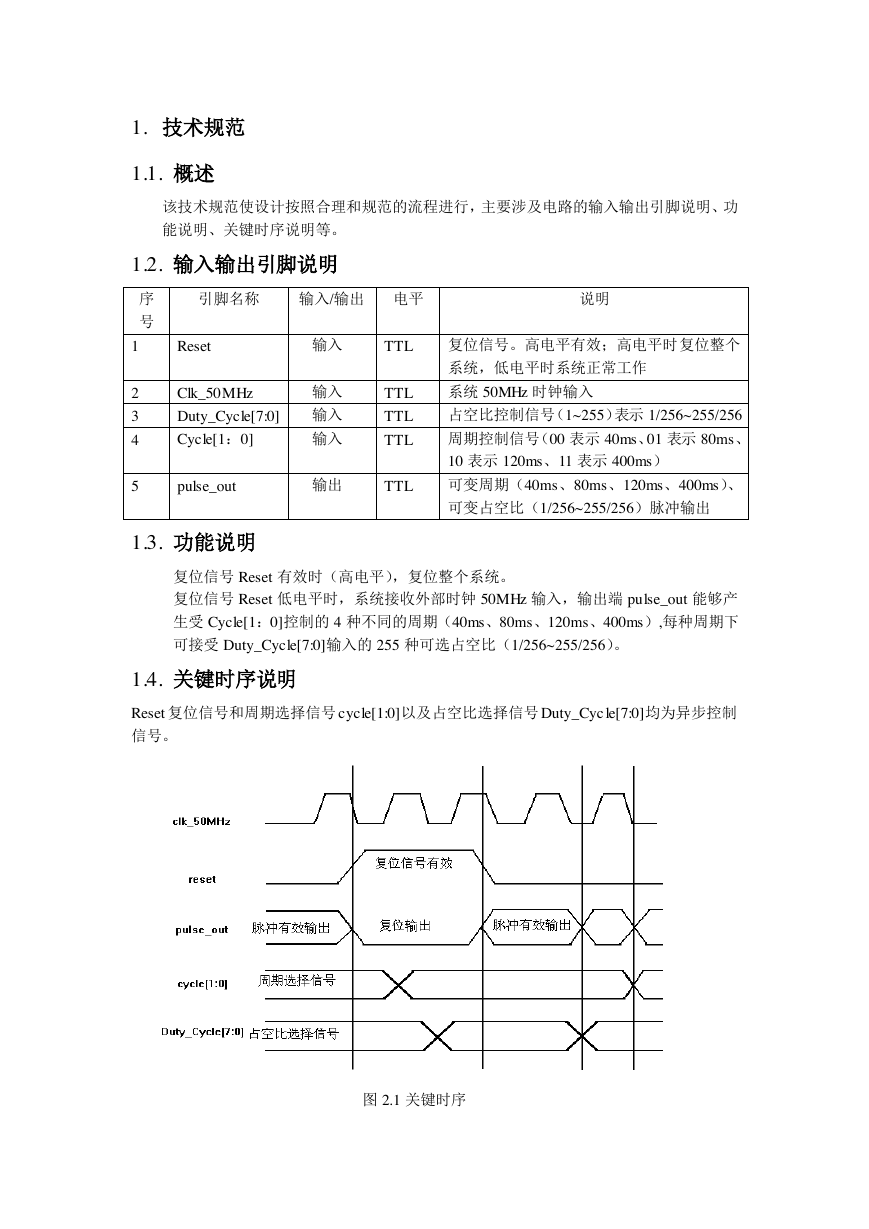

1.4. 关键时序说明

Reset 复位信号和周期选择信号 cycle[1:0]以及占空比选择信号 Duty_Cyc le[7:0]均为异步控制

信号。

图 2.1 关键时序

�

2. 总体设计方案

2.1 概述

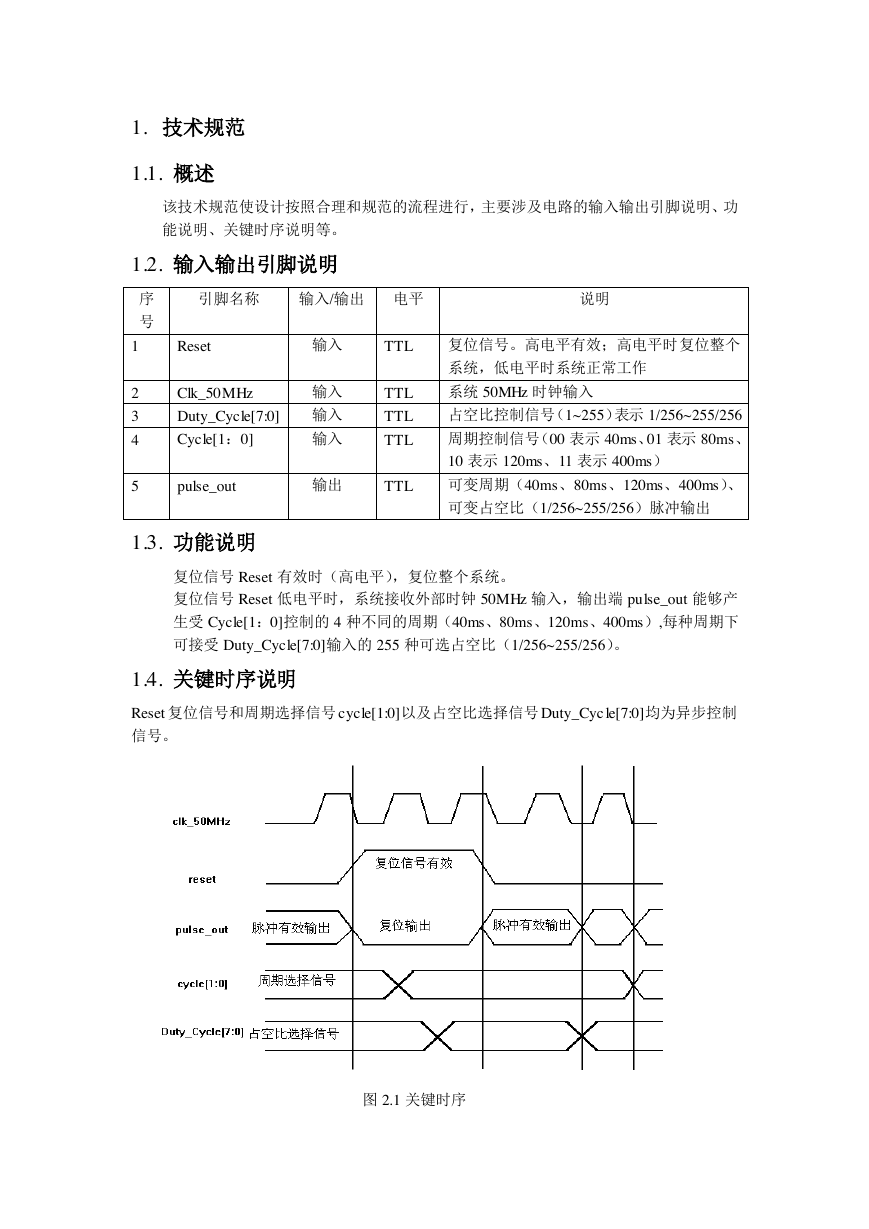

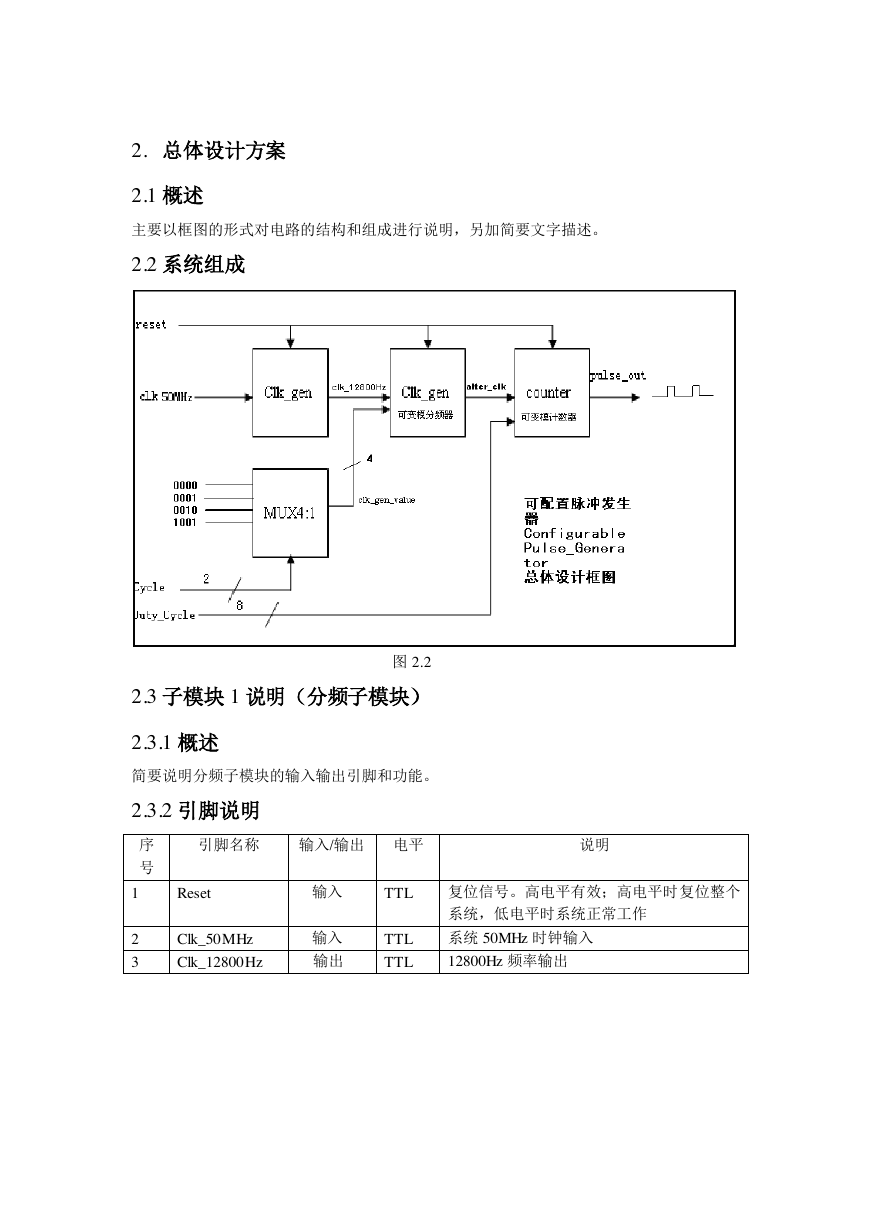

主要以框图的形式对电路的结构和组成进行说明,另加简要文字描述。

2.2 系统组成

2.3 子模块 1 说明(分频子模块)

图 2.2

2.3.1 概述

简要说明分频子模块的输入输出引脚和功能。

2.3.2 引脚说明

序

号

1

2

3

引脚名称

输入/输出 电平

说明

Reset

输入

TTL

Clk_50MHz

Clk_12800Hz

输入

输出

TTL

TTL

复位信号。高电平有效;高电平时复位整个

系统,低电平时系统正常工作

系统 50MHz 时钟输入

12800Hz 频率输出

�

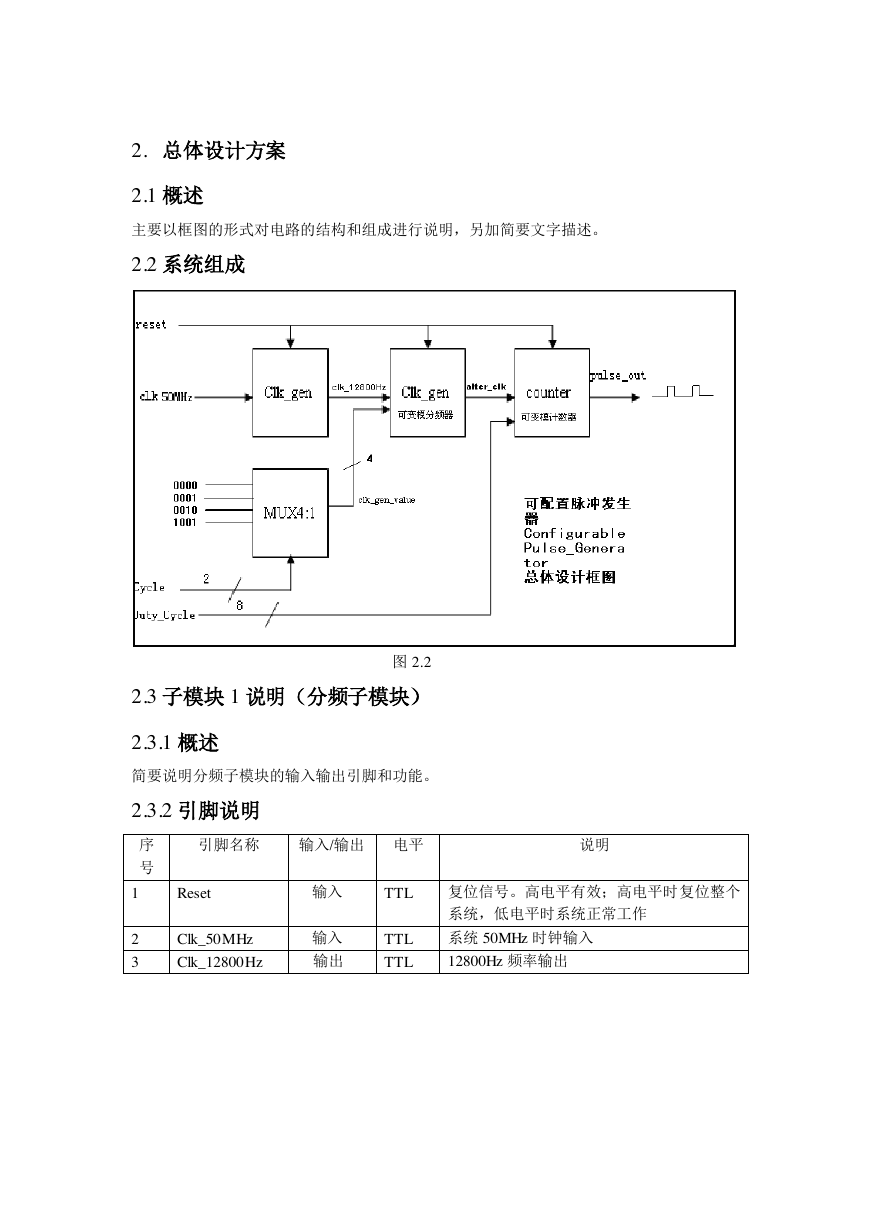

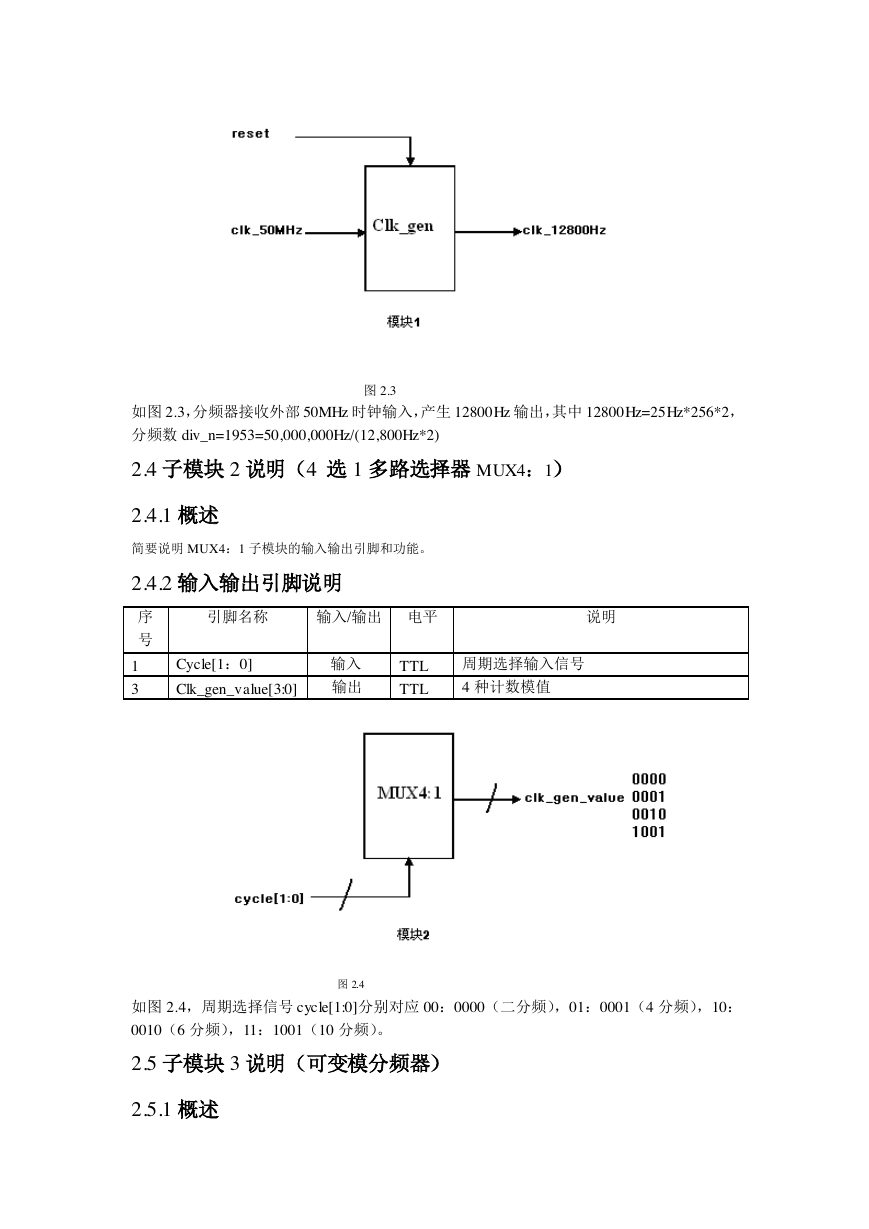

图 2.3

如图 2.3,分频器接收外部 50MHz 时钟输入,产生 12800Hz 输出,其中 12800Hz=25Hz*256*2,

分频数 div_n=1953=50,000,000Hz/(12,800Hz*2)

2.4 子模块 2 说明(4 选 1 多路选择器 MUX4:1)

2.4.1 概述

简要说明 MUX4:1 子模块的输入输出引脚和功能。

2.4.2 输入输出引脚说明

序

号

1

3

引脚名称

输入/输出 电平

说明

Cycle[1:0]

输入

Clk_gen_value[3:0] 输出

TTL 周期选择输入信号

TTL

4 种计数模值

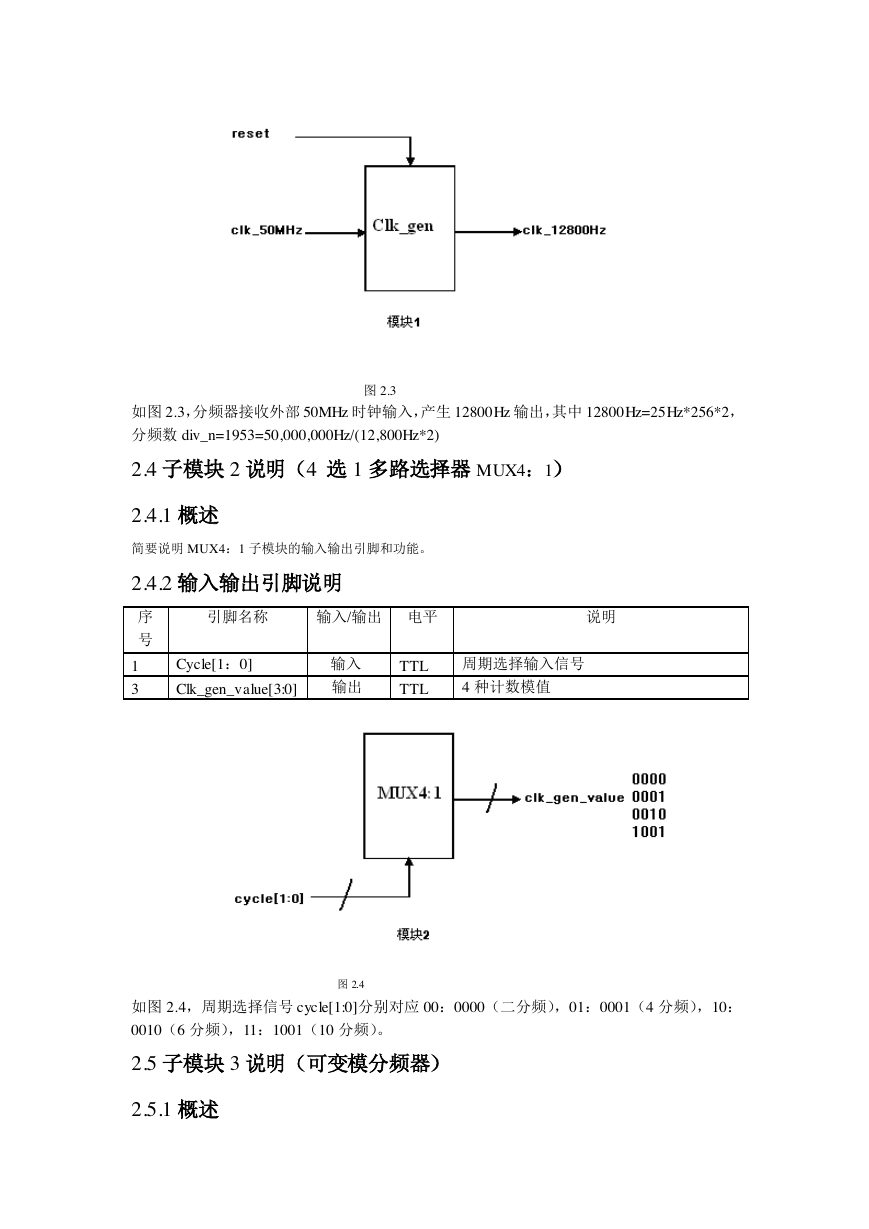

图 2.4

如图 2.4,周期选择信号 cycle[1:0]分别对应 00:0000(二分频),01:0001(4 分频),10:

0010(6 分频),11:1001(10 分频)。

2.5 子模块 3 说明(可变模分频器)

2.5.1 概述

�

简要说明可变分频器子模块的输入输出引脚和功能。

2.5.2 输入输出引脚说明

序

号

1

2

3

4

引脚名称

输入/输

电平

说明

Reset

出

输入

Clk_gen_value[3:0] 输入

输入

输出

Clk_12800Hz

Alter_clk

TTL 复位信号。高电平有效;高电平时复位整

个系统,低电平时系统正常工作

TTL 可变计数器模值

12800Hz 频率输入

TTL

TTL 可变频率

图 2.5

如图 2.5 置入不同的分频模值(0000,0001,0010,1001)可以产生不同的频率(25Hz,12.5Hz,

8.3Hz,2.5Hz)

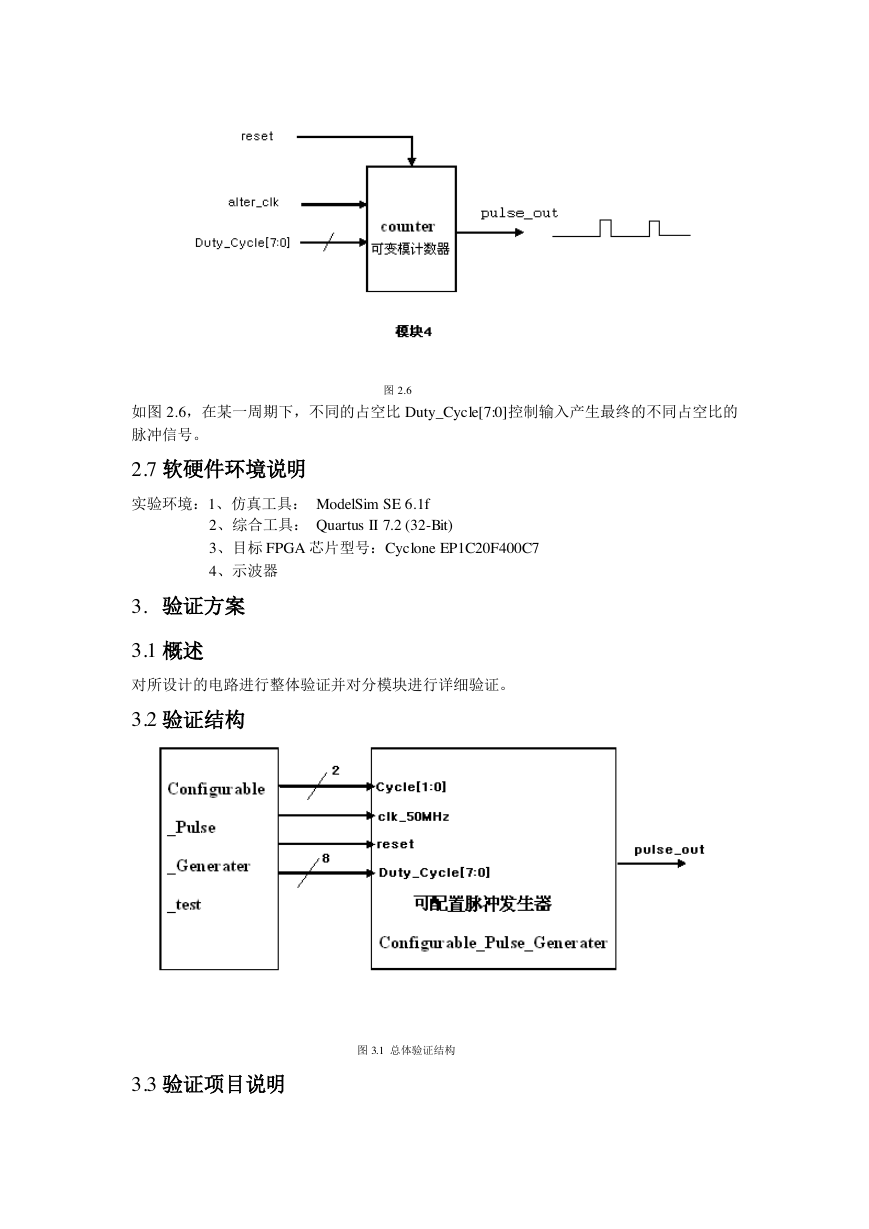

2.6 子模块 4 说明(可变模计数器)

2.6.1 概述

简要说明可变计数器子模块的输入输出引脚和功能。

2.6.2 输入输出引脚说明

引脚名称

输入/输出 电平

说明

Reset

输入

TTL

输入

Alter_clk

Duty_Cycle[7:0] 输入

输出

Pulse_out

TTL

TTL

TTL

复位信号。高电平有效;高电平时复位整个

系统,低电平时系统正常工作

可变频率(40ms、80ms、120ms、400ms)

可变占空比输入(1~255)

可变周期(40ms、80ms、120ms、400ms)、

可变占空比(1/256~255/256)脉冲输出

序

号

1

2

3

4

�

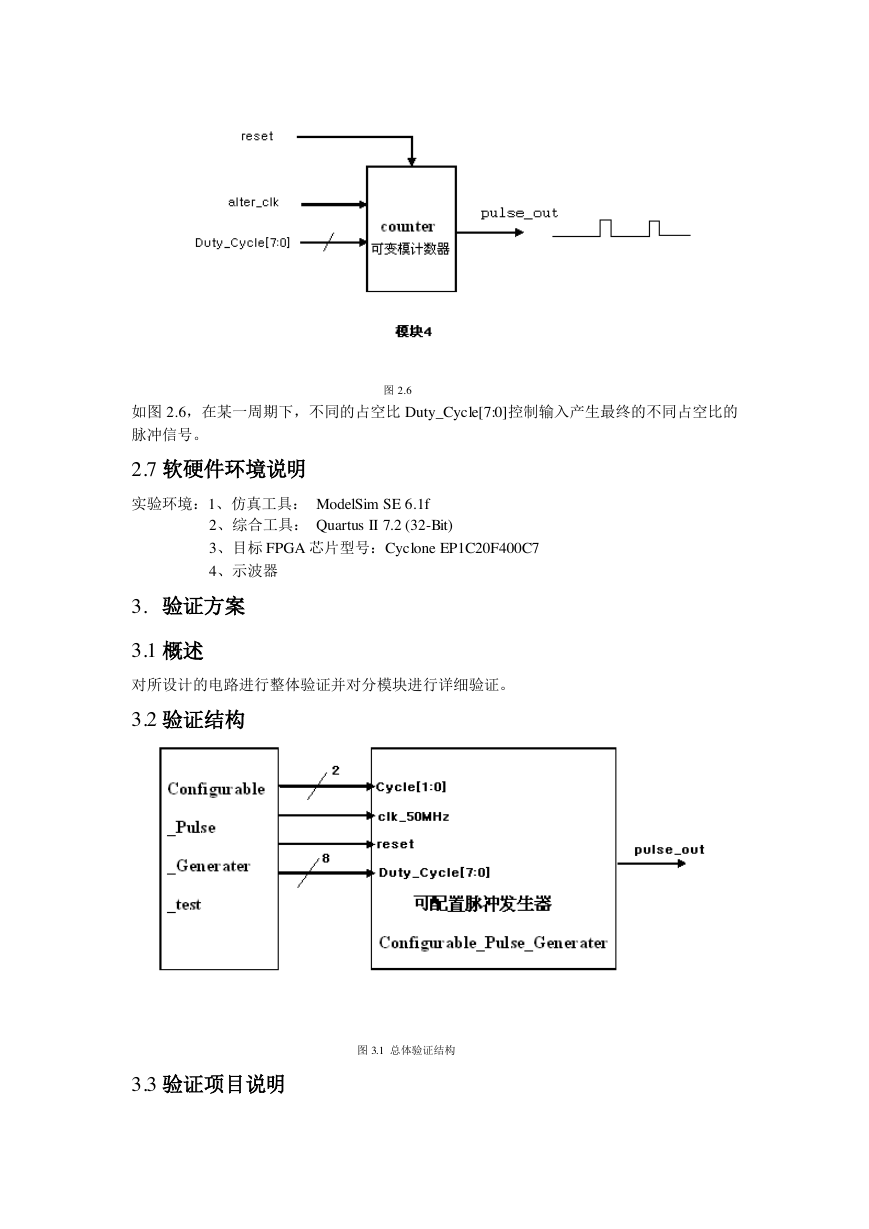

如图 2.6,在某一周期下,不同的占空比 Duty_Cycle[7:0]控制输入产生最终的不同占空比的

脉冲信号。

图 2.6

2.7 软硬件环境说明

实验环境:1、仿真工具: ModelSim SE 6.1f

2、综合工具: Quartus II 7.2 (32-Bit)

3、目标 FPGA 芯片型号:Cyclone EP1C20F400C7

4、示波器

3. 验证方案

3.1 概述

对所设计的电路进行整体验证并对分模块进行详细验证。

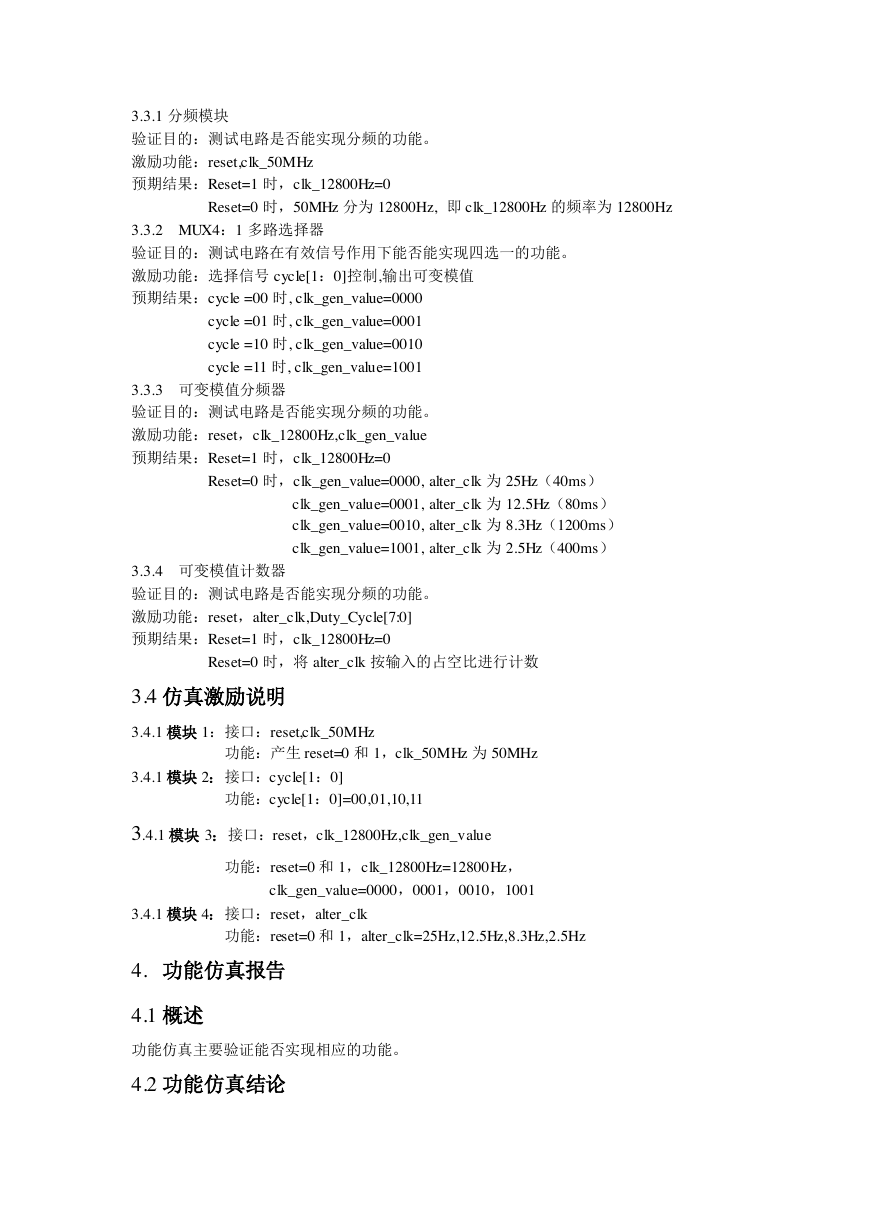

3.2 验证结构

图 3.1 总体验证结构

3.3 验证项目说明

�

3.3.1 分频模块

验证目的:测试电路是否能实现分频的功能。

激励功能:reset,clk_50MHz

预期结果:Reset=1 时,clk_12800Hz=0

Reset=0 时,50MHz 分为 12800Hz, 即 clk_12800Hz 的频率为 12800Hz

3.3.2 MUX4:1 多路选择器

验证目的:测试电路在有效信号作用下能否能实现四选一的功能。

激励功能:选择信号 cycle[1:0]控制,输出可变模值

预期结果:cycle =00 时, clk_gen_value=0000

cycle =01 时, clk_gen_value=0001

cycle =10 时, clk_gen_value=0010

cycle =11 时, clk_gen_value=1001

3.3.3 可变模值分频器

验证目的:测试电路是否能实现分频的功能。

激励功能:reset,clk_12800Hz,clk_gen_value

预期结果:Reset=1 时,clk_12800Hz=0

Reset=0 时,clk_gen_value=0000, alter_clk 为 25Hz(40ms)

clk_gen_value=0001, alter_clk 为 12.5Hz(80ms)

clk_gen_value=0010, alter_clk 为 8.3Hz(1200ms)

clk_gen_value=1001, alter_clk 为 2.5Hz(400ms)

3.3.4 可变模值计数器

验证目的:测试电路是否能实现分频的功能。

激励功能:reset,alter_clk,Duty_Cycle[7:0]

预期结果:Reset=1 时,clk_12800Hz=0

Reset=0 时,将 alter_clk 按输入的占空比进行计数

3.4 仿真激励说明

3.4.1 模块 1:接口:reset,clk_50MHz

功能:产生 reset=0 和 1,clk_50MHz 为 50MHz

3.4.1 模块 2:接口:cycle[1:0]

功能:cycle[1:0]=00,01,10,11

3.4.1 模块 3:接口:reset,clk_12800Hz,clk_gen_value

功能:reset=0 和 1,clk_12800Hz=12800Hz,

clk_gen_value=0000,0001,0010,1001

3.4.1 模块 4:接口:reset,alter_clk

功能:reset=0 和 1,alter_clk=25Hz,12.5Hz,8.3Hz,2.5Hz

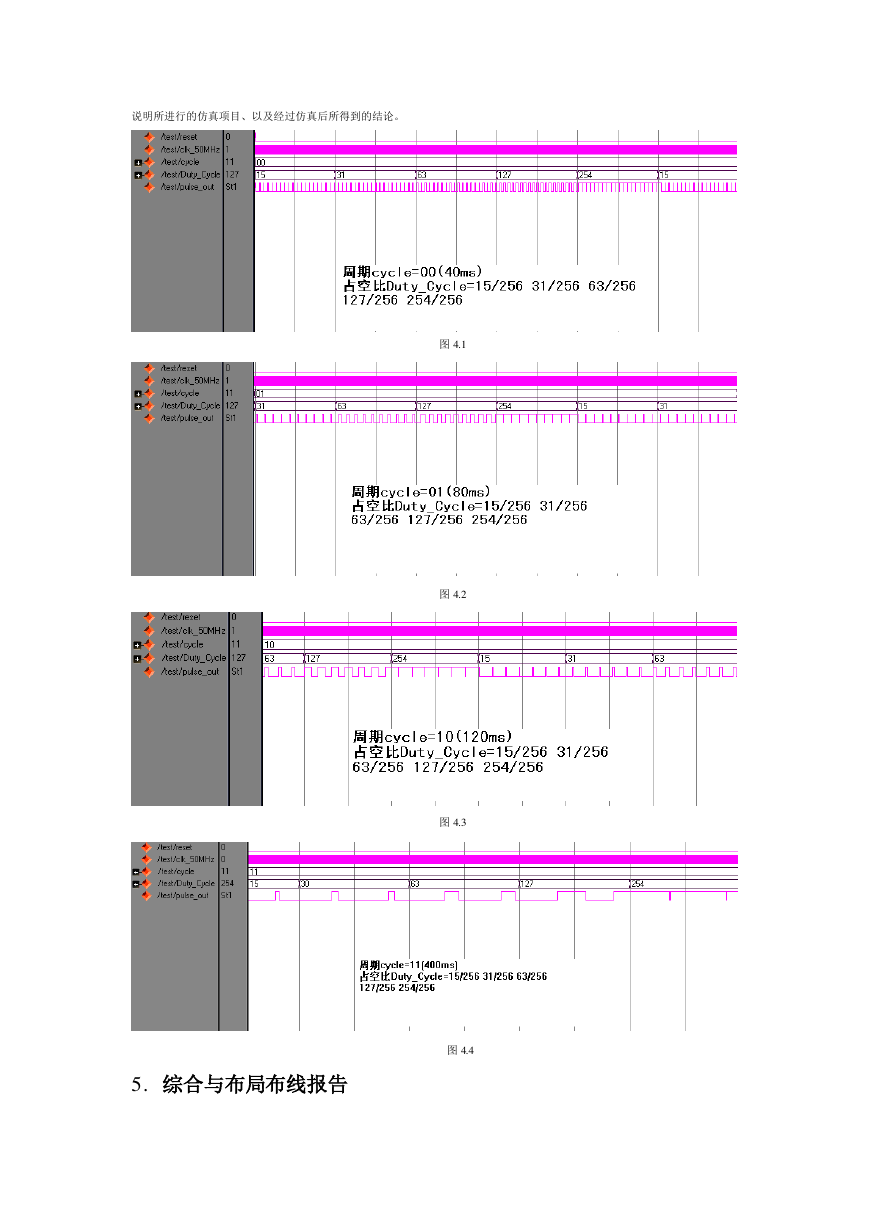

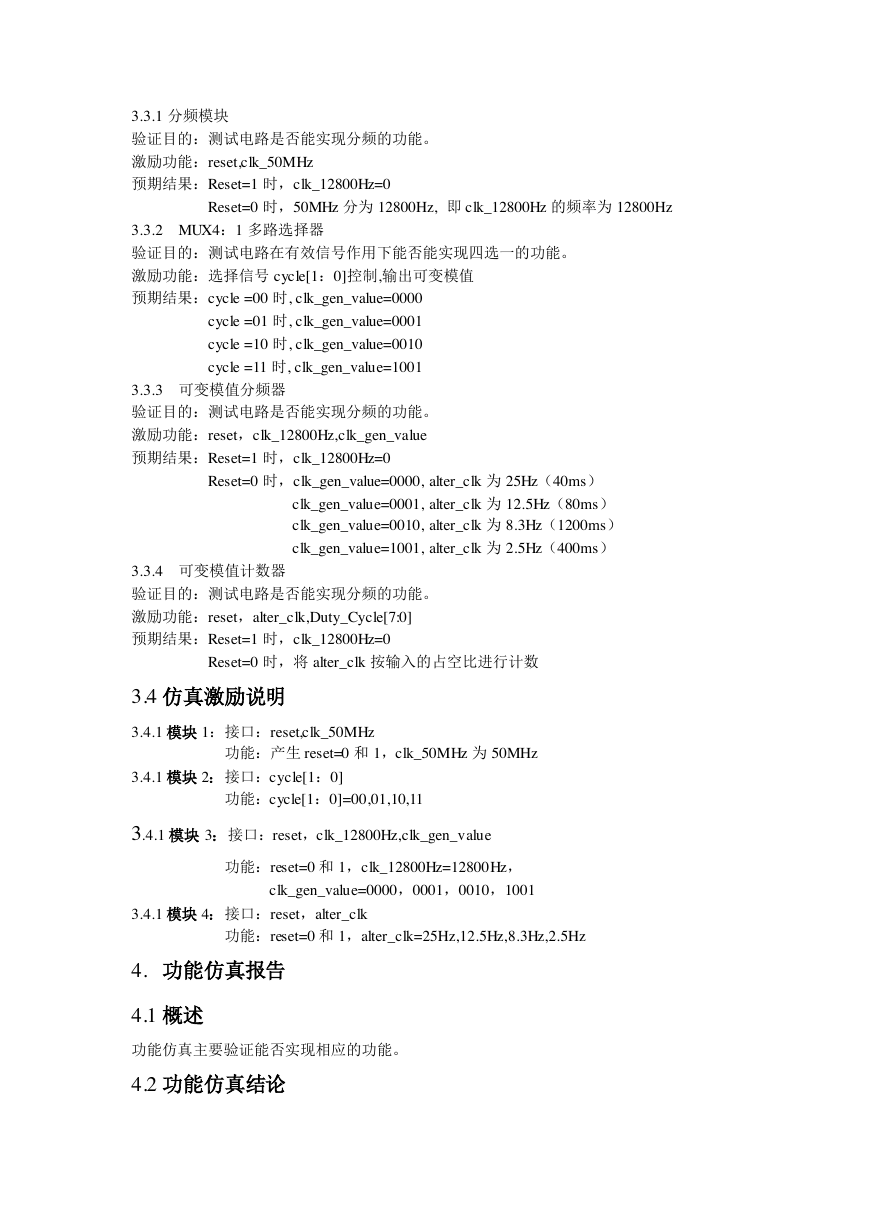

4. 功能仿真报告

4.1 概述

功能仿真主要验证能否实现相应的功能。

4.2 功能仿真结论

�

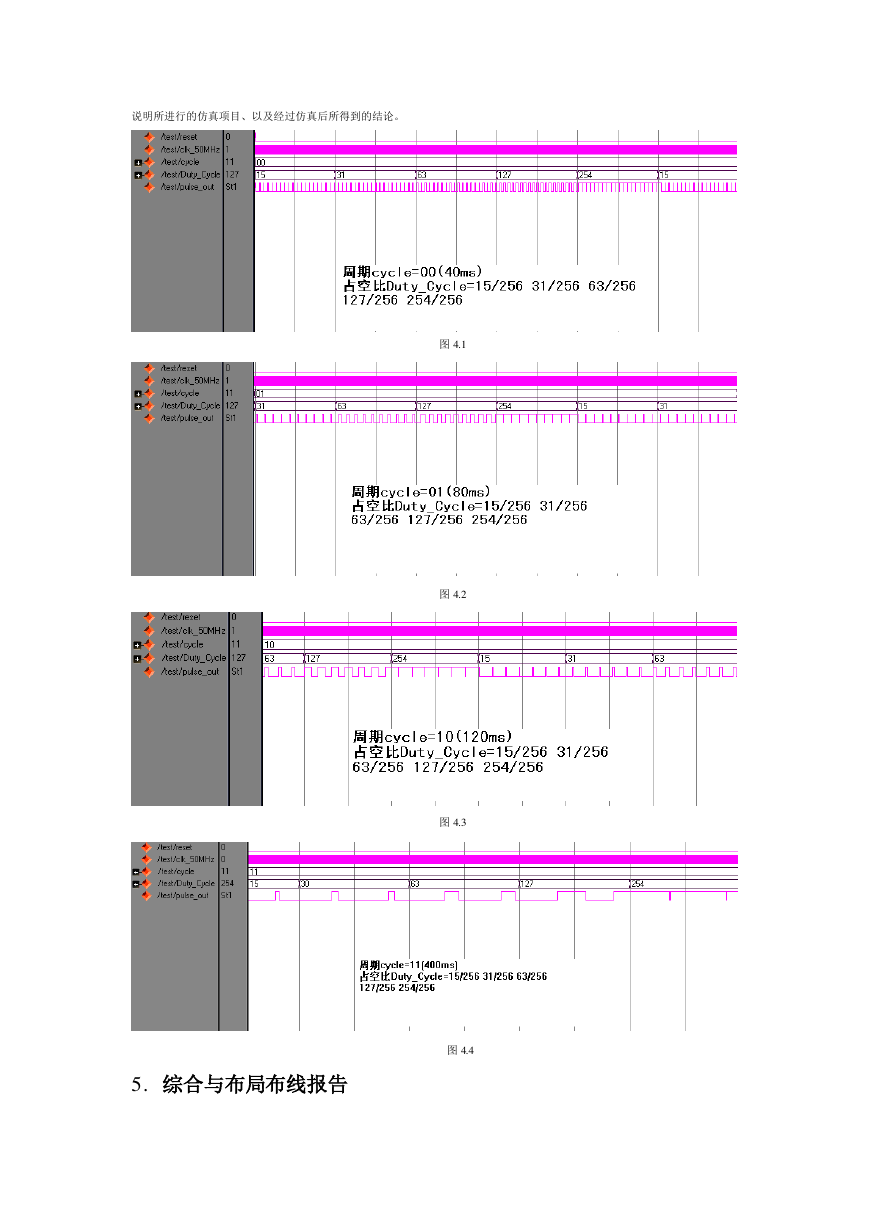

说明所进行的仿真项目、以及经过仿真后所得到的结论。

图 4.1

图 4.2

图 4.3

图 4.4

5. 综合与布局布线报告

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc