STM8L参考手册(RM0031)

介绍

表1. 适用产品

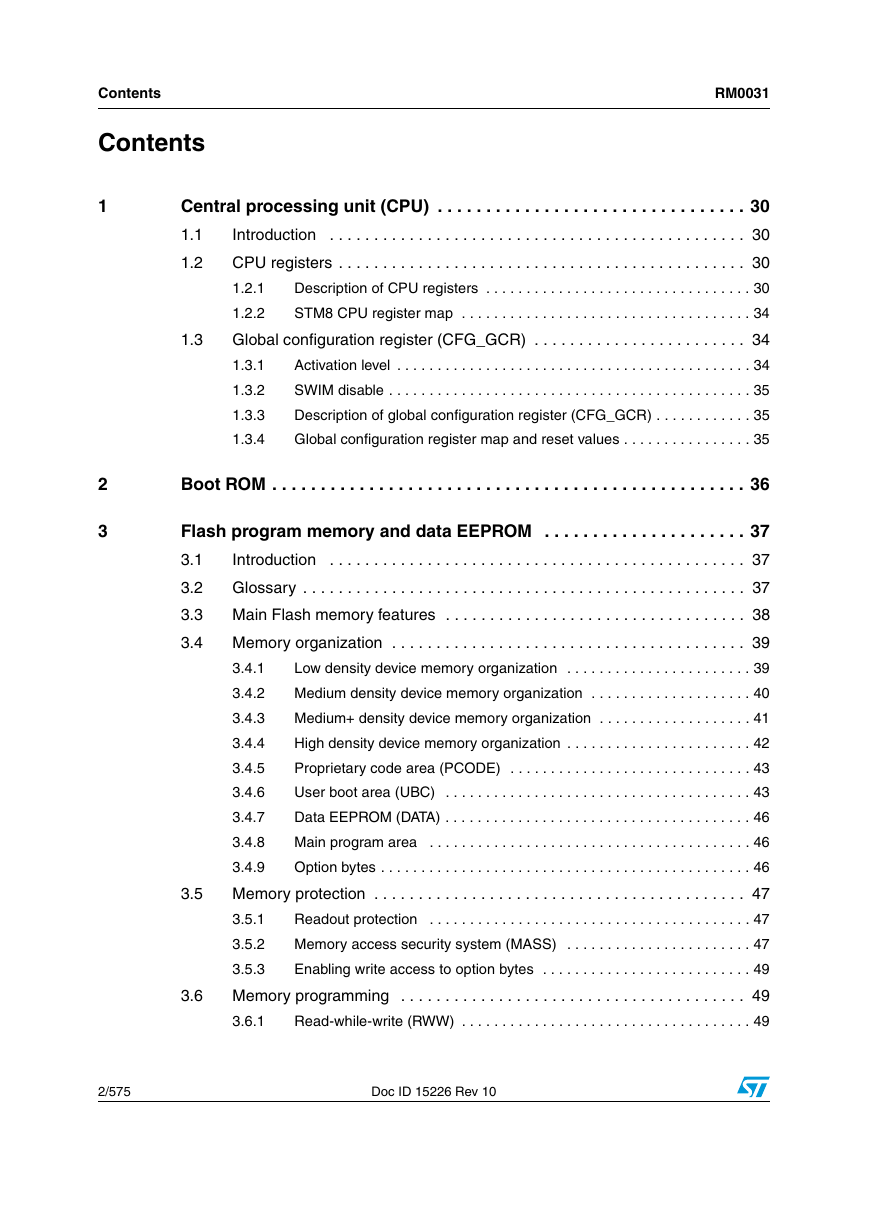

1 中央处理单元(CPU)

1.1 介绍

1.2 CPU 寄存器

1.2.1 Description of CPU registers

Figure 1. Programming model

Figure 2. Stacking order

Table 2. Interrupt levels

1.2.2 STM8 CPU register map

Table 3. CPU register map

1.3 全局配置寄存器(CFG_GCR)

1.3.1 激活水平

1.3.2 SWIM禁用

1.3.3 全局配置寄存器的描述(CFG_GCR)

1.3.4 全局配置寄存器映射和复位值

表 4. CFG_GCR 寄存器映射

2 引导ROM

3 闪存程序存储器和数据EEPROM

3.1 介绍

3.2 名词解释

3.3 主要闪存记忆体功能

3.4 存储器结构

3.4.1 Low density device memory organization

Figure 3. Low density Flash program and data EEPROM

3.4.2 Medium density device memory organization

Figure 4. Medium density Flash program and data EEPROM organization

3.4.3 Medium+ density device memory organization

Figure 5. Medium+ density Flash program and data EEPROM organization

3.4.4 High density device memory organization

Figure 6. High density Flash program and data EEPROM organization

3.4.5 Proprietary code area (PCODE)

3.4.6 User boot area (UBC)

Figure 7. UBC area size definition for low density devices

Figure 8. UBC area size definition for medium density devices

Figure 9. UBC area size definition for medium + STM8L05xx/15xx devices

Figure 10. UBC area size definition for high density devices

3.4.7 Data EEPROM (DATA)

3.4.8 Main program area

3.4.9 Option bytes

3.5 存储器保护

3.5.1 Readout protection

3.5.2 Memory access security system (MASS)

3.5.3 Enabling write access to option bytes

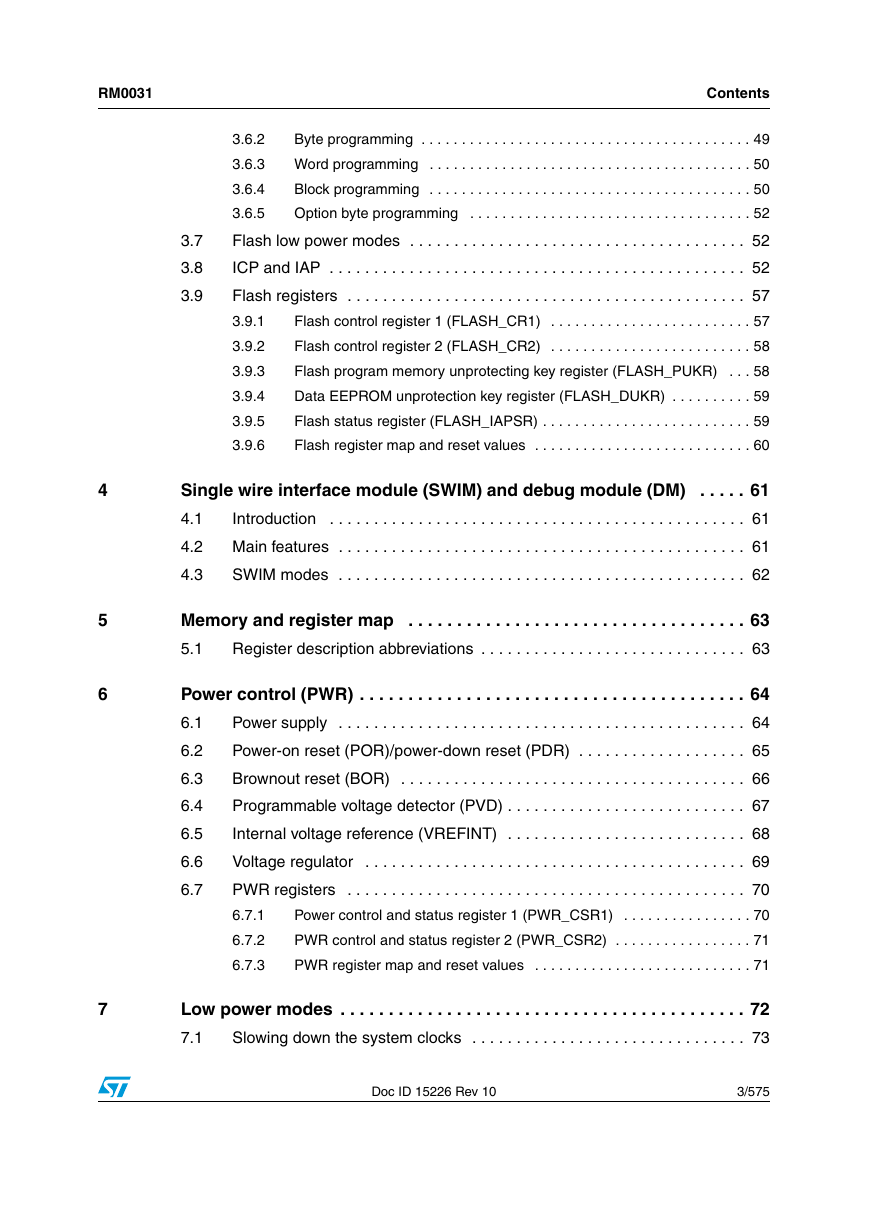

3.6 存储器编程

3.6.1 Read-while-write (RWW)

3.6.2 Byte programming

3.6.3 Word programming

3.6.4 Block programming

Table 5. Block size

3.6.5 Option byte programming

3.7 闪存低功耗模式

3.8 ICP 和 IAP

Table 6. Memory access versus programming method (low density devices)

Table 7. Memory access versus programming method (medium density devices)

Table 8. Memory access versus programming method (medium+ and high density devices)

3.9 闪存寄存器

3.9.1 Flash control register 1 (FLASH_CR1)

3.9.2 Flash control register 2 (FLASH_CR2)

3.9.3 Flash program memory unprotecting key register (FLASH_PUKR)

3.9.4 Data EEPROM unprotection key register (FLASH_DUKR)

3.9.5 Flash status register (FLASH_IAPSR)

3.9.6 Flash register map and reset values

Table 9. Flash register map

4 单线接口模块(SWIM)和调试模块(DM)

4.1 介绍

4.2 Main features

Figure 11. SWIM pin connection

4.3 SWIM modes

5 内存和寄存器映射

5.1 Register description abbreviations

Table 10. List of abbreviations

6 电源控制(PWR)

6.1 Power supply

Figure 12. Power supply overview

6.2 Power-on reset (POR)/power-down reset (PDR)

Figure 13. Power on reset/power down reset waveform

6.3 Brownout reset (BOR)

Figure 14. VDD voltage detection: BOR threshold

6.4 Programmable voltage detector (PVD)

Figure 15. PVD threshold

6.5 Internal voltage reference (VREFINT)

Table 11. Internal voltage reference status during Halt/Active-halt mode

6.6 Voltage regulator

Table 12. PWR interrupt requests

6.7 PWR registers

6.7.1 Power control and status register 1 (PWR_CSR1)

6.7.2 PWR control and status register 2 (PWR_CSR2)

6.7.3 PWR register map and reset values

Table 13. PWR register map and reset values

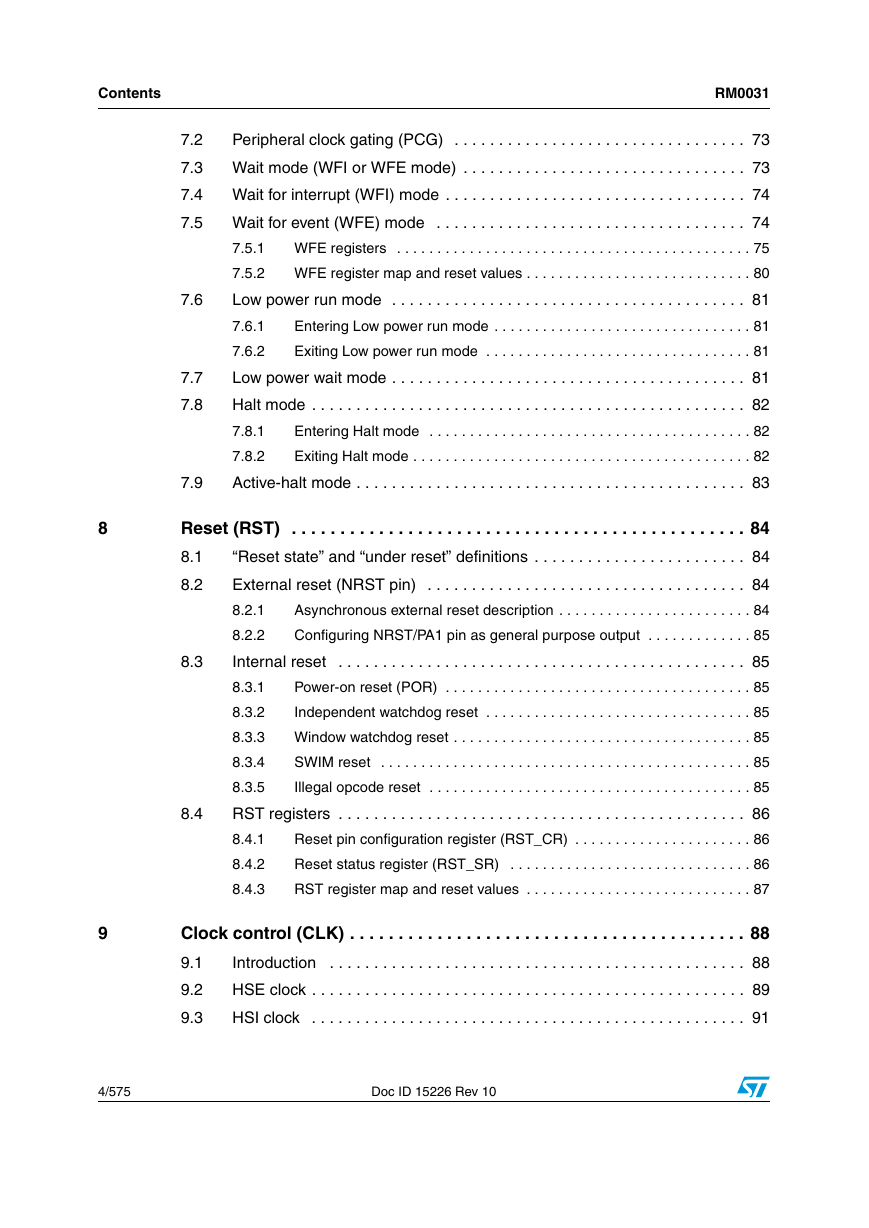

7 低功耗模式

Table 14. Low power mode summary

7.1 Slowing down the system clocks

7.2 Peripheral clock gating (PCG)

7.3 Wait mode (WFI or WFE mode)

7.4 Wait for interrupt (WFI) mode

7.5 Wait for event (WFE) mode

7.5.1 WFE registers

7.5.2 WFE register map and reset values

Table 15. WFE register map

7.6 Low power run mode

7.6.1 Entering Low power run mode

7.6.2 Exiting Low power run mode

7.7 Low power wait mode

7.8 Halt mode

7.8.1 Entering Halt mode

7.8.2 Exiting Halt mode

7.9 Active-halt mode

8 复位 (RST)

图16.复位电路

8.1“复位状态”和“复位下”定义

8.2外部复位(NRST引脚)

8.2.1异步外部复位描述

8.2.2配置NEST/ PA1引脚作为通用输出

8.3内部复位

8.3.1 上电复位(POR)

8.3.2 独立的看门狗复位

8.3.3 窗口看门狗复位

8.3.4 SWIM复位

8.3.5 非法操作码复位

8.4 RST 寄存器

8.4.1 复位引脚配置寄存器(RST_CR)

8.4.2 复位状态寄存器(RST_SR)

8.4.3 RST寄存器映射和复位值

表16. RST寄存器映射和复位值

9 时钟控制(CLK)

9.1 介绍

图17 时钟结构

9.2 HSE 时钟

图 18. HSE 时钟结构

9.3 HSI 时钟

9.4 LSE 时钟

9.5 LSI 时钟

9.6 系统时钟源

9.6.1 系统启动

9.6.2 系统时钟切换程序

图19 时钟切换流程图(自动模式为例)

图20 时钟切换流程图(无中断手动模式的例子)

图21 时钟切换流程图(带中断手动模式的例子)

9.7 外设时钟门控(PCG)

9.8 时钟安全系统(CSS)

9.8.1 HSE时钟安全系统

9.8.2 LSE时钟安全系统

表17 LSE低功耗模式下的CSS

9.8.3 LSE的CSS控制和状态寄存器(CSSLSE_CSR)

9.8.4 LSE的CSS寄存器映射和复位值

表 18. LSE的CSS寄存器映射

9.9 RTC和LCD时钟

9.10 BEEP 时钟

9.11 可配置的时钟输出能力(CCO)

9.12 TIM2/TIM3独立的系统时钟源

9.13 CLK 中断

表 19. CLK 中断寄存器

9.14 CLK 寄存器

9.14.1 系统时钟分频寄存器(CLK_CKDIVR)

9.14.2 RTC时钟寄存器(CLK_CRTCR)

9.14.3 内部时钟寄存器(CLK_ICKCR)

9.14.4 外设时钟门控寄存器 1 (CLK_PCKENR1)

表 20. 外设时钟门控位(PCKEN 10 to PCKEN 17)

9.14.5 外设时钟门控寄存器 2 (CLK_PCKENR2)

表 21. 外设时钟门控位(PCKEN 20 to PCKEN 27)

9.14.6 外设时钟门控寄存器 3 (CLK_PCKENR3)

表 22. 外设时钟门控位(PCKEN 30 to PCKEN 35)

9.14.7 可配置的时钟输出寄存器(CLK_CCOR)

9.14.8 外部时钟寄存器(CLK_ECKCR)

9.14.9 系统时钟状态寄存器(CLK_SCSR)

9.14.10 系统时钟切换寄存器(CLK_SWR)

9.14.11 切换控制寄存器(CLK_SWCR)

9.14.12 时钟安全系统寄存器(CLK_CSSR)

9.14.13 时钟提示音寄存器(CLK_CBEEPR)

9.14.14 HSI校准寄存器 (CLK_HSICALR)

9.14.15 HSI 时钟校准调节寄存器 (CLK_HSITRIMR)

9.14.16 HSI 解锁寄存器(CLK_HSIUNLCKR)

9.14.17 主调节器的控制状态寄存器 (CLK_REGCSR)

9.14.18 CLK 寄存器映射和复位值

表 23. CLK 寄存器映射和复位值

10 通用I/ O端口(GPIO)

10.1 Introduction

10.2 GPIO main features

Figure 22. GPIO block diagram

10.3 Port configuration and usage

Table 24. I/O port configuration summary

10.3.1 Input modes

10.3.2 Output modes

10.4 Reset configuration

10.5 Unused I/O pins

10.6 Low power modes

Table 25. Effect of low power modes on GPIO ports

10.7 Input mode details

10.7.1 Alternate function input

10.7.2 Interrupt capability

10.8 Output mode details

10.8.1 Alternate function output

10.8.2 Slope control

10.9 GPIO registers

10.9.1 Port x output data register (Px_ODR)

10.9.2 Port x pin input register (Px_IDR)

10.9.3 Port x data direction register (Px_DDR)

10.9.4 Port x control register 1 (Px_CR1)

10.9.5 Port x control register 2 (Px_CR2)

10.9.6 Peripheral alternate function remapping

10.9.7 GPIO register map and reset values

Table 26. GPIO register map

11 路由接口(RI)和系统配置控制器(SYSCFG)

11.1 介绍

11.2 RI 主要功能

图23 路由接口(RI)框图(中,中+高密度设备)

图24 路由接口(RI)的框图(低密度器件)

11.2.1 RI 功能描述

11.2.2 I/O 组

表27 I/O组和选择

11.2.3 TIM1 输入捕捉路由

表28 TIM1输入捕捉路由

11.2.4 TIM2 & TIM3 routing

Figure 25. TIM2 and TIM3 interconnections

11.2.5 Comparator routing

11.2.6 DAC routing

Figure 26. DAC interconnections

11.2.7 Internal reference voltage routing

Figure 27. Internal reference voltage output

11.3 RI 中断

Table 29. RI interrupt requests

11.4 RI 寄存器

11.4.1 Timer input capture routing register 1 (RI_ICR1)

11.4.2 Timer input capture routing register 2 (RI_ICR2)

11.4.3 I/O input register 1 (RI_IOIR1)

11.4.4 I/O input register 2 (RI_IOIR2)

11.4.5 I/O input register 3 (RI_IOIR3)

11.4.6 I/O control mode register 1 (RI_IOCMR1)

11.4.7 I/O control mode register 2 (RI_IOCMR2)

11.4.8 I/O control mode register 3 (RI_IOCMR3)

11.4.9 I/O switch register 1 (RI_IOSR1)

11.4.10 I/O switch register 2 (RI_IOSR2)

11.4.11 I/O switch register 3 (RI_IOSR3)

11.4.12 IO group control register (RI_IOGCR)

11.4.13 Analog switch register 1 (RI_ASCR1)

11.4.14 Analog switch register 2 (RI_ASCR2)

11.4.15 Resistor control register (RI_RCR)

11.4.16 Control register (RI_CR)

11.4.17 IO mask register 1 (RI_IOMR1)

11.4.18 IO mask register 2 (RI_IOMR2)

11.4.19 IO mask register 3 (RI_IOMR3)

11.4.20 IO mask register 4 (RI_IOMR4)

11.4.21 I/O input register 4 (RI_IOIR4)

11.4.22 I/O control mode register 4 (RI_IOCMR4)

11.4.23 I/O switch register 4 (RI_IOSR4)

11.4.24 RI register map and reset values

Table 30. Routing interface register map

11.5 SYSCFG 寄存器

11.5.1 SYSCFG 重映射控制寄存器 1 (SYSCFG_RMPCR1)

11.5.2 SYSCFG 重映射控制寄存器 2 (SYSCFG_RMPCR2)

11.5.3 SYSCFG 重映射控制寄存器 3 (SYSCFG_RMPCR3)

11.5.4 SYSCFG 寄存器映射和复位值

表 31. 寄存器映射

12 中断控制器 (ITC)

12.1 ITC 介绍

12.2 中断屏蔽和处理流程

表32 软件的优先级

图28 中断处理流程图

12.2.1 提供中断挂起服务

图29 优先级的决策过程

12.2.2 中断源

12.3 中断和低功耗模式

12.4 激活水平/低功率模式控制

12.5 并发和嵌套中断管理

12.5.1 并发中断管理模式

图30 并发中断管理

12.5.2 嵌套的中断管理模式

表33 软件的向量地址与映射优先级位

图31 嵌套中断管理

12.6 外部中断

表34 外部中断灵敏度

12.7 中断指令

表35 专用的中断指令集

12.8 中断映射

12.9 ITC和EXTI寄存器

12.9.1 CPU的状态码寄存器的中断位(CCR)

12.9.2 软件优先级寄存器x(ITC_SPRx)

12.9.3 外部中断控制寄存器 1(EXTI_CR1)

12.9.4 外部中断控制寄存器 2 (EXTI_CR2)

12.9.5 外部中断控制寄存器 3 (EXTI_CR3)

12.9.6 外部中断控制寄存器 4 (EXTI_CR4)

12.9.7 外部中断状态寄存器 1 (EXTI_SR1)

12.9.8 外部中断状态寄存器 2 (EXTI_SR2)

12.9.9 外部中断端口选择寄存器 1 (EXTI_CONF1)

12.9.10 外部中断端口选择寄存器 2 (EXTI_CONF2)

12.9.11 ITC和EXTI寄存器映射和复位值

图36. ITC 和EXTI寄存器映射

13 直接存储器存取控制器 (DMA)

13.1 DMA 介绍

名词解释

13.2 DMA 主要功能

图32 DMA框图

13.3 DMA 功能描述

13.3.1 DMA 传输

13.3.2 DMA仲裁器

13.3.3 DMA 通道

数据大小的编程

图33 16位字节模式时序

指针增量

通道配置过程

循环模式(自动重载模式)

内存到内存模式

源地址和目的地址

图34. 正常信道(中密度装置)

图35. 正常通道(介质+和高密度的设备)

图36. 当MEM=0时的内存通道(中密度装置)

图37. 当MEM=0时的内存通道(介质+和高密度的设备)

图38. 当MEM=1时的内存通道(中密度装置)

图39. 当MEM=1时的内存通道(介质+和高密度的设备)

表37 源地址和目的地址

DMA传输暂停

13.3.4 DMA1 寄存器映射

表38 DMA1通道请求映射

图40 DMA1请求映射(中密度装置)

图41 DMA1请求映射(中+高密度设备)

13.3.5 DMA硬件要求说明

AES DMA请求

SPIx DMA请求

USARTx DMA请求

表39 SPIx/ USARTx DMA请求

I2C1 DMA请求

表40 I2C1 DMA请求

ADC1 DMA请求

TIMX DMA请求

表41 TIMX DMA请求

DAC的DMA请求

13.4 DMA 低功耗模式

表42. 在低功耗模式DMA的问题

13.5 DMA 中断

表43 DMA中断请求

13.6 DMA 寄存器

13.6.1 DMA全局配置和状态寄存器(DMA_GCSR)

13.6.2 DMA全局中断寄存器1(DMA_GIR1)

13.6.3 DMA通道配置寄存器(DMA_CxCR)

13.6.4 DMA通道的状态和优先级寄存器(DMA_CxSPR)

13.6.5 DMA数据传输数量寄存器(DMA_CxNDTR)

13.6.6 DMA外设地址寄存器高位(DMA_CxPARH)

13.6.7 DMA外设地址寄存器低位(DMA_CxPARL)

13.6.8 DMA通道3外设地址高位和内存1地址高位寄存器(DMA_C3PARH_C3M1ARH)

13.6.9 DMA通道3外设地址低位和内存1地址低位寄存器(DMA_C3PARL_C3M1ARL)

13.6.10 DMA存储器0地址寄存器高位(DMA_CxM0ARH)

13.6.11 DMA存储器0地址寄存器低位(DMA_CxM0ARL)

13.6.12 DMA通道3的内存0扩展地址寄存器(DMA_C3M0EAR)

13.6.13 DMA 寄存器映射和复位值

Table 44. DMA寄存器映射

14 模拟 - 数字转换器(ADC)

14.1 ADC 介绍

14.2 ADC 主要功能

14.3 ADC 功能说明

14.3.1 概况介绍

图42 ADC框图

14.3.2 模拟量通道数

14.3.3 ADC的通断控制

14.3.4 单次转换模式

ADC外部触发

图43 ADC的外部触发器

14.3.5 连续转换模式

14.3.6 ADC 时钟

14.3.7 模拟看门狗

14.3.8 中断

表45. 标志/中断配置

14.3.9 通道选择(扫描模式)

图44 序列的例子

14.3.10 数据完整性

14.3.11 DMA 传输

14.3.12 配置解析

14.3.13 数据对齐

图45 分辨率和数据对齐

14.3.14 可编程的采样时间

表46. 授权的采样周期

14.3.15 施密特触发器禁用

14.3.16 温度传感器

14.3.17 内部参考电压转换

14.4 ADC 低功耗模式

表47 在低功耗模式下的行为

14.5 ADC 中断

表48. 中断请求

14.6 ADC 寄存器

14.6.1 ADC 配置寄存器1 (ADC_CR1)

14.6.2 ADC 配置寄存器2 (ADC_CR2)

14.6.3 ADC 配置寄存器3 (ADC_CR3)

14.6.4 ADC 状态寄存器 (ADC_SR)

14.6.5 ADC 数据高位寄存器(ADC_DRH)

14.6.6 ADC 数据低位寄存器 (ADC_DRL)

14.6.7 ADC 高阈值高位寄存器(ADC_HTRH)

14.6.8 ADC 高阈值低位寄存器 (ADC_HTRL)

14.6.9 ADC 低阈值高位寄存器 (ADC_LTRH)

14.6.10 ADC 低阈值低位寄存器 (ADC_LTRL)

14.6.11 ADC 通道序列寄存器1 (ADC_SQR1)

14.6.12 ADC 通道序列寄存器 2 (ADC_SQR2)

14.6.13 ADC 通道序列寄存器 3 (ADC_SQR3)

14.6.14 ADC 通道选择扫描 4 (ADC_SQR4)

14.6.15 ADC 触发关闭 1 (ADC_TRIGR1)

14.6.16 ADC 触发关闭 2 (ADC_TRIGR2)

14.6.17 ADC 触发关闭 3 (ADC_TRIGR3)

14.6.18 ADC 触发关闭 4 (ADC_TRIGR4)

14.6.19 ADC 寄存器映射和复位值

表 49. 寄存器映射

15 数字 - 模拟转换器 (DAC)

15.1 DAC introduction

15.2 DAC main features

Figure 46. DAC channel block diagram (medium density devices)

Figure 47. DAC channel block diagram (medium+ and high density devices)

15.3 DAC functional description

15.3.1 DAC channel x enable

15.3.2 DAC output buffer enable

15.3.3 DAC output switch configuration

Table 50. DAC output switch configuration

Table 51. DAC output switch configuration (medium and medium+ and high density devices)

15.3.4 DAC data format

15.3.5 DAC conversion sequence

15.3.6 DAC output voltage

15.3.7 DAC trigger selection

Table 52. Sources of conversion trigger (medium, medium+ and high density devices)

Table 53. Sources of conversion trigger

15.3.8 DAC DMA request

15.3.9 DAC DMA underrun interrupt

15.3.10 Noise generation

Figure 48. DAC LFSR register calculation algorithm

15.3.11 Triangle-wave generation

Figure 49. DAC triangle wave generation

15.3.12 Dual DAC conversion

15.4 DAC registers

15.4.1 DAC channel x control register 1 (DAC_CHxCR1)

15.4.2 DAC channel x control register 2 (DAC_CHxCR2)

15.4.3 DAC software trigger register (DAC_SWTRIGR)

15.4.4 DAC status register (DAC_SR)

15.4.5 DAC channel x right aligned data holding register high (DAC_RDHRH)

15.4.6 DAC channel x right aligned data holding register low (DAC_CHxRDHRL)

15.4.7 DAC channel x left aligned data holding register high (DAC_CHxLDHRH)

15.4.8 DAC channel x left aligned data holding register low (DAC_CHxLDHRL)

15.4.9 DAC channel x 8-bit data holding register (DAC_CHxDHR8)

15.4.10 DAC channel x dual mode right aligned data holding register high (DAC_DCHxRDHRH)

15.4.11 DAC channel x dual mode right aligned data holding register low (DAC_DCHxRDHRL)

15.4.12 DAC channel x dual mode left aligned data holding register high (DAC_DCHxLDHRH)

15.4.13 DAC channel x left aligned data holding register low (DAC_DCHxLDHRL)

15.4.14 DAC channel x dual mode 8-bit data holding register (DAC_DCHxDHR8)

15.4.15 DAC channel x data output register high (DAC_CHxDORH)

15.4.16 DAC channel x data output register low (DAC_CHxDORL)

15.4.17 DAC register map and reset values

Table 54. DAC register map (medium, medium+ and high density devices)

16 比较器(COMP)

16.1 COMP introduction

Figure 50. Comparator block diagram

16.2 COMP main features

16.3 Comparator 1 (COMP1)

Figure 51. COMP1 interconnections

16.4 Comparator 2 (COMP2)

Figure 52. COMP2 interconnections

Figure 53. COMP2 output redirection

16.5 Using the comparators in window mode

Figure 54. Configuring the comparators in window mode

Table 55. Window interrupts/wakeup modes

16.6 COMP low power modes

Table 56. Behavior of comparators in low power modes

16.7 COMP interrupts

Table 57. Comparator interrupt requests

16.8 COMP registers

16.8.1 Comparator control and status register 1 (COMP_CSR1)

16.8.2 Comparator control and status register 2 (COMP_CSR2)

16.8.3 Comparator control and status register 3 (COMP_CSR3)

16.8.4 Comparator control and status register 4 (COMP_CSR4)

16.8.5 Comparator control and status register 5 (COMP_CSR5)

16.8.6 COMP register map and reset values

Table 58. Comparators and routing Interface register map

17 LCD 控制器

17.1 LCD controller introduction

17.1.1 Definitions

17.2 LCD controller main features

17.3 LCD functional description

17.3.1 General description

Figure 55. Medium + and high density LCD controller block diagram

Figure 56. Medium density LCD controller block diagram

17.3.2 Frequency generator

Table 59. Typical frame rate calculation for input frequency of 16.384 kHz

Table 60. Typical frame rate calculation for input frequency of 500 kHz

17.3.3 Common driver

Figure 57. 1/3 bias, 1/4 duty

Figure 58. Static duty

Figure 59. Liquid crystal display and terminal connection (static duty)

Figure 60. Liquid crystal display and terminal connection (1/2 duty, 1/2 bias)

Figure 61. Liquid crystal display and terminal connection (1/3 duty, 1/3 bias)

Figure 62. Liquid crystal display and terminal connection (1/4 duty, 1/3 bias)

Figure 63. Liquid crystal display and terminal connection (1/8 duty, 1/4 bias)

17.3.4 Segment driver

17.3.5 Enabling a segment

17.3.6 Blink

17.3.7 Multiplexing COM[7:4] and SEG[43:40], SEG[39:36], or SEG[31:28]

Table 61. SEG and COM signal mapping

17.3.8 Generation of LCD voltage levels

Figure 64. Resistive network

Figure 65. Contrast control

17.3.9 LCD buffer update

17.4 LCD controller low power modes

Table 62. LCD behavior in low power modes

17.5 LCD controller interrupts

Figure 66. SOF interrupt signal

Table 63. LCD interrupt requests

17.6 LCD controller registers

17.6.1 Control register 1 (LCD_CR1)

17.6.2 Control register 2 (LCD_CR2)

17.6.3 Control register 3 (LCD_CR3)

17.6.4 Frequency selection register (LCD_FRQ)

17.6.5 Port mask registers (LCD_PM)

17.6.6 Control register 4 (LCD_CR4)

17.6.7 LCD display memory (LCD_RAM)

17.6.8 LCD register map and reset values

Table 64. LCD register map

18 定时器概述

Table 65. Timer characteristics

18.1 Timer feature comparison

Table 66. Timer feature comparison

18.2 Glossary of timer signal names

Table 67. Glossary of internal timer signals

Table 68. Explanation of indices‘i’, ‘n’, and ‘x’

19 16位高级控制定时器(TIM1)

19.1 介绍

19.2 TIM1 主要功能

图67 TIM1一般框图

19.3 TIM1 时基单元

图68 时基单元

19.3.1 读取和写入的16位计数器

图69 16位计数器读取顺序(TIM1_CNTR)

19.3.2 16位TIM1_ARR寄存器写入顺序

19.3.3 预分频器

19.3.4 向上计数模式

图70 计数器向上计数模式

图71 当ARPE= 0(ARR没有预加载)使用预分频器=2时,计数器更新

图72 当ARPE= 1(TIM1_ARR预加载)时,计数器更新事件

19.3.5 递减计数模式

图73 计数器递减计数模式

图74 当ARPE= 0(ARR没有预加载)使用预分频器=2时,计数器更新

图75 当ARPE= 1(TIM1_ARR预加载)时,计数器更新事件

19.3.6 中心对齐模式(加/减计数)

图76 计数器中心对齐模式

图77 计数器时序图,fCK_CNT= fCK_PSC TIM1_ARR=06H ARPE=1

19.3.7 重复向下计数器

图78 根据模式和TIM1_RCR寄存器的设置更新率的例子

19.4 TIM1 时钟/触发控制器

图79 时钟/触发控制器框图

19.4.1 预分频时钟(CK_PSC)

19.4.2 内部时钟源(FSYSCLK)

Figure 80. Control circuit in normal mode, fCK_PSC = fSYSCLK

19.4.3 外部时钟源模式 1

Figure 81. TI2 external clock connection example

Figure 82. Control circuit in external clock mode 1

19.4.4 外部时钟源模式 2

Figure 83. External trigger input block diagram

Figure 84. Control circuit in external clock mode 2

19.4.5 触发同步

Figure 85. Control circuit in trigger mode

Figure 86. Control circuit in trigger reset mode

Figure 87. Control circuit in trigger gated mode

Figure 88. Control circuit in external clock mode 2 + trigger mode

19.4.6 计时器之间的同步

Figure 89. Timer chaining system implementation example

Figure 90. Trigger/master mode selection blocks

Figure 91. Master/slave timer example

Figure 92. Gating timer B with OC1REF of timer A

Figure 93. Gating timer B with the counter enable signal of timer A (CNT_EN)

Figure 94. Triggering timer B with the UEV of timer A (TIMERA-UEV)

Figure 95. Triggering timer B with counter enable CNT_EN of timer A

Figure 96. Triggering Timer A and B with Timer A TI1 input

19.5 TIM1 捕获/比较通道

Figure 97. Capture/compare channel 1 main circuit

Figure 98. 16-bit read sequence for the TIM1_CCRi register in capture mode

19.5.1 Write sequence for 16-bit TIM1_CCRi registers

19.5.2 Input stage

Figure 99. Channel input stage block diagram

Figure 100. Input stage of TIM 1 channel 1

19.5.3 Input capture mode

Figure 101. PWM input signal measurement

Figure 102. PWM input signal measurement example

19.5.4 Output stage

Figure 103. Channel output stage block diagram

Figure 104. Detailed output stage of channel with complementary output (channel 1)

19.5.5 Forced output mode

19.5.6 Output compare mode

Figure 105. Output compare mode, toggle on OC1

19.5.7 PWM mode

Figure 106. Edge-aligned counting mode PWM mode 1 waveforms (ARR = 8)

Figure 107. Center-aligned PWM waveforms (ARR = 8)

Figure 108. Example of one-pulse mode

Figure 109. Complementary output with deadtime insertion

Figure 110. Deadtime waveforms with a delay greater than the negative pulse

Figure 111. Deadtime waveforms with a delay greater than the positive pulse

Figure 112. Six-step generation, COM example (OSSR = 1)

19.5.8 Using the break function

Figure 113. Behavior of outputs in response to a break (channel without complementary output)

Figure 114. Behavior of outputs in response to a break (TIM1 complementary outputs)

19.5.9 Clearing the OCiREF signal on an external event

Figure 115. OCREFCLR activation

19.5.10 Encoder interface mode

Table 69. Counting direction versus encoder signals

Figure 116. Example of counter operation in encoder interface mode

Figure 117. Example of encoder interface mode with IC1 polarity inverted

19.5.11 Timer input XOR function

19.5.12 Interfacing with Hall sensors

Figure 118. Example of Hall sensor interface

19.6 TIM1 中断

19.6.1 TIM1 等待换事件的能力

19.7 TIM1 DMA

19.7.1 DMA single mode

19.7.2 DMA burst mode

Figure 119. DMA burst modes example

19.8 TIM1 寄存器

19.8.1 Control register 1 (TIM1_CR1)

19.8.2 Control register 2 (TIM1_CR2)

19.8.3 Slave mode control register (TIM1_SMCR)

19.8.4 External trigger register (TIM1_ETR)

19.8.5 DMA request enable register (TIM1_DER)

19.8.6 Interrupt enable register (TIM1_IER)

19.8.7 Status register 1 (TIM1_SR1)

19.8.8 Status register 2 (TIM1_SR2)

19.8.9 Event generation register (TIM1_EGR)

19.8.10 Capture/compare mode register 1 (TIM1_CCMR1)

19.8.11 Capture/compare mode register 2 (TIM1_CCMR2)

19.8.12 Capture/compare mode register 3 (TIM1_CCMR3)

19.8.13 Capture/compare mode register 4 (TIM1_CCMR4)

19.8.14 Capture/compare enable register 1 (TIM1_CCER1)

Table 70. Output control for complementary OCi and OCiN channels with break feature

19.8.15 Capture/compare enable register 2 (TIM1_CCER2)

19.8.16 Counter high (TIM1_CNTRH)

19.8.17 Counter low (TIM1_CNTRL)

19.8.18 Prescaler high (TIM1_PSCRH)

19.8.19 Prescaler low (TIM1_PSCRL)

19.8.20 Auto-reload register high (TIM1_ARRH)

19.8.21 Auto-reload register low (TIM1_ARRL)

19.8.22 Repetition counter register (TIM1_RCR)

19.8.23 Capture/compare register 1 high (TIM1_CCR1H)

19.8.24 Capture/compare register 1 low (TIM1_CCR1L)

19.8.25 Capture/compare register 2 high (TIM1_CCR2H)

19.8.26 Capture/compare register 2 low (TIM1_CCR2L)

19.8.27 Capture/compare register 3 high (TIM1_CCR3H)

19.8.28 Capture/compare register 3 low (TIM1_CCR3L)

19.8.29 Capture/compare register 4 high (TIM1_CCR4H)

19.8.30 Capture/compare register 4 low (TIM1_CCR4L)

19.8.31 Break register (TIM1_BKR)

19.8.32 Deadtime register (TIM1_DTR)

19.8.33 Output idle state register (TIM1_OISR)

19.8.34 DMA control register 1 (TIM1_DCR1)

19.8.35 DMA control register 2 (TIM1_DCR2)

19.8.36 DMA address for burst mode (TIM1_DMAR)

19.8.37 TIM1 register map and reset values

Table 71. TIM1 register map

20 16位通用定时器(TIM2/TIM3/TIM5)

20.1 介绍

20.2 TIMx 主要功能

20.3 TIMx 功能描述

图120. TIMx框图

20.3.1时基单元

图 121. 时基单元

20.3.2 时钟/触发控制器

20.3.3 捕获/比较通道

图 122. 输入级框图

图 123. TIM2通道1的输入级

图 124. 输出级

图 125. 通道1的输出级

20.3.4 定时器输入XOR功能

20.4 TIMx 中断

20.5 TIMx 寄存器

20.5.1 控制寄存器 1 (TIMx_CR1)

20.5.2 控制寄存器 2 (TIMx_CR2)

20.5.3 从模式控制寄存器 (TIMx_SMCR)

表 72. TIMx内部触发连接

20.5.4 外部触发寄存器 (TIMx_ETR)

20.5.5 DMA请求使能寄存器 (TIMx_DER)

20.5.6 中断使能寄存器 (TIMx_IER)

20.5.7 状态寄存器 1 (TIMx_SR1)

20.5.8 状态寄存器 2 (TIMx_SR2)

20.5.9 事件生成寄存器 (TIMx_EGR)

20.5.10 捕获/比较模式寄存器 1 (TIMx_CCMR1)

20.5.11 捕获/比较模式寄存器 2 (TIMx_CCMR2)

20.5.12 捕获/比较使能寄存器 1 (TIMx_CCER1)

20.5.13 计数器高位 (TIMx_CNTRH)

20.5.14 计数器低位 (TIMx_CNTRL)

20.5.15 分频器寄存器 (TIMx_PSCR)

20.5.16 自动重载寄存器高位 (TIMx_ARRH)

20.5.17 自动重载寄存器低位 (TIMx_ARRL)

20.5.18 捕获/比较 1 高位 (TIMx_CCR1H)

20.5.19 捕获/比较 1 低位 (TIMx_CCR1L)

20.5.20 捕获/比较 2 高位 (TIMx_CCR2H)

20.5.21 捕获/比较 2 低位 (TIMx_CCR2L)

20.5.22 中断寄存器 (TIMx_BKR)

表73.输出控制位oci频道和休息的功能(中断功能实现的,互补输出未实现)

20.5.23 输出空闲状态寄存器(TIMx_OISR)

20.5.24 TIMx 寄存器映射和复位值

表 74. TIMx 寄存器映射

21 8位基本定时器(TIM4)

21.1 介绍

图126 TIM4框图

21.2 TIM4 主要功能

21.3 TIM4 中断

21.4 TIM4 时钟选择

21.5 TIM4 寄存器

21.5.1 控制寄存器 1 (TIM4_CR1)

21.5.2 控制寄存器 2 (TIM4_CR2)

21.5.3 从模式控制寄存器(TIM4_SMCR)

21.5.4 DMA请求使能寄存器(TIM4_DER)

21.5.5 中断使能寄存器(TIM4_IER)

21.5.6 状态寄存器 1 (TIM4_SR)

21.5.7 事件产生寄存器(TIM4_EGR)

21.5.8 计数器 (TIM4_CNTR)

21.5.9 预分频寄存器 (TIM4_PSCR)

21.5.10 自动重装寄存器 (TIM4_ARR)

21.5.11 TIM4 寄存器映射和复位值

表 75. TIM4 寄存器映射

22 红外(IRTIM)接口

22.1 Introduction

Figure 127. IR internal hardware connections with TIM2 and TIM3

22.2 Main features

22.3 IRTIM register

22.3.1 Control register (IR_CR)

22.3.2 IRTIM register map and reset values

Table 76. IR register map

23 蜂鸣器(BEEP)

23.1 Introduction

Figure 128. BEEP block diagram

23.2 BEEP functional description

23.2.1 Beeper operation

23.2.2 Beeper calibration

23.2.3 LSI clock frequency measurement

23.3 BEEP registers

23.3.1 BEEP control/status register 1 (BEEP_CSR1)

23.3.2 BEEP control/status register 2 (BEEP_CSR2)

23.3.3 BEEP register map and reset values

Table 77. BEEP register map

24 实时时钟(RTC)

24.1 简介

24.2 RTC 主要功能

24.3 RTC 功能说明

24.3.1 时钟和预分频器

图129 RTC模块框图(低密度器件)

图130 RTC模块框图(中密度装置)

图131 RTC模块框图(中+高密度设备)

24.3.2 实时时钟和日历

24.3.3 可编程报警

24.3.4 定期自动唤醒

24.3.5 RTC 初始化和配置

24.3.6 读取日历

24.3.7 重置RTC

24.3.8 RTC同步

24.3.9 RTC 流畅的数字校准

24.3.10 干预检测

24.3.11 校准时钟输出

24.3.12 报警输出

24.4 RTC 低功耗模式

表78. 在RTC的低功耗模式的影响

24.5 RTC 中断

表79. 中断控制位

24.6 RTC 寄存器

24.6.1 时间寄存器 1 (RTC_TR1)

24.6.2 时间寄存器 2 (RTC_TR2)

24.6.3 时间寄存器 3 (RTC_TR3)

24.6.4 数据寄存器 1 (RTC_DR1)

24.6.5 数据寄存器 2 (RTC_DR2)

24.6.6 数据寄存器 3 (RTC_DR3)

24.6.7 分秒级寄存器高位 (RTC_SSRH)

24.6.8 分秒级寄存器低位 (RTC_SSRL)

24.6.9 控制寄存器 1 (RTC_CR1)

24.6.10 控制寄存器 2 (RTC_CR2)

24.6.11 控制寄存器 3 (RTC_CR3)

24.6.12 初始化和状态寄存器 1 (RTC_ISR1)

24.6.13 初始化和状态寄存器 2 (RTC_ISR2)

24.6.14 同步分频寄存器高位 (RTC_SPRERH)

24.6.15 同步分频寄存器低位(RTC_SPRERL)

24.6.16 异步预分频寄存器 (RTC_APRER)

24.6.17 唤醒定时器寄存器高位 (RTC_WUTRH)

24.6.18 唤醒定时器寄存器低位 (RTC_WUTRL)

24.6.19 写保护寄存器 (RTC_WPR)

24.6.20 RTC偏移控制寄存器高位(RTC_SHIFTRH)

24.6.21 RTC偏移控制寄存器低位 (RTC_SHIFTRL)

24.6.22 报警A寄存器 1 (RTC_ALRMAR1)

24.6.23 报警A寄存器 2 (RTC_ALRMAR2)

24.6.24 报警A寄存器 3 (RTC_ALRMAR3)

24.6.25 报警A寄存器 4 (RTC_ALRMAR4)

24.6.26 报警A分秒寄存器高位 (RTC_ALRMASSRH)

24.6.27 报警A分秒寄存器低位(RTC_ALRMASSRL)

24.6.28 报警器A分秒屏蔽寄存器 (RTC_ALRMASSMSKR)

24.6.29 校准寄存器高位 (RTC_CALRH)

24.6.30 校准寄存器低位 (RTC_CALRL)

24.6.31 防篡改控制寄存器 1 (RTC_TCR1)

24.6.32 防篡改控制寄存器 2 (RTC_TCR2)

24.6.33 RTC寄存器映射和复位值

表 80. RTC 寄存器复位值

25 独立看门狗(IWDG)

25.1 Introduction

25.2 IWDG functional description

Figure 132. Independent watchdog (IWDG) block diagram

Table 81. Min/Max IWDG timeout (LSI clock frequency = 38 kHz)

25.3 IWDG registers

25.3.1 Key register (IWDG_KR)

25.3.2 Prescaler register (IWDG_PR)

25.3.3 Reload register (IWDG_RLR)

25.3.4 IWDG register map and reset values

Table 82. IWDG register map

26 窗口看门狗(WWDG)

26.1简介

26.2 WWDG主要特点

26.3 WWDG 功能说明

Figure 133. 看门狗模块

26.4 如何编程看门狗超时

Figure 134. Window watchdog timing diagram

Table 83. Window watchdog timing example

26.5 WWDG low power modes

Table 84. Effect of low power modes on WWDG

26.6 Hardware watchdog option

26.7 WWDG interrupts

26.8 WWDG registers

26.8.1 Control register (WWDG_CR)

26.8.2 Window register (WWDG_WR)

26.9 Window watchdog register map and reset values

Table 85. WWDG register map and reset values

27 AES硬件加速器(AES)

27.1 Introduction

27.2 AES main features

27.3 AES functional description

Figure 135. Block diagram

27.4 Modes of operation

27.4.1 Mode 1: encryption

Figure 136. Mode 1: encryption

27.4.2 Mode 2: Key derivation

Figure 137. Mode 2: key derivation

27.4.3 Mode 3: decryption

Figure 138. Mode 3: decryption

27.4.4 Mode 4: key derivation and decryption

Figure 139. Mode 4: key derivation and decryption

27.5 AES DMA interface

Figure 140. DMA requests and data transfers during input phase (AES_IN)

Figure 141. DMA requests during output phase (AES_OUT)

27.6 Error flags

27.7 Processing time

Table 86. Processing time (in clock cycles)

27.8 AES low power modes

Table 87. Effect of low power modes on AES

27.9 AES interrupts

Table 88. AES interrupt requests

27.10 AES registers

27.10.1 AES control register (AES_CR)

27.10.2 AES status register (AES_SR)

27.10.3 AES data input register (AES_DINR)

27.10.4 AES data output register (AES_DOUTR)

27.10.5 AES register map and reset values

Table 89. AES register map and reset values

28 内部集成电路(I2C)接口

28.1 Introduction

28.2 I2C main features

28.3 I2C general description

Figure 142. I2C bus protocol

Figure 143. I2C block diagram

28.4 I2C functional description

28.4.1 I2C slave mode

Figure 144. Transfer sequence diagram for slave transmitter

Figure 145. Transfer sequence diagram for slave receiver

28.4.2 I2C master mode

Figure 146. Transfer sequence diagram for master transmitter

Figure 147. Method 1: transfer sequence diagram for master receiver

Figure 148. Method 2: transfer sequence diagram for master receiver when N >2

Figure 149. Method 2: transfer sequence diagram for master receiver when N=2

Figure 150. Method 2: transfer sequence diagram for master receiver when N=1

28.4.3 Error conditions

28.4.4 SDA/SCL line control

28.4.5 SMBus

Table 90. SMBus vs. I2C

28.4.6 DMA requests

28.4.7 Packet error checking

28.5 I2C low power modes

Table 91. I2C interface behavior in low power modes

28.6 I2C interrupts

Table 92. I2C Interrupt requests

Figure 151. I2C interrupt mapping

28.7 I2C registers

28.7.1 Control register 1 (I2C_CR1)

28.7.2 Control register 2 (I2C_CR2)

28.7.3 Frequency register (I2C_FREQR)

28.7.4 Own address register LSB (I2C_OAR1L)

28.7.5 Own address register MSB (I2C_OAR1H)

28.7.6 Own address register 2 (I2C_OAR2)

28.7.7 Data register (I2C_DR)

28.7.8 Status register 1 (I2C_SR1)

28.7.9 Status register 2 (I2C_SR2)

28.7.10 Status register 3 (I2C_SR3)

28.7.11 Interrupt and DMA register (I2C_ITR)

28.7.12 Clock control register low (I2C_CCRL)

28.7.13 Clock control register high (I2C_CCRH)

Table 93. I2C_CCR values for SCL frequency table (fSYSCLK= 10 MHz or 16 MHz)

28.7.14 TRISE register (I2C_TRISER)

28.7.15 PEC register (I2C_PECR)

28.7.16 I2C register map and reset values

Table 94. I2C register map

29 通用同步/异步收发器(USART)

29.1 USART 介绍

29.2 USART 主要功能

29.3 USART 功能描述

图152 USART框图

29.3.1 USART的说明

图153字长编程

29.3.2 发送器

图154可配置的停止位

图155 发送的时候的TC/ TXE行为

29.3.3 接收器

图156起始位检测

图157噪声检测数据采样

表95.噪声检测从采样数据

29.3.4高精度的波特率发生器

图158如何编写USART_DIV中的BRR寄存器

表96波特率编程和计算错误

表97波特率编程和计算错误

表98波特率编程和计算错误

29.3.5 USART接收器的时钟偏差的耐受性

表99 USART接收器当USART_DIV[3:0]为0时的耐受性

表100 USART接收器当USART_DIV[3:0]不为0时的耐受性

29.3.6奇偶控制

表101 帧格式

29.3.7多处理器通信

图159. 利用空闲线检测静音模式

图160 静音模式下使用的地址标记检测

29.3.8 USART同步通信

图161 USART同步传输的例子

图162 USART的数据时钟的时序图(M= 0)

图163 USART的数据时钟的时序图(M= 1)

图164 RX数据建立/保持时间

29.3.9 单线半双工通信

29.3.10 智能卡

图165 ISO7816-3异步协议

图166 使用1.5个停止位奇偶校验错误检测

29.3.11 IrDA的SIR ENDEC块

图167 IrDA SIR ENDEC-框图

图168 IrDA数据调制(3/16) - 正常模式

29.3.12 使用DMA的连续通讯

使用DMA发送

图169. 使用DMA传输

使用DMA接收

图170. 使用DMA接收

多缓冲通信的错误标志和中断生成

29.4 USART 低功耗模式

表 102. 低功耗模式的USART接口特性

29.5 USART 中断

表103 USART的中断请求

图171 USART的中断映射图

29.6 USART 寄存器

29.6.1 状态寄存器 (USART_SR)

29.6.2 数据寄存器 (USART_DR)

29.6.3 波特率寄存器1(USART_BRR1)

29.6.4 波特率寄存器2 (USART_BRR2)

29.6.5 控制寄存器 1 (USART_CR1)

29.6.6 控制寄存器 2 (USART_CR2)

29.6.7 控制寄存器 3 (USART_CR3)

29.6.8 控制寄存器 4 (USART_CR4)

29.6.9 控制寄存器 5 (USART_CR5)

29.6.10 保护时间寄存器(USART_GTR)

29.6.11 预分频寄存器(USART_PSCR)

29.6.12 USART寄存器映射与复位值

Table 104. USART register map

30 串行外设接口(SPI)

30.1 介绍

30.2 SPI 主要特点

30.3 SPI 功能描述

30.3.1 总体描述

图 172. SPI 框图

图 173 单主机/单从应用

从机选择(NSS)引脚的管理

时钟相位和时钟极性

图 174.数据时钟时序图

30.3.2 配置SPI从模式

30.3.3 配置SPI主模式

30.3.4 配置SPI为通信单工

30.3.5 数据发送和接收程序

Rx和Tx缓冲区

图175.在全双工模式连续传输的情况下,TXW/ RXN/ BAY行为(仅接收=0)。

图 176. 从机/全双工模式连续传输的情况下,(BDM=0,RXONLY=0)TXE/ RXE/BOSSY行为。

图177. TXE/ BSY在主发送-只读模式连续传输的情况下(BDM=0和RXONLY=0)。

图178 TXE/ BSY从机发射-只读模式连续传输的情况下,(BDM=0和RXONLY=0)。

图179. 连续传输的情况下,在只接收模式,RXNE行为(BDM= 0和RXONLY= 1)。

图180 不连续传输的情况下, 发送时TXE/ BSY行为(BDM= 0和RXLONY= 0)时。

30.3.6 CRC计算

30.3.7 状态标志

30.3.8 禁止SPI

30.3.9 SPI 使用DMA通信(直接内存寻址)

图181.

使用DMA的传输

图182. 使用DMA接收

30.3.10 错误标志

30.3.11 SPI 低功耗模式

表105. 低功耗模式下的SPI行为

30.3.12 SPI 中断

表 106. SPI 中断映射

30.4 SPI 寄存器

30.4.1 SPI 控制寄存器 1 (SPI_CR1)

30.4.2 SPI 控制寄存器 2 (SPI_CR2)

30.4.3 SPI 中断控制寄存器 (SPI_ICR)

30.4.4 SPI 中断寄存器 (SPI_SR)

30.4.5 SPI 数据寄存器 (SPI_DR)

30.4.6 SPI CRC多项式寄存器 (SPI_CRCPR)

30.4.7 SPI Rx CRC 寄存器 (SPI_RXCRCR)

30.4.8 SPI Tx CRC 寄存器(SPI_TXCRCR)

30.5 SPI 寄存器映射和复位值

表107. SPI寄存器映射和复位值

31 修订历史

表108.文档修订历史记录

STM8S技术参考手册V4

导言

目录

1 中央处理器(CPU)

1.1 简介

1.2 CPU寄存器

1.2.1 CPU寄存器描述

1.2.2 STM8 CPU寄存器映射

1.3 全局配置寄存器(CFG_GCR)

1.3.1 激活级别

1.3.2 禁用SWIM

1.3.3 全局配置寄存器(CFG_GCR)描述

1.3.4 全局配置寄存器映射及复位值

2 用于系统启动的只读存储器

3 存储器和寄存器映射

3.1 寄存器描述缩写

4 FLASH程序存储器和数据EEPROM

4.1 介绍

4.2 词汇表

4.3 FLASH主要特性

4.4 存储器组织结构

4.4.1 用户启动区域(UBC)

4.4.2 数据EEPROM(DATA)

4.4.3 主程序区

4.4.4 选项字节(Option byte)

4.5 存储器保护

4.5.1 读保护

4.5.2 存储器存取安全系统(MASS)

对主程序存储器的写操作

对DATA区域的写操作

4.5.3 对选项字节的写操作

4.6 存储器编程

4.7 读同时写 (RWW)

4.7.1 字节编程

自动快速字节编程

4.7.2 字编程

4.7.3 块编程

标准块编程

快速块编程

块擦除

4.7.4 选项字节(Option byte)编程

4.8 ICP和IAP

4.9 FLASH寄存器

4.9.1 FLASH控制寄存器1(FLASH_CR1)

4.9.2 FLASH控制寄存器2(FLASH_CR2)

4.9.3 FLASH互补控制寄存器2(FLASH_NCR2)

4.9.4 FLASH保护寄存器(FLASH_FPR)

4.9.5 FLASH保护寄存器(FLASH_NFPR)

4.9.6 FLASH程序存储器解保护寄存器(FLASH_PUKR)

4.9.7 DATA EEPROM解保护寄存器(FLASH_DUKR)

4.9.8 FLASH状态寄存器(FLASH_IAPSR)

4.9.9 FLASH寄存器映射和复位值

5 单线接口模块(SWIM)和调试模块(DM)

5.1 介绍

5.2 主要特性

5.3 SWIM模式

6 供电电源

7 复位(RST)

7.1 复位电路

7.2 内部复位源

7.2.1 上电复位(POR)和掉电复位(BOR)

7.2.2 看门狗复位

7.2.3 软件复位

7.2.4 SWIM复位

7.2.5 非法操作码复位

7.2.6 EMS复位

7.3 复位(RST)寄存器

7.3.1 复位状态寄存器(RST_SR)

7.4 复位寄存器地址映射

8 时钟控制

抗电磁干扰时钟配置寄存器

8.1 主时钟源

8.1.1 HSE

外部晶体/陶瓷谐振器(HSE晶体)

外部时钟源(HSE用户外部时钟)

8.1.2 HSI

备份时钟源

快速启动特性

校准

8.1.3 LSI

校准

8.2 主时钟切换

8.2.1 系统启动

8.2.2 主时钟切换的过程

自动切换

手动切换

8.3 低速时钟源的选择

8.4 CPU时钟分频器

8.5 外设时钟门控

8.6 时钟安全系统(CSS)

8.7 时钟输出功能(CCO)

8.8 时钟中断

8.9 时钟寄存器

8.9.1 内部时钟寄存器(CLK_ICKR)

8.9.2 外部时钟寄存器(CLK_ECKR)

8.9.3 主时钟状态寄存器(CLK_CMSR)

8.9.4 主时钟切换寄存器(CLK_SWR)

8.9.5 切换控制寄存器(CLK_SWCR)

8.9.6 时钟分频寄存器(CLK_CKDIVR)

8.9.7 外设时钟门控寄存器(CLK_PCKENR1)

8.9.8 外设时钟门控寄存器2(CLK_PCKENR2)

8.9.9 时钟安全系统寄存器(CLK_CSSR)

8.9.10 可配置时钟输出寄存器

8.9.11 CAN外部时钟控制寄存器(CLK_CANCCR)

8.9.12 HSI时钟修正寄存器(CLK_HSITRIMR)

8.9.13 SWIM时钟控制寄存器(CLK_SWIMCCR)

8.10 时钟寄存器地址映射

9 电源管理

9.1 常规考虑

9.2 低功耗的时钟管理

9.2.1 降低系统时钟

9.2.2 外设时钟门控

9.3 低功耗模式

9.3.1 等待(Wait)模式

9.3.2 停机(Halt)模式

快速时钟启动

9.3.3 活跃停机(Active Halt)模式

主电压调节器自动关闭

快速唤醒时钟

9.4 附加的模拟功耗控制

9.4.1 停机模式下的快速内存唤醒

9.4.2 活跃停机模式下的超低内存功耗

10 中断控制器(ITC)

10.1 简介

10.2 中断屏蔽和处理流程

10.2.1 处理等待(排队)的中断

10.2.2 中断源

10.3 中断和低功耗模式

10.4 活动等级/低功耗模式的控制

10.5 同时的和嵌套的中断管理

10.5.1 同时发生中断管理模式

10.5.2 嵌套中断管理模式

10.6 外部中断

10.7 中断指令

10.8 中断映射

10.9 ITC寄存器

10.9.1 CPU CC 寄存器中断位

10.9.2 软件优先级寄存器 x (ITC_SPRx)

10.9.3 外部中断控制寄存器 1 (EXTI_CR1)

10.9.4 外部中断控制寄存器 1 (EXTI_CR2)

10.9.5 寄存器表和复位值

11 通用输入输出口(GPIO)

11.1 简介

11.2 GPIO主要功能

11.3 I/O的配置和使用

11.3.1 输入模式

11.3.2 输出模式

11.4 复位后的默认配置

11.5 没有使用的引脚

11.6 低功耗模式

11.7 输入模式的详述

11.7.1 复用功能输入

11.7.2 中断功能

11.7.3 模拟通道

11.7.4 施密特触发器

11.8 输出模式详述

11.8.1 复用功能的输出

11.8.2 摆率控制

11.9 GPIO 寄存器

11.9.1 端口 x 输出数据寄存器 (Px_ODR)

11.9.2 端口 x 输入寄存器 (Px_IDR)

11.9.3 端口 x 数据方向 (Px_DDR)

11.9.4 端口 x 控制寄存器 1 (Px_CR1)

11.9.5 端口 x 控制寄存器 2 (Px_CR2)

11.9.6 GPIO 寄存器表和复位值

12 自动唤醒(AWU)

12.1 简介

12.2 AWU功能描述

12.2.1 AWU 操作

12.2.2 时基选择

12.2.3 LSI 低速内部时钟频率检测

12.3 AWU 寄存器

12.3.1 控制/状态寄存器 (AWU_CSR)

12.3.2 异步预分频寄存器 (AWU_APR)

12.3.3 时基选择寄存器 (AWU_TBR)

12.3.4 AWU 寄存器表和复位值

13 蜂鸣器(BEEP)

13.1 简介

13.2 功能描述

13.2.1 蜂鸣器操作

13.2.2 蜂鸣器校准

13.3 蜂鸣器 寄存器

13.3.1 蜂鸣器 控制/状态 寄存器 (BEEP_CSR)

13.3.2 BEEP寄存器表和复位值

14 独立看门狗(IWDG)

14.1 介绍

14.2 独立看门狗功能说明

硬件看门狗功能

超时周期

14.3 IWDG寄存器

14.3.1 键寄存器(IWDG_KR)

14.3.2 预分频寄存器(IWDG_PR)

14.3.3 重装载寄存器(IWDG_RLR)

14.3.4 IWDG寄存器映像和复位数值

15 窗口看门狗(WWDG)

15.1 介绍

15.2 WWDG主要功能

15.3 WWDG功能说明

15.4 在停止模式下使用WWDG

15.5 如何设置看门狗的超时

15.6 WWDG低功耗模式

15.7 硬件看门狗选项

15.8 在停止模式下使用WWDG

15.9 WWDG中断

15.10 WWDG寄存器

15.10.1 控制寄存器(WWDG_CR)

15.10.2 窗口寄存器(WWDG_WR)

15.11 窗口看门狗寄存器映像和复位数值

16 定时器概述

16.1 定时器功能比较

16.2 定时器信号术语表

16位高级控制定时器(TIM1)

17.1 简介

17.2 主要特性

17.3 时基单元

17.3.1 读写16位计数器

17.3.2 16位TIM1_ARR寄存器的写操作

17.3.3 预分频器

17.3.4 向上计数模式

17.3.5 向下计数模式

17.3.6 中央对齐模式(向上/向下计数)

17.3.7 重复计数器

17.4 时钟/触发控制器

17.4.1 预分频时钟(CK_PSC)

17.4.2 内部时钟源(fMASTER)

17.4.3 外部时钟源模式1

17.4.4 外部时钟源模式2

17.4.5 触发同步

标准触发模式

复位触发模式

门控触发模式

外部时钟模式2 + 触发模式

17.4.6 与TIM5/TIM6定时器的同步

使用一个定时器作为另一个定时器的预分频时钟

使用一个定时器使能另一个定时器

使用一个定时器启动另一个定时器

用外部信号同步的触发两个定时器

17.5 捕获/比较通道

17.5.1 16位TIM1_CCRi寄存器的写流程

17.5.2 输入模块

17.5.3 输入捕获模式

PWM输入信号测量

17.5.4 输出模块

17.5.5 强制输出模式

17.5.6 输出比较模式

17.5.7 PWM模式

PWM 边沿对齐模式

PWM 中央对齐模式

单脉冲模式

特殊情况:OCx快速使能

互补输出和死区插入

重定向OCiREF到OCi或OCiN

针对马达控制的六步PWM输出

17.5.8 使用刹车功能

17.5.9 在外部事件发生时清除OCREF信号

17.5.10 编码器接口模式

17.6 中断

17.7 TIM1寄存器描述

17.7.1 控制寄存器1(TIM1_CR1)

17.7.2 控制寄存器2(TIM1_CR2)

17.7.3 从模式控制寄存器(TIM1_SMCR)

17.7.4 外部触发寄存器(TIM1_ETR)

17.7.5 中断使能寄存器(TIM1_IER)

17.7.6 状态寄存器1 (TIM1_SR1)

17.7.7 状态寄存器2(TIM1_SR2)

17.7.8 事件产生寄存器(TIM1_EGR)

17.7.9 捕获/比较模式寄存器1(TIM1_CCMR1)

17.7.10 捕获/比较模式寄存器2(TIM1_CCMR2)

17.7.11 捕获/比较模式寄存器3(TIM1_CCMR3)

17.7.12 捕获/比较模式寄存器4(TIM1_CCMR4)

17.7.13 捕获/比较使能寄存器1(TIM1_CCER1)

17.7.14 捕获/比较使能寄存器2(TIM1_CCER2)

17.7.15 计数器高8位(TIM1_CNTRH)

17.7.16 计数器低8位(TIM1_CNTRL)

17.7.17 预分频器高8位(TIM1_PSCRH)

17.7.18 预分频器低8位(TIM1_PSCRL)

17.7.19 自动重装载寄存器高8位(TIM1_ARRH)

17.7.20 自动重装载寄存器低8位(TIM1_ARRL)

17.7.21 重复计数寄存器(TIM1_RCR)

17.7.22 捕获/比较寄存器1高8位(TIM1_CCR1H)

17.7.23 捕获/比较寄存器1低8位(TIM1_CCR1L)

17.7.24 捕获/比较寄存器2高8位(TIM1_CCR2H)

17.7.25 捕获/比较寄存器2低8位(TIM1_CCR2L)

17.7.26 捕获/比较寄存器3高8位(TIM1_CCR3H)

17.7.27 捕获/比较寄存器3低8位(TIM1_CCR3L)

17.7.28 捕获/比较寄存器4高8位(TIM1_CCR4H)

17.7.29 捕获/比较寄存器4低8位(TIM1_CCR4L)

17.7.30 刹车寄存器(TIM1_BKR)

17.7.31 死区寄存器(TIM1_DTR)

17.7.32 输出空闲状态寄存器(TIM1_OISR)

17.7.33 TIM1寄存器图

18 16位通用定时器(TIM2,TIM3,TIM5)

18.1 介绍

18.2 TIM2/TIM3的主要功能

18.3 TIM5主要功能

18.4 TIM2/TIM3/TIM5功能概述

18.4.1 时基单元

预分频器

计数器的操作

18.4.2 时钟/触发控制器

18.4.3 捕获/比较通道

输入部分

输出部分

18.5 中断

18.6 TIM2/TIM3/TIM5寄存器

18.6.1 控制寄存器1(TIMx_CR1)

18.6.2 控制寄存器2(TIM5_CR2)

18.6.3 触发从模式控制寄存器(TIM5_SMCR)

18.6.4 中断使能寄存器(TIMx_IER)

18.6.5 状态寄存器1(TIMx_SR1)

18.6.6 状态寄存器2(TIMx_SR2)

18.6.7 事件产生寄存器(TIMx_EGR)

18.6.8 捕获/比较模式寄存器1(TIMx_CCMR1)

18.6.9 捕获/比较模式寄存器2(TIMx_CCMR2)

18.6.10 捕获/比较模式寄存器3(TIMx_CCMR3)

18.6.11 捕获/比较使能寄存器1(TIMx_CCER1)

18.6.12 捕获/比较使能寄存器2(TIMx_CCER2)

18.6.13 计数器高位(TIMx_CNTRH)

18.6.14 计数器低位(TIMx_CNTRL)

18.6.15 预分频器(TIMx_PSCR)

18.6.16 自动装载寄存器高位(TIMx_ARRH)

18.6.17 自动装载寄存器低位(TIMx_ARRL)

18.6.18 捕获/比较寄存器1高位TIMx_CCR1H)

18.6.19 捕获/比较寄存器1低位(TIMx_CCR1L)

18.6.20 捕获/比较寄存器2高位(TIMx_CCR2H)

18.6.21 捕获/比较寄存器2低位(TIMx_CCR2L)

18.6.22 捕获/比较寄存器3高位(TIMx_CCR3H)

18.6.23 捕获/比较寄存器3低位(TIMx_CCR3L)

18.6.24 TIM2/TIM3/TIM5寄存器图和复位值

19 8位基本定时器 (TIM4, TIM6)

19.1 简介

19.2 TIMER4的主要功能

19.3 TIMER6的主要功能

19.4 TIM4/TIM6中断

19.5 TIM4/TIM6时钟选择

19.6 TIM4/TIM6 寄存器

19.6.1 控制寄存器 1 (TIMx_CR1)

19.6.2 控制寄存器 2 (TIMx_CR2)

19.6.3 从模式控制寄存器 (TIMx_SMCR)

19.6.4 中断使能寄存器 (TIMx_IER)

19.6.5 状态寄存器 1 (TIMx_SR1)

19.6.6 事件产生寄存器(TIMx_EGR)

19.6.7 计数器 (TIMx_CNTR)

19.6.8 预分频寄存器 (TIMx_PSCR)

19.6.9 自动重装载寄存器(TIMx_ARR)

19.6.10 TIM4/TIM6 寄存器表和复位值

20 串行外设接口(SPI)

20.1 SPI简介

20.2 SPI主要特征

20.3 SPI功能描述

20.3.1 概述

从选择(NSS)脚管理

时钟信号的相位和极性

数据帧格式

20.3.2 SPI从模式

配置步骤

数据传输过程

20.3.3 SPI主模式

配置步骤

数据传输过程

20.3.4 单工通信

1条时钟线和1条双向数据线

1条时钟和1条数据线(双工或只接收方式)

只接收模式

20.3.5 状态标志

总线忙(Busy)标志

发送缓冲器空标志(TXE)

接收缓冲器非空(RXNE)

20.3.6 CRC计算

20.3.7 错误标志

主模式错误(MODF)

溢出错误

CRC 错误

20.3.8 关闭SPI

20.3.9 低功耗

使用SPI将设备从停机(Halt)模式唤醒

--全双工和只发模式的半双工

--只接收模式的半双工

20.3.10 SPI中断

20.4 SPI寄存器描述

20.4.1 SPI控制寄存器1(SPI_CR1)

20.4.2 SPI控制寄存器2(SPI_CR2)

20.4.3 SPI 中断控制寄存器(SPI_ICR)

20.4.4 SPI 状态寄存器(SPI_SR)

20.4.5 SPI 数据寄存器(SPI_DR)

20.4.6 SPI CRC多项式寄存器(SPI_CRCPR)

20.4.7 SPI Rx CRC寄存器(SPI_RXCRCR)

20.4.8 SPI Tx CRC寄存器(SPI_TXCRCR)

20.5 SPI 寄存器地址映象以及复位值

21 I2C接口

21.1 I2C简介

21.2 I2C主要特点

21.3 I2C简介

模式选择

通信过程

21.4 I2C功能描述

21.4.1 I2C从模式

从发送模式

从设备接收模式

关闭从模式通信

21.4.2 I2C主模式

起始条件

从地址的发送

主设备发送模式

关闭通信

主设备接收

关闭通信

21.4.3 出错状态

总线错误(BERR)

应答错误(AF)

仲裁失败(ARLO)

过载/欠载错误(OVR)

21.4.4 SDA/SCL线控制

21.5 低功耗模式

21.6 I2C中断请求

21.7 I2C寄存器描述

21.7.1 控制寄存器1(I2C_CR1)

21.7.2 控制寄存器2(I2C_CR2)

21.7.3 频率寄存器(I2C_FREQR)

21.7.4 自身地址寄存器LSB(I2C_OARL)

21.7.5 自身地址寄存器MSB(I2C_OARH)

21.7.6 数据寄存器(I2C_DR)

21.7.7 状态寄存器1(I2C_SR1)

21.7.8 状态寄存器2 (I2C_SR2)

21.7.9 状态寄存器3 (I2C_SR3)

21.7.10 中断寄存器 (I2C_ITR)

21.7.11 时钟控制寄存器低位部分(I2C_CCRL)

21.7.12 时钟控制寄存器高位部分(I2C_CCRH)

21.7.13 TRISE寄存器(I2C_TRISE)

21.7.14 I2C寄存器地址映射和复位值

22 通用异步收发器(UART)

22.1 UART介绍

22.2 UART主要特性

22.3 UART功能概述

22.3.1 UART 特性描述

22.3.2 发送器

字符发送

可配置的停止位

单字节通信

断开符号

空闲符号

22.3.3 接收器

字符接收

断开符号

空闲符号

过载错误

噪音错误

帧错误

接收期间的可配置的停止位

22.3.4 高精度波特率发生器

22.3.5 奇偶校验控制

22.3.6 多处理器通信

空闲总线检测(WAKE=0)

地址标记(address mark)检测(WAKE=1)

22.3.7 LIN(局域互联网)模式

22.3.8 UART 同步模式

22.3.9 单线半双工通信

22.3.10 智能卡

22.3.11 IrDA SIR ENDEC 功能块

IrDA低功耗模式

22.4 LIN模式功能描述

22.4.1 主模式

UART初始化

LIN报文头(header)的发送

LIN断开符和分界符侦测

响应发送(主设备是响应的发布方)

响应接收(主设备是响应的签署方)

响应忽略(从设备对从设备通讯)

22.4.2 自动重同步功能禁用的从模式

UART初始化

LIN报文头(header)的接收

响应发送(从设备是响应的发布方)

响应接收(从设备是响应的签署方)

响应忽略

LIN从模式奇偶校验

LIN报文头错误检测

LIN报文头超时错误

静默模式与错误

22.4.3 自动重同步使能的从模式

自动重同步

同步域的偏移错误

LIN报文头错误侦测

LIN报文头超时错误

同步后UART时钟的允许误差

未经同步UART时钟的允许误差

时钟偏移原因

LIN同步域测量引起的错误

波特率量化引起的错误

在最大波特率时时钟偏移的影响

22.4.4 LIN模式选择

22.5 低功耗模式

22.6 中断

22.7 UART寄存器描述

22.7.1 状态寄存器(UART_SR)

22.7.2 数据寄存器(UART_DR)

22.7.3 波特比率寄存器1(UART_BRR1)

22.7.4 波特比率寄存器2 (UART_BRR2)

22.7.5 控制寄存器1(UART_CR1)

22.7.6 控制寄存器2(UART_CR2)

22.7.7 控制寄存器3(UART_CR3)

22.7.8 控制寄存器4(UART_CR4)

22.7.9 控制寄存器5(UART_CR5)

22.7.10 控制寄存器6(UART_CR6)

22.7.11 保护时间寄存器(UART_GTR)

22.7.12 分频寄存器(UART_PSCR)

22.7.13 UART寄存器地址映射

23 控制器局域网(beCAN)

23.1 简介

23.2 主要特点

发送

接收

时间触发通信模式

管理

23.3 总体描述

23.3.1 CAN 2.0B (active)内核

23.3.2 控制、状态和配置寄存器

23.3.3 发送邮箱

23.3.4 接收过滤器

接收FIFO

23.4 工作模式

23.4.1 初始化模式

23.4.2 正常模式

23.4.3 睡眠模式(低功耗)

23.4.4 时间触发通讯模式

23.5 测试模式

23.5.1 静默模式

23.5.2 环回模式

23.5.3 环回静默模式

23.6 功能描述

23.6.1 发送处理

发送优先级

中止

禁止自动重传模式

23.6.2 接收处理

有效报文

FIFO管理

溢出

与接收相关的中断

23.6.3 标识符过滤

可变的位宽

屏蔽位模式

标识符列表模式

过滤器组位宽和模式的设置

过滤器匹配序号

过滤器优先级规则

23.6.4 报文存储

发送邮箱

接收邮箱

23.6.5 出错管理

离线恢复

23.6.6 位时序

23.7 中断

23.8 寄存器访问保护

23.9 时钟系统

23.10 beCAN低功耗模式

23.11 CAN 寄存器描述

23.11.1 CAN主控制寄存器 (CAN_MCR)

23.11.2 CAN主状态寄存器 (CAN_MSR)

23.11.3 CAN发送状态寄存器 (CAN_TSR)

23.11.4 CAN发送优先级寄存器 (CAN_TPR)

23.11.5 CAN接收FIFO 1寄存器(CAN_RFR)

23.11.6 CAN中断允许寄存器 (CAN_IER)

23.11.7 CAN诊断寄存器 (CAN_DGR)

23.11.8 CAN页面选择寄存器 (CAN_PSR)

23.11.9 CAN错误状态寄存器 (CAN_ESR)

23.11.10 CAN出错中断使能寄存器 (CAN_EIER)

23.11.11 CAN发送出错计数器寄存器 (CAN_TECR)

23.11.12 CAN接收出错计数器寄存器 (CAN_RECR)

23.11.13 CAN位时间特性寄存器 (CAN_BTR1)

23.11.14 CAN位时间特性寄存器 (CAN_BTR2)

23.11.15 邮箱寄存器

CAN报文控制/状态寄存器 (CAN_MCSR)

CAN邮箱过滤匹配索引寄存器 (CAN_MFMIR)

CAN邮箱标识符寄存器 1(CAN_MIDR1)

CAN邮箱标识符寄存器 2(CAN_MIDR2)

CAN邮箱标识符寄存器 3(CAN_MIDR3)

CAN邮箱标识符寄存器 4(CAN_MIDR4)

CAN邮箱数据长度控制寄存器 (CAN_MDLCR)

CAN邮箱数据寄存器 x(CAN_MDARx) (x=1..8)

CAN邮箱时间戳低位寄存器 (CAN_MTSRL)

CAN邮箱时间戳高位寄存器 (CAN_MTSRH)

23.11.16 CAN过滤器寄存器

CAN 过滤器主控寄存器 (CAN_FMR1)

CAN 过滤器模式寄存器 (CAN_FMR2)

CAN 过滤器设置寄存器 (CAN_FCR1)

CAN 过滤器设置寄存器 (CAN_FCR2)

CAN 过滤器设置寄存器 (CAN_FCR3)

CAN 过滤器组x寄存器 (CAN_FiRx) (i=0..5,x=1..8)

23.12 beCAN寄存器列表

23.12.1 CAN的页映射

24 模拟 / 数字转换器(ADC)

24.1 简介

24.2 主要功能

24.3 扩展(增强)功能

24.4 引脚描述

24.5 功能描述

24.5.1 ADC 开-关控制

24.5.2 ADC 时钟

24.5.3 通道选择

24.5.4 转换模式

单次模式

连续和带缓存的连续模式

单次扫描模式

连续扫描模式

24.5.5 溢出标志位

24.5.6 模拟看门狗

24.5.7 基于外部触发信号的转换

24.5.8 模拟放大

24.5.9 时序图

24.6 低功耗模式

24.7 中断

24.8 数据对齐

24.9 读取转换结果

24.10 施密特触发器禁止寄存器

24.11 寄存器描述

24.11.1 ADC高位数据缓存寄存器(ADC_DBxRH)(x=0..7 or 0..9)

24.11.2 ADC低位数据缓存寄存器(ADC_DBxRL)(x=0..7 or 0..9)

24.11.3 ADC控制/状态寄存器(ADC_CSR)

24.11.4 ADC 配置寄存器1 (ADC_CR1)

24.11.5 ADC 配置寄存器2 (ADC_CR2)

24.11.6 ADC配置寄存器3 (ADC_CR3)

24.11.7 ADC 数据高位寄存器(ADC_DRH)

24.11.8 ADC 数据低位寄存器(ADC_DRL)

24.11.9 ADC 施密特触发器禁止寄存器高位 (ADC_TDRH)

24.11.10 ADC 施密特触发器禁止寄存器低位 (ADC_TDRL)

24.11.11 ADC 上限门槛值高位寄存器(ADC_HTRH)

24.11.12 ADC 上限门槛值低位寄存器(ADC_HTRL)

24.11.13 ADC 下限门槛值高位寄存器(ADC_LTRH)

24.11.14 ADC 下限门槛值低位寄存器(ADC_LTRL)

24.11.15 ADC看门狗状态高位寄存器(ADC_AWSRH)

24.11.16 ADC看门狗状态低位寄存器(ADC_AWSRL)

24.11.17 ADC看门狗控制高位寄存器(ADC_AWCRH)

24.11.18 ADC看门狗控制低位寄存器(ADC_AWCRL)

24.12 ADC寄存器映像表和复位值

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc