5

4

3

2

1

D

C

B

A

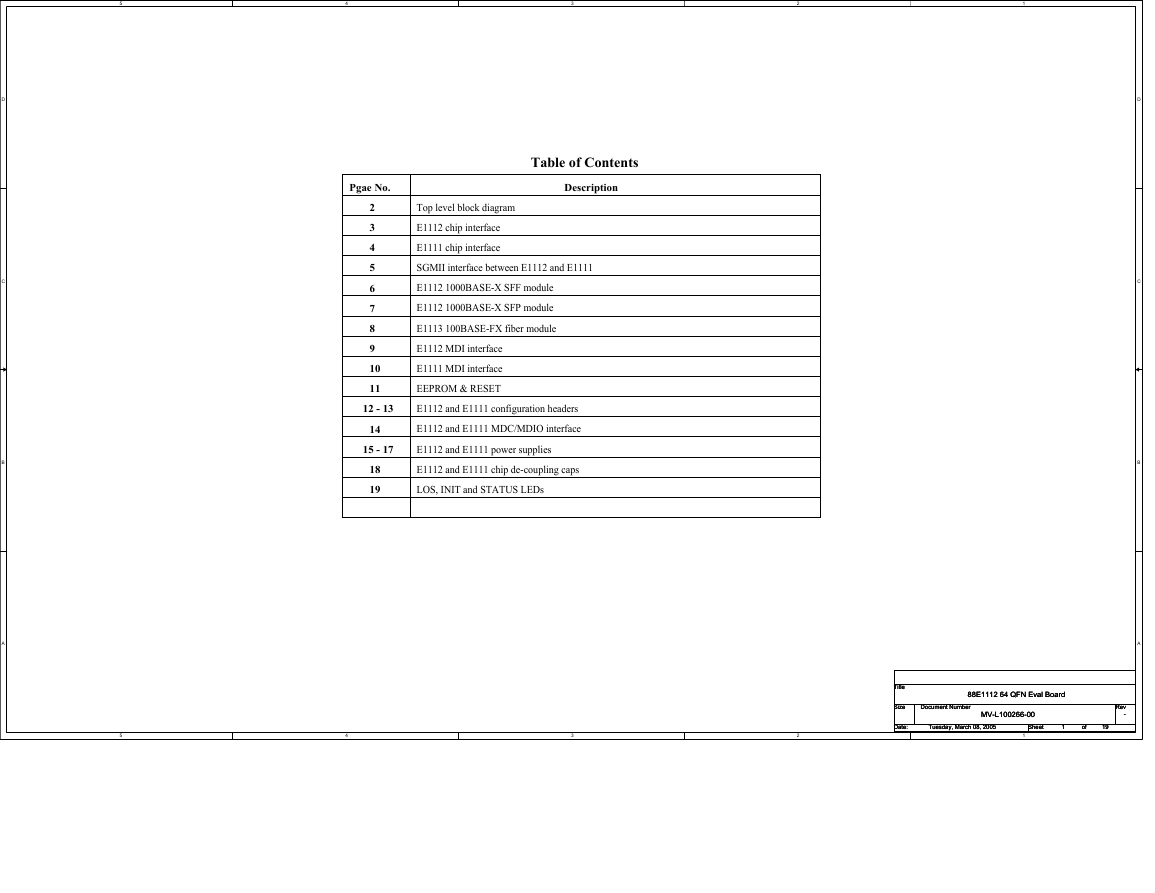

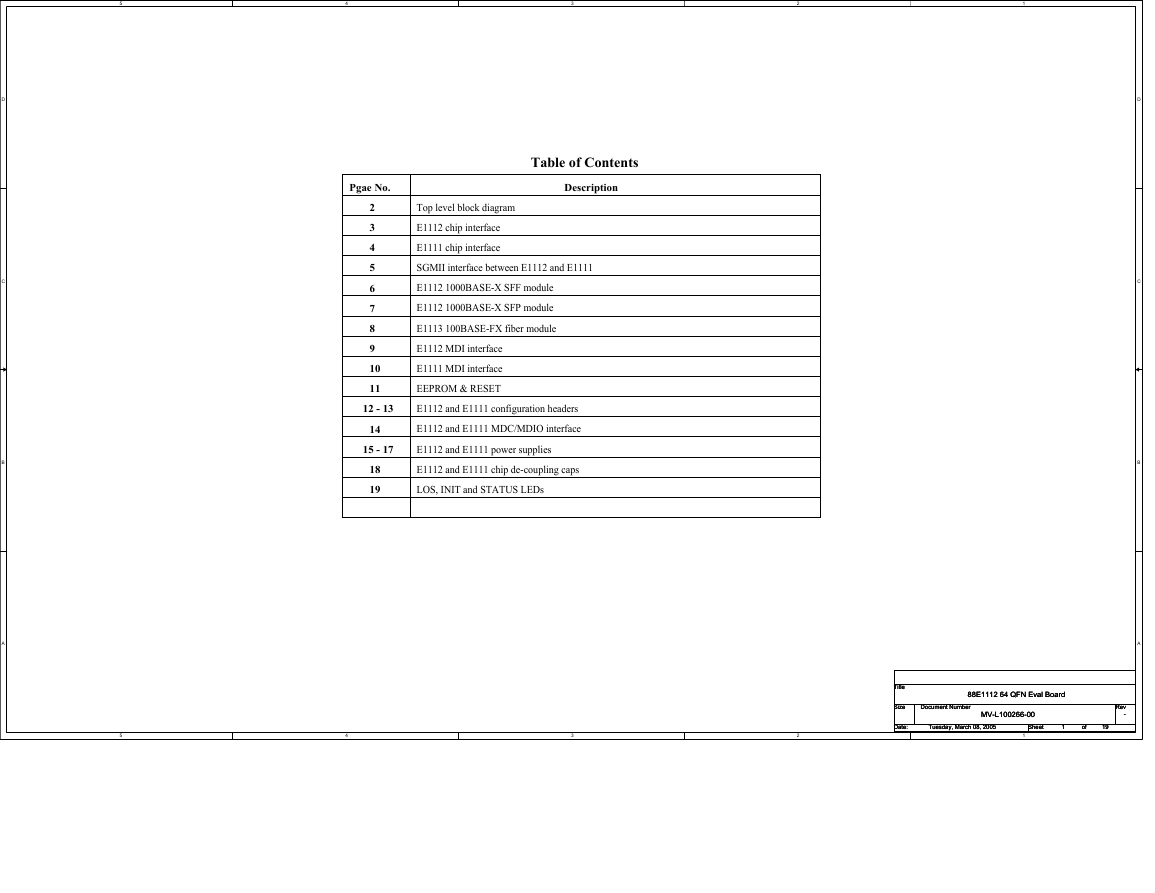

Table of Contents

Description

Top level block diagram

E1112 chip interface

E1111 chip interface

SGMII interface between E1112 and E1111

E1112 1000BASE-X SFF module

E1112 1000BASE-X SFP module

E1113 100BASE-FX fiber module

E1112 MDI interface

E1111 MDI interface

EEPROM & RESET

E1112 and E1111 configuration headers

E1112 and E1111 MDC/MDIO interface

E1112 and E1111 power supplies

E1112 and E1111 chip de-coupling caps

LOS, INIT and STATUS LEDs

Pgae No.

2

3

4

5

6

7

8

9

10

11

12 - 13

14

15 - 17

18

19

D

C

B

A

5

4

3

2

1

Title

Title

Title

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

Size

Size

Size

Document Number

Document Number

Document Number

MV-L100266-00

MV-L100266-00

MV-L100266-00

Rev

Rev

Rev

-

-

-

Date:

Date:

Date:

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Sheet

Sheet

Sheet

1

1

1

of

of

of

19

19

19

�

D

C

B

A

5

4

3

2

1

Top Level Block Diagram

E1112 RJ45

E1112

1000BASE-SFF

E1112

1000BASE-SFP

E1113

100BASE-FX

E1111 RJ45

Magnetic

-

/

+

]

0

:

3

[

I

D

M

_

1

1

1

1

E

T

E

D

S

,

/

N

P

_

T

U

O

F

,

/

N

P

_

N

I

F

Magnetic

-

/

+

]

0

:

3

[

I

D

M

_

2

1

1

1

E

LOS

INIT

POL_RST

NORMAL

SCL

SDA

LED

LED

OSC

XTAL

Switch Control

Serial EEPROM

CONFIG[5:0]

SGMII Interface

SIN_P/N, SOUT_P/N,

SCLK_P/N

E1111

(Copper over SGMII)

E1112/E1113

r

e

w

o

P

1

1

1

1

E

s

e

i

l

p

p

u

S

T

P

T

S

T

/

N

P

_

C

A

D

S

H

]

0

:

1

[

S

U

T

A

T

S

D

E

L

E1112 Power Supplies

E1112_RESET/

Polarity-Change

MDC/MDIO

SYS_RESETN

XTAL

5

4

3

2

1

Title

Title

Title

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

Size

Size

Size

Document Number

Document Number

Document Number

MV-L100266-00

MV-L100266-00

MV-L100266-00

Rev

Rev

Rev

-

-

-

Date:

Date:

Date:

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Sheet

Sheet

Sheet

2

2

2

of

of

of

19

19

19

D

C

B

A

�

5

4

3

2

1

D

C

B

A

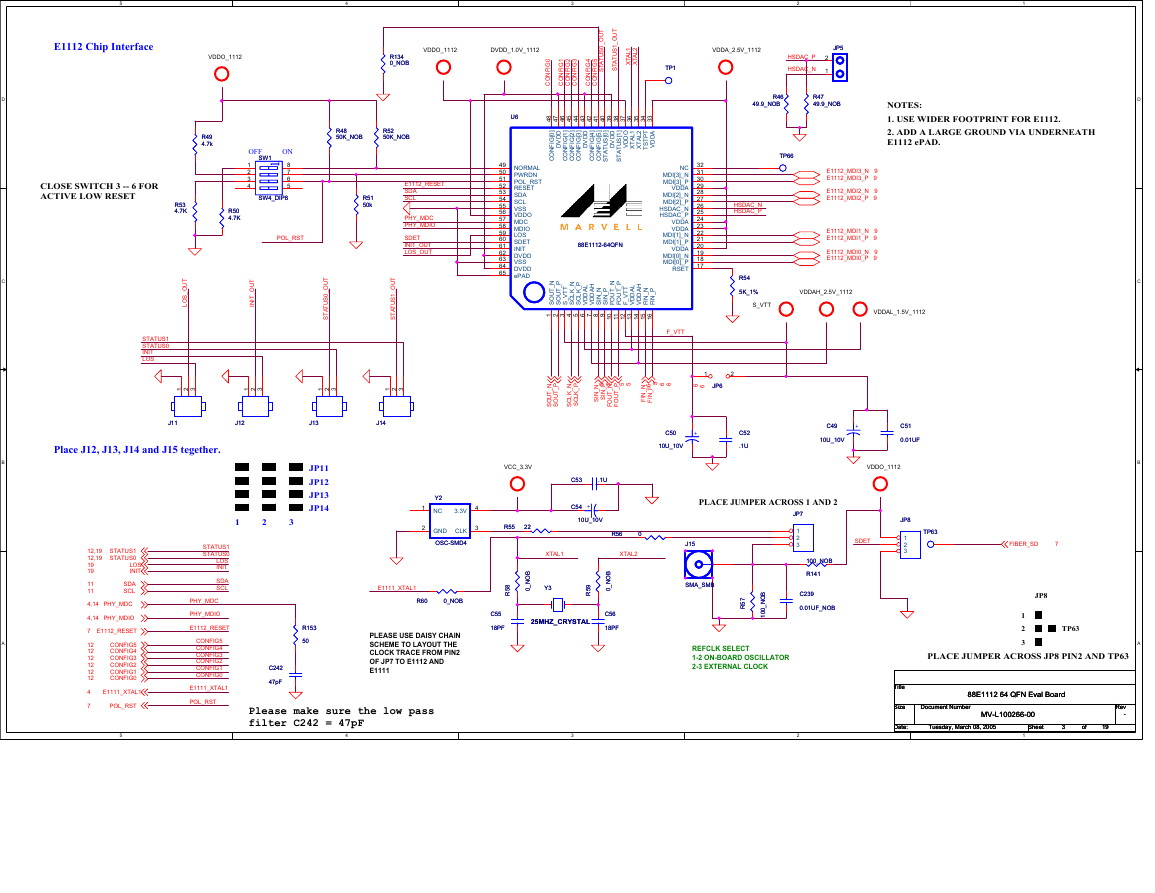

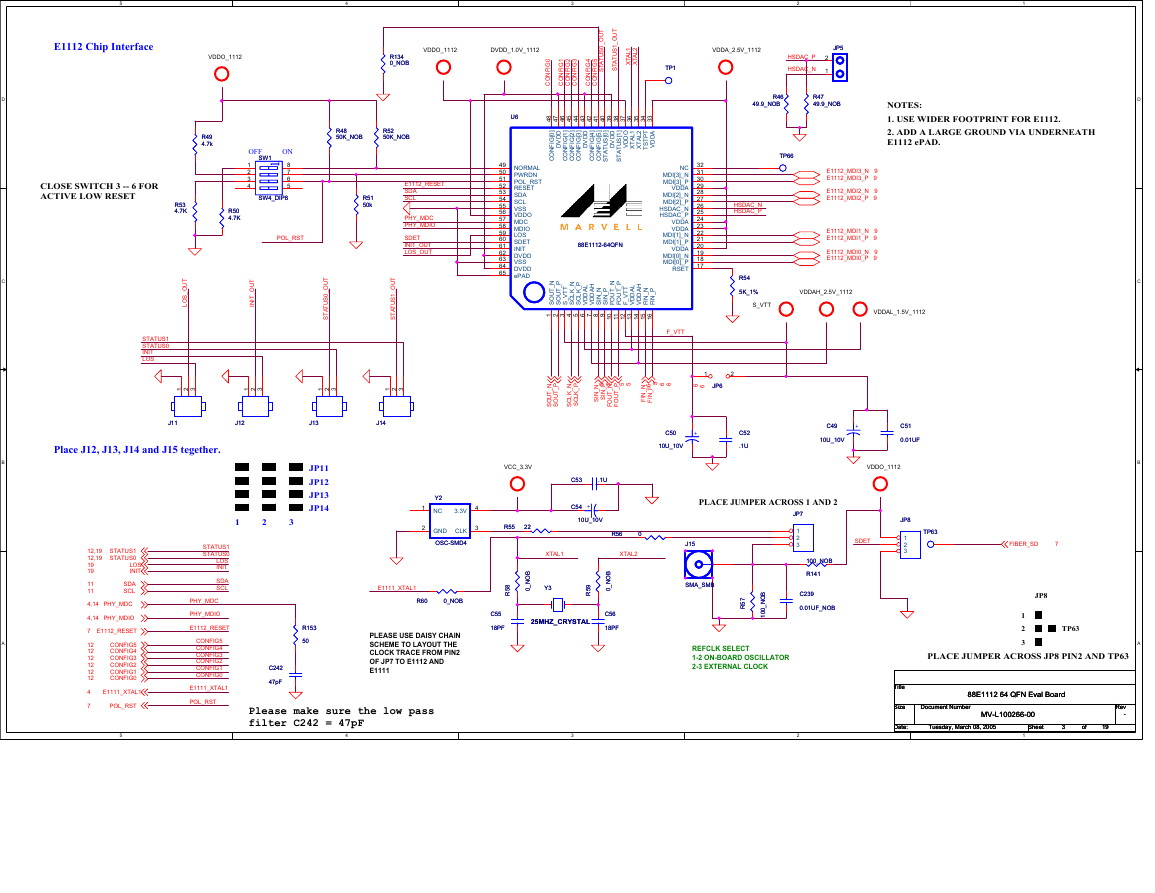

E1112 Chip Interface

VDDO_1112

VDDO_1112

DVDD_1.0V_1112

R134

R134

0_NOB

0_NOB

I

0

G

F

N

O

C

I

I

I

1

G

F

N

O

C

2

G

F

N

O

C

3

G

F

N

O

C

T

U

O

_

0

S

U

T

A

T

S

I

I

4

G

F

N

O

C

5

G

F

N

O

C

T

U

O

_

1

S

U

T

A

T

S

1

L

A

T

X

2

L

A

T

X

TP1TP1

VDDA_2.5V_1112

JP5JP5

HSDAC_P

HSDAC_N

2

1

R46

R46

49.9_NOB

49.9_NOB

R47

R47

49.9_NOB

49.9_NOB

R49

R49

4.7k

4.7k

R53

R53

4.7K

4.7K

T

U

O

_

S

O

L

CLOSE SWITCH 3 -- 6 FOR

ACTIVE LOW RESET

STATUS1

STATUS0

INIT

LOS

R48

R48

50K_NOB

50K_NOB

R52

R52

50K_NOB

50K_NOB

OFF

SW1

SW1

ON

8

7

6

5

R50

R50

4.7K

4.7K

1

2

3

4

T

U

O

_

T

N

I

I

SW4_DIP8

SW4_DIP8

R51

R51

50k

50k

POL_RST

T

U

O

_

0

S

U

T

A

T

S

T

U

O

_

1

S

U

T

A

T

S

E1112_RESET

SDA

SCL

PHY_MDC

PHY_MDIO

SDET

INIT_OUT

LOS_OUT

U6

U6

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

NORMAL

PWRDN

POL_RST

RESET

SDA

SCL

VSS

VDDO

MDC

MDIO

LOS

SDET

INIT

DVDD

VSS

DVDD

ePAD

8

4

7

4

6

4

5

4

4

4

3

4

2

4

1

4

0

4

9

3

8

3

7

3

6

3

5

3

4

3

3

3

D

D

V

D

]

[

I

0

G

F

N

O

C

D

D

V

D

]

]

]

[

I

[

I

[

I

1

G

F

N

O

C

2

G

F

N

O

C

3

G

F

N

O

C

]

]

]

[

[

I

[

I

4

G

F

N

O

C

5

G

F

N

O

C

0

S

U

T

A

T

S

D

D

V

D

]

[

1

S

U

T

A

T

S

O

D

D

V

1

L

A

T

X

2

L

A

T

X

T

P

T

S

T

A

D

D

V

88E1112-64QFN

88E1112-64QFN

N

_

T

U

O

S

P

_

T

U

O

S

N

_

K

L

C

S

P

_

K

L

C

S

L

A

D

D

V

H

A

D

D

V

T

T

V

_

S

N

_

T

U

O

F

P

_

T

U

O

F

N

_

N

S

P

_

N

S

I

I

L

A

D

D

V

H

A

D

D

V

T

T

V

_

F

N

_

N

F

P

_

N

F

I

I

1

2

3

4

5

6

7

8

9

0

1

1

1

2

1

3

1

4

1

5

1

6

1

TP66

TP66

HSDAC_N

HSDAC_P

E1112_MDI3_N 9

E1112_MDI3_P 9

E1112_MDI2_N 9

E1112_MDI2_P 9

E1112_MDI1_N 9

E1112_MDI1_P 9

E1112_MDI0_N 9

E1112_MDI0_P 9

R54

R54

5K_1%

5K_1%

S_VTT

VDDAH_2.5V_1112

VDDAL_1.5V_1112

NC 32

MDI[3]_N 31

MDI[3]_P 30

VDDA 29

MDI[2]_N 28

MDI[2]_P 27

HSDAC_N 26

HSDAC_P 25

VDDA 24

VDDA 23

MDI[1]_N 22

MDI[1]_P 21

VDDA 20

MDI[0]_N 19

MDI[0]_P 18

17

RSET

F_VTT

NOTES:

1. USE WIDER FOOTPRINT FOR E1112.

2. ADD A LARGE GROUND VIA UNDERNEATH

E1112 ePAD.

123

123

123

123

J11J11

J12J12

J13J13

J14J14

N

_

T

U

O

S

P

_

T

U

O

S

N

_

K

L

C

S

P

_

K

L

C

S

Place J12, J13, J14 and J15 tegether.

1

2

6

6

JP6JP6

5

6

6

N

_

N

F

5

P

_

N

F

I

I

5

5

5

P

_

N

S

N

_

N

S

I

I

5

N

_

T

U

O

F

P

_

T

U

O

F

JP11

JP12

JP13

JP14

1

2

3

R153

R153

50

50

C242

C242

47pF

47pF

VCC_3.3V

R55

R55

22

22

C53

C53

.1U

.1U

+C54

+C54

10U_10V

10U_10V

R56

R56

0

0

XTAL1

XTAL2

B

B

O

O

N

N

_

_

0

0

Y3

Y3

8

8

5

5

R

R

B

B

O

O

N

N

_

_

0

0

9

9

5

5

R

R

C55

C55

18PF

18PF

25MHZ_CRYSTAL

25MHZ_CRYSTAL

C56

C56

18PF

18PF

1

2

Y2

Y2

NC

3.3V 4

GND

CLK 3

OSC-SMD4

OSC-SMD4

E1111_XTAL1

R60

R60

0_NOB

0_NOB

PLEASE USE DAISY CHAIN

SCHEME TO LAYOUT THE

CLOCK TRACE FROM PIN2

OF JP7 TO E1112 AND

E1111

Please make sure the low pass

filter C242 = 47pF

12,19

12,19

19

19

11

11

STATUS1

STATUS0

LOS

INIT

SDA

SCL

4,14

PHY_MDC

4,14

PHY_MDIO

7

E1112_RESET

12

12

12

12

12

12

4

7

CONFIG5

CONFIG4

CONFIG3

CONFIG2

CONFIG1

CONFIG0

E1111_XTAL1

POL_RST

STATUS1

STATUS0

LOS

INIT

SDA

SCL

PHY_MDC

PHY_MDIO

E1112_RESET

CONFIG5

CONFIG4

CONFIG3

CONFIG2

CONFIG1

CONFIG0

E1111_XTAL1

POL_RST

C50

C50

+

+

10U_10V

10U_10V

C52

C52

.1U

.1U

C49

C49

+

+

10U_10V

10U_10V

C51

C51

0.01UF

0.01UF

VDDO_1112

PLACE JUMPER ACROSS 1 AND 2

JP7JP7

1

2

3

100_NOB

100_NOB

R141

R141

C239

C239

0.01UF_NOB

0.01UF_NOB

J15

J15

SMA_SMB

SMA_SMB

7

7

5

5

R

R

B

B

O

O

N

N

_

_

0

0

0

0

1

1

REFCLK SELECT

1-2 ON-BOARD OSCILLATOR

2-3 EXTERNAL CLOCK

SDET

TP63

TP63

JP8JP8

1

2

3

FIBER_SD

7

JP8

1

2

3

TP63

PLACE JUMPER ACROSS JP8 PIN2 AND TP63

Title

Title

Title

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

Size

Size

Size

Document Number

Document Number

Document Number

MV-L100266-00

MV-L100266-00

MV-L100266-00

Rev

Rev

Rev

-

-

-

Date:

Date:

Date:

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Sheet

Sheet

Sheet

3

3

3

of

of

of

19

19

19

5

4

3

2

1

D

C

B

A

�

D

C

B

A

5

4

3

2

1

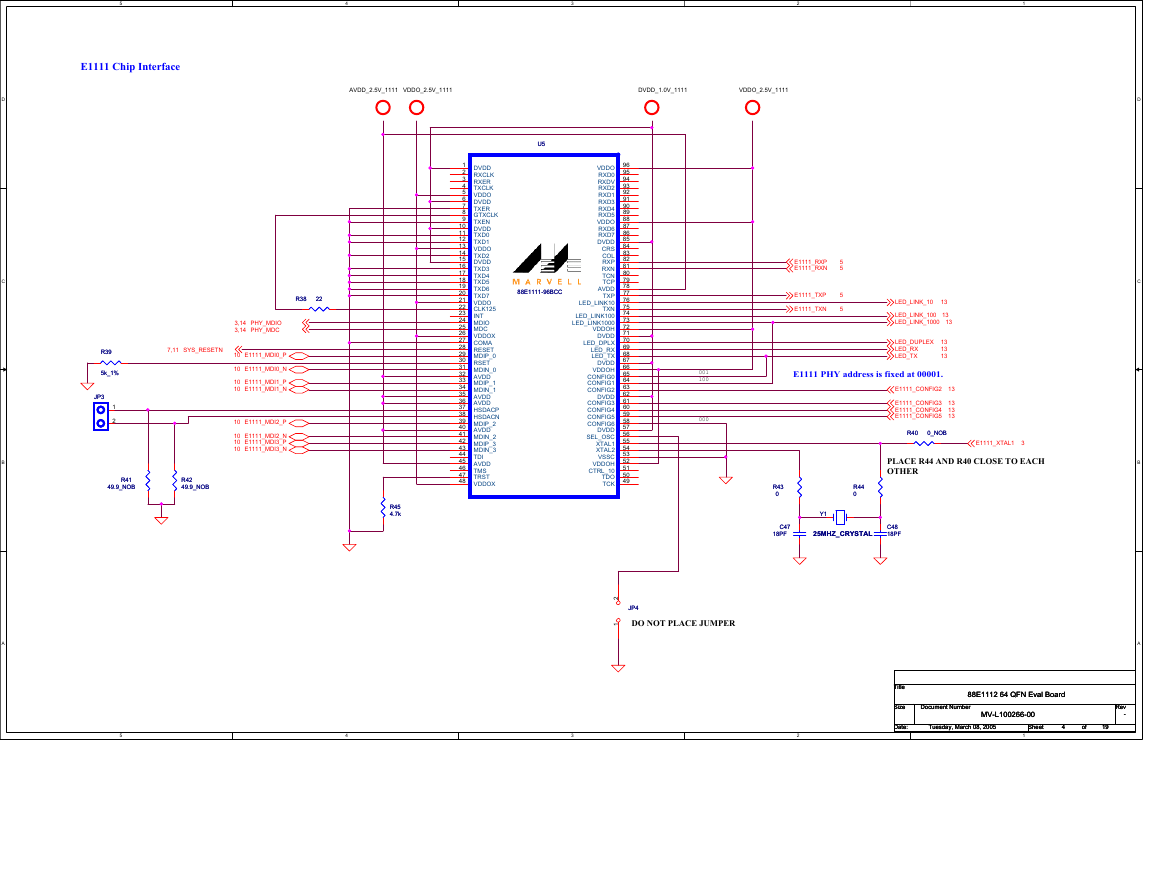

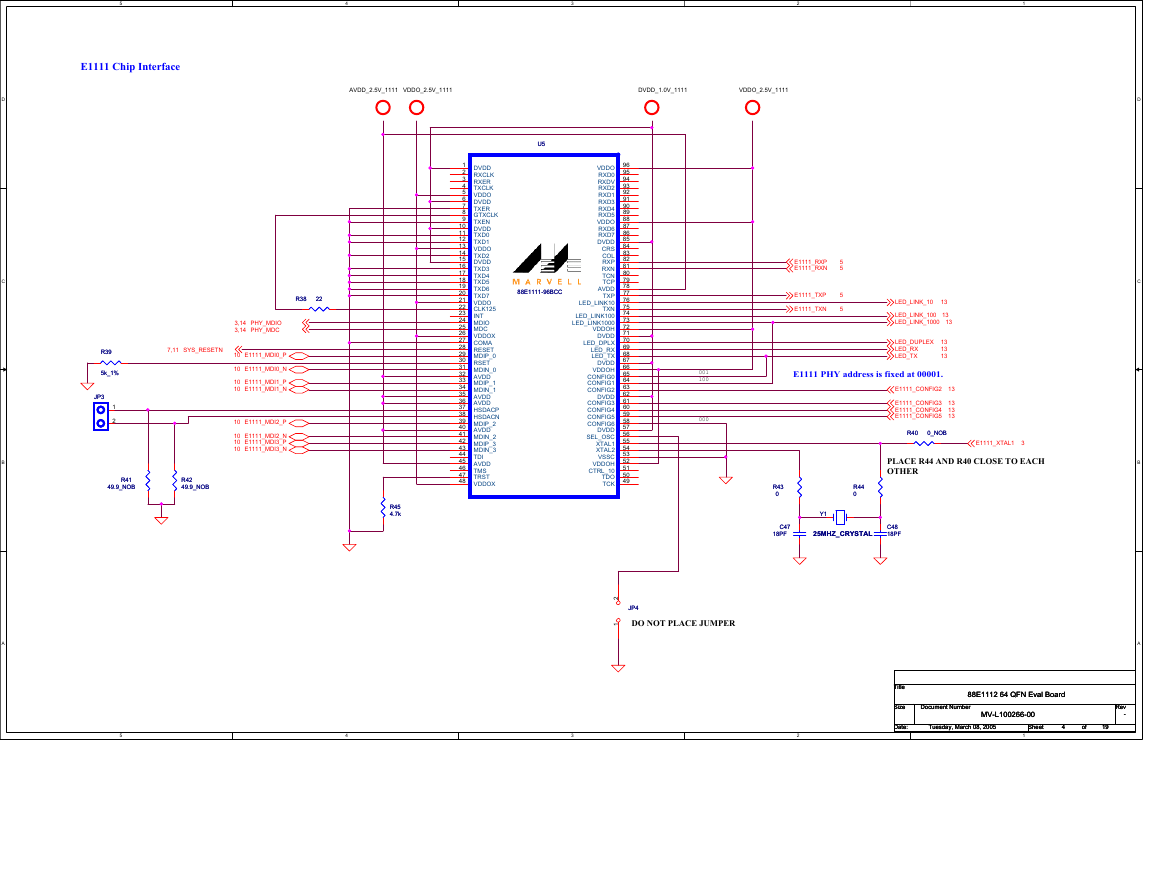

E1111 Chip Interface

AVDD_2.5V_1111

VDDO_2.5V_1111

DVDD_1.0V_1111

VDDO_2.5V_1111

U5

U5

88E1111-96BCC

88E1111-96BCC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

DVDD

RXCLK

RXER

TXCLK

VDDO

DVDD

TXER

GTXCLK

TXEN

DVDD

TXD0

TXD1

VDDO

TXD2

DVDD

TXD3

TXD4

TXD5

TXD6

TXD7

VDDO

CLK125

INT

MDIO

MDC

VDDOX

COMA

RESET

MDIP_0

RSET

MDIN_0

AVDD

MDIP_1

MDIN_1

AVDD

AVDD

HSDACP

HSDACN

MDIP_2

AVDD

MDIN_2

MDIP_3

MDIN_3

TDI

AVDD

TMS

TRST

VDDOX

R38

R38

22

22

3,14

3,14

PHY_MDIO

PHY_MDC

10

E1111_MDI0_P

10

E1111_MDI0_N

10

10

E1111_MDI1_P

E1111_MDI1_N

10

E1111_MDI2_P

10

10

10

E1111_MDI2_N

E1111_MDI3_P

E1111_MDI3_N

7,11

SYS_RESETN

R39

R39

5k_1%

5k_1%

JP3JP3

1

2

R41

R41

49.9_NOB

49.9_NOB

R42

R42

49.9_NOB

49.9_NOB

R45

R45

4.7k

4.7k

LED_LINK10

LED_LINK100

LED_LINK1000

VDDO 96

95

RXD0

RXDV 94

93

RXD2

92

RXD1

91

RXD3

90

RXD4

89

RXD5

VDDO 88

87

RXD6

86

RXD7

DVDD 85

CRS 84

83

COL

RXP 82

RXN 81

TCN 80

TCP 79

AVDD 78

TXP 77

76

TXN 75

74

73

VDDOH 72

DVDD 71

LED_DPLX 70

LED_RX 69

LED_TX 68

DVDD 67

VDDOH 66

65

CONFIG0

64

CONFIG1

63

CONFIG2

DVDD 62

61

CONFIG3

60

CONFIG4

59

CONFIG5

58

CONFIG6

DVDD 57

SEL_OSC 56

55

XTAL1

54

XTAL2

VSSC 53

VDDOH 52

51

CTRL_10

TDO 50

TCK 49

001

100

000

E1111_RXP

E1111_RXN

E1111_TXP

E1111_TXN

5

5

5

5

LED_LINK_10

13

LED_LINK_100 13

LED_LINK_1000 13

LED_DUPLEX 13

LED_RX

13

13

LED_TX

E1111 PHY address is fixed at 00001.

E1111_CONFIG2 13

E1111_CONFIG3 13

E1111_CONFIG4 13

E1111_CONFIG5 13

R40

R40

0_NOB

0_NOB

E1111_XTAL1

3

PLACE R44 AND R40 CLOSE TO EACH

OTHER

R43

R43

0

0

C47

C47

18PF

18PF

R44

R44

0

0

Y1

Y1

25MHZ_CRYSTAL

25MHZ_CRYSTAL

C48

C48

18PF

18PF

2

1

JP4JP4

DO NOT PLACE JUMPER

5

4

3

2

1

Title

Title

Title

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

Size

Size

Size

Document Number

Document Number

Document Number

MV-L100266-00

MV-L100266-00

MV-L100266-00

Rev

Rev

Rev

-

-

-

Date:

Date:

Date:

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Sheet

Sheet

Sheet

4

4

4

of

of

of

19

19

19

D

C

B

A

�

5

4

3

2

1

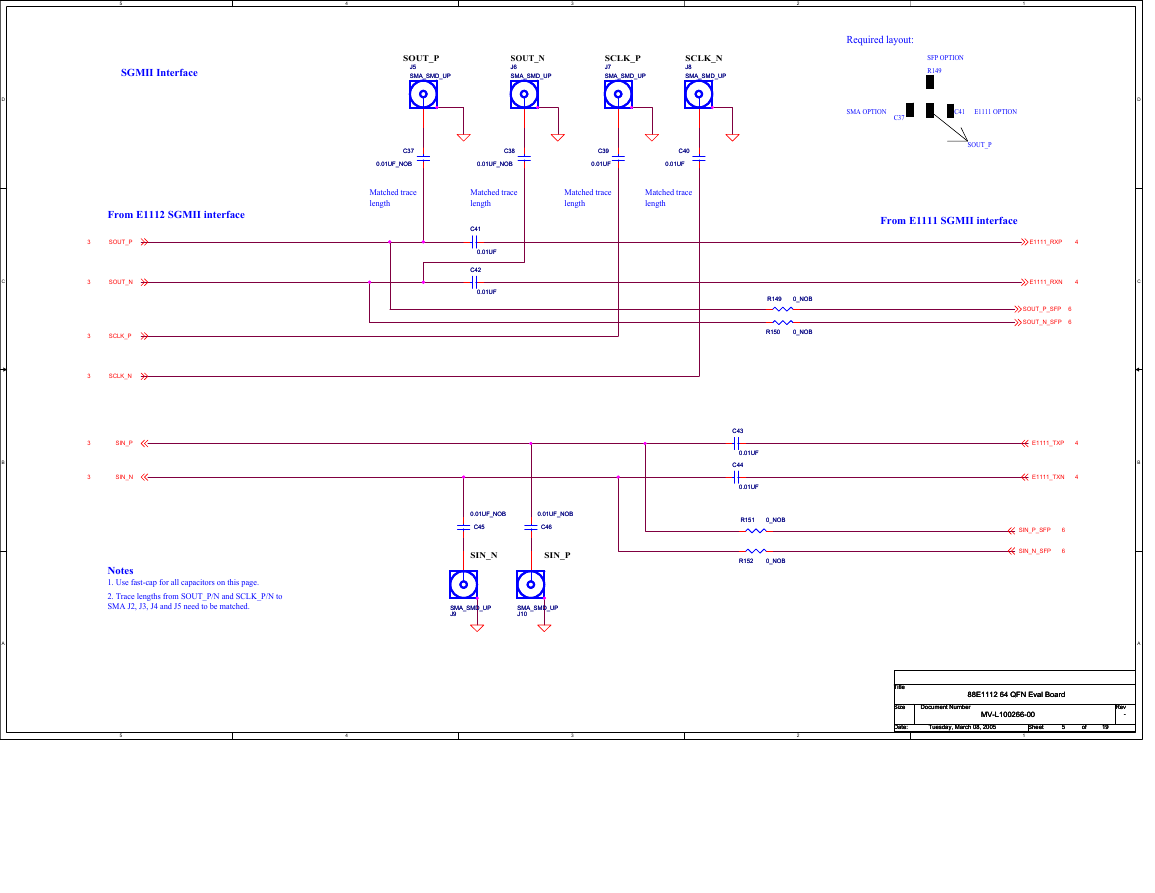

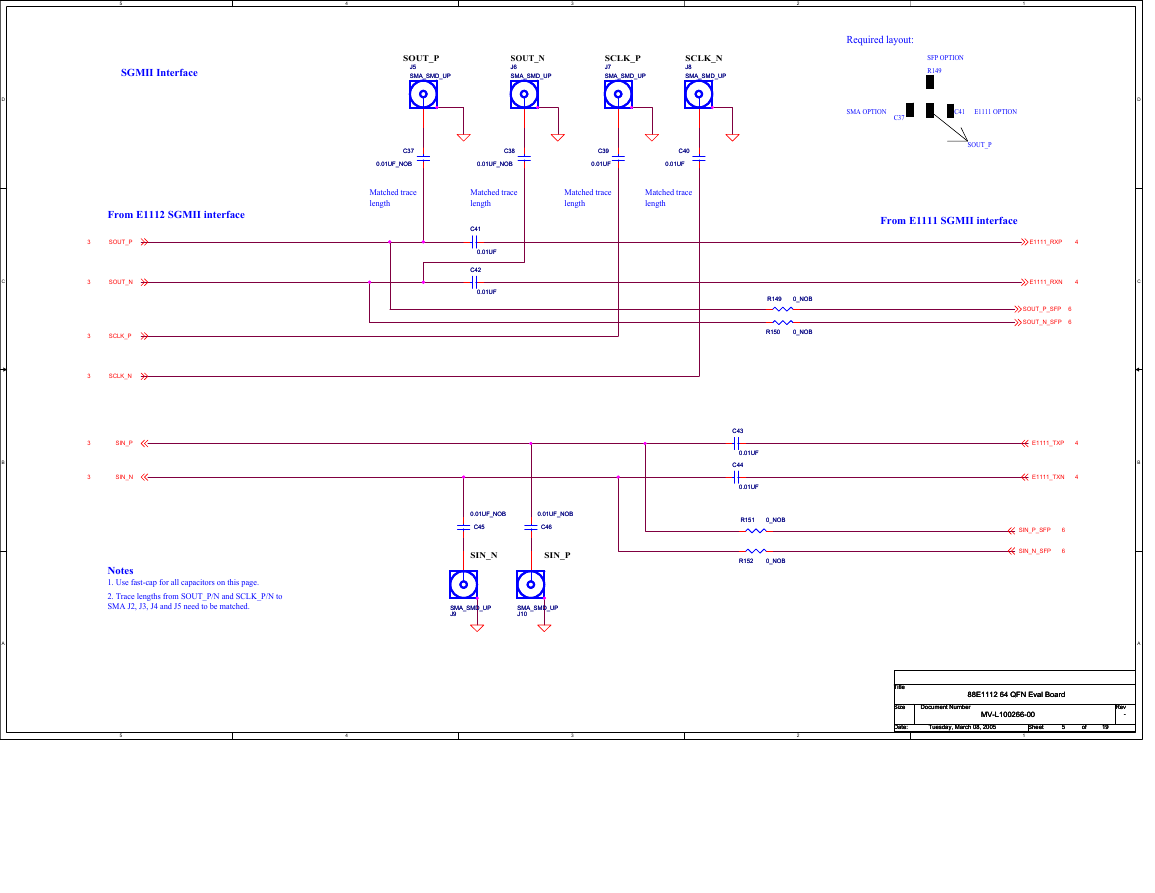

SGMII Interface

SOUT_P

J5

J5

SMA_SMD_UP

SMA_SMD_UP

SOUT_N

J6

J6

SMA_SMD_UP

SMA_SMD_UP

SCLK_P

J7

J7

SMA_SMD_UP

SMA_SMD_UP

SCLK_N

J8

J8

SMA_SMD_UP

SMA_SMD_UP

From E1112 SGMII interface

C37

C37

0.01UF_NOB

0.01UF_NOB

Matched trace

length

C38

C38

0.01UF_NOB

0.01UF_NOB

C39

C39

0.01UF

0.01UF

C40

C40

0.01UF

0.01UF

Matched trace

length

Matched trace

length

Matched trace

length

C41

C41

0.01UF

0.01UF

C42

C42

0.01UF

0.01UF

3

3

3

3

3

3

SOUT_P

SOUT_N

SCLK_P

SCLK_N

SIN_P

SIN_N

Notes

1. Use fast-cap for all capacitors on this page.

2. Trace lengths from SOUT_P/N and SCLK_P/N to

SMA J2, J3, J4 and J5 need to be matched.

0.01UF_NOB

0.01UF_NOB

0.01UF_NOB

0.01UF_NOB

C45

C45

C46

C46

SIN_N

SIN_P

SMA_SMD_UP

SMA_SMD_UP

J9

J9

SMA_SMD_UP

SMA_SMD_UP

J10

J10

D

C

B

A

Required layout:

SFP OPTION

R149

SMA OPTION

C37

C41

E1111 OPTION

SOUT_P

D

From E1111 SGMII interface

E1111_RXP

4

E1111_RXN

4

C

SOUT_P_SFP 6

SOUT_N_SFP 6

E1111_TXP

E1111_TXN

4

4

SIN_P_SFP

SIN_N_SFP

6

6

B

A

Title

Title

Title

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

Size

Size

Size

Document Number

Document Number

Document Number

MV-L100266-00

MV-L100266-00

MV-L100266-00

Rev

Rev

Rev

-

-

-

Date:

Date:

Date:

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Sheet

Sheet

Sheet

5

5

5

of

of

of

19

19

19

R149

R149

0_NOB

0_NOB

R150

R150

0_NOB

0_NOB

C43

C43

0.01UF

0.01UF

C44

C44

0.01UF

0.01UF

R151

R151

0_NOB

0_NOB

R152

R152

0_NOB

0_NOB

5

4

3

2

1

�

5

4

3

J1

J1

SMA_SMD_UP

SMA_SMD_UP

J2

J2

SMA_SMD_UP

SMA_SMD_UP

2

1

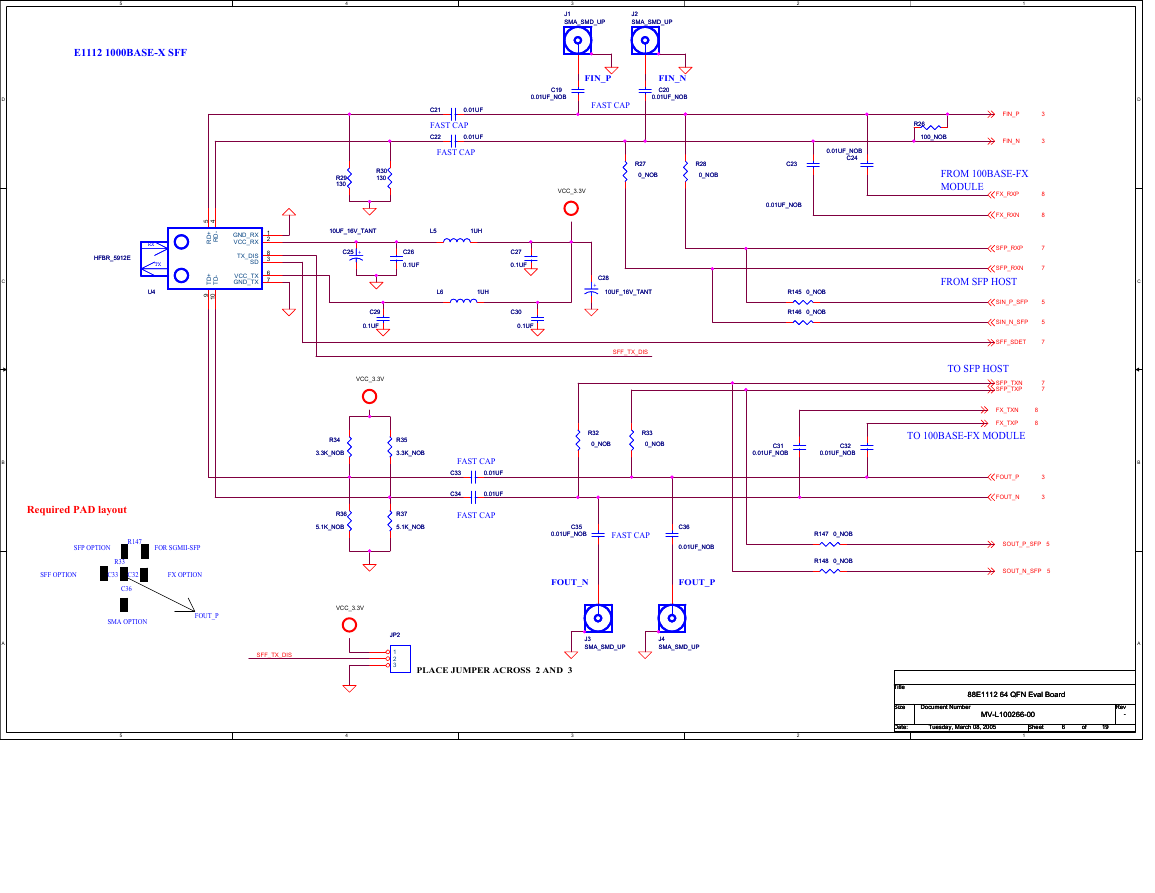

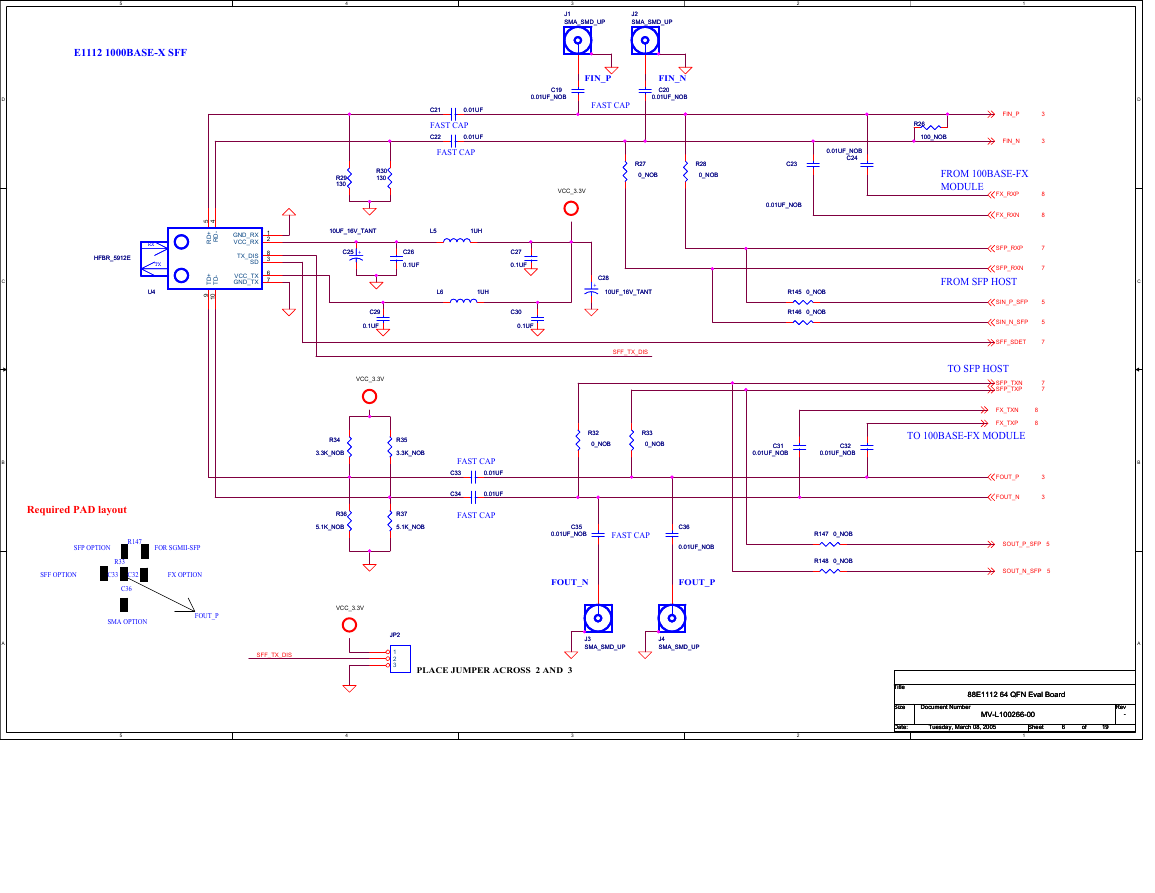

E1112 1000BASE-X SFF

HFBR_5912E

HFBR_5912E

RX

RX

TX

TX

U4

U4

C19

C19

0.01UF_NOB

0.01UF_NOB

FIN_P

FAST CAP

FIN_N

C20

C20

0.01UF_NOB

0.01UF_NOB

0.01UF

0.01UF

C21

C21

FAST CAP

C22

C22

0.01UF

0.01UF

FAST CAP

R30

R30

130

130

R29

R29

130

130

R27

R27

0_NOB

0_NOB

R28

R28

0_NOB

0_NOB

VCC_3.3V

0.01UF_NOB

0.01UF_NOB

C24

C24

C23

C23

0.01UF_NOB

0.01UF_NOB

5

4

+

D

R

-

D

R

+

D

T

-

D

T

GND_RX 1

VCC_RX 2

TX_DIS 8

SD 3

VCC_TX 6

GND_TX 7

10UF_16V_TANT

10UF_16V_TANT

L5

L5

1UH

1UH

C25

C25

+

+

C26

C26

0.1UF

0.1UF

9

0

1

L6

L6

1UH

1UH

C29

C29

0.1UF

0.1UF

VCC_3.3V

C27

C27

0.1UF

0.1UF

C30

C30

0.1UF

0.1UF

+

+

C28

C28

10UF_16V_TANT

10UF_16V_TANT

SFF_TX_DIS

R145 0_NOB

R145 0_NOB

R146 0_NOB

R146 0_NOB

Required PAD layout

SFP OPTION

R147

R33

FOR SGMII-SFP

SFF OPTION

C33

C32

FX OPTION

C36

SMA OPTION

FOUT_P

R34

R34

3.3K_NOB

3.3K_NOB

R35

R35

3.3K_NOB

3.3K_NOB

R36

R36

5.1K_NOB

5.1K_NOB

R37

R37

5.1K_NOB

5.1K_NOB

FAST CAP

C33

C33

C34

C34

0.01UF

0.01UF

0.01UF

0.01UF

FAST CAP

R32

R32

0_NOB

0_NOB

R33

R33

0_NOB

0_NOB

C31

C31

0.01UF_NOB

0.01UF_NOB

C32

C32

0.01UF_NOB

0.01UF_NOB

C35

C35

0.01UF_NOB

0.01UF_NOB

FAST CAP

FOUT_N

C36

C36

0.01UF_NOB

0.01UF_NOB

FOUT_P

R147 0_NOB

R147 0_NOB

R148 0_NOB

R148 0_NOB

VCC_3.3V

JP2JP2

1

2

3

SFF_TX_DIS

PLACE JUMPER ACROSS 2 AND 3

J3

J3

SMA_SMD_UP

SMA_SMD_UP

J4

J4

SMA_SMD_UP

SMA_SMD_UP

D

C

B

A

R26

R26

100_NOB

100_NOB

FIN_P

FIN_N

FROM 100BASE-FX

MODULE

FX_RXP

FX_RXN

SFP_RXP

SFP_RXN

FROM SFP HOST

SIN_P_SFP

SIN_N_SFP

SFF_SDET

TO SFP HOST

SFP_TXN

SFP_TXP

FX_TXN

FX_TXP

8

8

TO 100BASE-FX MODULE

FOUT_P

FOUT_N

3

3

8

8

7

7

5

5

7

7

7

3

3

SOUT_P_SFP 5

SOUT_N_SFP 5

D

C

B

A

5

4

3

2

1

Title

Title

Title

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

Size

Size

Size

Document Number

Document Number

Document Number

MV-L100266-00

MV-L100266-00

MV-L100266-00

Rev

Rev

Rev

-

-

-

Date:

Date:

Date:

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Sheet

Sheet

Sheet

6

6

6

of

of

of

19

19

19

�

5

4

3

2

1

E1112 1000BASE-X SFP

VCC_3.3V

14

14

SFP_MOD2

SFP_MOD1

SFP_MOD2

SFP_MOD1

D

C

B

A

8

8

1

1

R

R

9

9

1

1

R

R

0

0

2

2

R

R

1

1

2

2

R

R

2

2

2

2

R

R

K

K

0

0

1

1

K

K

0

0

1

1

K

K

0

0

1

1

K

K

0

0

1

1

K

K

0

0

1

1

1

2

3

4

5

6

7

8

9

10

U2

U2

VeeT

TxFault

Tx Disable

MOD-DEF_2

MOD-DEF_1

MOD-DEF_0

Rate Select

LOS

VeeR

VeeR

SFP_HOST

SFP_HOST

20

VeeT

19

TD-

18

TD+

17

VeeT

16

VccT

VccR 15

VeeR 14

13

RD+

12

RD-

VeeR 11

L3

L3

1UH

1UH

C11

C11

0.1UF

0.1UF

L4

L4

1UH

1UH

C16

C16

0.1UF

0.1UF

+

+

C14

C14

10UF_16V_TANT

10UF_16V_TANT

C15

C15

0.1UF

0.1UF

JP62

TP68

TP68

TP68

1

JP62

JP62

1

2

3

1

2

3

VCC_2.5V_1111

JP1JP1

3

2

1

FIBER_SD_IN

FIBER_SD

PLACE JUMPER OVER 1 AND 2

FOR SDET ONLY

VCC_2.5V_1111

C17

C17

0.1UF

0.1UF

U3

U3

1A

1B

1Y

2A

2B

2Y

GND

1

2

3

4

5

6

7

VCC 14

4B 13

4A 12

4Y 11

3B 10

3A 9

3Y 8

CD74AC86M

CD74AC86M

SYS_RESETN

POL_RST

TP69

TP69

1

JP63

JP63

2

1

TP70

TP70

1

Layout recommendation

TP69

1

2

JP63

TP70

L

A B Y

L

L

HHL

HLH

HH

L

SFP_TXN

SFP_TXP

6

6

VCC_3.3V

+ C12

+ C12

10UF_16V_TANT

10UF_16V_TANT

C13

C13

0.1UF

0.1UF

FIBER_SD_IN

SFP_RXP 6

SFP_RXN 6

FX_SDET

SFF_SDET

8

6

FIBER_SD

3

SYS_RESETN 4,11

E1112_RESET 3

POL_RST

3

R24

R24

1K_NOB

1K_NOB

E1112_RESET

C18

C18

0.1UF_NOB

0.1UF_NOB

D

C

B

A

Title

Title

Title

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

Size

Size

Size

Document Number

Document Number

Document Number

MV-L100266-00

MV-L100266-00

MV-L100266-00

Rev

Rev

Rev

-

-

-

Date:

Date:

Date:

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Sheet

Sheet

Sheet

7

7

7

of

of

of

19

19

19

5

4

3

2

1

�

5

4

3

2

1

D

C

B

A

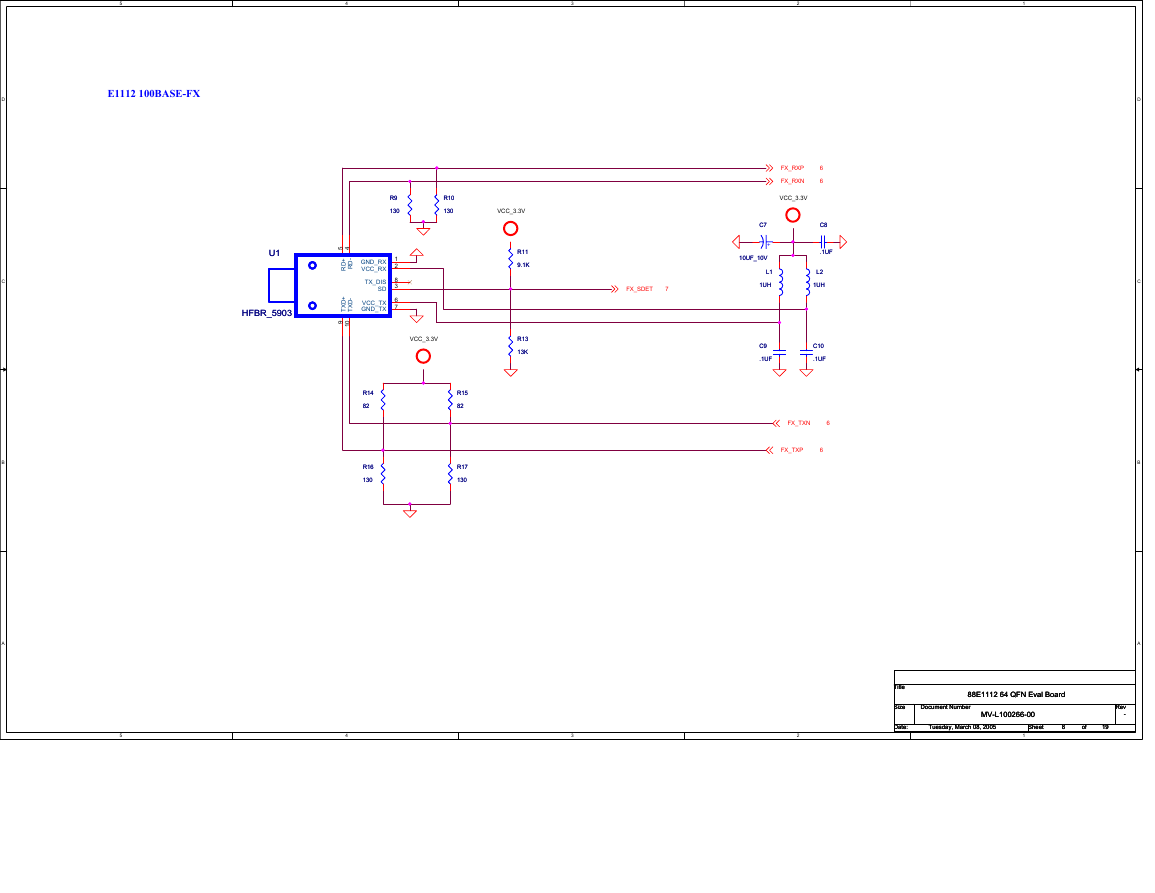

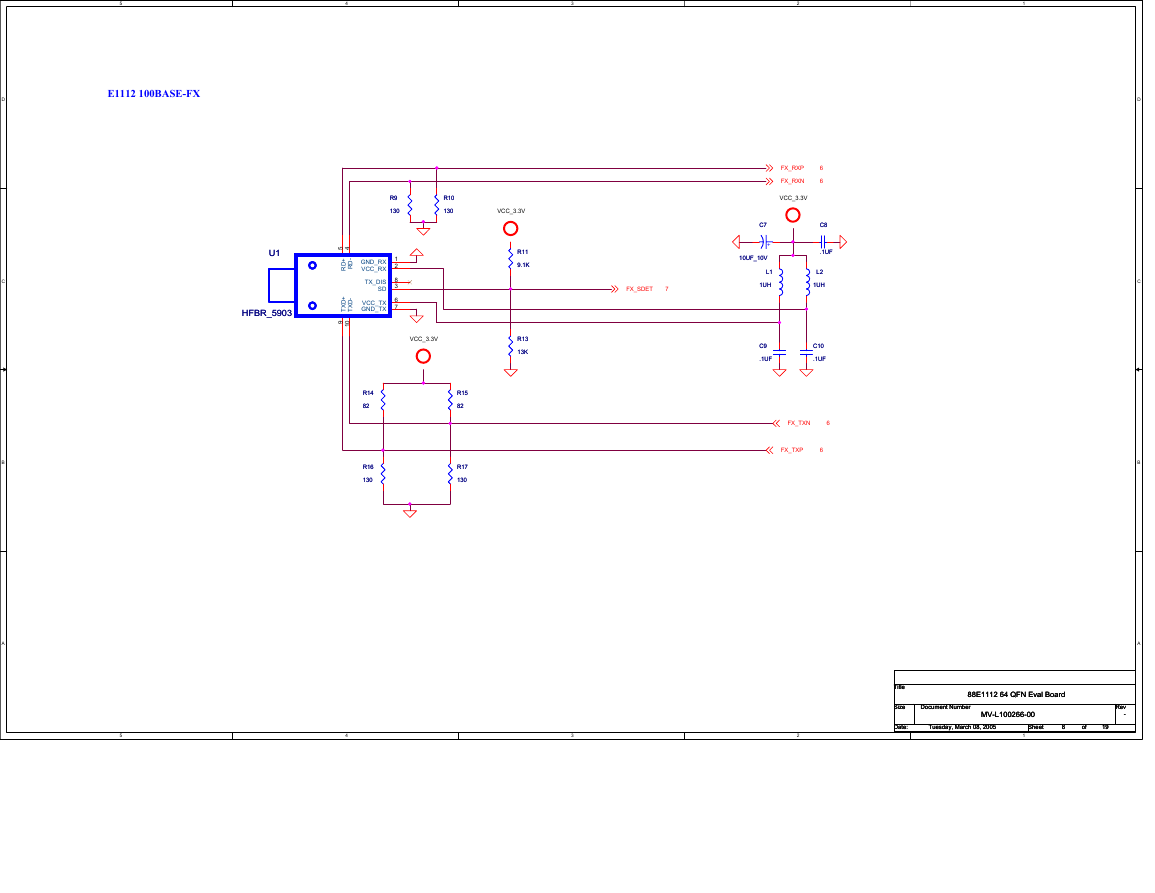

E1112 100BASE-FX

U1

U1

5

4

+

D

R

-

D

R

HFBR_5903

HFBR_5903

+

D

X

T

-

D

X

T

GND_RX 1

VCC_RX 2

TX_DIS 8

SD 3

VCC_TX 6

GND_TX 7

9

0

1

VCC_3.3V

R14

R14

82

82

R16

R16

130

130

R15

R15

82

82

R17

R17

130

130

R9

R9

130

130

R10

R10

130

130

VCC_3.3V

R11

R11

9.1K

9.1K

R13

R13

13K

13K

FX_SDET

7

FX_RXP

FX_RXN

6

6

VCC_3.3V

C7

C7

+

+

10UF_10V

10UF_10V

L1

L1

1UH

1UH

C8

C8

.1UF

.1UF

L2

L2

1UH

1UH

C9

C9

.1UF

.1UF

C10

C10

.1UF

.1UF

FX_TXN

6

FX_TXP

6

D

C

B

A

5

4

3

2

1

Title

Title

Title

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

88E1112 64 QFN Eval Board

Size

Size

Size

Document Number

Document Number

Document Number

MV-L100266-00

MV-L100266-00

MV-L100266-00

Rev

Rev

Rev

-

-

-

Date:

Date:

Date:

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Tuesday, March 08, 2005

Sheet

Sheet

Sheet

8

8

8

of

of

of

19

19

19

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc