Xxxxxxxxx

课 程 设 计 报 告

课程设计名称:计算机组成原理课程设计

课程设计题目:阵列除法器的设计

院(系):xxxxxxxxx

专

班

学

姓

业:xxxxxxxxx

级:xxxxxxxxx

号:xxxxxxxxxxx

名:xxxxxxxxxxxxx

指导教师:xxxxxxxxxxxx

完成日期:xxxxxxxxxxxxxxx

�

沈阳航空工业学院课程设计报告

目

录

第 1 章 总体设计方案.................................................................................................. 1

1.1 设计原理...............................................................................................................1

1.2 设计思路.............................................................................................................3

1.3 设计环境...............................................................................................................4

第 2 章 详细设计方案.................................................................................................. 7

2.1 顶层方案图的设计与实现...................................................................................7

2.1.1 创建顶层图形设计文件...................................................................................7

2.1.2 器件的选择与引脚锁定...................................................................................8

2.1.3 编译、综合、适配...........................................................................................9

2.2 功能模块的设计与实现.......................................................................................9

2.3 仿真调试.............................................................................................................11

第 3 章 编程下载与硬件测试.................................................................................... 14

3.1 编程下载.............................................................................................................14

3.2 硬件测试及结果分析.........................................................................................14

参考文献.........................................................................................................................16

附录(电路原理图).................................................................................................... 17

-I-

�

沈阳航空工业学院课程设计报告

第 1 章 总体设计方案

1.1 设计原理

阵列除法器是一种并行运算部件,采用大规模集成电路制造,与早期的串行

除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运

算速度。阵列除法器有多种形式,如不恢复余数阵列除法器、补码阵列除法器等

等本实验设计的是加减交替阵列除法器。

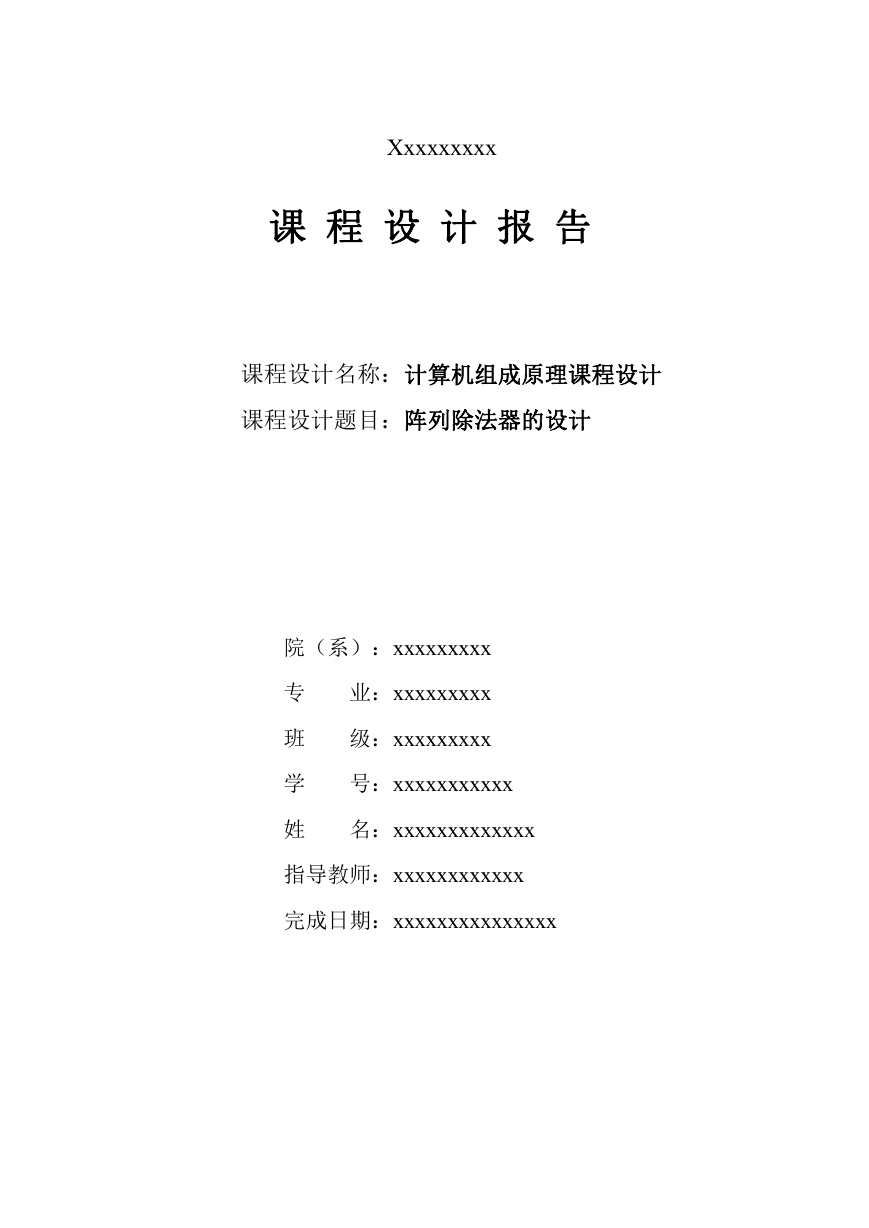

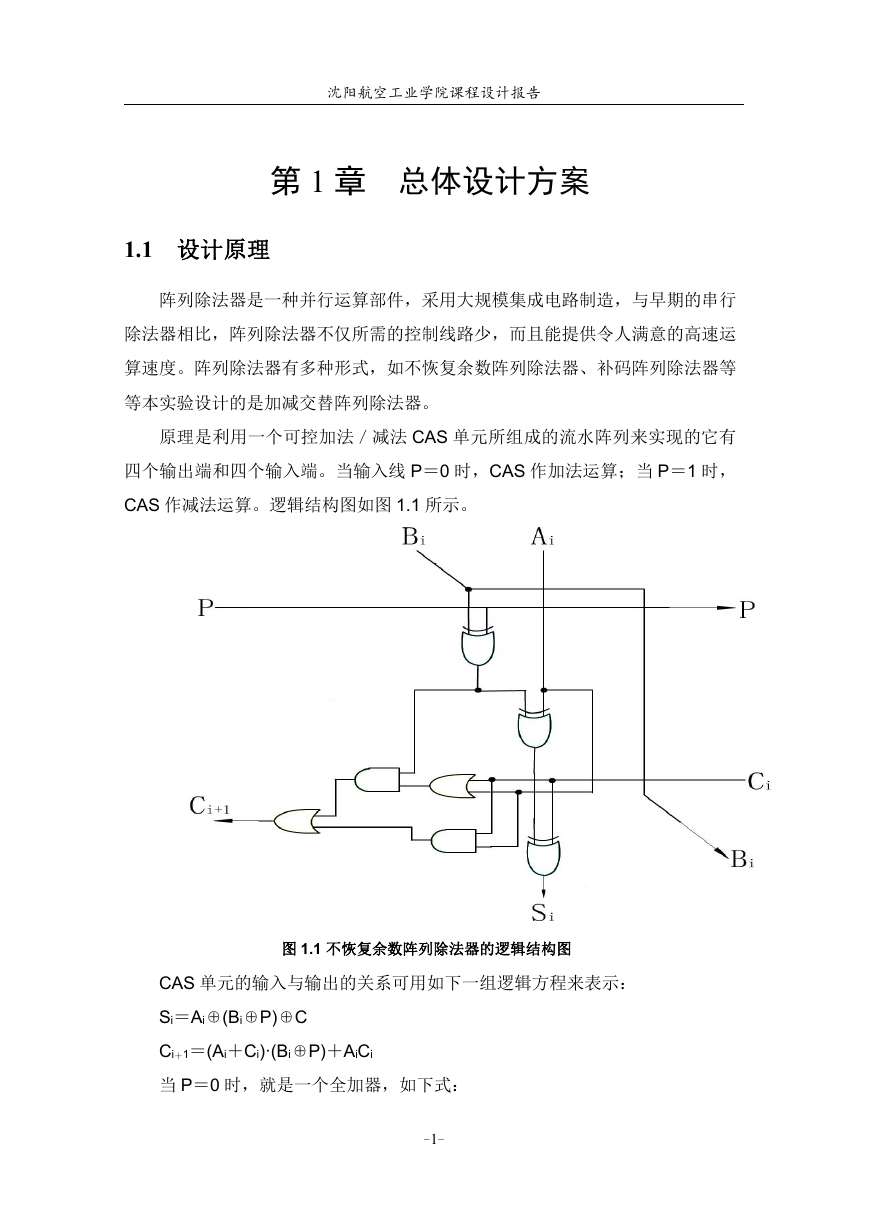

原理是利用一个可控加法/减法 CAS 单元所组成的流水阵列来实现的它有

四个输出端和四个输入端。当输入线 P=0 时,CAS 作加法运算;当 P=1 时,

CAS 作减法运算。逻辑结构图如图 1.1 所示。

图 1.1 不恢复余数阵列除法器的逻辑结构图

CAS 单元的输入与输出的关系可用如下一组逻辑方程来表示:

Si=Ai⊕(Bi⊕P)⊕C

Ci+1=(Ai+Ci)·(Bi⊕P)+AiCi

当 P=0 时,就是一个全加器,如下式:

-1-

�

沈阳航空工业学院课程设计报告

Si=Ai⊕Bi⊕Ci

Ci+1=AiBi+BiCi+AiCi

当 P=1 时,则得求差公式:

Si=Ai⊕Bi⊕Ci

Ci+1=AiBi+BiCi+AiCi

其中 Bi=Bi⊕1。

在减法情况下,输入 Ci 称为借位输入,而 Ci+1 称为借位输出。

不恢复余数的除法也就是加减交替法。在不恢复余数的除法阵列中,每一行

所执行的操作究竟是加法还是减法,取决于前一行输出的符号与被除数的符号是

否一致。当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产

生一个商位“0”,除数首先沿对角线右移,然后加到下一行的部分余数上。当

部分余数不改变它的符号时,即产生商位“1”,下一行的操作应该是减法。

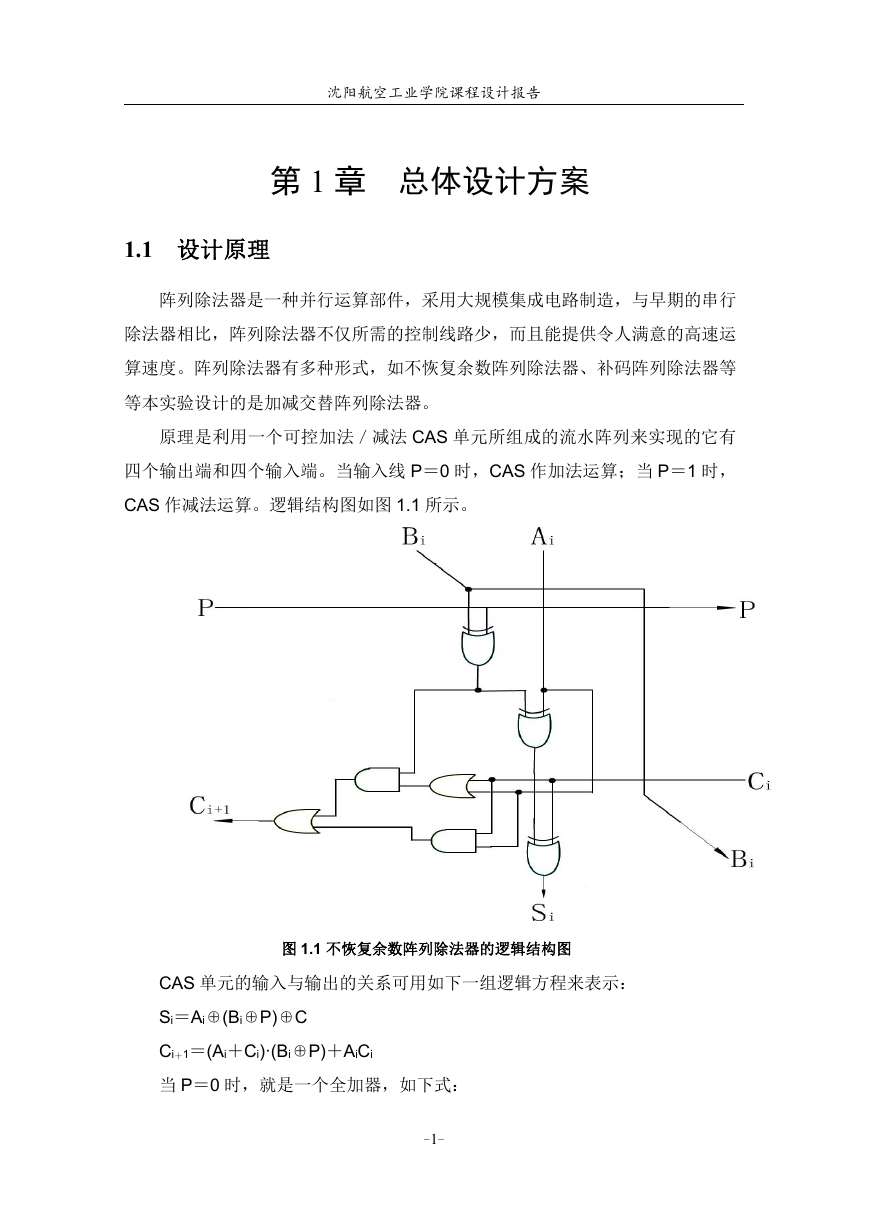

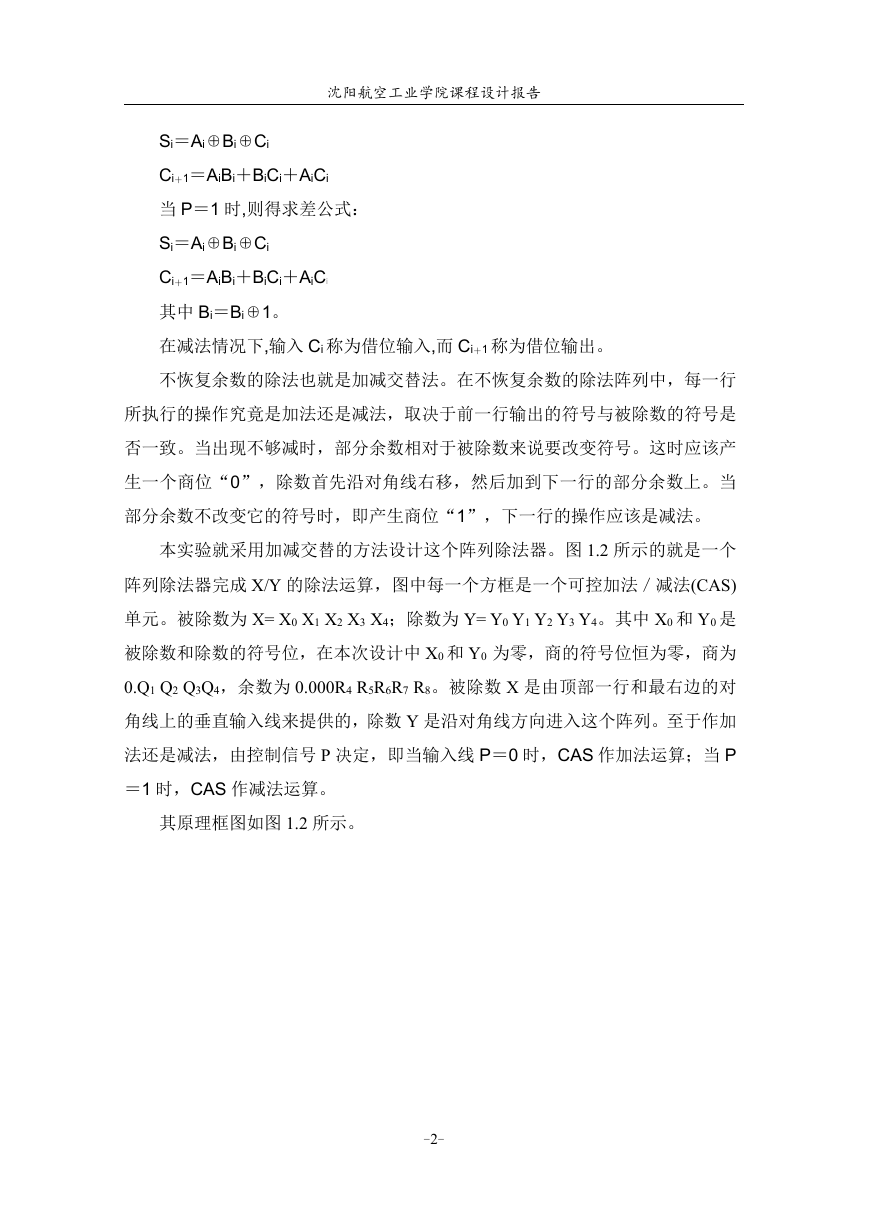

本实验就采用加减交替的方法设计这个阵列除法器。图 1.2 所示的就是一个

阵列除法器完成 X/Y 的除法运算,图中每一个方框是一个可控加法/减法(CAS)

单元。被除数为 X= X0 X1 X2 X3 X4;除数为 Y= Y0 Y1 Y2 Y3 Y4。其中 X0 和 Y0 是

被除数和除数的符号位,在本次设计中 X0 和 Y0 为零,商的符号位恒为零,商为

0.Q1 Q2 Q3Q4,余数为 0.000R4 R5R6R7 R8。被除数 X 是由顶部一行和最右边的对

角线上的垂直输入线来提供的,除数 Y 是沿对角线方向进入这个阵列。至于作加

法还是减法,由控制信号 P 决定,即当输入线 P=0 时,CAS 作加法运算;当 P

=1 时,CAS 作减法运算。

其原理框图如图 1.2 所示。

-2-

�

沈阳航空工业学院课程设计报告

图 1.2 阵列除法器原理框图

1.2 设计思路

是用一个可控加法/减法(CAS)单元所组成的流水阵列来实现的。推广到一

般情况,一个(n+1)位除(n+1)位的加减交替除法阵列由(n+1)2 个 CAS 单元组

成,其中两个操作数(被除数与除数)都是正的。流水阵列除法逻辑框图如图 1.2

可控加法/减法(RO)单元如图 1.2 所示,其中被除数为 X = 0. X1 X2 X3 X4,除

数为 Y= 0. Y1 Y2 Y3Y4,商数为 Q = 0. Q1 Q2 Q3Q4,它的余数为 R = 0. 000 R4 R5

R6R7R8,字长为 n + 1 = 5。

单元之间的互联是用 n=4 的阵列来表示的。

被除数 X 是一个 4 位的小数:X = 0. X1 X2 X3 X4

它是由顶部一行和最右边的对角线上的垂直输入线来提供的。

除数 Y 是一个 4 位的小数:Y= 0. Y1 Y2 Y3 Y4

它沿对角线方向进入这个阵列。因为,在除法中所需要的部分余数的左移,

可以用下列等效的操作来代替:即让余数保持固定,而将除数沿对角线右移。

商 Q 是一个 4 位的小数:Q = 0. Q1 Q2 Q3 Q4

它在阵列的左边产生。

余数 R 是一个 8 位的小数:R = 0. 000 R4 R5 R6R7R8

它在阵列的最下一行产生。

最上面一行所执行的初始操作经常是减法。因此最上面一行的控制线 P 置

成“1”。减法是用 2 的补码运算来实现的,这时右端各 CAS 单元上的反馈线用

-3-

�

沈阳航空工业学院课程设计报告

作初始的进位输入。每一行最左边的单元的进位输出决定着商的数值。将当前的

商反馈到下一行,我们就能确定下一行的操作。由于进位输出信号指示出当前的部

分余数的符号,因此,它将决定下一行的操作将进行加法还是减法。

不恢复余数阵列除法器来说,在进行运算时,沿着每一行都有进位(或借位)

传播,同时所有行在它们的进位链上都是串行连接。

采用细胞模块和门电路等逻辑部件设计并实现阵列除法功能,设计的原理图

调试后形成 liufei3.bit 文件并下载到 XCV200 可编程逻辑芯片中,经硬件测试验

证设计的正确性。

1.3 设计环境

(1)硬件环境

•伟福 COP2000 型计算机组成原理实验仪

COP2000 计算机组成原理实验系统由实验平台、开关电源、软件三大部分组

成实验平台上有寄存器组 R0-R3、运算单元、累加器 A、暂存器 B、直通/左移/

右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单

元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总

线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20 个按键、字符式 LCD、RS232

口。

COP2000 计算机组成原理实验系统各单元部件都以计算机结构模型布局,清

晰明了,系统在实验时即使不借助 PC 机,也可实时监控数据流状态及正确与否,

实验系统的软硬件对用户的实验设计具有完全的开放特性,系统提供了微程序控

制器和组合逻辑控制器两种控制器方式, 系统还支持手动方式、联机方式、模拟

方式三种工作方式,系统具备完善的寻址方式、指令系统和强大的模拟调试功能。

·XCV200 实验板

在 COP2000 实验仪中的 FPGA 实验板主要用于设计性实验和课程设计实

验,它的核心器件是 20 万门 XCV200 的 FPGA 芯片。用 FPGA 实验板可设计 8

位 16 位和 32 位模型机。

XCV200 相应管脚已经连接好配合 FPGA 实验板的 PC 调试软件可方便地

进行各种实验。U3 IDT71V016SA 是 64Kx16 位存储器能保存大容量的程序。

-4-

�

沈阳航空工业学院课程设计报告

C0-C5 D0-D5 是 12 个 7 段数码管用于显示模型机内部的寄存器总线数值,在设

计时可将需要观察的内部寄存器总线等值接到这些 7 段管上直观地观察模型机

运行时内部状态变化。A0-A7、B0-B7 是 16 个 LED 发光二极管用于显示模型机

内部的状态例如进位标志零标志中断申请标志等等。K0(0-7)-K4(0-7)是四十个开

关用于输入外部信号,例如在做单步实验时这些开关可用来输入地址总线值数据

总线值控制信号等。T6B595 是 7 段数码管的驱动芯片,74HC1649 是串转并芯

片,用于接 16 个 LED。

(2)EDA 环境

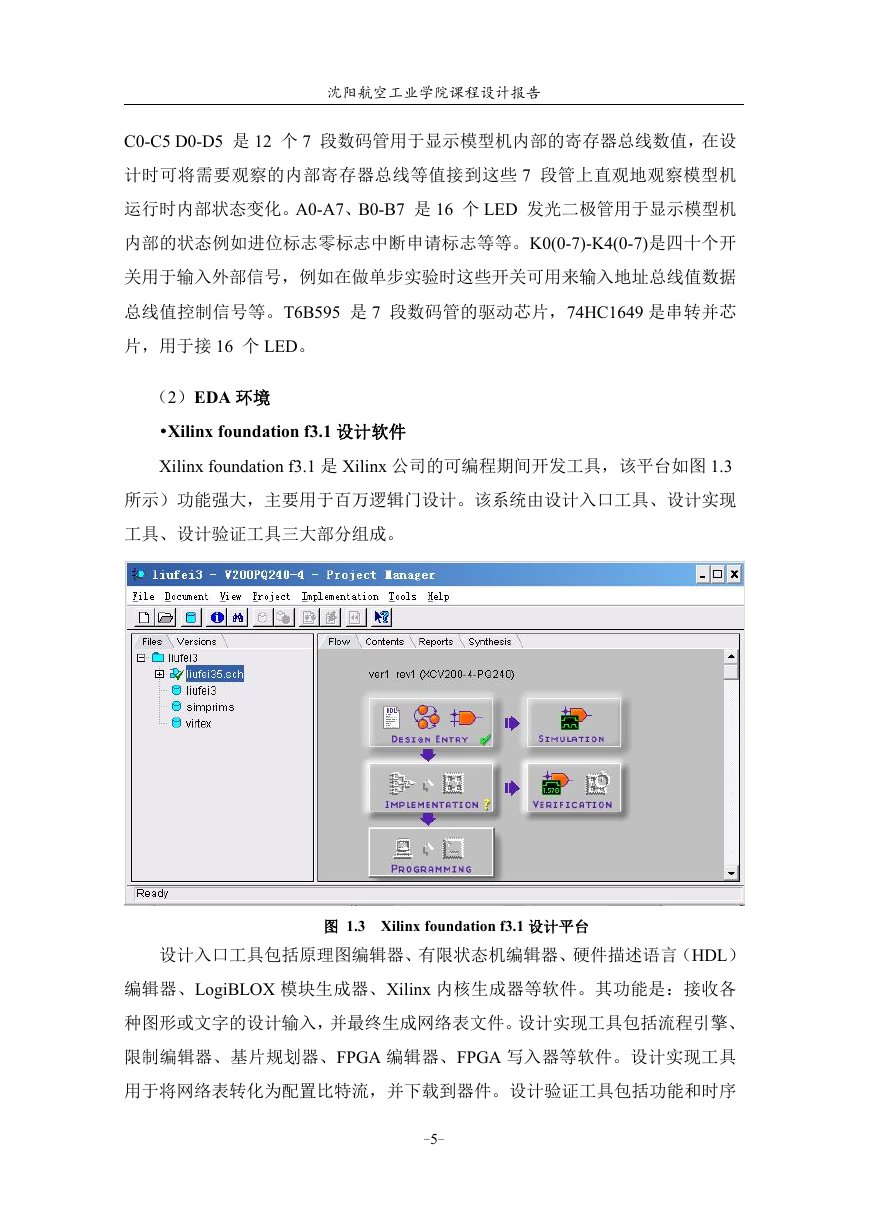

•Xilinx foundation f3.1 设计软件

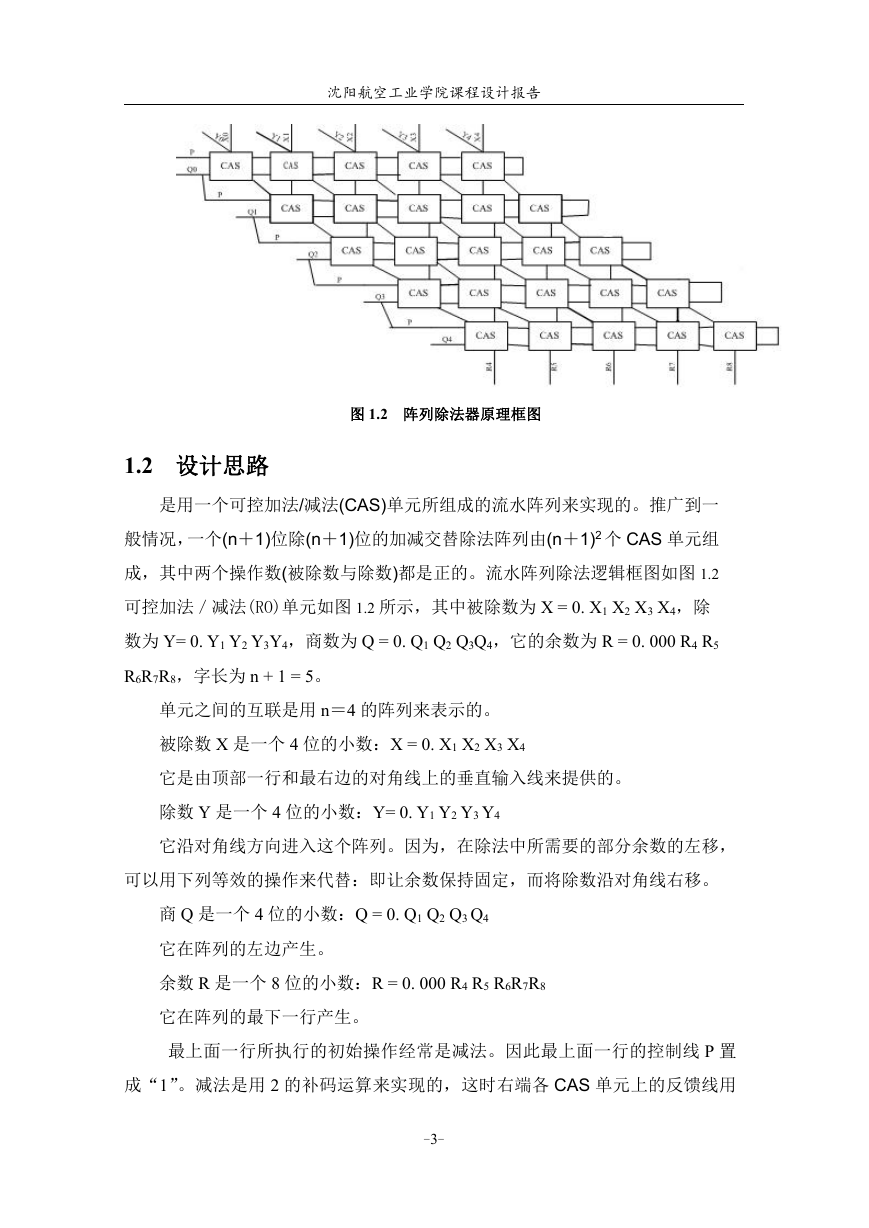

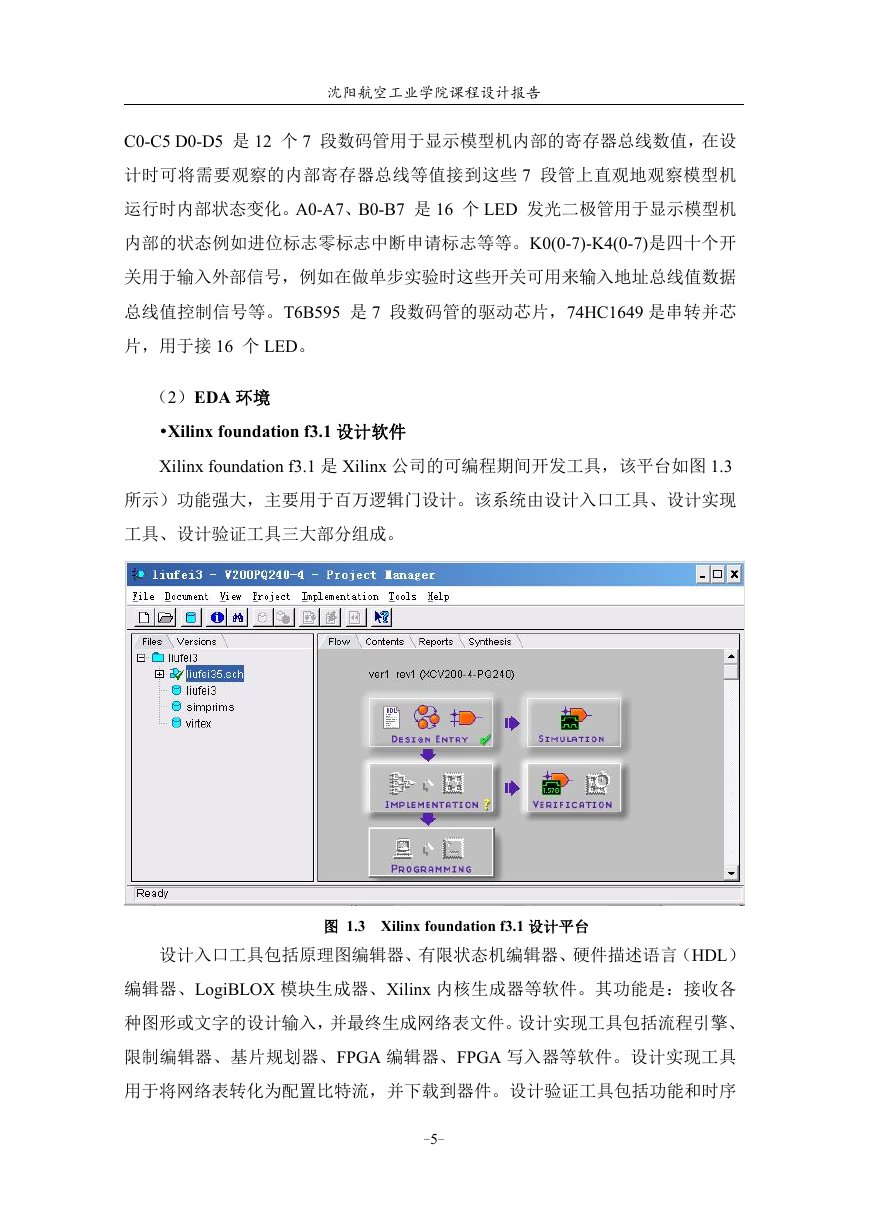

Xilinx foundation f3.1 是 Xilinx 公司的可编程期间开发工具,该平台如图 1.3

所示)功能强大,主要用于百万逻辑门设计。该系统由设计入口工具、设计实现

工具、设计验证工具三大部分组成。

图 1.3 Xilinx foundation f3.1 设计平台

设计入口工具包括原理图编辑器、有限状态机编辑器、硬件描述语言(HDL)

编辑器、LogiBLOX 模块生成器、Xilinx 内核生成器等软件。其功能是:接收各

种图形或文字的设计输入,并最终生成网络表文件。设计实现工具包括流程引擎、

限制编辑器、基片规划器、FPGA 编辑器、FPGA 写入器等软件。设计实现工具

用于将网络表转化为配置比特流,并下载到器件。设计验证工具包括功能和时序

-5-

�

沈阳航空工业学院课程设计报告

仿真器、静态时序分析器等,可用来对设计中的逻辑关系及输出结果进行检验,

并详尽分析各个时序限制的满足情况。

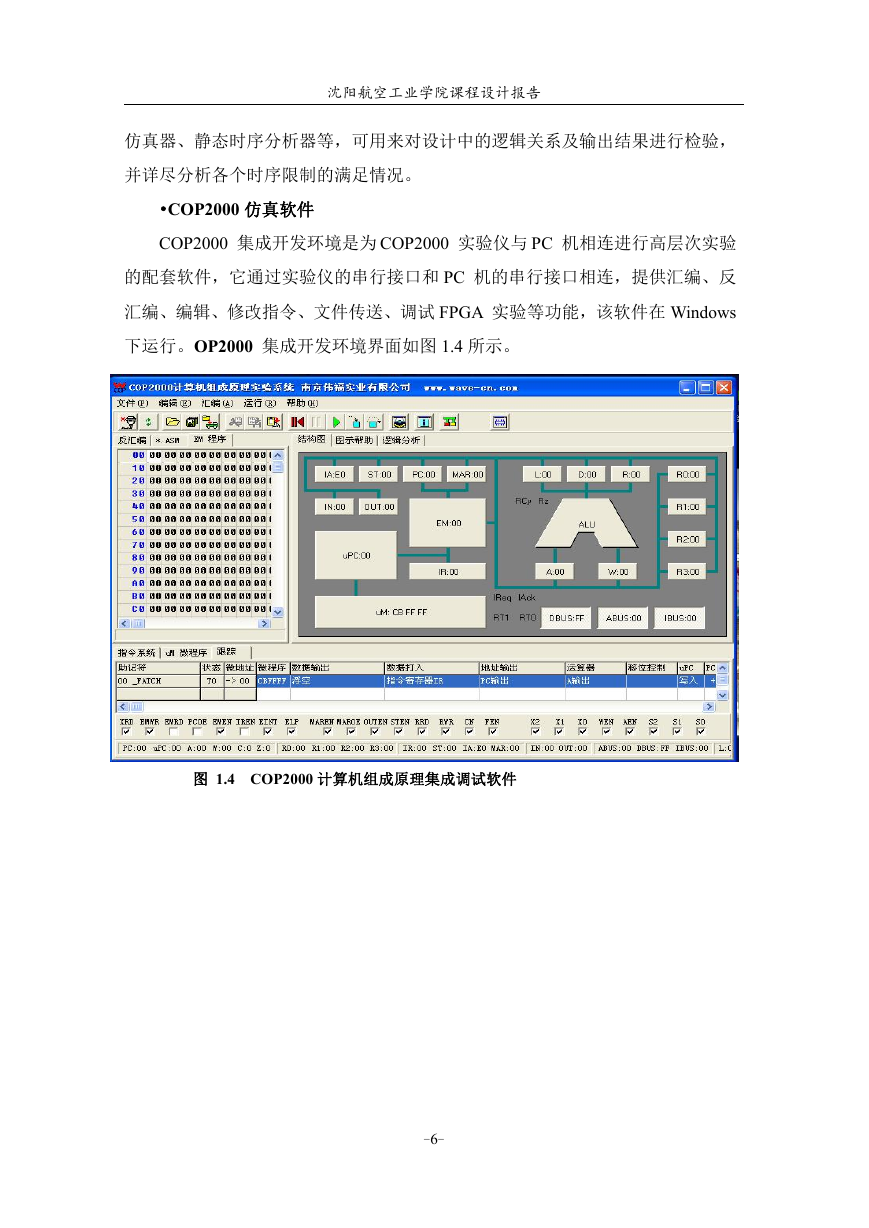

•COP2000 仿真软件

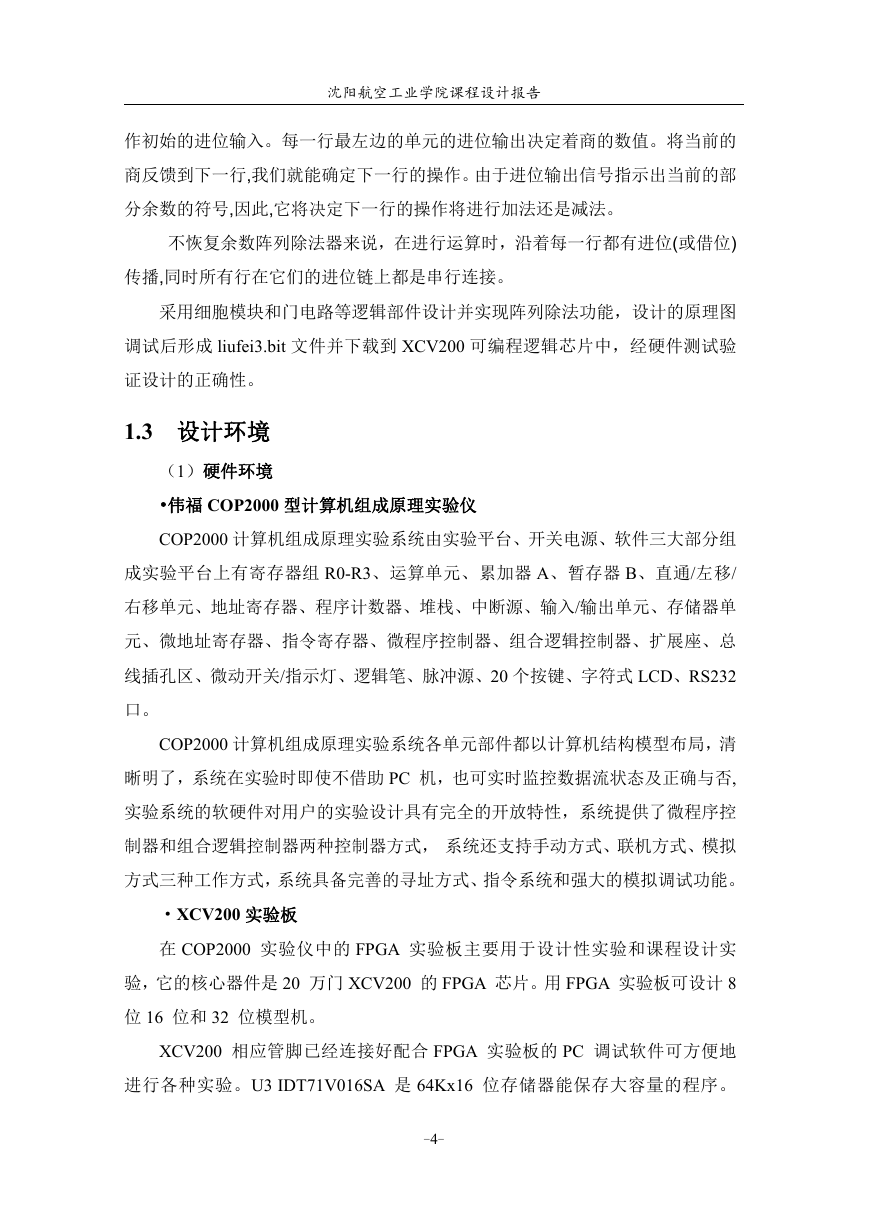

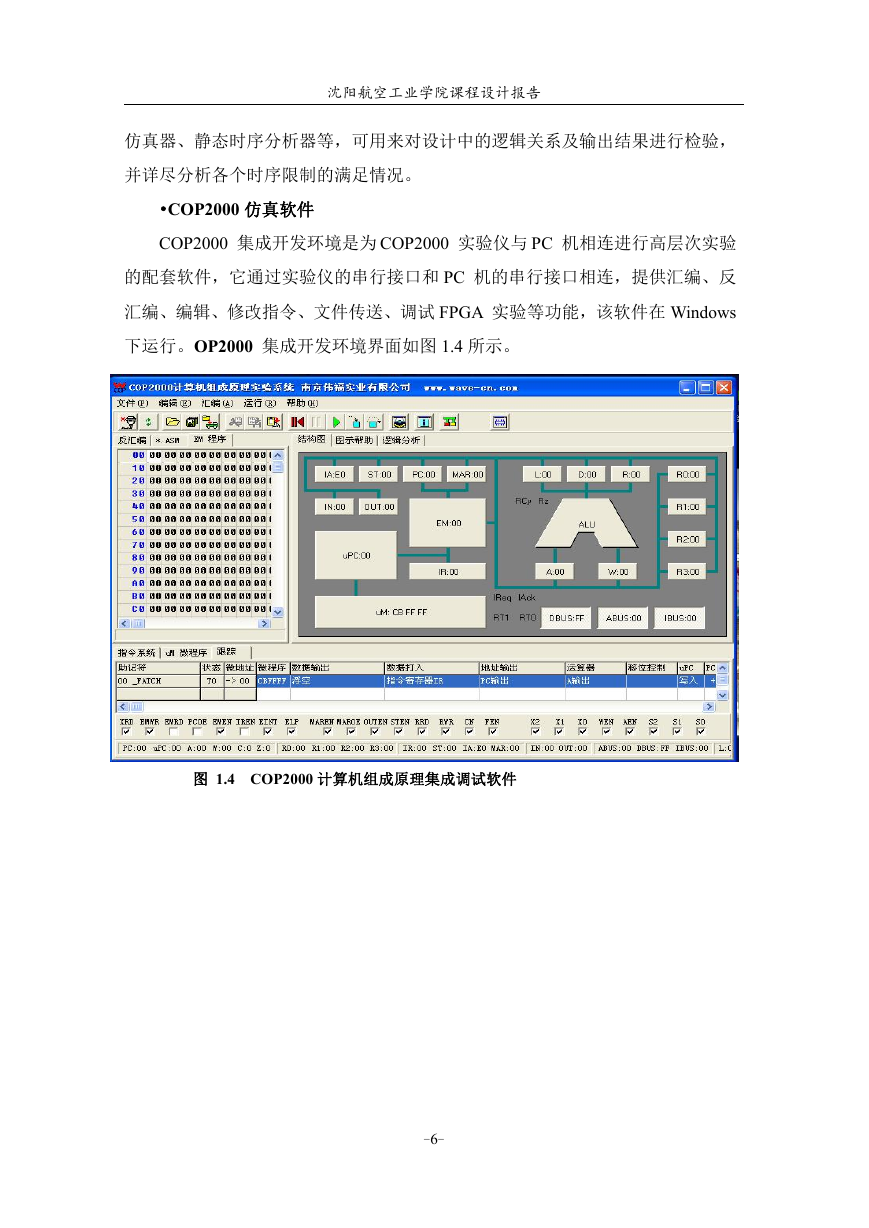

COP2000 集成开发环境是为 COP2000 实验仪与 PC 机相连进行高层次实验

的配套软件,它通过实验仪的串行接口和 PC 机的串行接口相连,提供汇编、反

汇编、编辑、修改指令、文件传送、调试 FPGA 实验等功能,该软件在 Windows

下运行。OP2000 集成开发环境界面如图 1.4 所示。

图 1.4 COP2000 计算机组成原理集成调试软件

-6-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc