Cadence cdsSPICE 使用说明 资料收藏 http://www.maihui.net PCB 收藏天地

第二章 Virtuoso Editing 的使用简介

全文将用一个贯穿始终的例子来说明如何绘制版图 这个例子绘制的是一个最简单的非

门的版图

§ 2

1 建立版图文件

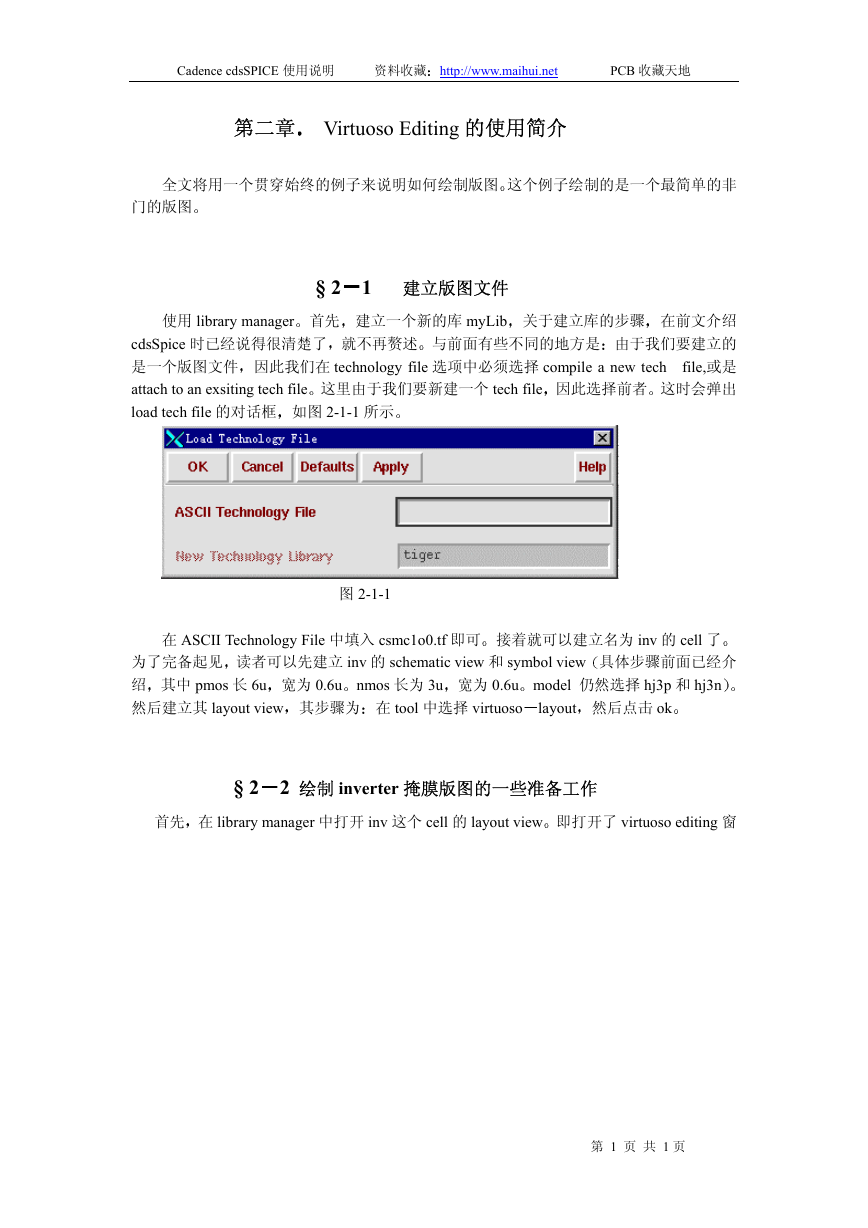

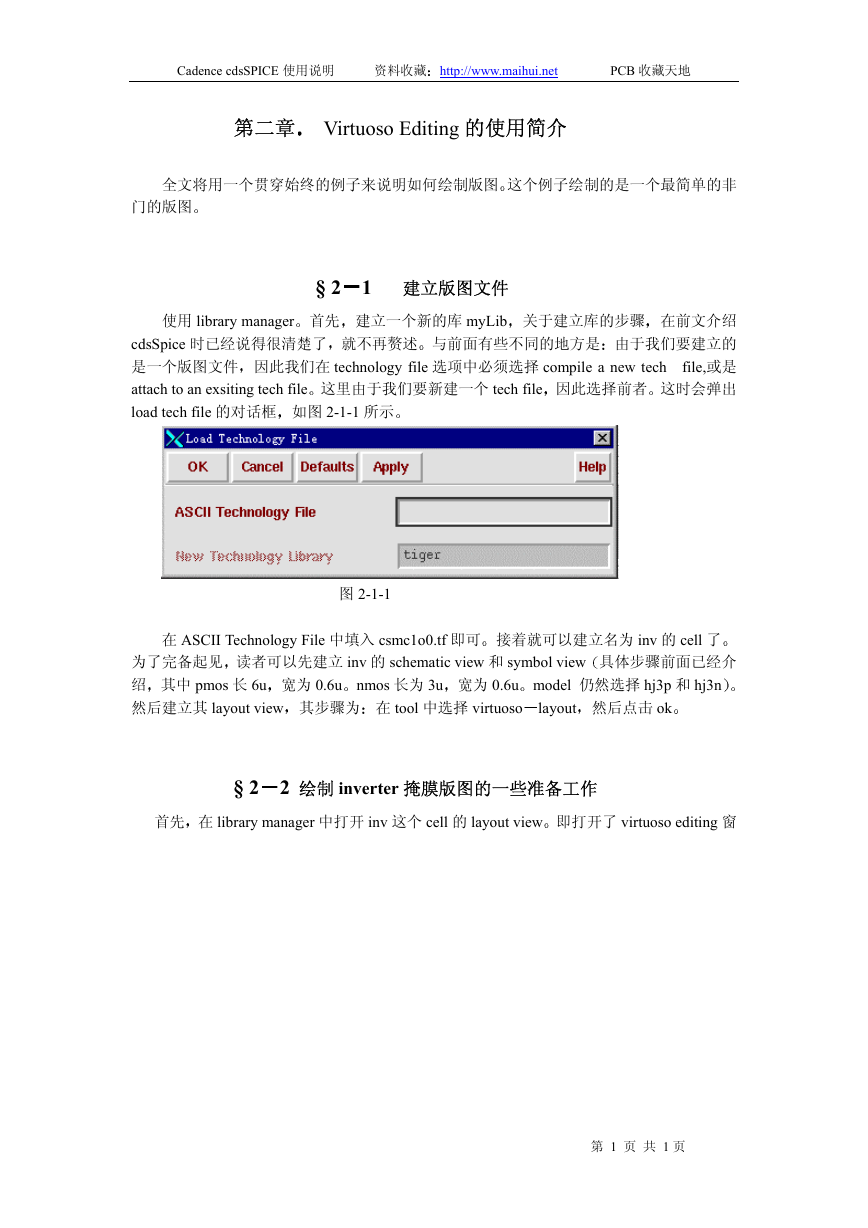

使用 library manager 首先 建立一个新的库 myLib 关于建立库的步骤 在前文介绍

cdsSpice 时已经说得很清楚了 就不再赘述 与前面有些不同的地方是 由于我们要建立的

是一个版图文件 因此我们在 technology file 选项中必须选择 compile a new tech file,或是

attach to an exsiting tech file 这里由于我们要新建一个 tech file 因此选择前者 这时会弹出

load tech file 的对话框 如图 2-1-1 所示

图 2-1-1

在 ASCII Technology File 中填入 csmc1o0.tf 即可 接着就可以建立名为 inv 的 cell 了

为了完备起见 读者可以先建立 inv 的 schematic view 和 symbol view 具体步骤前面已经介

绍 其中 pmos 长 6u 宽为 0.6u nmos 长为 3u 宽为 0.6u model 仍然选择 hj3p 和 hj3n

然后建立其 layout view 其步骤为 在 tool 中选择 virtuoso

layout 然后点击 ok

§ 2

2 绘制 inverter 掩膜版图的一些准备工作

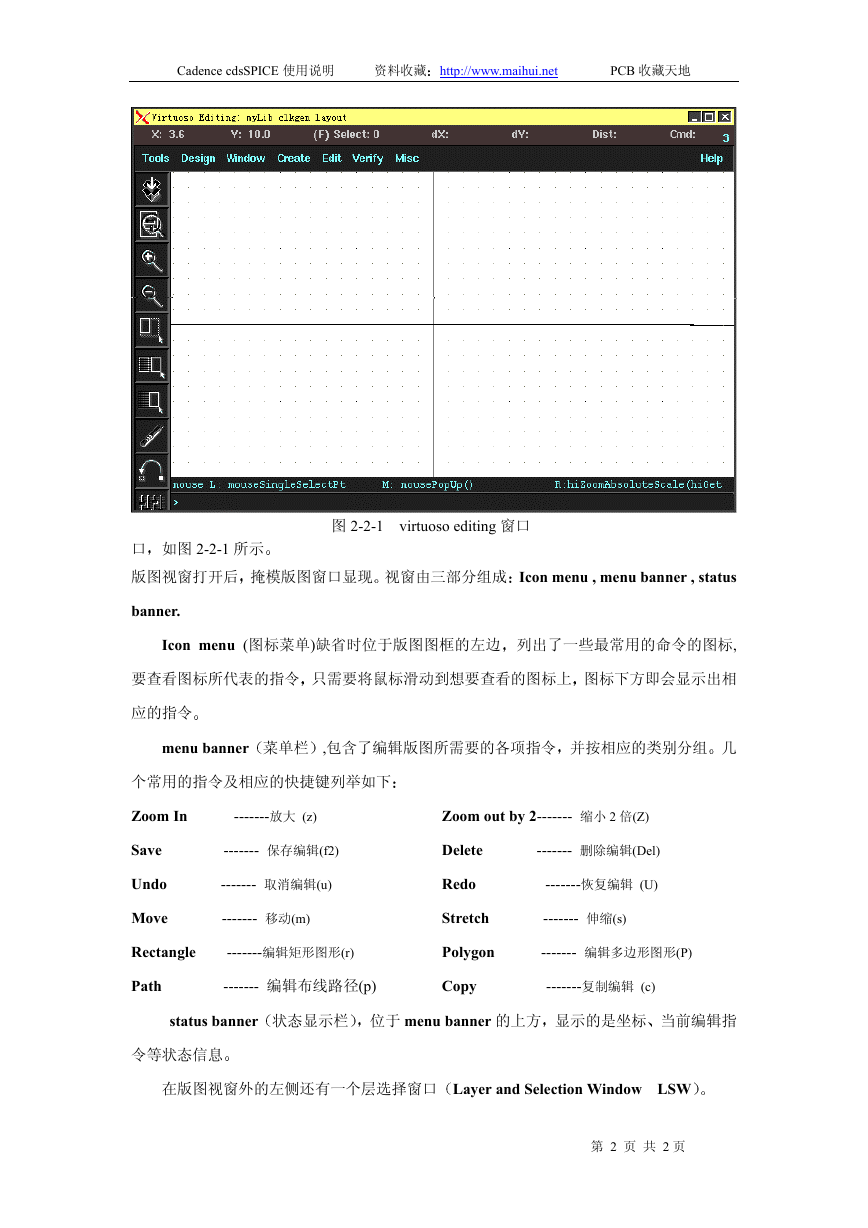

首先 在 library manager 中打开 inv 这个 cell 的 layout view 即打开了 virtuoso editing 窗

第 1 页 共 1 页

�

Cadence cdsSPICE 使用说明 资料收藏 http://www.maihui.net PCB 收藏天地

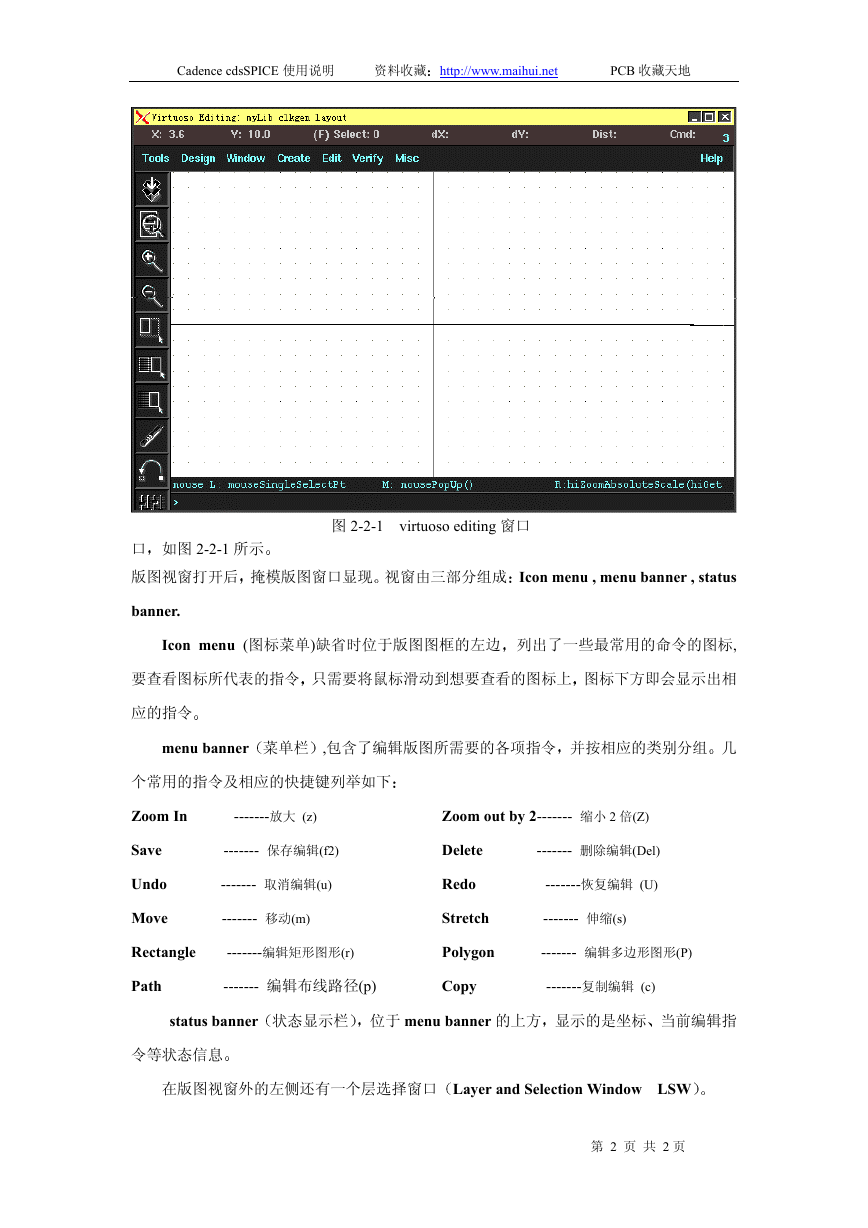

图 2-2-1 virtuoso editing 窗口

口 如图 2-2-1 所示

版图视窗打开后 掩模版图窗口显现 视窗由三部分组成 Icon menu , menu banner , status

banner.

Icon menu (图标菜单)缺省时位于版图图框的左边 列出了一些最常用的命令的图标,

要查看图标所代表的指令 只需要将鼠标滑动到想要查看的图标上 图标下方即会显示出相

应的指令

menu banner 菜单栏 ,包含了编辑版图所需要的各项指令 并按相应的类别分组 几

个常用的指令及相应的快捷键列举如下

Zoom In -------放大 (z)

Zoom out by 2------- 缩小 2 倍(Z)

Save ------- 保存编辑(f2)

Delete ------- 删除编辑(Del)

Undo ------- 取消编辑(u)

Redo -------恢复编辑 (U)

Move ------- 移动(m)

Stretch ------- 伸缩(s)

Rectangle -------编辑矩形图形(r)

Polygon ------- 编辑多边形图形(P)

Path ------- 编辑布线路径(p)

Copy -------复制编辑 (c)

status banner 状态显示栏 位于 menu banner 的上方 显示的是坐标 当前编辑指

令等状态信息

在版图视窗外的左侧还有一个层选择窗口 Layer and Selection Window LSW

第 2 页 共 2 页

�

Cadence cdsSPICE 使用说明 资料收藏 http://www.maihui.net PCB 收藏天地

LSW 视图的功能

1

2

3

可选择所编辑图形所在的层

可选择哪些层可供编辑

可选择哪些层可以看到

由于我们所需的部分版图层次在初始 LSW 中并不存在 因此下一步要做的是 建立我们

自己的工艺库所需的版图层次及其显示属性 为了简单起见 以下仅列出绘制我们这个版图

所需的最少版图层次

层次名称

说明

Nwell

Active

Pselect

Nselect

Contact

Metal1

Via

Metal2

Text

Poly

N 阱

有源区

P 型注入掩膜

N 型注入掩膜

引线孔 连接金属与多晶硅/有源区

第一层金属 用于水平布线 如电源和地

通孔 连接 metal1 和 metal2

第二层金属 用于垂直布线 如信号源的 I/O 口

标签

多晶硅 做 mos 的栅

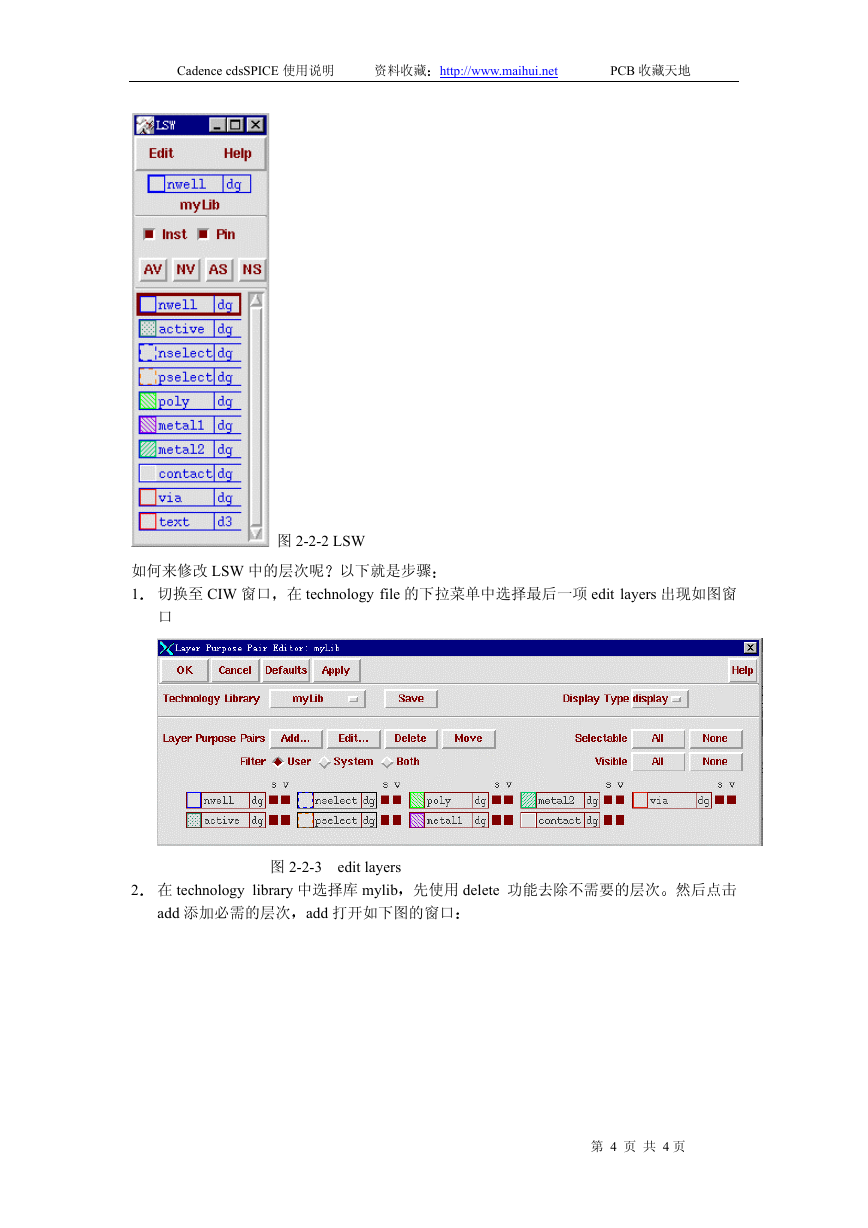

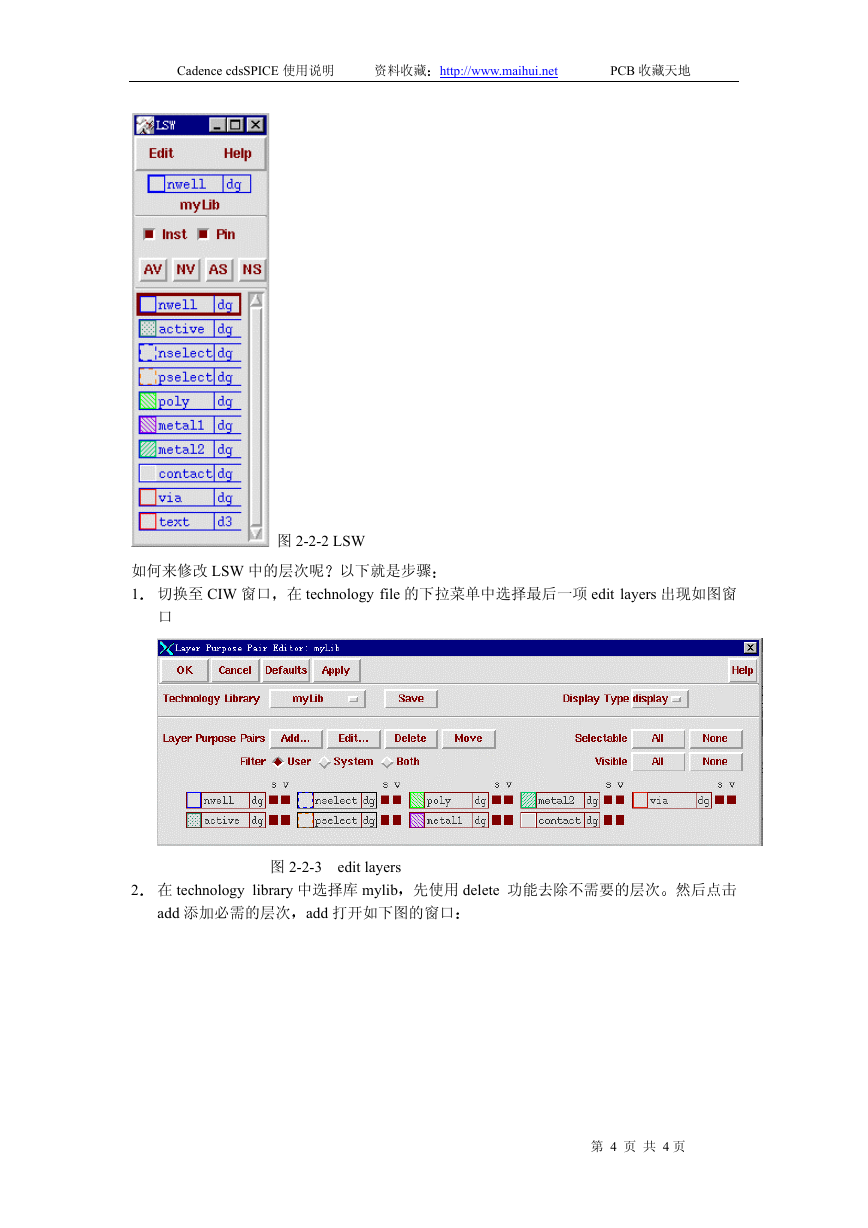

下图是修改后的 LSW

第 3 页 共 3 页

�

Cadence cdsSPICE 使用说明 资料收藏 http://www.maihui.net PCB 收藏天地

图 2-2-2 LSW

如何来修改 LSW 中的层次呢 以下就是步骤

1

切换至 CIW 窗口 在 technology file 的下拉菜单中选择最后一项 edit layers 出现如图窗

口

图 2-2-3 edit layers

2

在 technology library 中选择库 mylib 先使用 delete 功能去除不需要的层次 然后点击

add 添加必需的层次 add 打开如下图的窗口

第 4 页 共 4 页

�

Cadence cdsSPICE 使用说明 资料收藏 http://www.maihui.net PCB 收藏天地

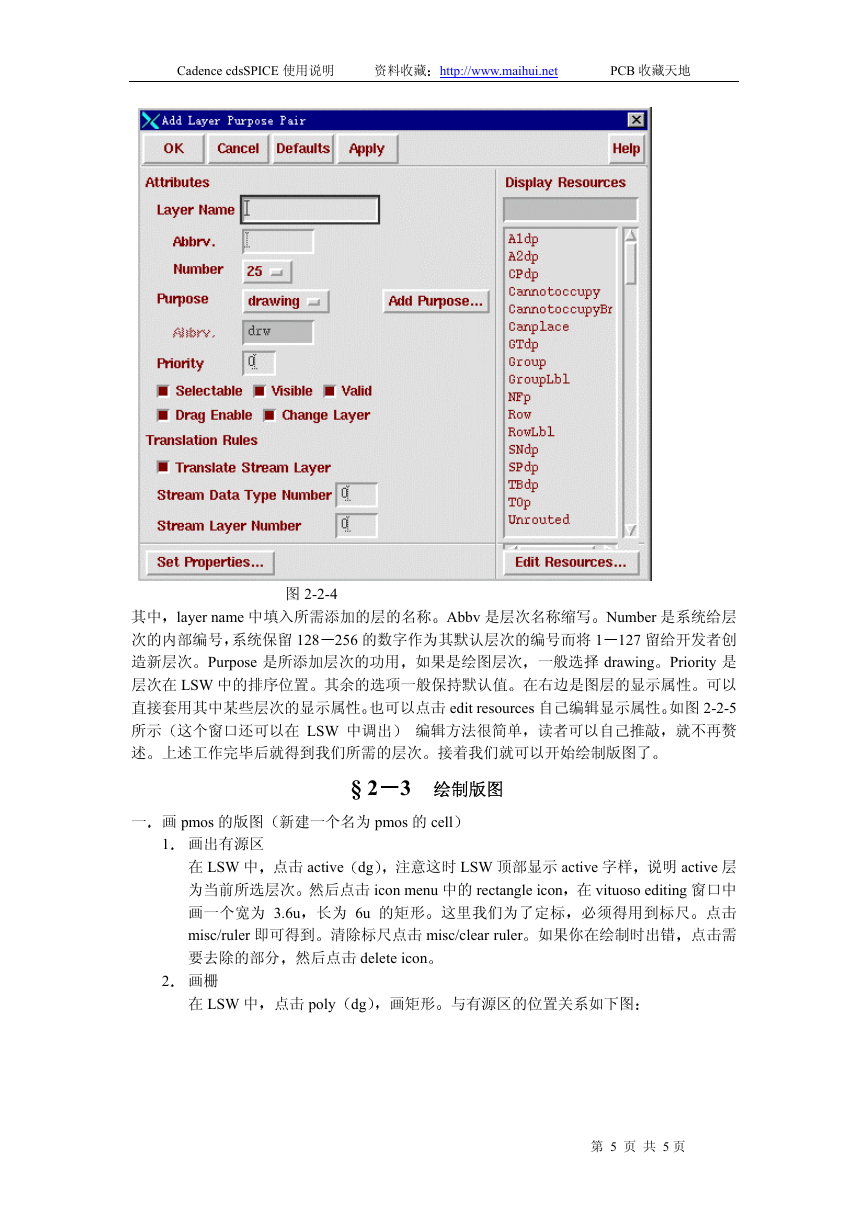

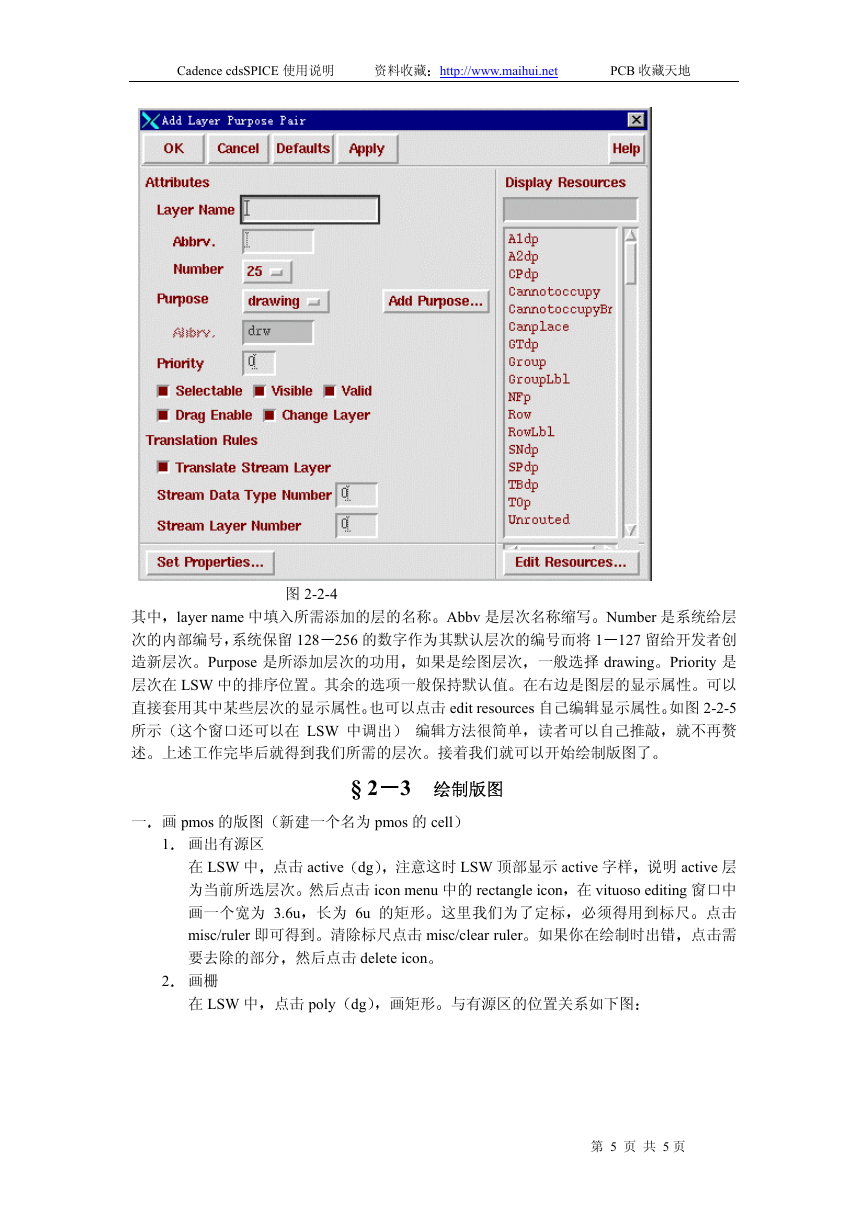

图 2-2-4

其中 layer name 中填入所需添加的层的名称 Abbv 是层次名称缩写 Number 是系统给层

次的内部编号 系统保留 128

256 的数字作为其默认层次的编号而将 1 127 留给开发者创

造新层次 Purpose 是所添加层次的功用 如果是绘图层次 一般选择 drawing Priority 是

层次在 LSW 中的排序位置 其余的选项一般保持默认值 在右边是图层的显示属性 可以

直接套用其中某些层次的显示属性 也可以点击 edit resources 自己编辑显示属性 如图 2-2-5

所示 这个窗口还可以在 LSW 中调出 编辑方法很简单 读者可以自己推敲 就不再赘

述 上述工作完毕后就得到我们所需的层次 接着我们就可以开始绘制版图了

一 画 pmos 的版图 新建一个名为 pmos 的 cell

§ 2

3 绘制版图

1

2

画出有源区

在 LSW 中 点击 active dg 注意这时 LSW 顶部显示 active 字样 说明 active 层

为当前所选层次 然后点击 icon menu 中的 rectangle icon 在 vituoso editing 窗口中

画一个宽为 3.6u 长为 6u 的矩形 这里我们为了定标 必须得用到标尺 点击

misc/ruler 即可得到 清除标尺点击 misc/clear ruler 如果你在绘制时出错 点击需

要去除的部分 然后点击 delete icon

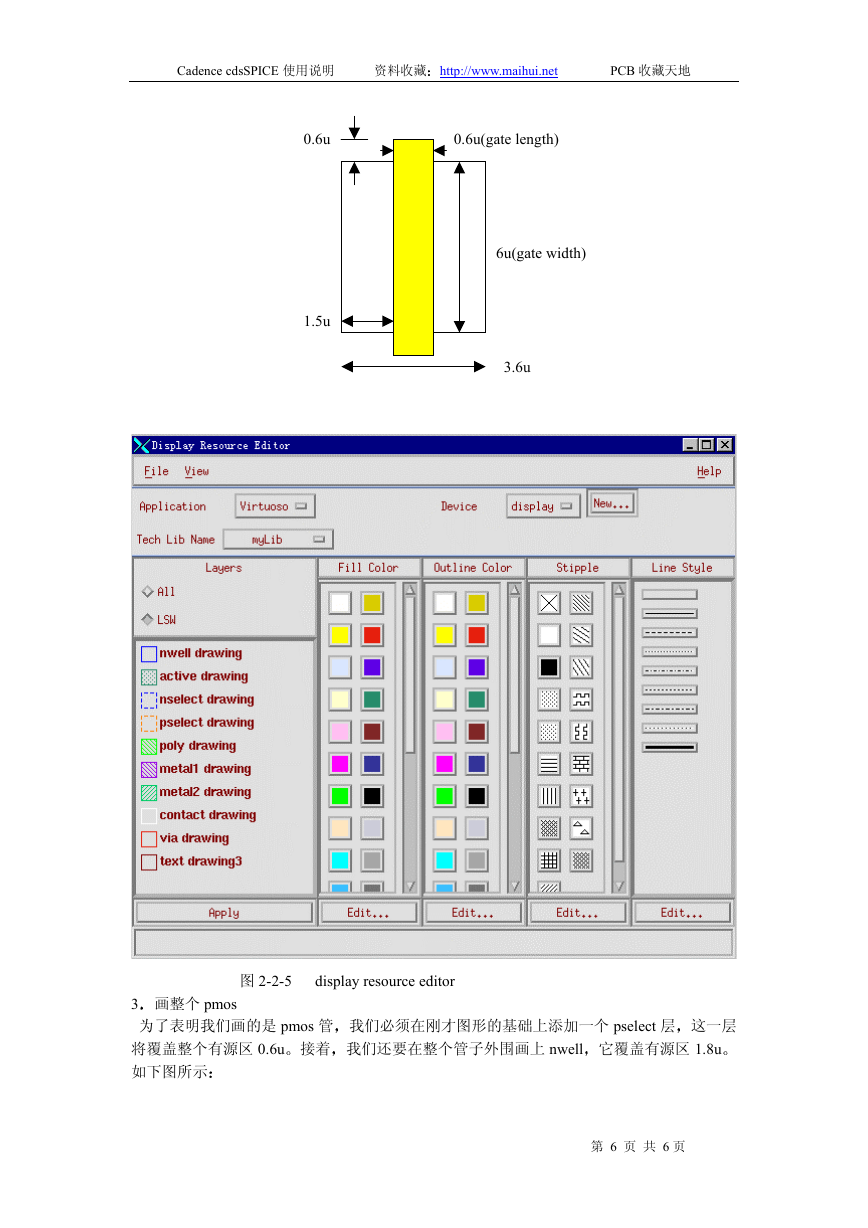

画栅

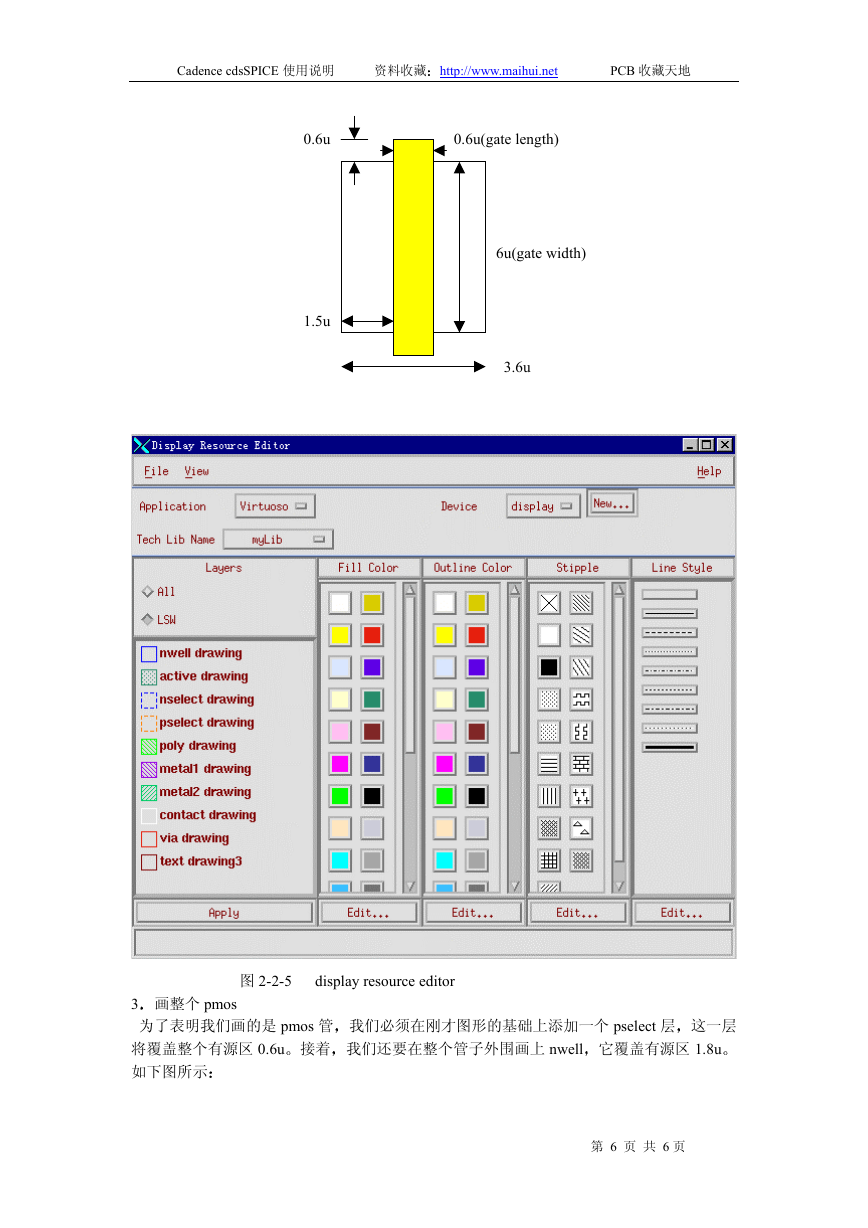

在 LSW 中 点击 poly dg 画矩形 与有源区的位置关系如下图

第 5 页 共 5 页

�

Cadence cdsSPICE 使用说明 资料收藏 http://www.maihui.net PCB 收藏天地

0.6u 0.6u(gate length)

6u(gate width)

1.5u

3.6u

图 2-2-5 display resource editor

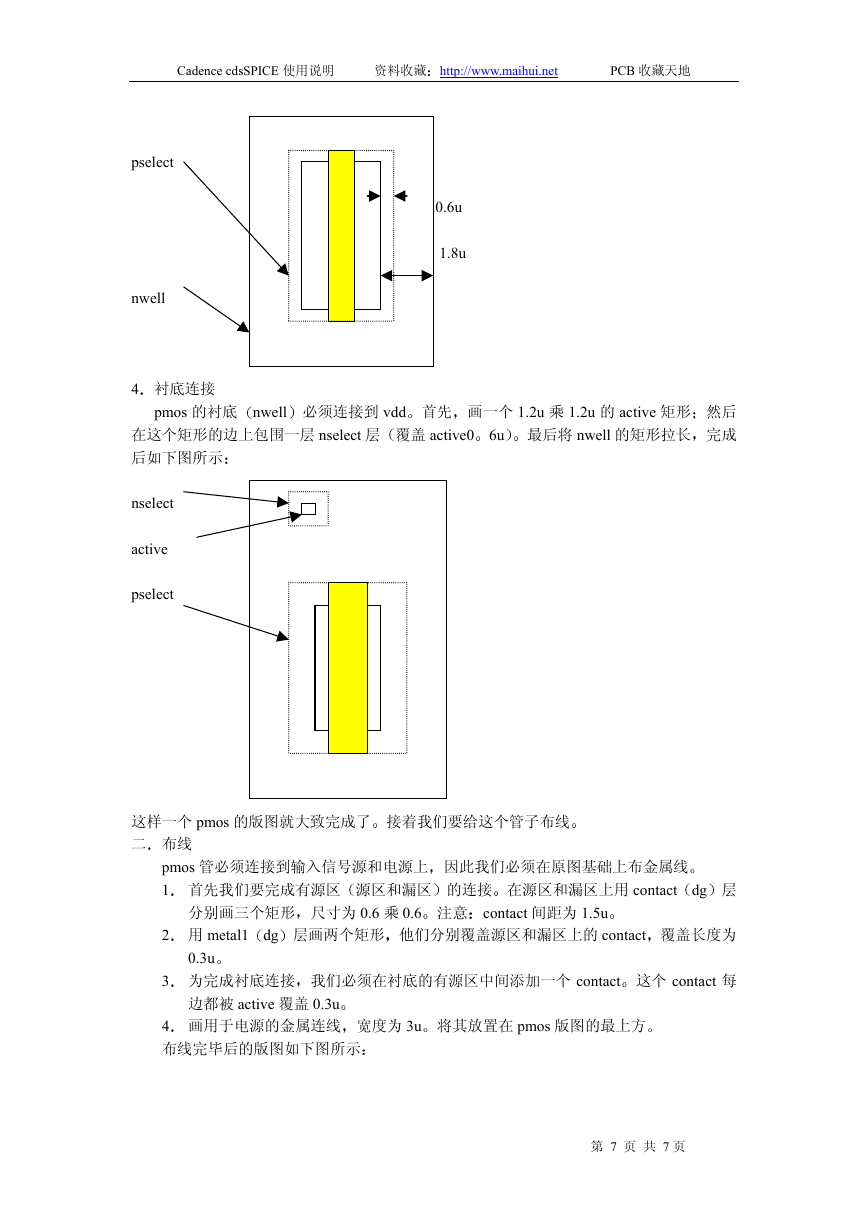

3 画整个 pmos

为了表明我们画的是 pmos 管 我们必须在刚才图形的基础上添加一个 pselect 层 这一层

将覆盖整个有源区 0.6u 接着 我们还要在整个管子外围画上 nwell 它覆盖有源区 1.8u

如下图所示

第 6 页 共 6 页

�

Cadence cdsSPICE 使用说明 资料收藏 http://www.maihui.net PCB 收藏天地

pselect

00.6u0.6u

1.8u

nwell

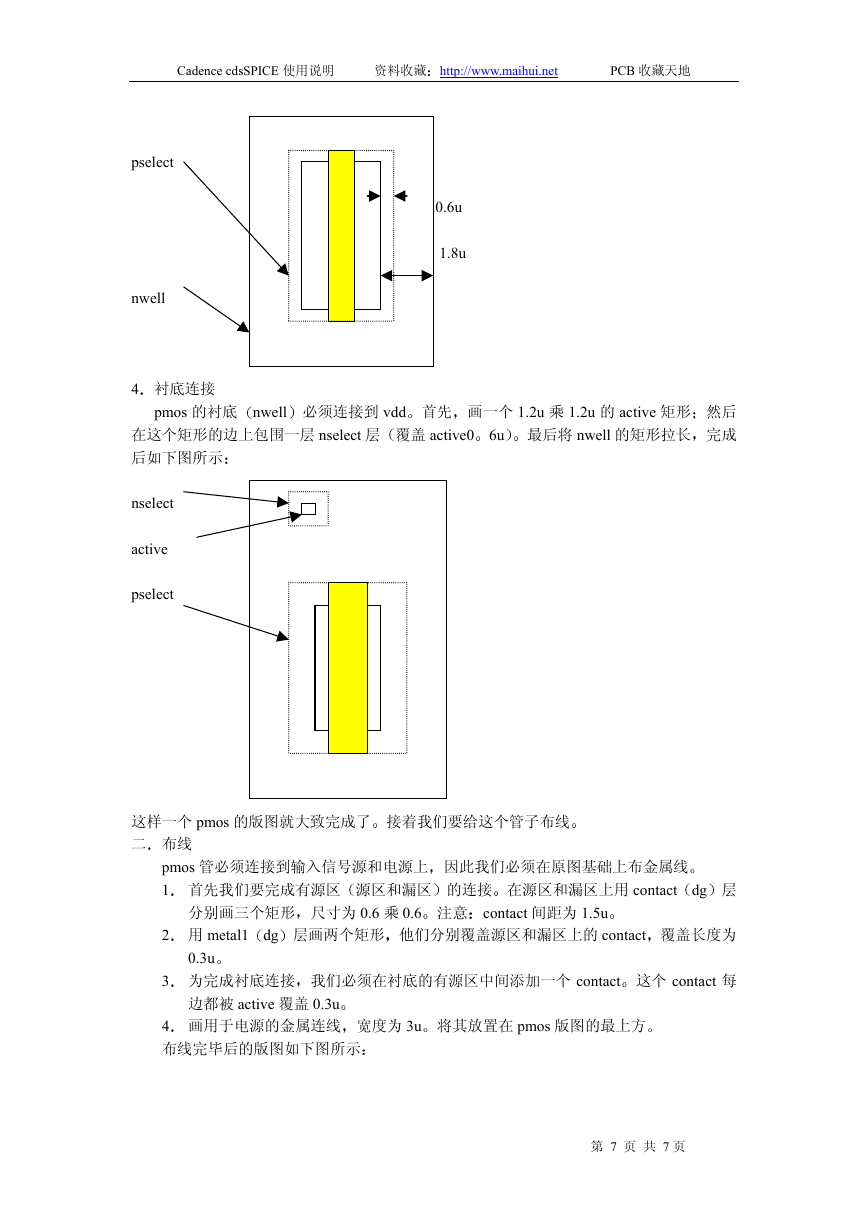

4 衬底连接

pmos 的衬底 nwell 必须连接到 vdd 首先 画一个 1.2u 乘 1.2u 的 active 矩形 然后

在这个矩形的边上包围一层 nselect 层 覆盖 active0 6u 最后将 nwell 的矩形拉长 完成

后如下图所示

nselect

active

pselect

这样一个 pmos 的版图就大致完成了 接着我们要给这个管子布线

二 布线

pmos 管必须连接到输入信号源和电源上 因此我们必须在原图基础上布金属线

1

首先我们要完成有源区 源区和漏区 的连接 在源区和漏区上用 contact dg 层

分别画三个矩形 尺寸为 0.6 乘 0.6 注意 contact 间距为 1.5u

用 metal1 dg 层画两个矩形 他们分别覆盖源区和漏区上的 contact 覆盖长度为

0.3u

为完成衬底连接 我们必须在衬底的有源区中间添加一个 contact 这个 contact 每

边都被 active 覆盖 0.3u

画用于电源的金属连线 宽度为 3u 将其放置在 pmos 版图的最上方

2

3

4

布线完毕后的版图如下图所示

第 7 页 共 7 页

�

Cadence cdsSPICE 使用说明 资料收藏 http://www.maihui.net PCB 收藏天地

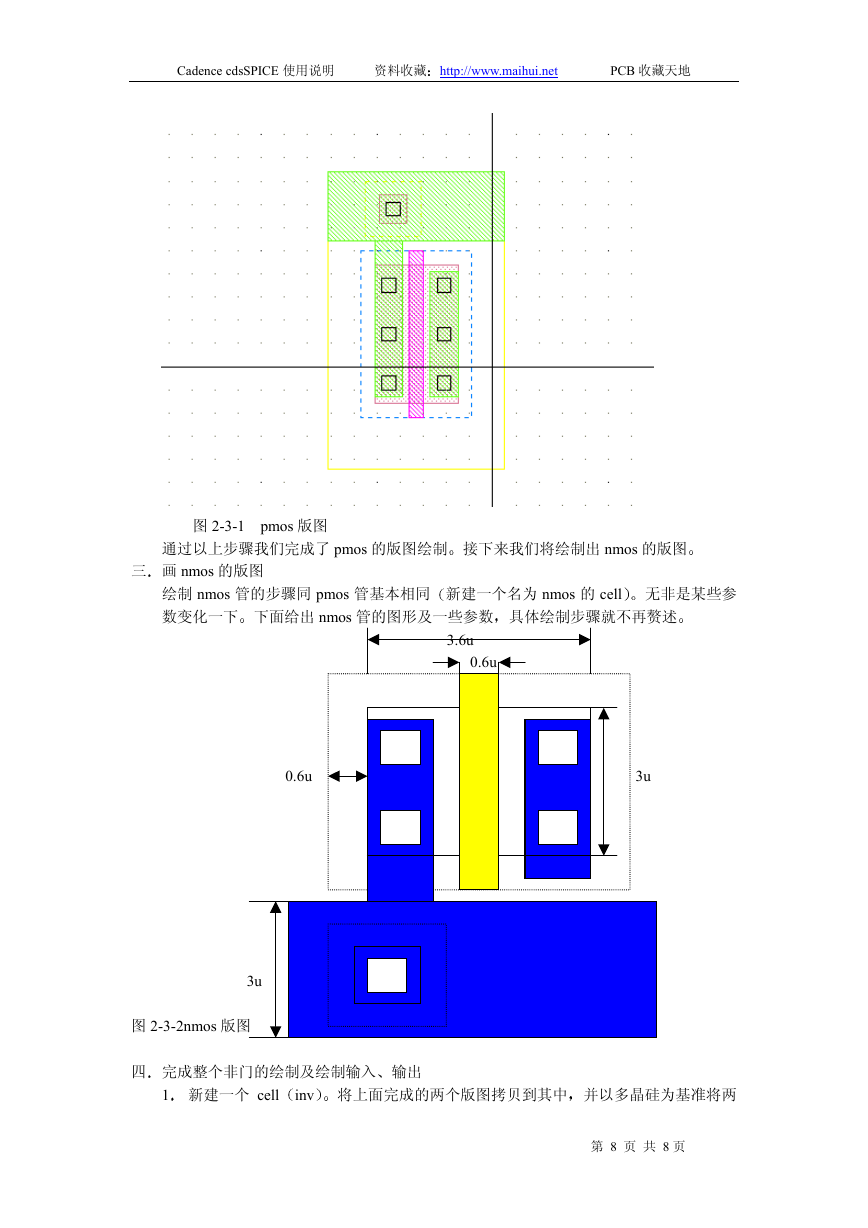

图 2-3-1 pmos 版图

通过以上步骤我们完成了 pmos 的版图绘制 接下来我们将绘制出 nmos 的版图

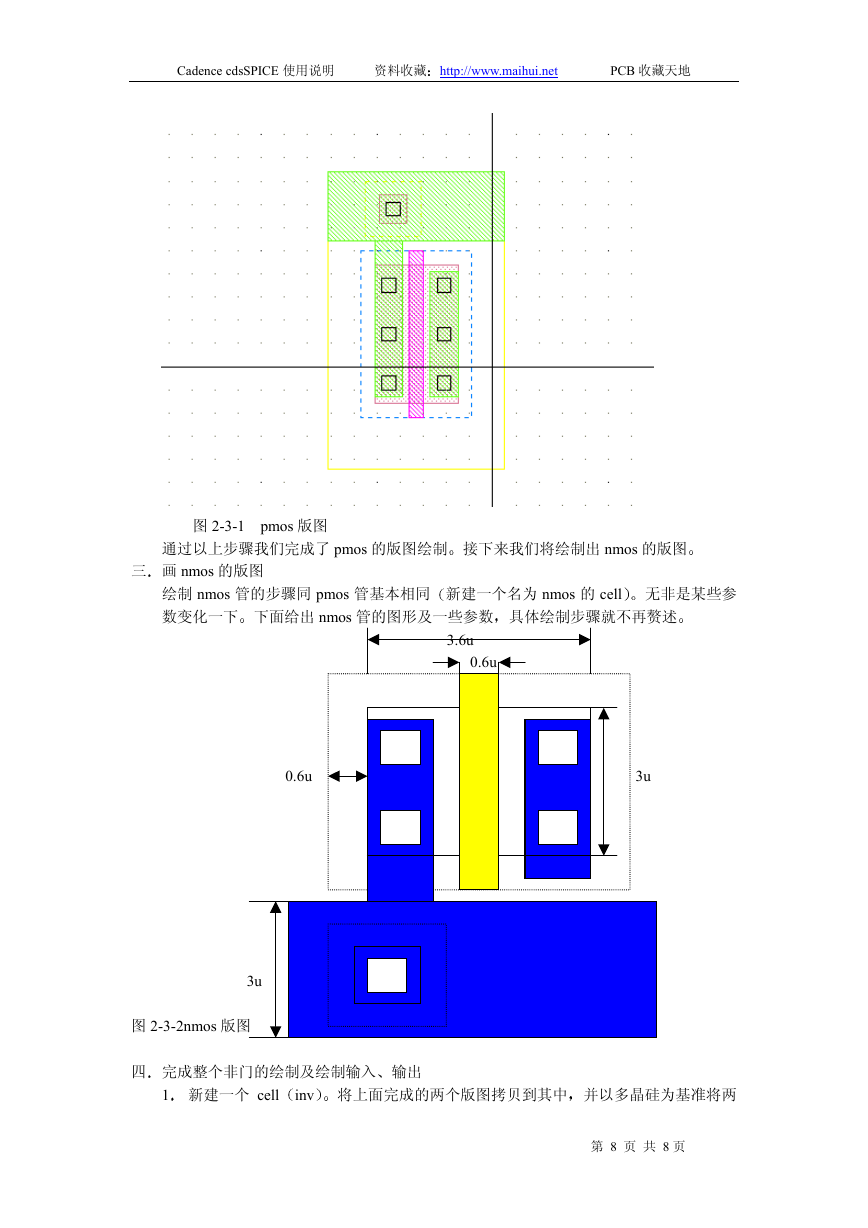

三 画 nmos 的版图

绘制 nmos 管的步骤同 pmos 管基本相同 新建一个名为 nmos 的 cell 无非是某些参

数变化一下 下面给出 nmos 管的图形及一些参数 具体绘制步骤就不再赘述

3.6u

0.6u

0.6u 3u

3u

图 2-3-2nmos 版图

四 完成整个非门的绘制及绘制输入 输出

1

新建一个 cell

inv 将上面完成的两个版图拷贝到其中 并以多晶硅为基准将两

第 8 页 共 8 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc