第1章: 简介信息

1.1 简介

1.2 功能要点

1.3 订购信息(无闪存的器件LPC4350/30/20/10)

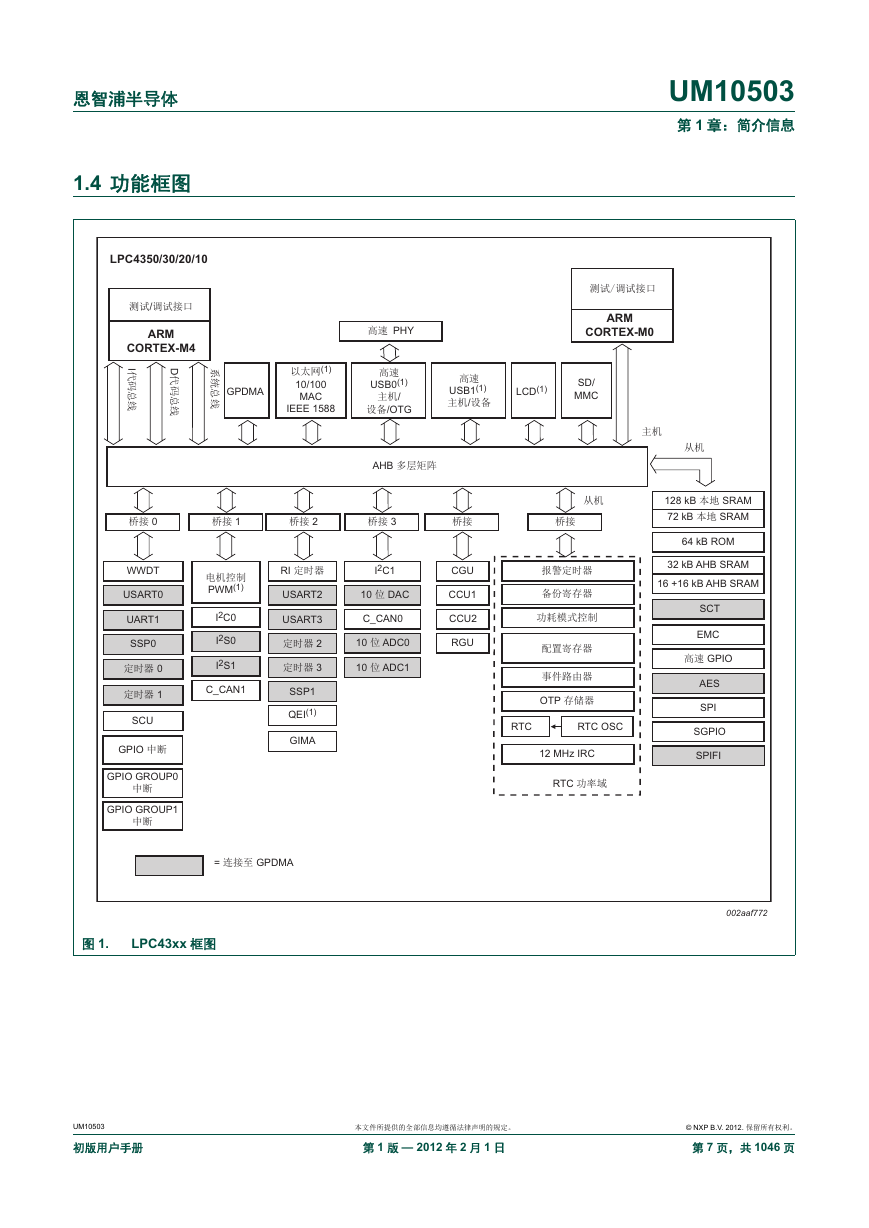

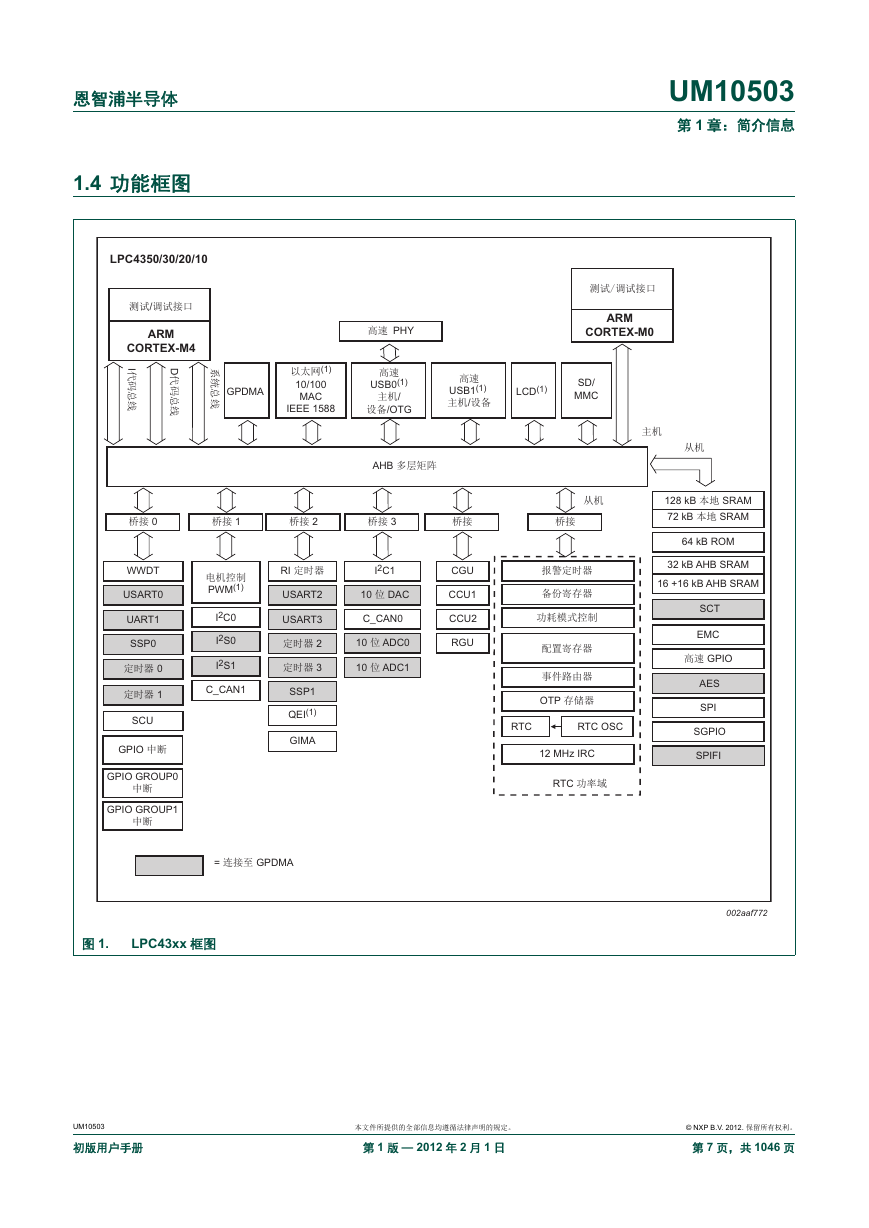

1.4 功能框图

第2章: LPC43xx ARM Cortex-M0协处理器和内核间通信(IPC)

2.1 本章导读

2.2 基本配置

2.3 简介

2.4 简介

2.4.1 硬件

2.4.2 中断处理

2.5 IPC协议描述

2.5.1 IPC队列

2.5.2 协议

2.5.3 示例

第3章: LPC43xx存储器映射

3.1 本章导读

3.2 基本配置

3.3 存储器配置

3.3.1 片内静态RAM

3.3.2 位带机制

3.3.3 掉电模式下的存储器保持

3.3.4 存储器保护单元(MPU)

3.4 存储器映射

3.5 AHB多层矩阵配置

第4章: LPC43xx一次性可编程(OTP)存储器和API

4.1 本章导读

4.2 功能要点

4.3 简介

4.4 寄存器描述

4.5 OTP API

4.5.1 OTP功能分配

4.5.2 OTP API调用

第5章: LPC43xx Boot ROM

5.1 本章导读

5.2 功能要点

5.3 功能说明

5.3.1 AES兼容设备

5.3.2 启动流程(仅适用于无片上闪存的器件)

5.3.3 启动映像格式

5.3.4 启动映像创建

5.3.5 引导流程时序

5.3.6 ISP

第6章: LPC43xx安全API

6.1 本章导读

6.2 功能要点

6.3 简介

6.4 AES API

6.4.1 AES功能分配

6.5 功能说明

6.5.1 AES解密

6.5.2 使用AES硬件加速的CMAC

6.5.3 AES密钥的使用

6.5.4 字节顺序

6.5.5 在深度掉电模式下存储AES密钥

第7章: LPC43xx可嵌套向量中断控制器(NVIC)

7.1 本章导读

7.2 基本配置

7.3 功能要点

7.4 简介

7.5 引脚描述

7.6 中断源

7.6.1 Cortex-M4中断源

7.6.2 Cortex-M0中断源

第8章: LPC43xx事件路由器

8.1 本章导读

8.2 基本配置

8.3 简介

8.4 事件路由器输入

8.5 引脚描述

8.6 寄存器描述

8.6.1 电平配置寄存器

8.6.2 边沿配置寄存器

8.6.3 清除事件使能寄存器

8.6.4 设置事件使能寄存器

8.6.5 事件状态寄存器

8.6.6 事件使能寄存器

8.6.7 清除事件状态寄存器

8.6.8 设置事件状态寄存器

第9章: LPC43xx配置寄存器(CREG)

9.1 本章导读

9.2 基本配置

9.3 功能要点

9.4 寄存器描述

9.4.1 CREG0控制寄存器

9.4.2 ARM Cortex-M4存储器映射寄存器

9.4.3 CREG5控制寄存器

9.4.4 DMA复用寄存器

9.4.5 ETB SRAM配置寄存器

9.4.6 CREG6控制寄存器

9.4.7 Cortex-M4 TXEV事件清除寄存器

9.4.8 器件ID寄存器

9.4.9 Cortex-M0 TXEV事件清除寄存器

9.4.10 ARM Cortex-M0存储器映射寄存器

第10章: LPC43xx电源管理控制器(PMC)

10.1 本章导读

10.2 基本配置

10.3 简介

10.3.1 工作模式

10.3.2 睡眠模式

10.3.3 深度睡眠模式

10.3.4 掉电模式

10.3.5 深度掉电模式

10.3.6 掉电模式下的存储器保持

10.4 寄存器描述

10.4.1 硬件睡眠事件使能寄存器PD0_SLEEP0_HW_ENA

10.4.2 掉电模式寄存器PD0_SLEEP0_MODE

10.5 功能说明

10.5.1 运行时编程

第11章: LPC43xx时钟产生单元(CGU)

11.1 本章导读

11.2 基本配置

11.3 功能要点

11.4 简介

11.5 引脚描述

11.6 寄存器描述

11.6.1 频率监控寄存器

11.6.2 晶体振荡器控制寄存器

11.6.3 PLL0USB寄存器

11.6.4 PLL0AUDIO寄存器

11.6.5 PLL1寄存器

11.6.6 整数分频器寄存器A

11.6.7 整数分频器寄存器B、C、D

11.6.8 整数分频器寄存器E

11.6.9 BASE_SAFE_CLK控制寄存器

11.6.10 BASE_USB0_CLK控制寄存器

11.6.11 BASE_PERIPH_CLK控制寄存器

11.6.12 BASE_USB1_CLK控制寄存器

11.6.13 BASE_M4_CLK至BASE_UART3_CLK控制寄存器

11.6.14 BASE_OUT_CLK寄存器

11.6.15 BASE_APLL_CLK寄存器

11.6.16 BASE_CGU_OUT0_CLK至BASE_CGU_OUT1_CLK寄存器

11.7 功能描述

11.7.1 32 kHz振荡器

11.7.2 IRC

11.7.3 晶体振荡器

11.7.4 PLL0(PLL0USB和PLL0AUDIO)

11.7.5 PLL0AUDIO的小数分频器

11.7.6 PLL1

11.8 CGU配置示例

11.8.1 深度睡眠和掉电模式的CGU编程

11.8.2 对CGU进行编程以使I2S的外围设备时钟速率达到30 MHz

11.8.3 针对USB应用的PLL0USB设置

11.8.4 音频应用的PLL0AUDIO设置

第12章: LPC43xx时钟控制单元(CCU)

12.1 本章导读

12.2 基本配置

12.3 功能要点

12.4 简介

12.5 寄存器描述

12.5.1 电源模式寄存器

12.5.2 基础时钟状态寄存器

12.5.3 CCU1/2分支时钟配置寄存器

12.5.4 CCU1/2分支时钟状态寄存器

第13章: LPC43xx复位产生单元(RGU)

13.1 本章导读

13.2 基本配置

13.3 简介

13.3.1 复位等级

13.4 寄存器概述

13.4.1 RGU复位控制寄存器

13.4.2 RGU复位状态寄存器

13.4.3 RGU复位活动状态寄存器

13.4.4 复位外部状态寄存器

第14章: LPC43xx引脚配置

14.1 本章导读

14.2 引脚说明

第15章: LPC43xx系统控制单元(SCU)/IO配置

15.1 本章导读

15.2 基本配置

15.3 简介

15.3.1 数字引脚功能

15.3.2 数字引脚模式

15.3.3 输入缓冲

15.3.4 可编程干扰滤波器

15.3.5 可编程转换速率

15.3.6 高速引脚

15.3.7 高驱动能力引脚

15.3.8 I2C0总线引脚

15.3.9 USB1 USB1_DP/USB1_DM引脚

15.3.10 EMC信号延迟控制

15.3.11 引脚复用

15.4 寄存器描述

15.4.1 标准电平驱动引脚的引脚配置寄存器

15.4.2 高驱动能力引脚的引脚配置寄存器

15.4.3 高速引脚的引脚配置寄存器

15.4.4 USB1引脚USB1_DP/USB1_DM的引脚配置寄存器

15.4.5 开漏I2C总线引脚的引脚配置寄存器

15.4.6 ADC0功能选择寄存器

15.4.7 ADC1功能选择寄存器

15.4.8 模拟功能选择寄存器

15.4.9 EMC时钟延迟寄存器

15.4.10 引脚中断选择寄存器0

15.4.11 引脚中断选择寄存器1

第16章: LPC43xx全局输入多路复用器阵列(GIMA)

16.1 本章导读

16.2 基本配置

16.3 简介

16.3.1 GIMA事件输入选择

16.3.2 GIMA时钟同步

16.4 寄存器描述

16.4.1 定时器0 CAP0_0捕获输入多路复用器(CAP0_0_IN)

16.4.2 定时器0 CAP0_1捕获输入多路复用器(CAP0_1_IN)

16.4.3 定时器0 CAP0_2捕获输入多路复用器(CAP0_2_IN)

16.4.4 定时器0 CAP0_3捕获输入多路复用器(CAP0_3_IN)

16.4.5 定时器1 CAP1_0捕获输入多路复用器(CAP1_0_IN)

16.4.6 定时器1 CAP1_1捕获输入多路复用器(CAP1_1_IN)

16.4.7 定时器1 CAP1_2捕获输入多路复用器(CAP1_2_IN)

16.4.8 定时器1 CAP1_3捕获输入多路复用器(CAP1_3_IN)

16.4.9 定时器2 CAP2_0捕获输入多路复用器(CAP2_0_IN)

16.4.10 定时器2 CAP2_1捕获输入多路复用器(CAP2_1_IN)

16.4.11 定时器2 CAP2_2捕获输入多路复用器(CAP2_2_IN)

16.4.12 定时器2 CAP2_3捕获输入多路复用器(CAP2_3_IN)

16.4.13 定时器3 CAP3_0捕获输入多路复用器(CAP3_0_IN)

16.4.14 定时器3 CAP3_1捕获输入多路复用器(CAP3_1_IN)

16.4.15 定时器3 CAP3_2捕获输入多路复用器(CAP3_2_IN)

16.4.16 定时器3 CAP3_3捕获输入多路复用器(CAP3_3_IN)

16.4.17 SCT CTIN_0捕获输入多路复用器(CTIN_0_IN)

16.4.18 SCT CTIN_1捕获输入多路复用器(CTIN_1_IN)

16.4.19 SCT CTIN_2捕获输入多路复用器(CTIN_2_IN)

16.4.20 SCT CTIN_3捕获输入多路复用器(CTIN_3_IN)

16.4.21 SCT CTIN_4捕获输入多路复用器(CTIN_4_IN)

16.4.22 SCT CTIN_5捕获输入多路复用器(CTIN_5_IN)

16.4.23 SCT CTIN_6捕获输入多路复用器(CTIN_6_IN)

16.4.24 SCT CTIN_7捕获输入多路复用器(CTIN_7_IN)

16.4.25 VADC启动输入多路复用器(VADC_TRIGGER_IN)

16.4.26 事件路由器输入13多路复用器(EVENTROUTER_13_IN)

16.4.27 事件路由器输入14多路复用器(EVENTROUTER_14_IN)

16.4.28 事件路由器输入16多路复用器(EVENTROUTER_16_IN)

16.4.29 ADC启动0输入多路复用器(ADCSTART0_IN)

16.4.30 ADC启动1输入多路复用器(ADCSTART1_IN)

第17章: LPC43xx GPIO

17.1 本章导读

17.2 基本配置

17.3 功能要点

17.3.1 GPIO引脚中断功能要点

17.3.2 GPIO分组中断功能要点

17.3.3 GPIO端口功能要点

17.4 简介

17.4.1 GPIO引脚中断

17.4.2 GPIO分组中断

17.4.3 GPIO端口

17.5 寄存器描述

17.5.1 GPIO引脚中断寄存器描述

17.5.2 GPIO组0/组1中断寄存器描述

17.5.3 GPIO端口寄存器描述

17.6 功能描述

17.6.1 读取引脚状态

17.6.2 GPIO输出

17.6.3 I/O的掩码

17.6.4 GPIO中断

17.6.5 推荐用法

第18章: LPC43xx串行GPIO (SGPIO)

18.1 本章导读

18.2 基本配置

18.3 功能要点

18.4 简介

18.4.1 中断

18.5 引脚说明

18.6 寄存器描述

18.6.1 引脚多路复用器配置寄存器(OUT_MUX_CFG0至15)

18.6.2 SGPIO多路复用器配置寄存器(SGPIO_MUX_CFG0至15)

18.6.3 位串多路复用器配置寄存器(SLICE_MUX_CFG0至15)

18.6.4 位串数据寄存器(REG0至15)

18.6.5 位串数据影子寄存器(REG_SS0至15)

18.6.6 重新加载寄存器(PRESET0至15)

18.6.7 下行计数器寄存器(COUNT0至15)

18.6.8 位置寄存器(POS0至15)

18.6.9 位串A掩码寄存器(MASK_A)

18.6.10 位串H掩码寄存器(MASK_H)

18.6.11 位串I掩码寄存器(MASK_I)

18.6.12 位串P掩码寄存器(MASK_P)

18.6.13 GPIO输入状态寄存器(GPIO_INREG)

18.6.14 GPIO输出控制寄存器(GPIO_OUTREG)

18.6.15 GPIO输出使能寄存器(GPIO_OENREG)

18.6.16 位串计数使能寄存器(CTRL_ENABLED)

18.6.17 位串计数禁用寄存器(CTRL_DISABLED)

18.6.18 移位时钟中断清除掩码寄存器(CLR_EN_0)

18.6.19 移位时钟中断设置掩码寄存器(SET_EN_0)

18.6.20 移位时钟中断使能寄存器(ENABLE_0)

18.6.21 移位时钟中断状态寄存器(STATUS_0)

18.6.22 移位时钟中断清除状态寄存器(CTR_STATUS_0)

18.6.23 移位时钟中断设置状态寄存器(SET_STATUS_0)

18.6.24 捕获时钟中断清除掩码寄存器(CLR_EN_1)

18.6.25 捕获时钟中断设置掩码寄存器(SET_EN_1)

18.6.26 捕获时钟中断使能(ENABLE_1)

18.6.27 捕获时钟中断状态寄存器(STATUS_1)

18.6.28 捕获时钟中断清除状态寄存器(CTR_STATUS_1)

18.6.29 捕获时钟中断设置状态寄存器(SET_STATUS_1)

18.6.30 模式匹配中断清除掩码寄存器(CLR_EN_2)

18.6.31 模式匹配中断设置掩码寄存器(SET_EN_2)

18.6.32 模式匹配中断使能(ENABLE_2)

18.6.33 模式匹配中断状态寄存器(STATUS_2)

18.6.34 模式匹配中断清除状态寄存器(CTR_STATUS_2)

18.6.35 模式匹配中断设置状态寄存器(SET_STATUS_2)

18.6.36 输入位中断清除掩码寄存器(CLR_EN_3)

18.6.37 输入位匹配中断设置掩码寄存器(SET_EN_3)

18.6.38 输入位匹配中断使能(ENABLE_3)

18.6.39 输入位匹配中断状态寄存器(STATUS_3)

18.6.40 输入位匹配中断清除状态寄存器(CTR_STATUS_3)

18.6.41 输入位匹配中断设置状态寄存器(SET_STATUS_3)

18.7 功能说明

18.7.1 级联

18.7.2 模式匹配

18.7.3 引脚复用

18.7.4 位串多路复用器

18.7.5 内部连接

18.8 示例

18.8.1 多通道I2S

18.8.1.1 I2S位串选择

18.8.1.2 I2S位串配置

18.8.1.3 I2S位串编程

18.8.2 相机接口示例

18.8.2.1 相机接口位串配置

第19章: LPC43xx通用DMA (GPDMA)控制器

19.1 本章导读

19.2 基本配置

19.3 功能要点

19.4 简介

19.5 DMA系统连接

19.5.1 DMA请求信号

19.5.2 DMA响应信号

19.6 寄存器描述

19.6.1 DMA中断状态寄存器

19.6.2 DMA中断终结计数请求状态寄存器

19.6.3 DMA中断终结计数请求清除寄存器

19.6.4 DMA中断错误状态寄存器

19.6.5 DMA中断错误清除寄存器

19.6.6 DMA原始中断终结计数状态寄存器

19.6.7 DMA原始错误中断状态寄存器

19.6.8 DMA使能通道寄存器

19.6.9 DMA 软件连发传送请求寄存器

19.6.10 DMA软件单次请求寄存器

19.6.11 DMA软件最后一个连发请求寄存器

19.6.12 DMA软件最后一个单次请求寄存器

19.6.13 DMA配置寄存器

19.6.14 DMA同步寄存器

19.6.15 DMA通道寄存器

19.6.16 DMA通道源地址寄存器

19.6.17 DMA通道目标地址寄存器

19.6.18 DMA通道链接列表项寄存器

19.6.19 DMA通道控制寄存器

19.6.20 通道配置寄存器

19.7 功能说明

19.7.1 DMA控制器功能描述

19.8 使用DMA控制器

19.8.1 编程DMA控制器

19.8.2 流控制

19.8.3 中断请求

19.8.4 地址产生

19.8.5 分散/聚集

第20章: LPC43xx SD/MMC接口

20.1 本章导读

20.2 基本配置

20.3 功能要点

20.4 简介

20.5 引脚说明

20.6 寄存器描述

20.6.1 控制寄存器(CTRL)

20.6.2 电源使能寄存器(PWREN)

20.6.3 时钟分频器寄存器(CLKDIV)

20.6.4 SD时钟源寄存器(CLKSRC)

20.6.5 时钟使能寄存器(CLKENA)

20.6.6 超时寄存器(TMOUT)

20.6.7 卡类型寄存器(CTYPE)

20.6.8 块大小寄存器(BLKSIZ)

20.6.9 字节计数寄存器(BYTCNT)

20.6.10 中断掩码寄存器(INTMASK)

20.6.11 指令参数寄存器(CMDARG)

20.6.12 指令寄存器(CMD)

20.6.13 响应寄存器0 (RESP0)

20.6.14 响应寄存器1 (RESP1)

20.6.15 响应寄存器2 (RESP2)

20.6.16 响应寄存器3 (RESP3)

20.6.17 掩码中断状态寄存器(MINTSTS)

20.6.18 原始中断状态寄存器(RINTSTS)

20.6.19 状态寄存器(STATUS)

20.6.20 FIFO阈值水印寄存器(FIFOTH)

20.6.21 卡检测寄存器(CDETECT)

20.6.22 写保护寄存器(WRTPRT)

20.6.23 CIU卡已传输字节计数寄存器(TCBCNT)

20.6.24 主机至BIU-FIFO已传输字节计数寄存器(TBBCNT)

20.6.25 去抖动计数寄存器(DEBNCE)

20.6.26 UHS-1寄存器(UHS_REG)

20.6.27 硬件复位(RST_N)

20.6.28 总线模式寄存器(BMOD)

20.6.29 查询需求寄存器(PLDMND)

20.6.30 描述符表基地址寄存器(DBADDR)

20.6.31 内部DMAC状态寄存器(IDSTS)

20.6.32 内部DMAC中断使能寄存器(IDINTEN)

20.6.33 当前主机描述符地址寄存器(DSCADDR)

20.6.34 当前缓冲描述符地址寄存器(BUFADDR)

20.7 功能说明

20.7.1 自动停止。

20.7.2 软件/硬件限制

20.7.3 编程序列

20.7.4 挂起或恢复序列

20.7.5 DMA描述符

第21章: LPC43xx外部存储控制器(EMC)

21.1 本章导读

21.2 基本配置

21.3 功能要点

21.4 简介

21.5 存储组别选择

21.6 引脚说明

21.7 寄存器描述

21.7.1 EMC控制寄存器

21.7.2 EMC状态寄存器

21.7.3 EMC配置寄存器

21.7.4 动态存储器控制寄存器

21.7.5 动态存储器刷新定时器寄存器

21.7.6 动态存储器读配置寄存器

21.7.7 动态存储器预充电命令周期寄存器

21.7.8 动态存储器有效到预充电命令周期寄存器

21.7.9 动态存储器自刷新退出时间寄存器

21.7.10 动态存储器最后一个数据输出到有效时间寄存器

21.7.11 动态存储器数据输入到有效命令时间寄存器

21.7.12 动态存储器写恢复时间寄存器

21.7.13 动态存储器有效到有效命令周期寄存器

21.7.14 动态存储器自动刷新周期寄存器

21.7.15 动态存储器退出自刷新寄存器

21.7.16 动态存储器有效组A到有效组B时间寄存器

21.7.17 动态存储器加载模式寄存器到有效命令时间

21.7.18 静态存储器延长等待寄存器

21.7.19 动态存储器配置寄存器

21.7.20 动态存储器RAS和CAS延迟寄存器

21.7.21 静态存储器配置寄存器

21.7.22 静态存储器写使能延迟寄存器

21.7.23 静态存储器输出使能延迟寄存器

21.7.24 静态存储器读延迟寄存器

21.7.25 静态存储器页面模式读延迟寄存器

21.7.26 静态存储器写延迟寄存器

21.7.27 静态存储器周转期延迟寄存器

21.8 功能说明

21.8.1 AHB从机寄存器接口

21.8.2 AHB从机存储器接口

21.8.3 管脚接口

21.8.4 数据缓冲区

21.9 低功耗

21.9.1 低功耗SDRAM深度睡眠模式

21.9.2 低功耗SDRAM部分阵列刷新

21.10 外部静态存储器接口

21.10.1 32位宽存储组别连接

21.10.2 16位宽存储组别连接

21.10.3 8位宽存储组别连接

第22章: LPC43xx SPI闪存接口(SPIFI)

22.1 本章导读

22.2 基本配置

22.3 功能要点

22.4 简介

22.5 引脚说明

22.6 支持的QSPI设备

第23章: LPC43xx USB0主机/设备/OTG控制器

23.1 本章导读

23.2 基本配置

23.3 功能要点

23.4 简介

23.4.1 功能框图

23.4.2 关于USB OTG

23.4.3 USB首字母缩略词和缩写

23.4.4 发送和接收缓冲区

23.4.5 固定的端点配置

23.5 引脚说明

23.6 寄存器描述

23.6.1 寄存器使用

23.6.2 设备/主机功能寄存器

23.6.3 USB指令寄存器(USBCMD)

23.6.3.1 设备模式

23.6.3.2 主机模式

23.6.4 USB状态寄存器(USBSTS)

23.6.4.1 设备模式

23.6.4.2 主机模式

23.6.5 USB中断寄存器(USBINTR)

23.6.5.1 设备模式

23.6.5.2 主机模式

23.6.6 帧索引寄存器(FRINDEX)

23.6.6.1 设备模式

23.6.6.2 主机模式

23.6.7 设备地址(DEVICEADDR 设备)和周期性列表基址 (PERIODICLISTBASE 主机)寄存器

23.6.7.1 设备模式

23.6.7.2 主机模式

23.6.8 端点列表地址寄存器(端点LISTADDR 设备)和异步列表地址 (ASYNCLISTADDR 主机)寄存器

23.6.8.1 设备模式

23.6.8.2 主机模式

23.6.9 TT控制寄存器(TTCTRL)

23.6.9.1 设备模式

23.6.9.2 主机模式

23.6.10 突发大小寄存器(BURSTSIZE)

23.6.11 传输缓冲区填充调谐寄存器(TXFILLTUNING)

23.6.11.1 设备控制器

23.6.11.2 主机控制器

23.6.12 BINTERVAL寄存器

23.6.13 USB端点NAK寄存器(ENDPTNAK)

23.6.13.1 设备模式

23.6.13.2 主机模式

23.6.14 USB端点NAK使能寄存器(ENDPTNAKEN)

23.6.14.1 设备模式

23.6.14.2 主机模式

23.6.15 端口状态和控制寄存器(PORTSC1)

23.6.15.1 设备模式

23.6.15.2 主机模式

23.6.16 OTG状态和控制寄存器(OTGSC)

23.6.17 USB模式寄存器(USBMODE)

23.6.17.1 设备模式

23.6.17.2 主机模式

23.6.18 USB端点设置状态寄存器(ENDPSETUPSTAT)

23.6.19 USB端点启动寄存器(ENDPTPRIME)

23.6.20 USB端点刷新寄存器(ENDPTFLUSH)

23.6.21 USB端点状态寄存器(ENDPTSTAT)

23.6.22 USB端点完成寄存器(ENDPTCOMPLETE)

23.6.23 USB端点0控制寄存器(ENDPTCTRL0)

23.6.24 端点1到5控制寄存器

23.7 功能说明

23.7.1 OTG核

23.7.2 主机数据结构

23.7.3 主机操作模式

23.7.4 ATX_RGEN模块

23.7.5 ATX收发器

23.7.6 操作模式

23.7.7 SOF/VF指示器

23.7.8 硬件辅助

23.7.8.1 自动复位

23.7.8.2 数据脉冲

23.7.8.3 B断开到A连接(跳变到A外设状态)

23.8 与EHCI标准的偏差

23.8.1 嵌入式事务转换器功能

23.8.1.1 功能寄存器

23.8.1.2 操作寄存器

23.8.1.3 探索

23.8.1.4 数据结构

23.8.1.5 操作模式

23.8.1.5.1 微帧管道

23.8.1.6 拆分状态机

23.8.1.7 异步事务计划和缓冲区管理

23.8.1.8 定期事务计划和缓冲区管理

23.8.1.9 多事务转译器

23.8.2 设备操作

23.8.2.1 USBMODE寄存器

23.8.2.2 寄存器文件的非零字段

23.8.2.3 SOF中断

23.8.3 EHCI其它变型

23.8.3.1 探索

23.8.3.1.1 端口复位

23.8.3.1.2 端口速度检测

23.9 设备数据结构

23.9.1 端点队列头(dQH)

23.9.1.1 端点性能和特点

23.9.1.2 传输重叠

23.9.1.3 当前dTD指针

23.9.1.4 设置缓冲区

23.9.2 端点传输描述符(dTD)

23.9.2.1 确定同步IN端点数据包的数目

23.10 设备操作模型

23.10.1 设备控制器初始化

23.10.2 端口状态和控制

23.10.3 总线复位

23.10.4 挂起/恢复

23.10.4.1 挂起

23.10.4.1.1 操作模式

23.10.4.2 恢复

23.10.5 管理端点

23.10.5.1 端点初始化

23.10.5.2 停止

23.10.5.3 数据切换

23.10.5.3.1 数据切换复位

23.10.5.3.2 数据切换禁止

23.10.6 数据包传输操作模式

23.10.6.1 启动发送端点

23.10.6.2 启动接收端点

23.10.7 中断/批量端点操作模式

23.10.7.1 中断/批量端点总线响应矩阵

23.10.8 控制端点操作模式

23.10.8.1 设置阶段

23.10.8.1.1 使用设置锁定机制处理设置数据包

23.10.8.1.2 使用绊网机制处理设置数据包

23.10.8.2 数据阶段

23.10.8.3 状态阶段

23.10.8.4 控制端点母线响应矩阵

23.10.9 同步端点操作模式

23.10.9.1 同步管道的同步化

23.10.9.2 同步端点母线响应矩阵

23.10.10 管理队列头

23.10.10.1 队列头初始化

23.10.10.2 设置传输的操作模式

23.10.11 使用传输描述符管理传输

23.10.11.1 软件链接指针

23.10.11.2 建立传输描述符

23.10.11.3 执行传输描述符

23.10.11.4 传输完成

23.10.11.5 刷新/取消启动端点

23.10.11.6 设备错误矩阵

23.10.12 服务中断

23.10.12.1 高频中断

23.10.12.2 低频中断

23.10.12.3 错误中断

23.11 USB功率优化

23.11.1 USB功率状态

23.11.2 设备功率状态

23.11.3 主机功率状态

23.11.4 Susp_CTRL模块

第24章: LPC43xx USB1主机/设备控制器

24.1 本章导读

24.2 基本配置

24.2.1 全速模式,无外部PHY

24.2.2 高速模式,有ULPI接口

24.3 功能要点

24.4 简介

24.5 引脚说明

24.6 寄存器描述

24.6.1 设备/主机功能寄存器

24.6.2 USB指令寄存器(USBCMD)

24.6.3 USB状态寄存器(USBSTS)

24.6.4 USB中断寄存器(USBINTR)

24.6.5 帧索引寄存器(FRINDEX)

24.6.6 设备地址(DEVICEADDR)和周期性列表基址(PERIODICLISTBASE)寄存器

24.6.7 端点列表地址寄存器(ENDPOINTLISTADDR)和异步列表地址(ASYNCLISTADDR) 寄存器

24.6.8 TT控制寄存器(TTCTRL)

24.6.9 突发大小寄存器(BURSTSIZE)

24.6.10 传输缓冲区填充调谐寄存器(TXFILLTUNING)

24.6.11 USB ULPI视口寄存器(ULPIVIEWPORT)

24.6.12 BINTERVAL寄存器

24.6.13 USB端点NAK寄存器(ENDPTNAK)

24.6.14 USB端点NAK使能 寄存器(ENDPTNAKEN)

24.6.15 端口状态和控制寄存器(PORTSC1)

24.6.16 USB模式寄存器(USBMODE)

24.6.17 USB端点设置状态寄存器(ENDPSETUPSTAT)

24.6.18 USB端点启动寄存器(ENDPTPRIME)

24.6.19 USB端点刷新寄存器(ENDPTFLUSH)

24.6.20 USB端点状态寄存器(ENDPTSTAT)

24.6.21 USB端点完成寄存器(ENDPTCOMPLETE)

24.6.22 USB端点0控制寄存器(ENDPTCTRL0)

24.6.23 端点1到3控制寄存器

24.7 功能说明

第25章: LPC43xx USB API

25.1 本章导读

25.2 简介

25.3 USB驱动器函数

25.4 调用USB设备驱动器

25.5 USB API

25.5.1 __WORD_BYTE

25.5.2 _BM_T

25.5.3 _CDC_ABSTRACT_CONTROL_MANAGEMENT_DESCRIPTOR

25.5.4 _CDC_CALL_MANAGEMENT_DESCRIPTOR

25.5.5 _CDC_HEADER_DESCRIPTOR

25.5.6 _CDC_LINE_CODING

25.5.7 _CDC_UNION_1SLAVE_DESCRIPTOR

25.5.8 _CDC_UNION_DESCRIPTOR

25.5.9 _DFU_STATUS

25.5.10 _HID_DESCRIPTOR

25.5.11 _HID_DESCRIPTOR::_HID_DESCRIPTOR_LIST

25.5.12 _HID_REPORT_T

25.5.13 _MSC_CBW

25.5.14 _MSC_CSW

25.5.15 _REQUEST_TYPE

25.5.16 _USB_COMMON_DESCRIPTOR

25.5.17 _USB_CORE_DESCS_T

25.5.18 _USB_DEVICE_QUALIFIER_DESCRIPTOR

25.5.19 _USB_DFU_FUNC_DESCRIPTOR

25.5.20 _USB_INTERFACE_DESCRIPTOR

25.5.21 _USB_OTHER_SPEED_CONFIGURATION

25.5.22 _USB_SETUP_PACKET

25.5.23 _USB_STRING_DESCRIPTOR

25.5.24 _WB_T

25.5.25 USBD_API

25.5.26 USBD_API_INIT_PARAM

25.5.27 USBD_CDC_API

25.5.28 USBD_CDC_INIT_PARAM

25.5.29 USBD_CORE_API

25.5.30 USBD_DFU_API

25.5.31 USBD_DFU_INIT_PARAM

25.5.32 USBD_HID_API

25.5.33 USBD_HID_INIT_PARAM

25.5.34 USBD_HW_API

25.5.35 USBD_MSC_API

25.5.36 USBD_MSC_INIT_PARAM

第26章: LPC43xx以太网

26.1 本章导读

26.2 基本配置

26.3 功能要点

26.4 简介

26.5 引脚说明

26.6 寄存器描述

26.6.1 MAC配置寄存器

26.6.2 MAC帧滤波寄存器

26.6.3 MAC Hash表高位寄存器

26.6.4 MAC Hash表低位寄存器

26.6.5 MAC MII地址寄存器

26.6.6 MAC MII数据寄存器

26.6.7 MAC流控制寄存器

26.6.8 MAC VLAN标签寄存器

26.6.9 MAC调试寄存器

26.6.10 MAC远程唤醒帧滤波寄存器

26.6.11 MAC PMT控制和状态寄存器

26.6.12 MAC中断状态寄存器

26.6.13 MAC中断掩码寄存器

26.6.14 MAC地址0高位寄存器

26.6.15 MAC地址0低位寄存器

26.6.16 MAC IEEE1588时间戳控制寄存器

26.6.17 亚秒递增寄存器

26.6.18 系统时间秒寄存器

26.6.19 系统时间纳秒寄存器

26.6.20 系统时间秒更新寄存器

26.6.21 系统时间纳秒更新寄存器

26.6.22 时间戳加数寄存器

26.6.23 目标时间秒寄存器

26.6.24 目标时间纳秒寄存器

26.6.25 系统时间高字秒寄存器

26.6.26 时间戳状态寄存器

26.6.27 PPS控制寄存器

26.6.28 辅助时间戳纳秒寄存器

26.6.29 辅助时间戳秒寄存器

26.6.30 DMA总线模式寄存器

26.6.31 DMA发送轮询请求寄存器

26.6.32 DMA接收轮询请求寄存器

26.6.33 DMA接收描述符列表地址寄存器

26.6.34 DMA发送描述符列表地址寄存器

26.6.35 DMA状态寄存器

26.6.36 DMA操作模式寄存器

26.6.37 DMA中断使能寄存器

26.6.38 DMA遗漏帧和缓冲区溢出计数寄存器

26.6.39 DMA接收中断看门狗定时器寄存器

26.6.40 DMA当前主机发送描述符寄存器

26.6.41 DMA当前主机接收描述符寄存器

26.6.42 DMA当前主机发送缓冲区地址寄存器

26.6.43 DMA当前主机接收缓冲区地址寄存器

26.7 功能说明

26.7.1 电源管理块

26.7.2 DMA仲裁程序功能

26.7.3 IPC接收校验和卸载引擎

26.8 IEEE 1588-2002时间戳

26.8.1 基准时间源

26.8.2 系统时间寄存器模块

26.8.3 发送路径功能

26.8.4 接收路径功能

26.8.5 时间戳误差容限

26.8.6 基准时间时钟的频率范围

26.9 IEEE 1588-2008高级时间戳

26.9.1 点对点PTP透明时钟(P2P TC)消息支持

26.9.2 时钟类型

26.9.3 基准时间源

26.9.4 发送路径功能

26.9.5 接收路径功能

26.9.6 辅助快照

26.10 DMA控制器说明

26.10.1 初始化

26.10.2 传输

26.10.3 以太网描述符

第27章: LPC43xx LCD

27.1 本章导读

27.2 基本配置

27.3 功能要点

27.4 简介

27.4.1 可编程参数

27.4.2 硬件游标支持

27.4.3 所支持的LCD面板

27.5 引脚说明

27.5.1 信号使用

27.6 寄存器描述

27.6.1 水平定时寄存器

27.6.2 垂直定时寄存器

27.6.3 时钟和信号极性寄存器

27.6.4 行结束控制寄存器

27.6.5 上面板帧基址寄存器

27.6.6 下面板帧基址寄存器

27.6.7 LCD控制寄存器

27.6.8 中断掩码寄存器

27.6.9 原始中断状态寄存器

27.6.10 掩码中断状态寄存器

27.6.11 中断清除寄存器

27.6.12 上面板当前地址寄存器

27.6.13 下面板当前地址寄存器

27.6.14 颜色调色板寄存器

27.6.15 游标图像寄存器

27.6.16 游标控制寄存器

27.6.17 游标配置寄存器

27.6.18 游标调色板寄存器0

27.6.19 游标调色板寄存器1

27.6.20 游标XY位置寄存器

27.6.21 游标剪切位置寄存器

27.6.22 游标中断掩码寄存器

27.6.23 游标中断清除寄存器

27.6.24 游标原始中断状态寄存器

27.6.25 游标掩码中断状态寄存器

27.7 LCD控制器功能描述

27.7.1 AHB接口

27.7.2 双DMA FIFO和相关的控制逻辑

27.7.3 像素串行器

27.7.4 RAM调色板

27.7.5 硬件游标

27.7.6 灰阶器

27.7.7 上面板和下面板格式器。

27.7.8 面板时钟生成器

27.7.9 定时控制器

27.7.10 STN和TFT数据选择

27.7.11 中断生成

27.7.12 LCD加电和掉电序列

27.8 LCD时序图

27.9 LCD面板信号的使用

第28章: LPC43xx状态可配置定时器(SCT)

28.1 本章导读

28.2 基本配置

28.3 功能要点

28.4 简介

28.5 引脚说明

28.6 寄存器描述

28.6.1 SCT配置寄存器

28.6.2 SCT控制寄存器

28.6.3 SCT限值寄存器

28.6.4 SCT终止条件寄存器

28.6.5 SCT停止条件寄存器

28.6.6 SCT启动条件寄存器

28.6.7 SCT计数器寄存器

28.6.8 SCT状态寄存器

28.6.9 SCT输入寄存器

28.6.10 SCT匹配/捕获寄存器模式寄存器

28.6.11 SCT输出寄存器

28.6.12 SCT双向输出控制寄存器

28.6.13 SCT解决冲突寄存器

28.6.14 SCT DMA请求0和请求1寄存器

28.6.15 SCT标志使能寄存器

28.6.16 SCT事件标志寄存器

28.6.17 SCT冲突使能寄存器

28.6.18 SCT冲突标志寄存器

28.6.19 SCT匹配寄存器0至15(REGMODEn位=0)

28.6.20 SCT捕获寄存器0至15(REGMODEn位 = 1)

28.6.21 SCT匹配重新载入寄存器0至15(REGMODEn位 = 0)

28.6.22 SCT捕获控制寄存器0至15(REGMODEn位 = 1)

28.6.23 SCT事件状态掩码寄存器0至15

28.6.24 SCT事件控制寄存器0至15

28.6.25 SCT输出设置寄存器0至15

28.6.26 SCT输出清除寄存器0至15

28.7 功能说明

28.7.1 匹配逻辑

28.7.2 捕获逻辑

28.7.3 事件选择

28.7.4 输出生成

28.7.5 中断生成

28.7.6 清除预分频器

28.7.7 匹配事件与I/O事件

28.7.8 DMA操作

28.7.9 匹配/捕获寄存器的替换地址

28.7.10 SCT操作

28.7.10.1 配置SCT

28.7.10.1.1 配置计数器

28.7.10.1.2 配置匹配寄存器和捕获寄存器

28.7.10.1.3 配置事件和事件响应

28.7.10.1.4 配置多个状态

28.7.10.1.5 其他选项

28.7.10.2 操作SCT

28.7.10.3 在不使用状态的情况下配置SCT

28.7.10.4 示例

第29章: LPC43xx定时器0/1/2/3

29.1 本章导读

29.2 基本配置

29.3 功能要点

29.4 简介

29.5 引脚说明

29.6 DMA连接

29.7 寄存器描述

29.7.1 定时器中断寄存器

29.7.2 定时器控制寄存器

29.7.3 定时器计数器寄存器

29.7.4 定时器预分频寄存器

29.7.5 定时器预分频计数器寄存器

29.7.6 定时器匹配控制寄存器

29.7.7 定时器匹配寄存器(MR0 - MR3)

29.7.8 定时器捕获控制寄存器

29.7.9 定时器捕获寄存器(CR0 - CR3)

29.7.10 定时器外部匹配寄存器

29.7.11 定时器计数控制寄存器

29.7.12 DMA操作

29.8 定时器操作示例

29.9 架构

第30章: LPC43xx电动控制PWM(MOTOCONPWM)

30.1 本章导读

30.2 基本配置

30.3 简介

30.4 功能要点

30.5 简介

30.5.1 框图

30.6 引脚说明

30.7 寄存器描述

30.7.1 MCPWM控制寄存器

30.7.1.1 MCPWM控制读取地址

30.7.1.2 MCPWM控制设置地址

30.7.1.3 MCPWM控制清除地址

30.7.2 PWM捕获控制寄存器

30.7.2.1 MCPWM捕获控制读取地址

30.7.2.2 MCPWM捕获控制设置地址

30.7.2.3 MCPWM捕获控制清除地址

30.7.3 MCPWM定时器/计数器0-2寄存器

30.7.4 MCPWM限值0-2寄存器

30.7.5 MCPWM匹配0-2寄存器

30.7.5.1 边缘对齐模式中的匹配寄存器

30.7.5.2 中心对齐模式中的匹配寄存器

30.7.5.3 0和100%的占空比

30.7.6 MCPWM死区寄存器

30.7.7 MCPWM通信模式寄存器

30.7.8 MCPWM捕获读取地址

30.7.9 MCPWM中断寄存器

30.7.9.1 MCPWM中断使能读取地址

30.7.9.2 MCPWM中断使能设置地址

30.7.9.3 MCPWM中断使能清除地址

30.7.10 MCPWM计数控制寄存器

30.7.10.1 MCPWM计数控制读取地址

30.7.10.2 MCPWM计数控制设置地址

30.7.10.3 MCPWM计数控制清除地址

30.7.11 MCPWM中断标志寄存器

30.7.11.1 MCPWM中断标志读取地址

30.7.11.2 MCPWM中断标志设置地址

30.7.11.3 MCPWM中断标志清除地址

30.7.12 MCPWM捕获清除地址

30.8 功能说明

30.8.1 脉冲宽度调制

30.8.2 影子寄存器和同步更新

30.8.3 紧急停机(ABORT)

30.8.4 捕获事件

30.8.5 外部事件计数(计数器模式)

30.8.6 三相直流模式

30.8.7 三相交流模式

30.8.8 中断

第31章: LPC43xx正交编码器接口(QEI)

31.1 本章导读

31.2 基本配置

31.3 功能要点

31.4 简介

31.5 引脚说明

31.6 寄存器描述

31.6.1 控制寄存器

31.6.1.1 QEI控制寄存器

31.6.1.2 QEI状态寄存器

31.6.1.3 QEI配置寄存器

31.6.2 位置、索引和定时器寄存器

31.6.2.1 QEI位置寄存器

31.6.2.2 QEI最大位置寄存器

31.6.2.3 QEI位置比较寄存器0

31.6.2.4 QEI位置比较寄存器1

31.6.2.5 QEI位置比较寄存器2

31.6.2.6 QEI索引计数寄存器

31.6.2.7 QEI索引比较寄存器0

31.6.2.8 QEI定时器重新载入寄存器

31.6.2.9 QEI定时器寄存器

31.6.2.10 QEI速度寄存器

31.6.2.11 QEI速度捕获寄存器

31.6.2.12 QEI速度比较寄存器

31.6.2.13 相位A输入寄存器上的QEI数字过滤器

31.6.2.14 相位B输入寄存器上的QEI数字过滤器

31.6.2.15 索引输入寄存器上的QEI数字过滤器

31.6.2.16 QEI索引接受窗口寄存器

31.6.2.17 QEI索引比较寄存器1

31.6.2.18 QEI索引比较寄存器2

31.6.3 中断寄存器

31.6.3.1 QEI中断使能清除寄存器

31.6.3.2 QEI中断使能设置寄存器

31.6.3.3 QEI中断状态寄存器

31.6.3.4 QEI中断使能寄存器

31.6.3.5 QEI中断状态清除寄存器

31.6.3.6 QEI中断状态设置寄存器

31.7 功能说明

31.7.1 输入信号

31.7.1.1 正交输入信号

31.7.1.2 数字输入过滤

31.7.2 位置捕获

31.7.3 速度捕获

31.7.4 速度比较

第32章: LPC43xx重复性中断定时器(RIT)

32.1 本章导读

32.2 基本配置

32.3 功能要点

32.4 简介

32.5 寄存器描述

32.5.1 RI比较值寄存器

32.5.2 RI掩码寄存器

32.5.3 RI控制寄存器

32.5.4 RI计数器寄存器

32.6 RI定时器操作

第33章: LPC43xx报警定时器

33.1 本章导读

33.2 基本配置

33.3 简介

33.4 寄存器描述

33.4.1 向下计数器寄存器

33.4.2 预设值寄存器

33.4.3 中断清除使能寄存器

33.4.4 中断设置使能寄存器

33.4.5 中断状态寄存器

33.4.6 中断使能寄存器

33.4.7 清除状态寄存器

33.4.8 设置状态寄存器

第34章: LPC43xx窗口化看门狗定时器(WWDT)

34.1 本章导读

34.2 基本配置

34.3 功能要点

34.4 应用

34.5 描述

34.5.1 调试模式中的WWDT特性

34.5.2 掉电模式中的WWDT特性

34.6 时钟

34.7 寄存器描述

34.7.1 看门狗模式寄存器

34.7.2 看门狗定时器常数寄存器

34.7.3 看门狗输入寄存器

34.7.4 看门狗定时器值寄存器

34.7.5 看门狗定时器报警中断寄存器

34.7.6 看门狗定时器窗口寄存器

34.8 功能框图

34.9 看门狗定时示例

第35章: LPC43xx实时时钟(RTC)

35.1 本章导读

35.2 基本配置

35.3 功能要点

35.4 简介

35.5 引脚说明

35.6 寄存器描述

35.6.1 中断位置寄存器

35.6.2 时钟控制寄存器

35.6.3 计数器递增中断寄存器

35.6.4 报警掩码寄存器

35.6.5 完整时间寄存器

35.6.6 时间计数器组

35.6.7 报警寄存器组

35.7 功能说明

35.7.1 校准步骤

第36章: LPC43xx USART0_2_3

36.1 本章导读

36.2 基本配置

36.3 功能要点

36.4 简介

36.5 引脚说明

36.6 寄存器描述

36.6.1 USART接收缓冲寄存器

36.6.2 USART发送器保持寄存器

36.6.3 USART除数锁存LSB和MSB寄存器

36.6.4 USART中断使能寄存器

36.6.5 USART中断识别寄存器

36.6.6 USART FIFO控制寄存器

36.6.7 USART线路控制寄存器

36.6.8 USART线路状态寄存器

36.6.9 USART暂存寄存器

36.6.10 USART自动波特率控制寄存器

36.6.11 IrDA控制寄存器(USART3)

36.6.12 USART小数分频器寄存器(U0FDR - 0x4000 8028)

36.6.13 USART过采样寄存器

36.6.14 USART半双工使能寄存器

36.6.15 USART智能卡接口控制寄存器

36.6.16 USART RS485控制寄存器

36.6.17 USART RS485地址匹配寄存器

36.6.18 USART1 RS485延迟值寄存器

36.6.19 USART同步模式控制寄存器

36.6.20 USART发送使能寄存器

36.7 功能说明

36.7.1 同步模式

36.7.2 RS-485/EIA-485模式的操作

36.7.3 智能卡模式

第37章: LPC43xx UART1

37.1 本章导读

37.2 基本配置

37.3 功能要点

37.4 引脚说明

37.5 寄存器描述

37.5.1 UART1接收器缓冲寄存器(当DLAB = 0时)

37.5.2 UART1发送器保持寄存器(当DLAB = 0时)

37.5.3 UART1除数锁存器LSB和MSB寄存器(当DLAB = 1时)

37.5.4 UART1中断使能寄存器(当DLAB = 0时)

37.5.5 UART1中断识别寄存器

37.5.6 UART1 FIFO控制寄存器

37.5.7 UART1线路控制寄存器

37.5.8 UART1调制解调器控制寄存器

37.5.9 自动流控制

37.5.10 UART1线路状态寄存器

37.5.11 UART1调制解调器状态寄存器

37.5.12 UART1暂存寄存器

37.5.13 UART1自动波特率控制寄存器

37.5.14 自动波特率

37.5.15 自动波特率模式

37.5.16 UART1小数分频器寄存器

37.5.17 UART1发送使能寄存器

37.5.18 UART1 RS485控制寄存器

37.5.19 UART1 RS-485地址匹配寄存器

37.5.20 UART1 RS-485延迟值寄存器

37.5.21 RS-485/EIA-485模式的操作

37.5.22 UART1 FIFO电平寄存器

37.6 架构

第38章: LPC43xx SSP0/1

38.1 本章导读

38.2 基本配置

38.3 功能要点

38.4 简介

38.5 引脚说明

38.6 寄存器描述

38.6.1 SSP控制寄存器0

38.6.2 SSP控制寄存器1

38.6.3 SSP数据寄存器

38.6.4 SSP状态寄存器

38.6.5 SSP时钟预分频寄存器

38.6.6 SSP中断掩码设置/清除寄存器

38.6.7 SSP原始中断状态寄存器

38.6.8 SSP掩码中断状态寄存器

38.6.9 SSP中断清除寄存器

38.6.10 SSP DMA控制寄存器

38.7 功能说明

38.7.1 德州仪器同步串行帧格式

38.7.2 SPI帧格式

38.7.3 国家半导体Microwire帧格式

第39章: LPC43xx SPI

39.1 本章导读

39.2 基本配置

39.3 功能要点

39.4 简介

39.5 引脚说明

39.6 寄存器描述

39.6.1 SPI控制寄存器

39.6.2 SPI状态寄存器

39.6.3 SPI数据寄存器

39.6.4 SPI时钟计数器寄存器

39.6.5 SPI测试控制寄存器

39.6.6 SPI测试状态寄存器

39.6.7 SPI中断寄存器

39.7 功能说明

39.7.1 SPI数据传送

39.7.2 一般信息

39.7.3 主机操作

39.7.4 从机操作

39.7.5 异常状况

第40章: LPC43xx I2S接口

40.1 本章导读

40.2 基本配置

40.3 功能要点

40.4 简介

40.4.1 I2S连接方案

40.4.2 GIMA的I2S连接

40.5 引脚描述

40.6 寄存器描述

40.6.1 I2S数字音频输出寄存器

40.6.2 I2S数字音频输入寄存器

40.6.3 I2S发送FIFO寄存器

40.6.4 接收FIFO寄存器

40.6.5 I2S状态反馈寄存器

40.6.6 I2S DMA配置寄存器1

40.6.7 I2S DMA配置寄存器2

40.6.8 I2S中断请求控制寄存器

40.6.9 I2S发送时钟速率寄存器

40.6.10 I2S接收时钟速率寄存器

40.6.11 I2S发送时钟位速率寄存器

40.6.12 I2S接收时钟位速率寄存器

40.6.13 I2S发送模式控制寄存器

40.6.14 I2S接收模式控制寄存器

40.7 功能描述

40.7.1 I2S的发送和接收接口

40.7.2 I2S操作模式

40.7.3 FIFO控制器

第41章: LPC43xx C_CAN

41.1 本章导读

41.2 基本配置

41.3 功能要点

41.4 简介

41.5 引脚描述

41.6 寄存器描述

41.6.1 CAN协议寄存器

41.6.2 消息接口寄存器

41.6.3 消息处理器寄存器

41.6.4 CAN定时寄存器

41.7 功能描述

41.7.1 复位后C_CAN控制器状态

41.7.2 C_CAN操作模式

41.7.3 CAN消息处理器

41.7.4 中断处理

41.7.5 位时序

第42章: LPC43xx I2C总线接口

42.1 本章导读

42.2 基本配置

42.3 功能要点

42.4 应用

42.5 简介

42.5.1 I2C超快速模式

42.6 引脚说明

42.7 寄存器描述

42.7.1 I2C控制设置寄存器

42.7.2 I2C状态寄存器

42.7.3 I2C数据寄存器

42.7.4 I2C从机地址寄存器0

42.7.5 I2C SCL高、低占空比寄存器

42.7.6 I2C控制清除寄存器

42.7.7 I2C监控模式控制寄存器

42.7.8 I2C从机地址寄存器

42.7.9 I2C数据缓冲寄存器

42.7.10 I2C掩码寄存器

42.8 I2C操作模式

42.8.1 主发送器模式

42.8.2 主接收器模式

42.8.3 从属接收器模式

42.8.4 从属发送器模式

42.9 I2C执行和操作

42.9.1 输入滤波器与输出级

42.9.2 地址寄存器ADR0~ADR3

42.9.3 地址掩码寄存器,MASK0~MASK3

42.9.4 比较器

42.9.5 移位寄存器,DAT

42.9.6 仲裁与同步逻辑

42.9.7 串行时钟生成器

42.9.8 时序与控制

42.9.9 控制寄存器ICONSET和CONCLR

42.9.10 状态解码器与状态寄存器

42.10 I2C操作模式详解

42.10.1 主发送器模式

42.10.2 主接收器模式

42.10.3 从属接收器模式

42.10.4 从属发送器模式

42.10.5 其它状态

42.10.6 某些特殊情况

42.10.7 I2C状态服务程序

42.10.8 初始化

42.10.9 I2C中断服务

42.10.10 状态服务程序

42.10.11 配合实际应用的状态服务

42.11 软件示例

42.11.1 初始化程序

42.11.2 启动主机发送功能

42.11.3 启动主机接收功能

42.11.4 I2C中断程序

42.11.5 无指定模式的状态

42.11.6 主发送状态

42.11.7 主接收状态

42.11.8 从接收状态

42.11.9 从发送状态

第43章: LPC43xx 10位ADC0/1

43.1 本章导读

43.2 基本配置

43.3 功能要点

43.4 简介

43.5 引脚说明

43.6 寄存器描述

43.6.1 A/D控制寄存器

43.6.2 A/D全局数据寄存器。

43.6.3 A/D中断使能寄存器

43.6.4 A/D数据寄存器

43.6.5 A/D状态寄存器

43.7 操作

43.7.1 硬件启动转换

43.7.2 中断

43.7.3 DMA控制

第44章: LPC43xx DAC

44.1 本章导读

44.2 基本配置

44.3 功能要点

44.4 引脚说明

44.5 寄存器描述

44.5.1 D/A转换器寄存器

44.5.2 D/A转换器控制寄存器

44.5.3 D/A转换器计数器值寄存器

44.6 功能说明

44.6.1 DMA计数器

44.6.2 双缓冲

第45章: LPC43xx闪存编程/ISP和IAP

45.1 本章导读

45.2 简介

45.3 功能要点

45.4 描述

45.4.1 复位后的存储器映射

45.4.2 通信协议

45.5 带闪存的LPC43xx器件的启动过程流程图

45.6 扇区号

45.7 代码读保护(CRP)

45.8 ISP命令

45.8.1 解锁<解锁代码>

45.8.2 设置波特率<波特率> <停止位>

45.8.3 回应<设定>

45.8.4 写RAM <起始地址> <字节数>

45.8.5 读存储器<地址> <字节数>

45.8.6 准备写操作的扇区<起始扇区号> <结束扇区号>

45.8.7 将RAM内容复制到闪存 <闪存地址> <字节数>

45.8.8 运行<地址> <模式>

45.8.9 擦除扇区<起始扇区号> <结束扇区号>

45.8.10 扇区查空<起始扇区号> <结束扇区号>

45.8.11 读器件标识号

45.8.12 读取启动代码版本号

45.8.13 读取设备序列号

45.8.14 比较<地址1> <地址2> <字节数>

45.8.15 ISP返回代码

45.9 IAP命令

45.9.1 准备写操作扇区

45.9.2 复制RAM到闪存

45.9.3 擦除扇区

45.9.4 空白检查扇区

45.9.5 读取器件识别号

45.9.6 读取启动代码版本号

45.9.7 读取设备序列号

45.9.8 比较<地址1> <地址2> <字节数>

45.9.9 重新调用ISP

45.9.10 IAP状态代码

45.10 JTAG闪存编程接口

45.11 闪存签名生成

45.11.1 用于生成签名的寄存器描述

45.11.2 签名生成的算法和步骤

第46章: LPC43xx JTAG,串行调试接口(SWD)和跟踪功能

46.1 本章导读

46.2 基本配置

46.3 功能要点

46.4 描述

46.5 引脚说明

46.6 调试连接

46.6.1 ARM标准JTAG连接器(20引脚)

46.6.2 Cortex调试连接器(10引脚)

46.6.3 Cortex调试 + ETM连接器(20引脚)

46.7 调试注意事项

46.8 调试存储器重新映射

46.9 JTAG TAP识别

第47章: LPC43xx ARM Cortex M0/M4参考

47.1 本章导读

47.2 Cortex-M4指令集汇总

47.3 Cortex-M0指令集汇总

第48章: 补充信息

48.1 缩略词

48.2 法律信息

48.2.1 用户手册状态

48.2.2 定义

48.2.3 免责声明

48.2.4 商标

48.3 表

48.4 图

48.5 内容

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc