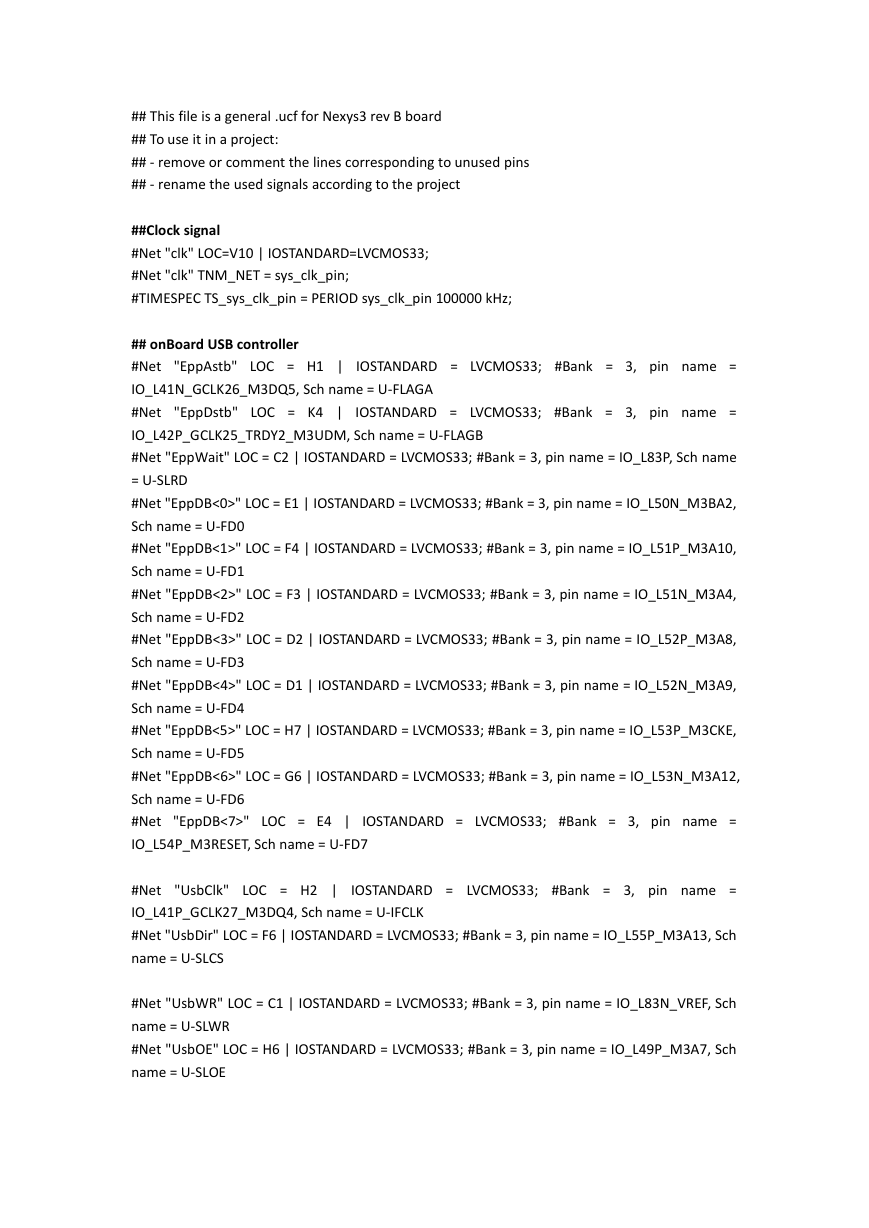

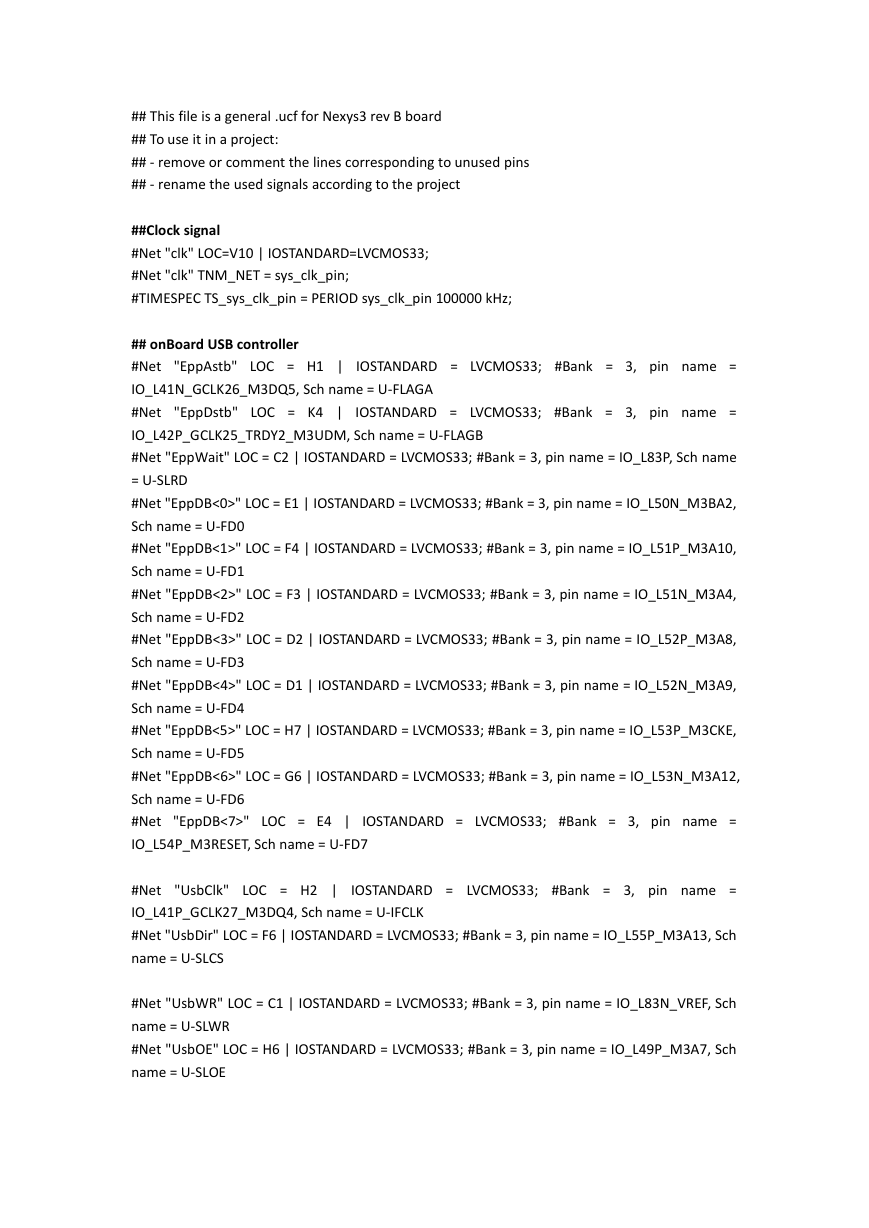

## This file is a general .ucf for Nexys3 rev B board

## To use it in a project:

## - remove or comment the lines corresponding to unused pins

## - rename the used signals according to the project

##Clock signal

#Net "clk" LOC=V10 | IOSTANDARD=LVCMOS33;

#Net "clk" TNM_NET = sys_clk_pin;

#TIMESPEC TS_sys_clk_pin = PERIOD sys_clk_pin 100000 kHz;

"EppDstb" LOC = K4 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

"EppAstb" LOC = H1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

## onBoard USB controller

#Net

IO_L41N_GCLK26_M3DQ5, Sch name = U-FLAGA

#Net

IO_L42P_GCLK25_TRDY2_M3UDM, Sch name = U-FLAGB

#Net "EppWait" LOC = C2 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L83P, Sch name

= U-SLRD

#Net "EppDB<0>" LOC = E1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L50N_M3BA2,

Sch name = U-FD0

#Net "EppDB<1>" LOC = F4 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L51P_M3A10,

Sch name = U-FD1

#Net "EppDB<2>" LOC = F3 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L51N_M3A4,

Sch name = U-FD2

#Net "EppDB<3>" LOC = D2 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L52P_M3A8,

Sch name = U-FD3

#Net "EppDB<4>" LOC = D1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L52N_M3A9,

Sch name = U-FD4

#Net "EppDB<5>" LOC = H7 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L53P_M3CKE,

Sch name = U-FD5

#Net "EppDB<6>" LOC = G6 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L53N_M3A12,

Sch name = U-FD6

#Net "EppDB<7>" LOC = E4 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L54P_M3RESET, Sch name = U-FD7

"UsbClk"

LOC = H2 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

#Net

IO_L41P_GCLK27_M3DQ4, Sch name = U-IFCLK

#Net "UsbDir" LOC = F6 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L55P_M3A13, Sch

name = U-SLCS

#Net "UsbWR" LOC = C1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L83N_VREF, Sch

name = U-SLWR

#Net "UsbOE" LOC = H6 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L49P_M3A7, Sch

name = U-SLOE

�

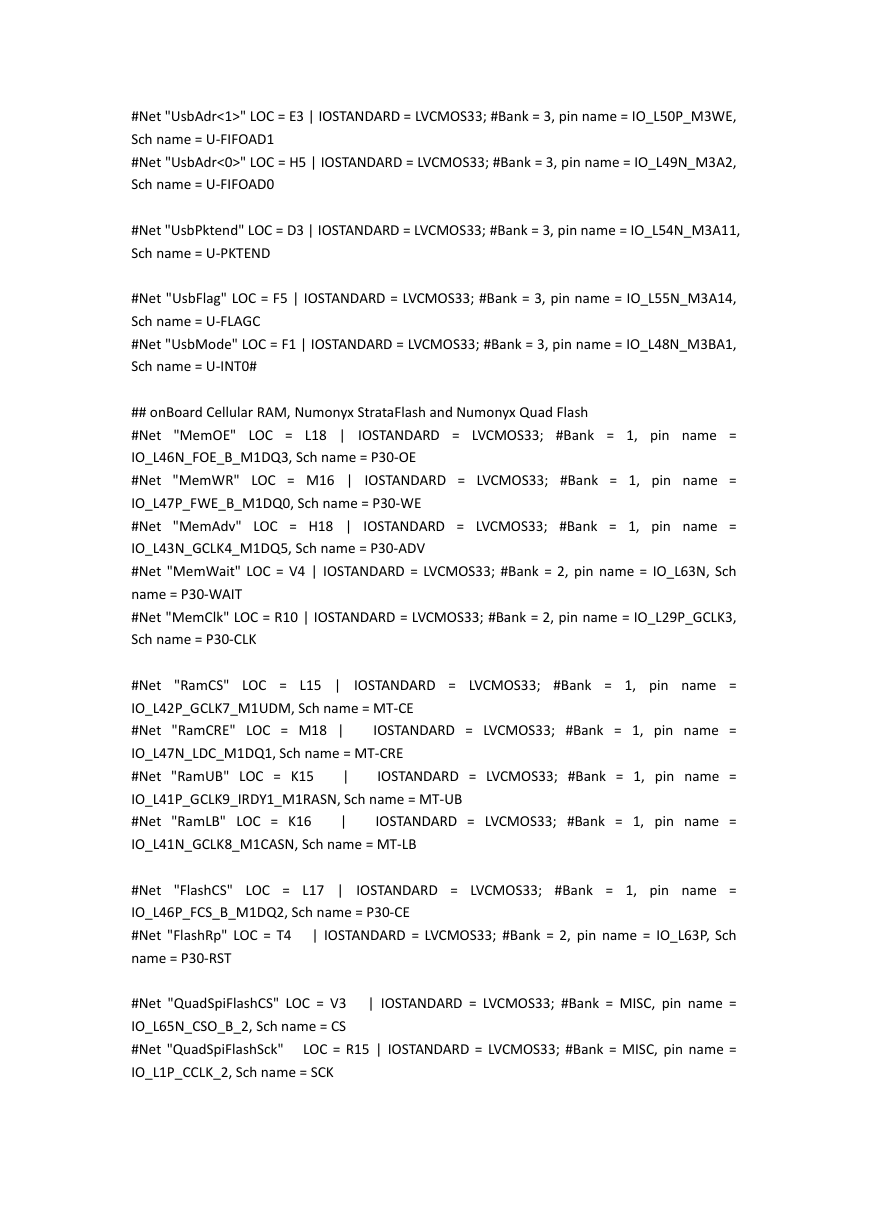

#Net "UsbAdr<1>" LOC = E3 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L50P_M3WE,

Sch name = U-FIFOAD1

#Net "UsbAdr<0>" LOC = H5 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L49N_M3A2,

Sch name = U-FIFOAD0

#Net "UsbPktend" LOC = D3 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L54N_M3A11,

Sch name = U-PKTEND

#Net "UsbFlag" LOC = F5 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L55N_M3A14,

Sch name = U-FLAGC

#Net "UsbMode" LOC = F1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L48N_M3BA1,

Sch name = U-INT0#

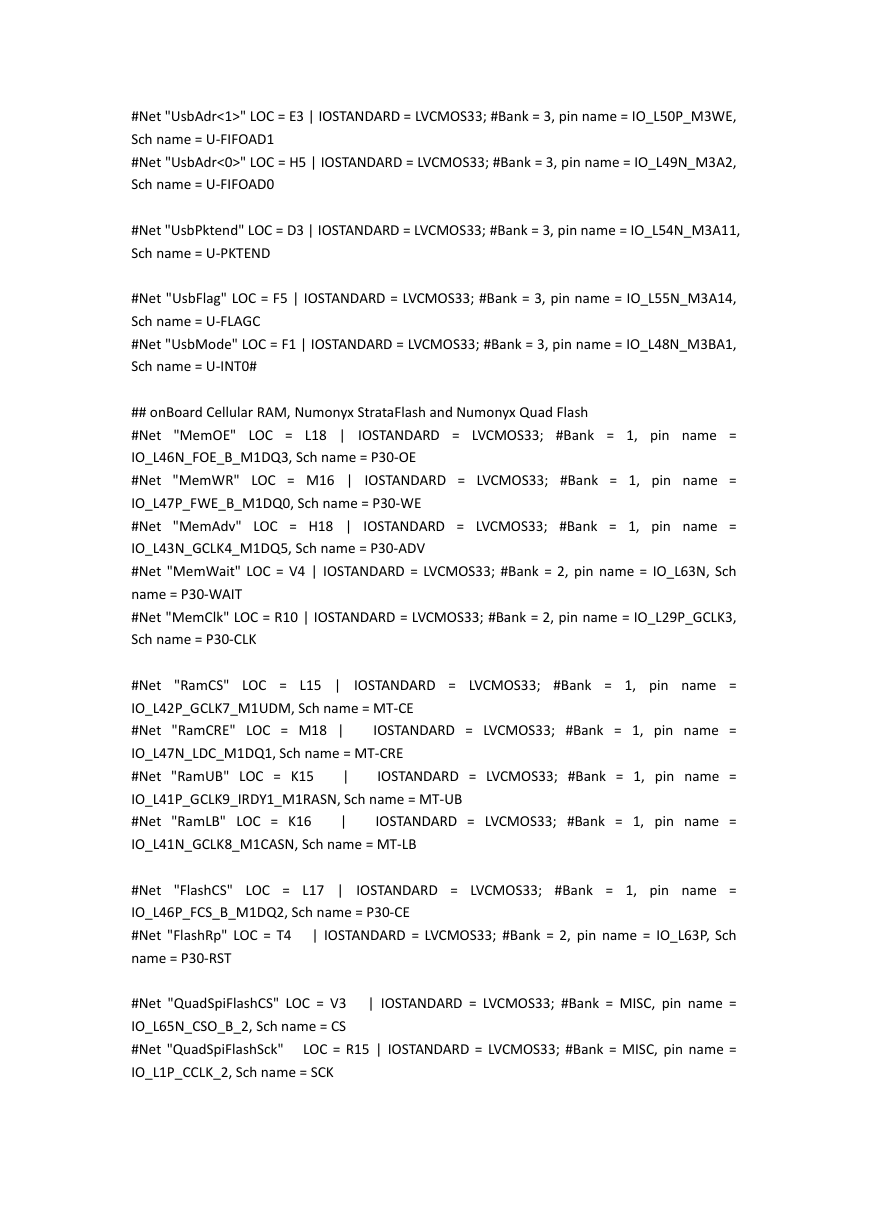

"MemOE" LOC = L18 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

## onBoard Cellular RAM, Numonyx StrataFlash and Numonyx Quad Flash

#Net

IO_L46N_FOE_B_M1DQ3, Sch name = P30-OE

#Net "MemWR" LOC = M16 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IO_L47P_FWE_B_M1DQ0, Sch name = P30-WE

#Net "MemAdv" LOC = H18 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IO_L43N_GCLK4_M1DQ5, Sch name = P30-ADV

#Net "MemWait" LOC = V4 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L63N, Sch

name = P30-WAIT

#Net "MemClk" LOC = R10 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L29P_GCLK3,

Sch name = P30-CLK

LOC = L15 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

"RamCS"

#Net

IO_L42P_GCLK7_M1UDM, Sch name = MT-CE

#Net "RamCRE" LOC = M18 |

IO_L47N_LDC_M1DQ1, Sch name = MT-CRE

#Net "RamUB" LOC = K15

IO_L41P_GCLK9_IRDY1_M1RASN, Sch name = MT-UB

#Net "RamLB" LOC = K16

IO_L41N_GCLK8_M1CASN, Sch name = MT-LB

|

|

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

"FlashCS" LOC = L17 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

| IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L63P, Sch

#Net

IO_L46P_FCS_B_M1DQ2, Sch name = P30-CE

#Net "FlashRp" LOC = T4

name = P30-RST

#Net "QuadSpiFlashCS" LOC = V3

IO_L65N_CSO_B_2, Sch name = CS

#Net "QuadSpiFlashSck"

IO_L1P_CCLK_2, Sch name = SCK

| IOSTANDARD = LVCMOS33; #Bank = MISC, pin name =

LOC = R15 | IOSTANDARD = LVCMOS33; #Bank = MISC, pin name =

�

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

|

|

|

|

|

|

|

#Net "MemAdr<1>" LOC = K18

IO_L45N_A0_M1LDQSN, Sch name = P30-A0

#Net "MemAdr<2>" LOC = K17

IO_L45P_A1_M1LDQS, Sch name = P30-A1

#Net "MemAdr<3>" LOC = J18

IO_L44N_A2_M1DQ7, Sch name = P30-A2

#Net "MemAdr<4>" LOC = J16

IO_L44P_A3_M1DQ6, Sch name = P30-A3

#Net "MemAdr<5>" LOC = G18

IO_L38N_A4_M1CLKN, Sch name = P30-A4

#Net "MemAdr<6>" LOC = G16

IO_L38P_A5_M1CLK, Sch name = P30-A5

#Net "MemAdr<7>" LOC = H16

|

IO_L37N_A6_M1A1, Sch name = P30-A6

#Net "MemAdr<8>" LOC = H15

|

IO_L37P_A7_M1A0, Sch name = P30-A7

#Net "MemAdr<9>" LOC = H14

|

IO_L36N_A8_M1BA1, Sch name = P30-A8

#Net "MemAdr<10>" LOC = H13

IO_L36P_A9_M1BA0, Sch name = P30-A9

#Net "MemAdr<11>" LOC = F18

IO_L35N_A10_M1A2, Sch name = P30-A10

#Net "MemAdr<12>" LOC = F17

IO_L35P_A11_M1A7, Sch name = P30-A11

#Net "MemAdr<13>" LOC = K13

IO_L34N_A12_M1BA2, Sch name = P30-A12

#Net "MemAdr<14>" LOC = K12

IO_L34P_A13_M1WE, Sch name = P30-A13

#Net "MemAdr<15>" LOC = E18

IO_L33N_A14_M1A4, Sch name = P30-A14

#Net "MemAdr<16>" LOC = E16

IO_L33P_A15_M1A10, Sch name = P30-A15

#Net "MemAdr<17>" LOC = G13

IO_L32N_A16_M1A9, Sch name = P30-A16

#Net "MemAdr<18>" LOC = H12

IO_L32P_A17_M1A8, Sch name = P30-A17

#Net "MemAdr<19>" LOC = D18

IO_L31N_A18_M1A12, Sch name = P30-A18

#Net "MemAdr<20>" LOC = D17

IO_L31P_A19_M1CKE, Sch name = P30-A19

#Net "MemAdr<21>" LOC = G14

IO_L30N_A20_M1A11, Sch name = P30-A20

#Net "MemAdr<22>" LOC = F14

IO_L30P_A21_M1RESET Sch name = P30-A21

|

|

|

|

|

|

|

|

|

|

|

|

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

�

|

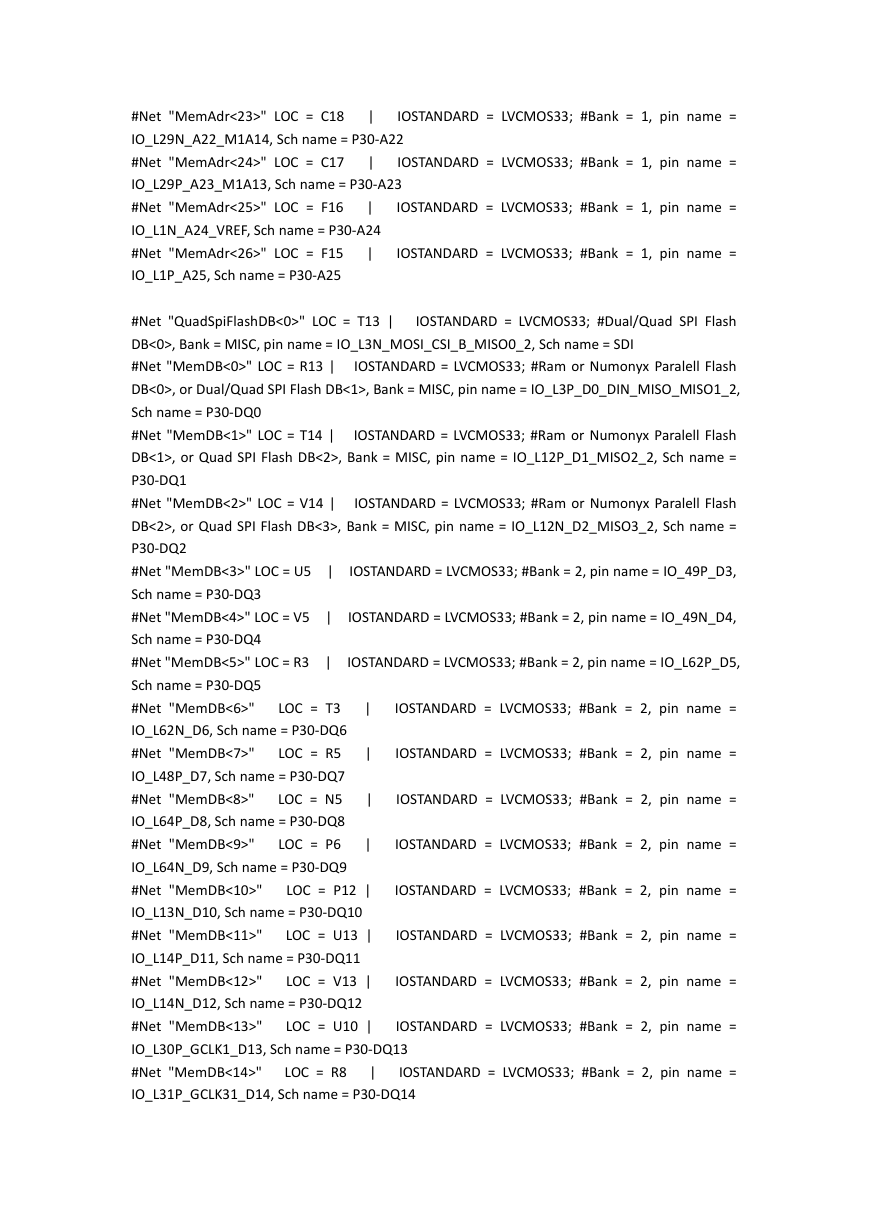

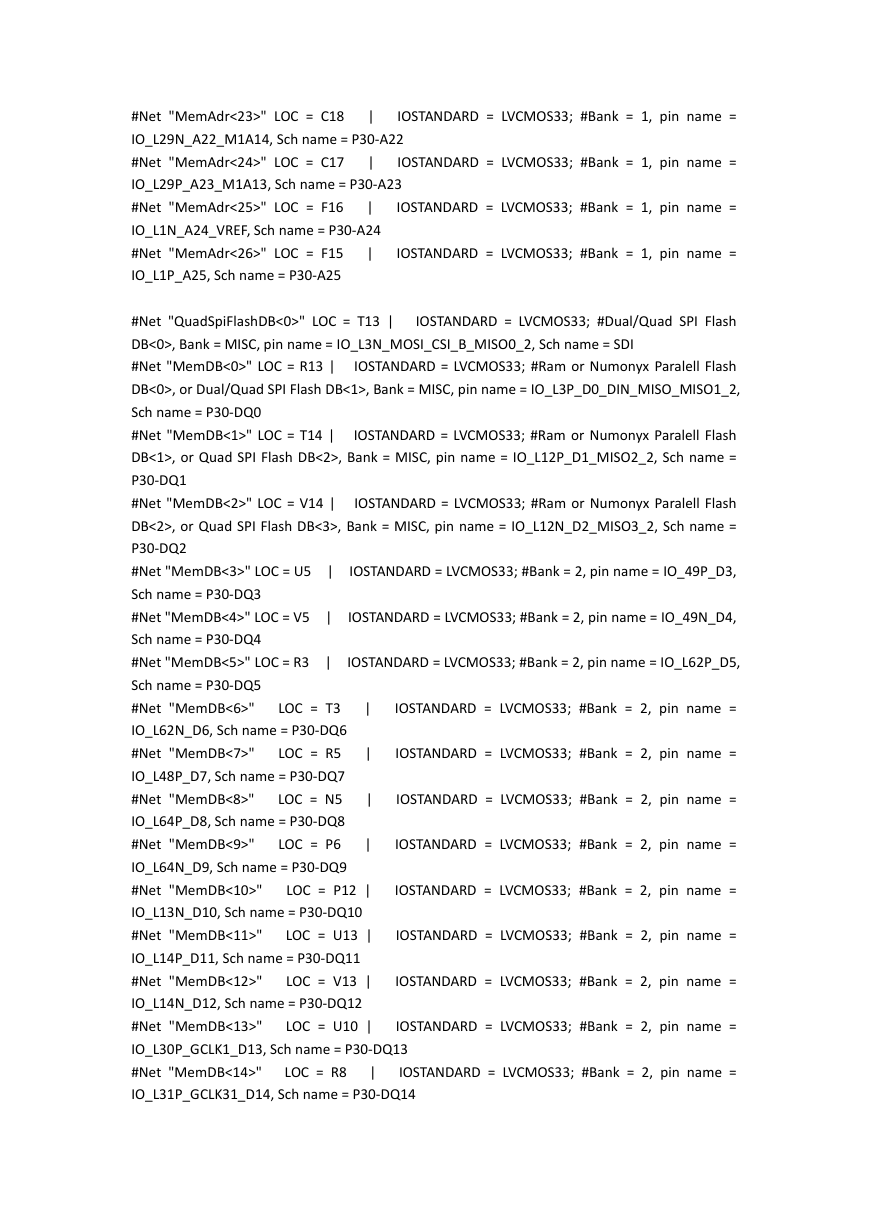

#Net "MemAdr<23>" LOC = C18

IO_L29N_A22_M1A14, Sch name = P30-A22

#Net "MemAdr<24>" LOC = C17

IO_L29P_A23_M1A13, Sch name = P30-A23

#Net "MemAdr<25>" LOC = F16

|

IO_L1N_A24_VREF, Sch name = P30-A24

#Net "MemAdr<26>" LOC = F15

|

IO_L1P_A25, Sch name = P30-A25

|

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IOSTANDARD = LVCMOS33; #Dual/Quad SPI Flash

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_49P_D3,

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_49N_D4,

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L62P_D5,

#Net "QuadSpiFlashDB<0>" LOC = T13 |

DB<0>, Bank = MISC, pin name = IO_L3N_MOSI_CSI_B_MISO0_2, Sch name = SDI

#Net "MemDB<0>" LOC = R13 |

IOSTANDARD = LVCMOS33; #Ram or Numonyx Paralell Flash

DB<0>, or Dual/Quad SPI Flash DB<1>, Bank = MISC, pin name = IO_L3P_D0_DIN_MISO_MISO1_2,

Sch name = P30-DQ0

#Net "MemDB<1>" LOC = T14 |

IOSTANDARD = LVCMOS33; #Ram or Numonyx Paralell Flash

DB<1>, or Quad SPI Flash DB<2>, Bank = MISC, pin name = IO_L12P_D1_MISO2_2, Sch name =

P30-DQ1

#Net "MemDB<2>" LOC = V14 |

IOSTANDARD = LVCMOS33; #Ram or Numonyx Paralell Flash

DB<2>, or Quad SPI Flash DB<3>, Bank = MISC, pin name = IO_L12N_D2_MISO3_2, Sch name =

P30-DQ2

#Net "MemDB<3>" LOC = U5

Sch name = P30-DQ3

#Net "MemDB<4>" LOC = V5

Sch name = P30-DQ4

#Net "MemDB<5>" LOC = R3

Sch name = P30-DQ5

#Net "MemDB<6>"

LOC = T3

IO_L62N_D6, Sch name = P30-DQ6

#Net "MemDB<7>"

LOC = R5

IO_L48P_D7, Sch name = P30-DQ7

#Net "MemDB<8>"

LOC = N5

IO_L64P_D8, Sch name = P30-DQ8

#Net "MemDB<9>"

LOC = P6

IO_L64N_D9, Sch name = P30-DQ9

#Net "MemDB<10>"

LOC = P12 |

IO_L13N_D10, Sch name = P30-DQ10

#Net "MemDB<11>"

LOC = U13 |

IO_L14P_D11, Sch name = P30-DQ11

LOC = V13 |

#Net "MemDB<12>"

IO_L14N_D12, Sch name = P30-DQ12

#Net "MemDB<13>"

LOC = U10 |

IO_L30P_GCLK1_D13, Sch name = P30-DQ13

#Net "MemDB<14>"

IO_L31P_GCLK31_D14, Sch name = P30-DQ14

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

LOC = R8

|

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

|

|

|

|

|

|

|

�

#Net "MemDB<15>"

IO_L31N_GCLK30_D15, Sch name = P30-DQ15

LOC = T8

|

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

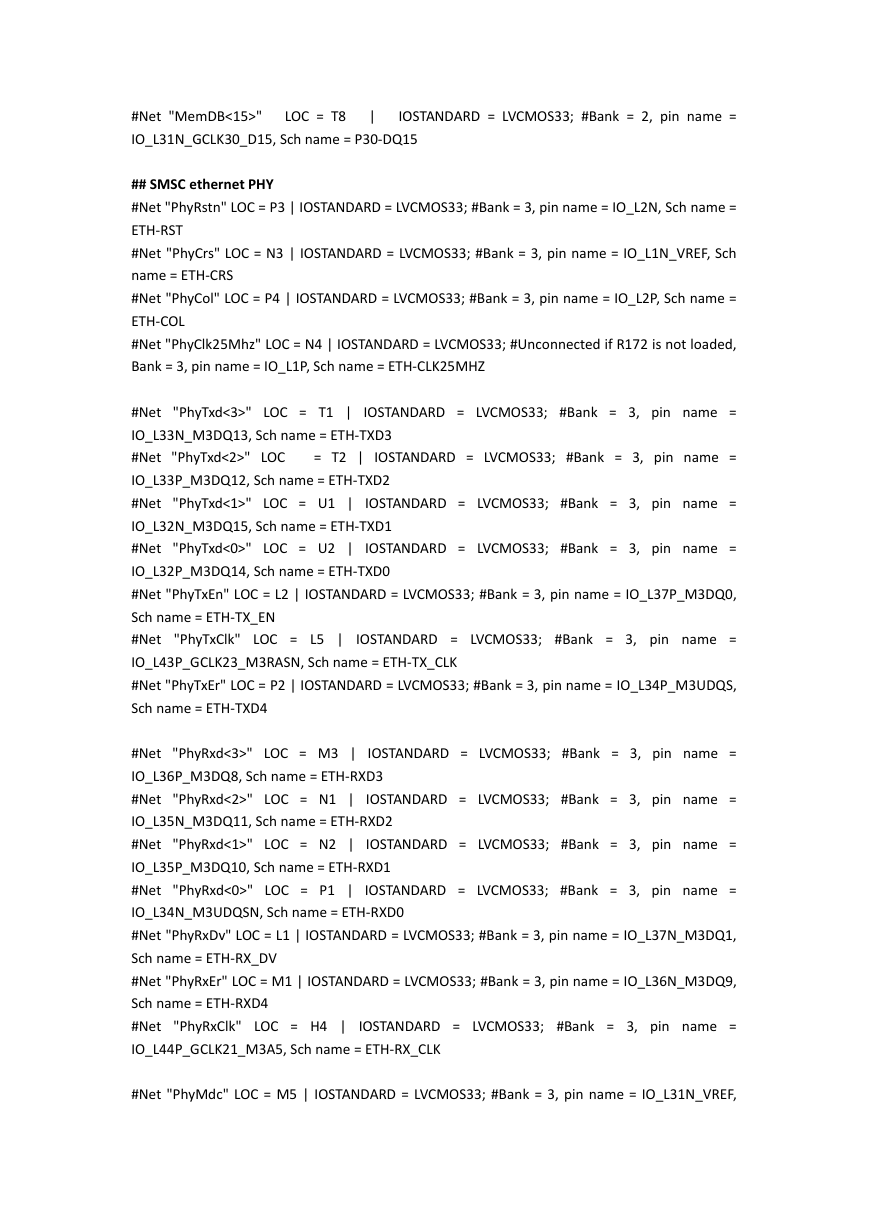

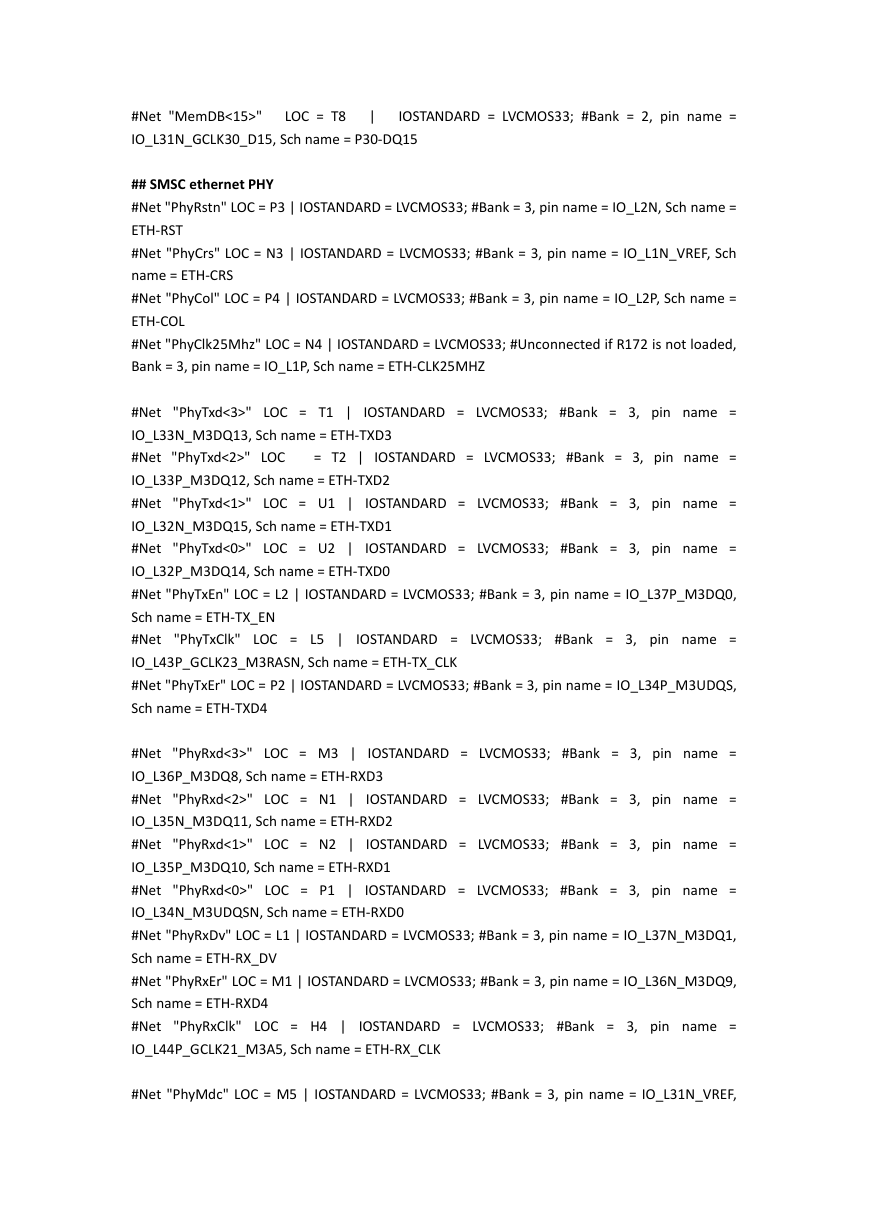

## SMSC ethernet PHY

#Net "PhyRstn" LOC = P3 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L2N, Sch name =

ETH-RST

#Net "PhyCrs" LOC = N3 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L1N_VREF, Sch

name = ETH-CRS

#Net "PhyCol" LOC = P4 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L2P, Sch name =

ETH-COL

#Net "PhyClk25Mhz" LOC = N4 | IOSTANDARD = LVCMOS33; #Unconnected if R172 is not loaded,

Bank = 3, pin name = IO_L1P, Sch name = ETH-CLK25MHZ

= T2 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

#Net "PhyTxd<3>" LOC = T1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L33N_M3DQ13, Sch name = ETH-TXD3

#Net "PhyTxd<2>" LOC

IO_L33P_M3DQ12, Sch name = ETH-TXD2

#Net "PhyTxd<1>" LOC = U1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L32N_M3DQ15, Sch name = ETH-TXD1

#Net "PhyTxd<0>" LOC = U2 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L32P_M3DQ14, Sch name = ETH-TXD0

#Net "PhyTxEn" LOC = L2 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L37P_M3DQ0,

Sch name = ETH-TX_EN

#Net

IO_L43P_GCLK23_M3RASN, Sch name = ETH-TX_CLK

#Net "PhyTxEr" LOC = P2 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L34P_M3UDQS,

Sch name = ETH-TXD4

"PhyTxClk" LOC = L5 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

#Net "PhyRxd<3>" LOC = M3 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L36P_M3DQ8, Sch name = ETH-RXD3

#Net "PhyRxd<2>" LOC = N1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L35N_M3DQ11, Sch name = ETH-RXD2

#Net "PhyRxd<1>" LOC = N2 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L35P_M3DQ10, Sch name = ETH-RXD1

#Net "PhyRxd<0>" LOC = P1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L34N_M3UDQSN, Sch name = ETH-RXD0

#Net "PhyRxDv" LOC = L1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L37N_M3DQ1,

Sch name = ETH-RX_DV

#Net "PhyRxEr" LOC = M1 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L36N_M3DQ9,

Sch name = ETH-RXD4

#Net "PhyRxClk" LOC = H4 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name =

IO_L44P_GCLK21_M3A5, Sch name = ETH-RX_CLK

#Net "PhyMdc" LOC = M5 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L31N_VREF,

�

Sch name = ETH-MDC

#Net "PhyMdio" LOC = L6 | IOSTANDARD = LVCMOS33; #Bank = 3, pin name = IO_L31P, Sch name

= ETH-MDIO

## Pic USB-HID interface

#Net "PS2KeyboardData" LOC = J13| IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IO_L39P_M1A3, Sch name = PIC-SDI1

#Net "PS2KeyboardClk" LOC = L12 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IO_L40P_GCLK11_M1A5, Sch name = PIC-SCK1

#NET "PS2MouseData" LOC = K14 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IO_L39N_M1ODT, Sch name = PIC-SDO1

#NET "PS2MouseClk" LOC = L13| IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IO_L40N_GCLK10_M1A6, Sch name = PIC-SS1

#Net "PicGpio<0>" LOC = L16 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IO_L42N_GCLK6_TRDY1_M1LDM, Sch name = PIC-GPIO0

#NET "PicGpio<1>" LOC = H17 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

IO_L43P_GCLK5_M1DQ4, Sch name = PIC-GPIO1

## Usb-RS232 interface

#Net "RxD" LOC = N17 | IOSTANDARD=LVCMOS33; #Bank = 1, pin name = IO_L48P_HDC_M1DQ8,

Sch name = MCU-RX

#Net "TxD" LOC = N18 | IOSTANDARD=LVCMOS33; #Bank = 1, pin name = IO_L48N_M1DQ9, Sch

name = MCU-TX

## 7 segment display

#Net "seg<0>" LOC = T17 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L51P_M1DQ12,

Sch name = CA

#Net "seg<1>" LOC = T18 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L51N_M1DQ13,

Sch name = CB

#Net "seg<2>" LOC = U17 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L52P_M1DQ14,

Sch name = CC

#Net "seg<3>" LOC = U18 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L52N_M1DQ15,

Sch name = CD

#Net "seg<4>" LOC = M14 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L53P, Sch name

= CE

#Net "seg<5>" LOC = N14 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L53N_VREF, Sch

name = CF

#Net "seg<6>" LOC = L14 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L61P, Sch name

= CG

#Net "seg<7>" LOC = M13 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L61N, Sch

name = DP

�

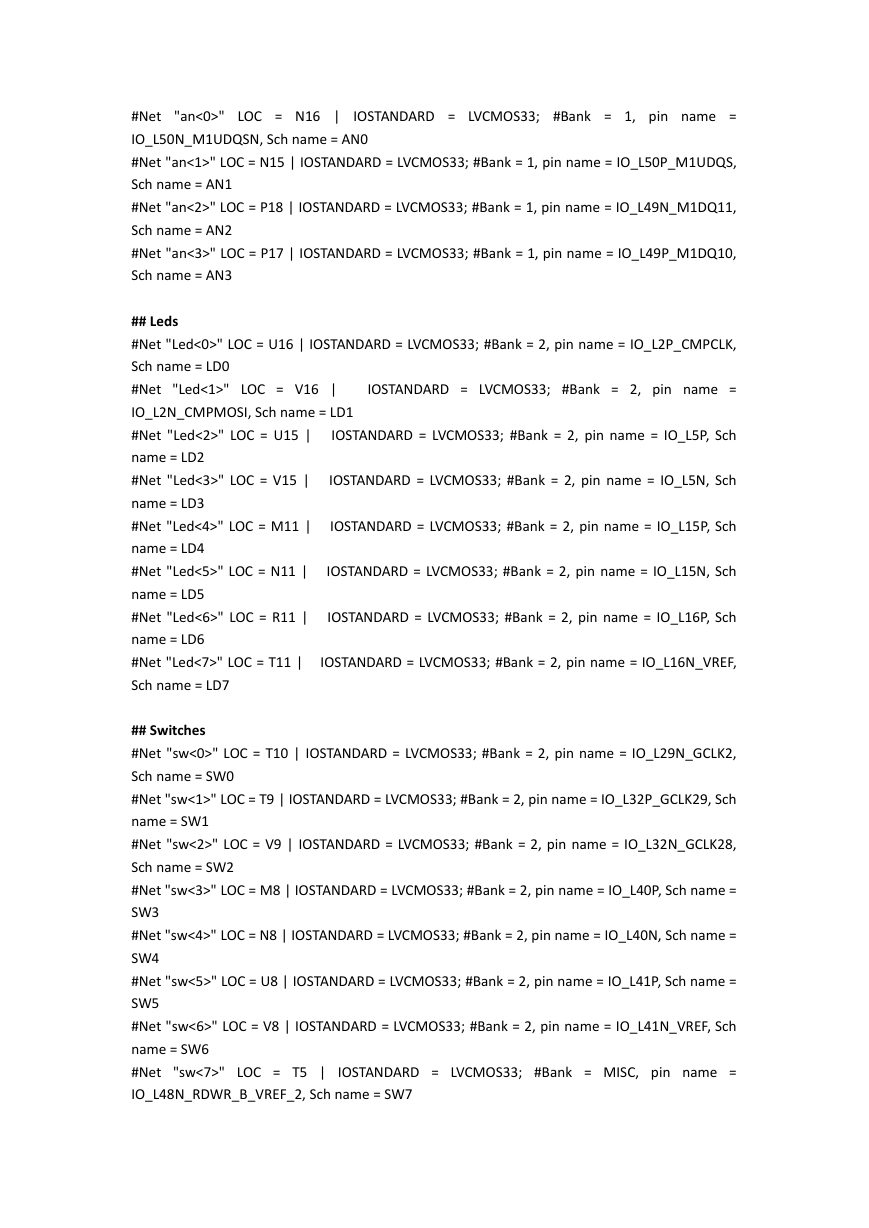

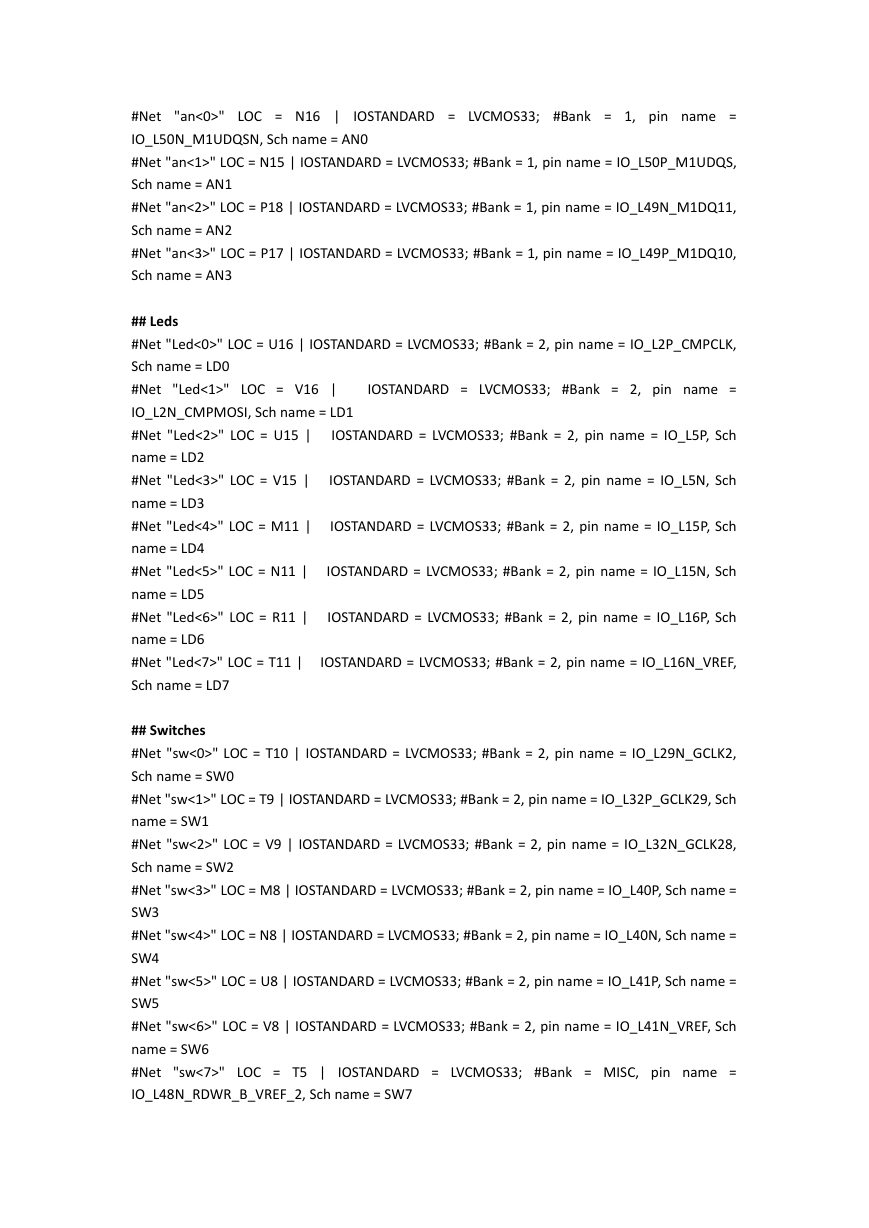

"an<0>"

LOC = N16 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name =

#Net

IO_L50N_M1UDQSN, Sch name = AN0

#Net "an<1>" LOC = N15 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L50P_M1UDQS,

Sch name = AN1

#Net "an<2>" LOC = P18 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L49N_M1DQ11,

Sch name = AN2

#Net "an<3>" LOC = P17 | IOSTANDARD = LVCMOS33; #Bank = 1, pin name = IO_L49P_M1DQ10,

Sch name = AN3

IOSTANDARD = LVCMOS33; #Bank = 2, pin name =

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L5P, Sch

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L5N, Sch

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L15P, Sch

## Leds

#Net "Led<0>" LOC = U16 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L2P_CMPCLK,

Sch name = LD0

#Net "Led<1>" LOC = V16 |

IO_L2N_CMPMOSI, Sch name = LD1

#Net "Led<2>" LOC = U15 |

name = LD2

#Net "Led<3>" LOC = V15 |

name = LD3

#Net "Led<4>" LOC = M11 |

name = LD4

#Net "Led<5>" LOC = N11 |

name = LD5

#Net "Led<6>" LOC = R11 |

name = LD6

#Net "Led<7>" LOC = T11 |

Sch name = LD7

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L16N_VREF,

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L15N, Sch

IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L16P, Sch

## Switches

#Net "sw<0>" LOC = T10 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L29N_GCLK2,

Sch name = SW0

#Net "sw<1>" LOC = T9 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L32P_GCLK29, Sch

name = SW1

#Net "sw<2>" LOC = V9 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L32N_GCLK28,

Sch name = SW2

#Net "sw<3>" LOC = M8 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L40P, Sch name =

SW3

#Net "sw<4>" LOC = N8 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L40N, Sch name =

SW4

#Net "sw<5>" LOC = U8 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L41P, Sch name =

SW5

#Net "sw<6>" LOC = V8 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L41N_VREF, Sch

name = SW6

#Net "sw<7>" LOC = T5 | IOSTANDARD = LVCMOS33; #Bank = MISC, pin name =

IO_L48N_RDWR_B_VREF_2, Sch name = SW7

�

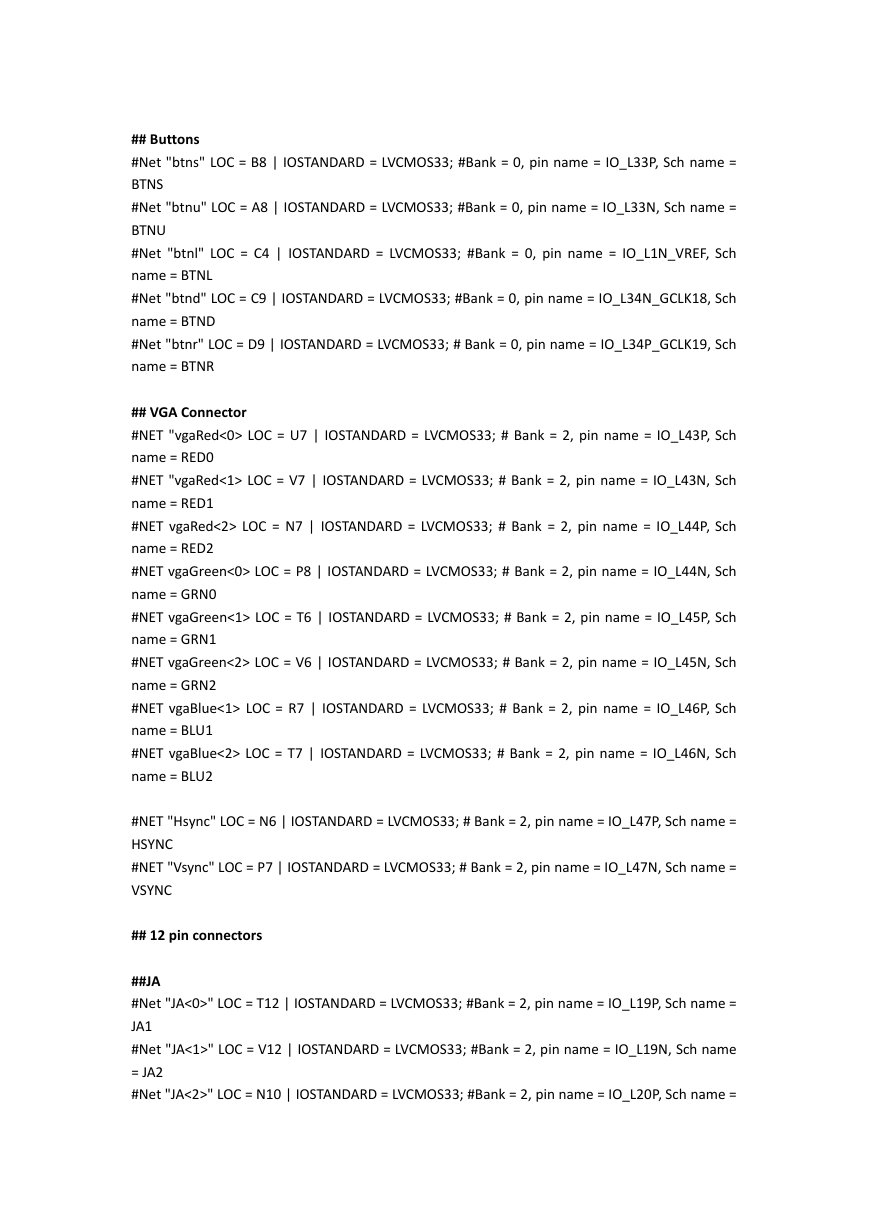

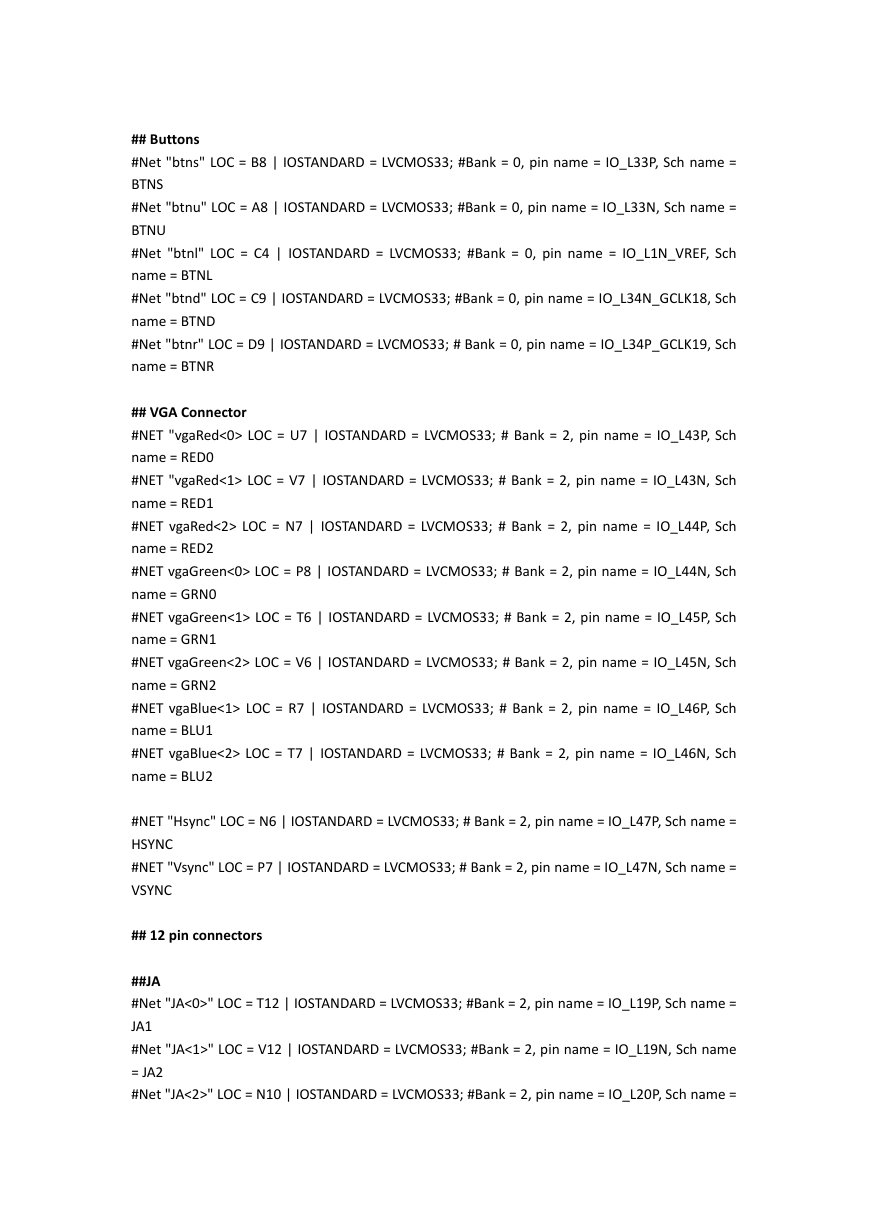

## Buttons

#Net "btns" LOC = B8 | IOSTANDARD = LVCMOS33; #Bank = 0, pin name = IO_L33P, Sch name =

BTNS

#Net "btnu" LOC = A8 | IOSTANDARD = LVCMOS33; #Bank = 0, pin name = IO_L33N, Sch name =

BTNU

#Net "btnl" LOC = C4 | IOSTANDARD = LVCMOS33; #Bank = 0, pin name = IO_L1N_VREF, Sch

name = BTNL

#Net "btnd" LOC = C9 | IOSTANDARD = LVCMOS33; #Bank = 0, pin name = IO_L34N_GCLK18, Sch

name = BTND

#Net "btnr" LOC = D9 | IOSTANDARD = LVCMOS33; # Bank = 0, pin name = IO_L34P_GCLK19, Sch

name = BTNR

## VGA Connector

#NET "vgaRed<0> LOC = U7 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L43P, Sch

name = RED0

#NET "vgaRed<1> LOC = V7 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L43N, Sch

name = RED1

#NET vgaRed<2> LOC = N7 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L44P, Sch

name = RED2

#NET vgaGreen<0> LOC = P8 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L44N, Sch

name = GRN0

#NET vgaGreen<1> LOC = T6 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L45P, Sch

name = GRN1

#NET vgaGreen<2> LOC = V6 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L45N, Sch

name = GRN2

#NET vgaBlue<1> LOC = R7 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L46P, Sch

name = BLU1

#NET vgaBlue<2> LOC = T7 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L46N, Sch

name = BLU2

#NET "Hsync" LOC = N6 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L47P, Sch name =

HSYNC

#NET "Vsync" LOC = P7 | IOSTANDARD = LVCMOS33; # Bank = 2, pin name = IO_L47N, Sch name =

VSYNC

## 12 pin connectors

##JA

#Net "JA<0>" LOC = T12 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L19P, Sch name =

JA1

#Net "JA<1>" LOC = V12 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L19N, Sch name

= JA2

#Net "JA<2>" LOC = N10 | IOSTANDARD = LVCMOS33; #Bank = 2, pin name = IO_L20P, Sch name =

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc