目 录

1.3

1.4

1.5

1.2

1.1

第 1 章 Libero 集成开发环境使用教程......................................................................2

SmartDesign 使用教程.............................................................................................2

1.1.1 概述...................................................................................................................2

1.1.2 简介...................................................................................................................2

1.1.3

SmartDesign 操作指南.....................................................................................5

1.1.4 小结.................................................................................................................12

1.1.5 测试程序.........................................................................................................12

ViewDraw 使用教程 ..............................................................................................16

1.2.1 概述.................................................................................................................16

ViewDraw 简介 ..............................................................................................16

1.2.2

1.2.3

ViewDraw 操作指南.......................................................................................17

1.2.4 小结.................................................................................................................22

Synplify 使用教程..................................................................................................23

1.3.1 概述.................................................................................................................23

1.3.2

Synplify 简介.................................................................................................25

1.3.3

Synplify 操作指南.........................................................................................31

1.3.4 小结.................................................................................................................43

WaveFormer 使用教程...........................................................................................44

1.4.1 概述.................................................................................................................44

WaveFormer 简介...........................................................................................44

1.4.2

1.4.3

WaveFormer 操作指南...................................................................................45

1.4.4 小结.................................................................................................................52

ModelSim 使用教程..............................................................................................53

1.5.1 概述.................................................................................................................53

1.5.2

ModelSim 简介..............................................................................................53

1.5.3

ModelSim 操作指南......................................................................................60

1.5.4 测试程序.........................................................................................................68

1.5.5 小结.................................................................................................................69

Designer 使用教程 ................................................................................................70

1.6.1 概述.................................................................................................................70

1.6.2

Designer 简介 .................................................................................................70

1.6.3

Designer 操作指南 .........................................................................................85

1.6.4 小结.................................................................................................................93

FlashPro 使用教程...............................................................................................xciv

1.7.1 概述..............................................................................................................xciv

FlashPro 简介...............................................................................................xciv

1.7.2

1.7.3

FlashPro 操作指南.......................................................................................xcvi

1.7.4 小结.................................................................................................................cii

附录 A 销售与服务网络..............................................................................................1

1.6

1.7

ZLG ACTEL�

第1章 Libero 集成开发环境使用教程

本文将深入介绍 Libero IDE 中集成的大部分软件的使用流程,包括 SmartDesign、

ViewDraw、ModelSim、Synplify、Designer 和 FlashPro 的使用。

上述软件都是高度集成在 LiberoIDE 环境中的。用户从 Libero 环境中进入某些软件

(ModelSim、Synplify、Designe 和 FlashPro)时,Libero 会自动为用户建立新工程并自动添

加相关文件。如打开 Synplify 时,Libero 会自动帮助用户建立新的工程并自动把工程中的文

件添加进来,一般情况下用户只需点击一下“RUN”按钮就可以开始综合了。为了让读者

更好地使用这些软件,以下的软件使用说明中都详细讲解了基于这些软件的独立工程建立的

过程。读者在平常的使用中,一般情况下都可以省去新建工程和添加文件到工程这两个步骤。

需要注意的是 Libero IDE 环境中使用的第三方软件都是定制版本,我们称之为 AE(Actel

Edition)。AE 版本的软件使用上有一些功能限制,如 ModelSim 不支持混合语言的仿真,

Synplfiy AE 也不支持包含混合语言工程的综合、不支持综合后的 RTL 视图查看等。用户平

常在使用中要注意这一点。

1.1 SmartDesign 使用教程

1.1.1 概述

SmartDesign 是 Actel 公司新推出的一款软件,只在 Libero 8.0 以上版本中集成。

SmartDesign 是用来创建和管理基于模块的文件,所谓模块的文件是指诸如 IP Core 等不需要

关注内部细节的文件块。SmartDesign 可以直接导入 IP cores、包括由 SmartGen 生成的 core、

由 CoreConsole 生成的 core。也可以导入由 HDL 文件生成的模块,在 SmartDesign 中可以互

连这些模块形成新的工程,利用 SmartDesign 用户可以很方便地编辑和管理这些块状文件。

本节将讲述 SmartDesign 的使用。

1.1.2 简介

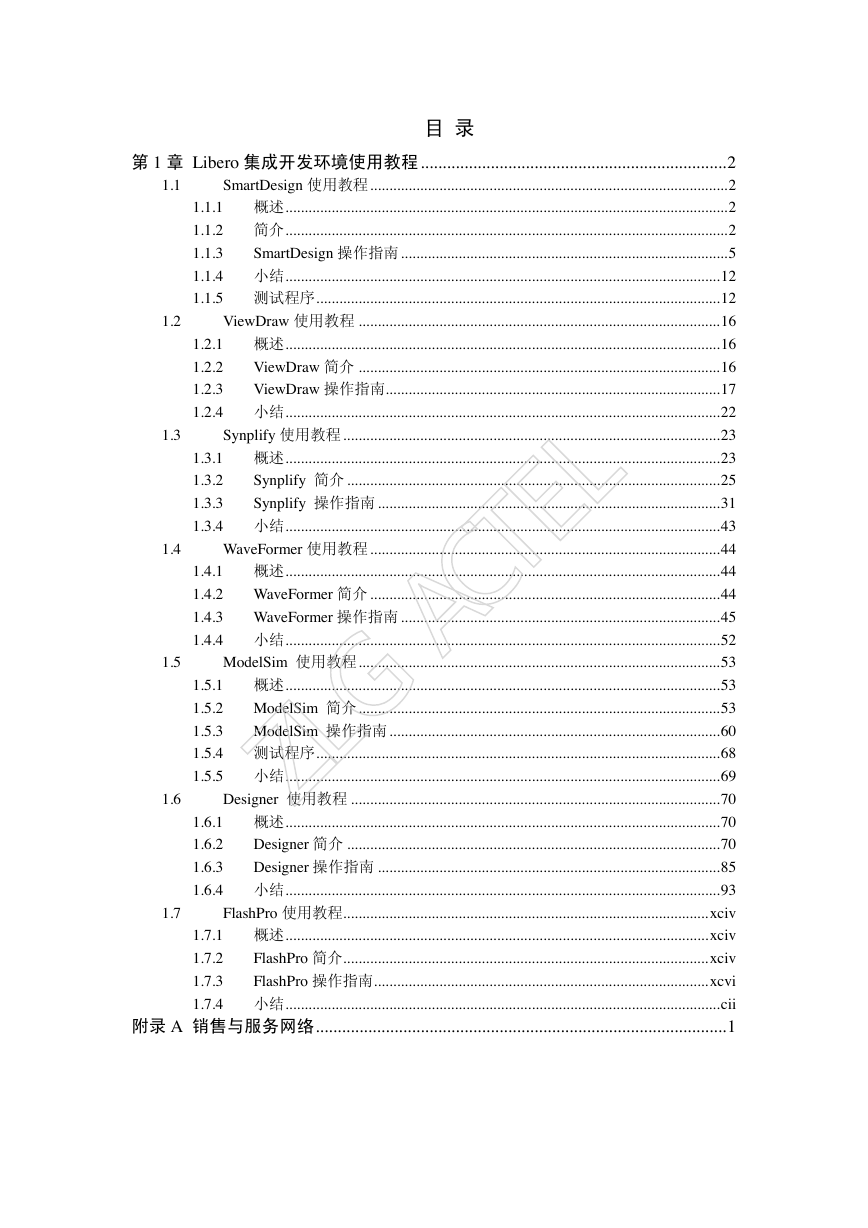

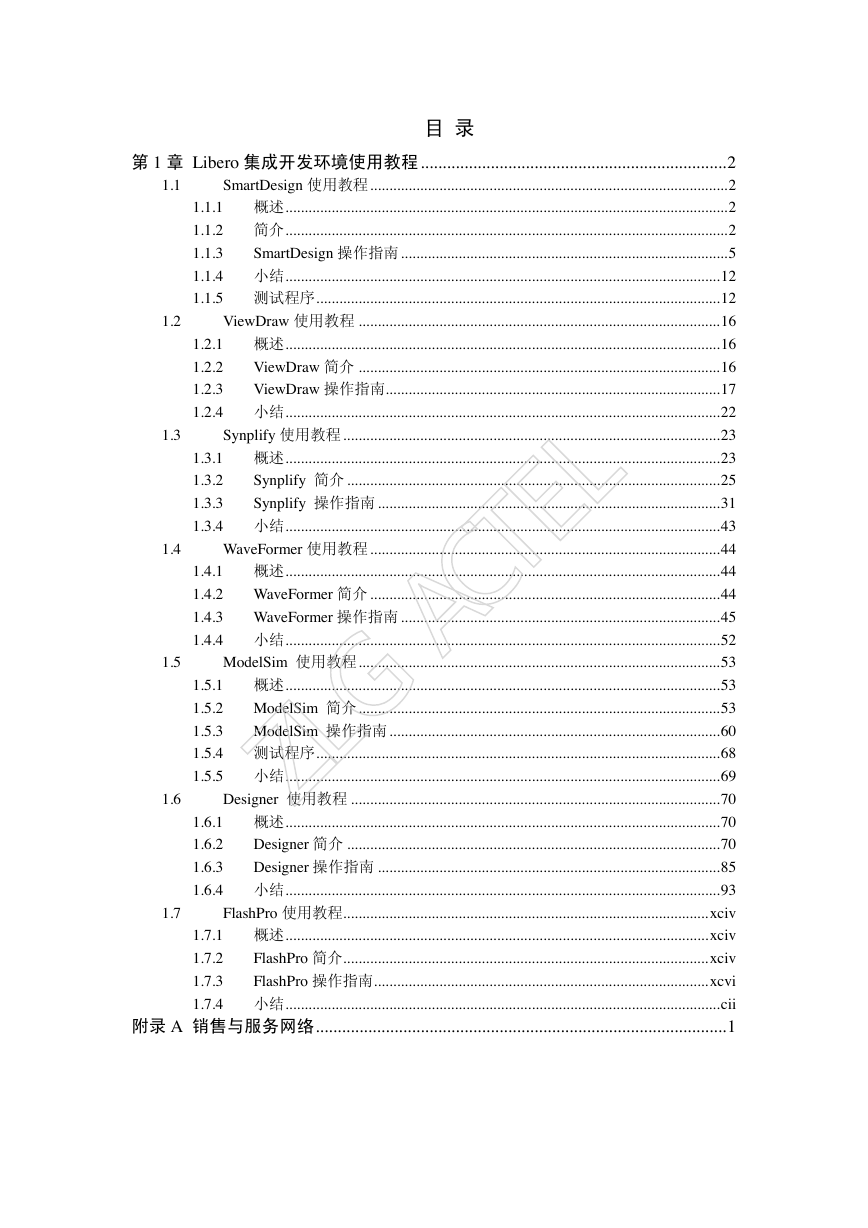

1. 进入 SmartDesign

点击流程图窗口中的 SmartDesign 图标进入,如图 1.1 所示。

图 1.1 进入 SmartDesign

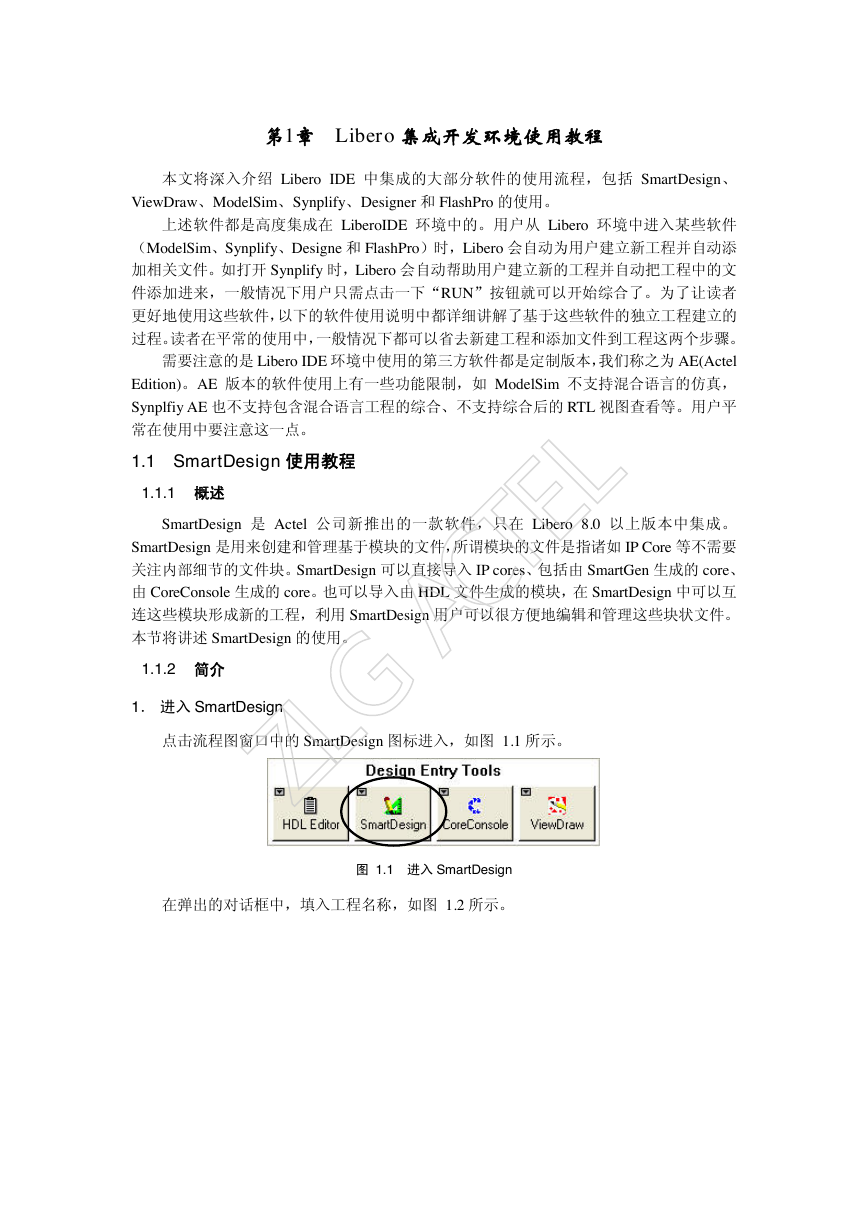

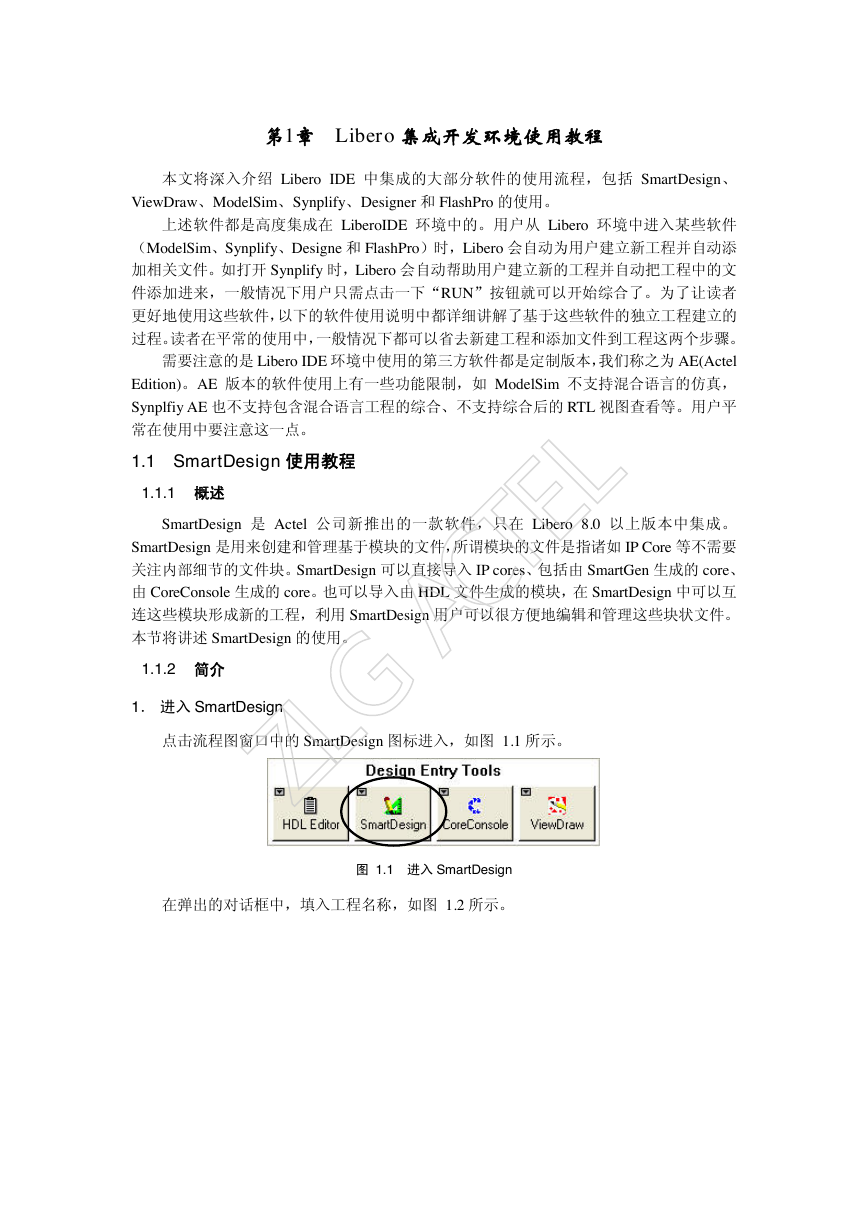

在弹出的对话框中,填入工程名称,如图 1.2 所示。

ZLG ACTEL�

2. SmartDesign 用户界面

图 1.2 新建工程

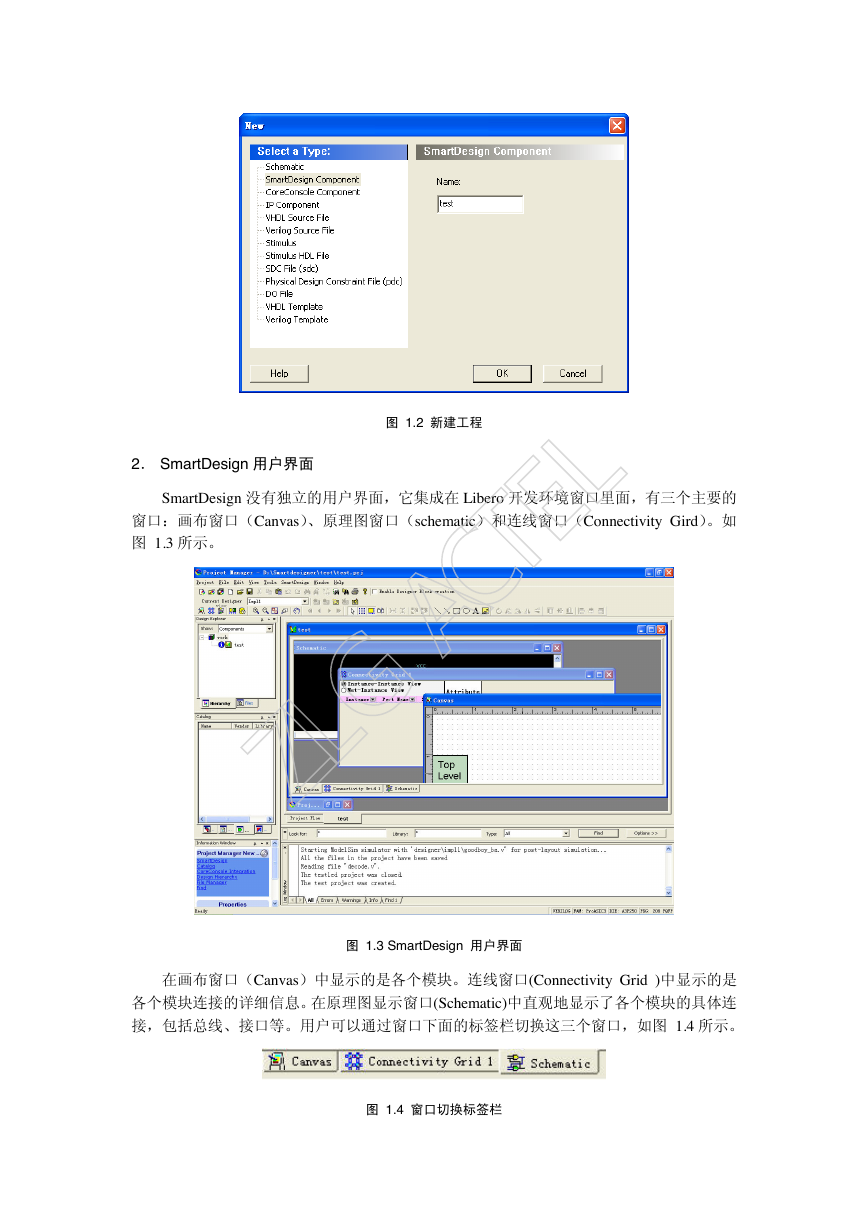

SmartDesign 没有独立的用户界面,它集成在 Libero 开发环境窗口里面,有三个主要的

窗口:画布窗口(Canvas)、原理图窗口(schematic)和连线窗口(Connectivity Gird)。如

图 1.3 所示。

图 1.3 SmartDesign 用户界面

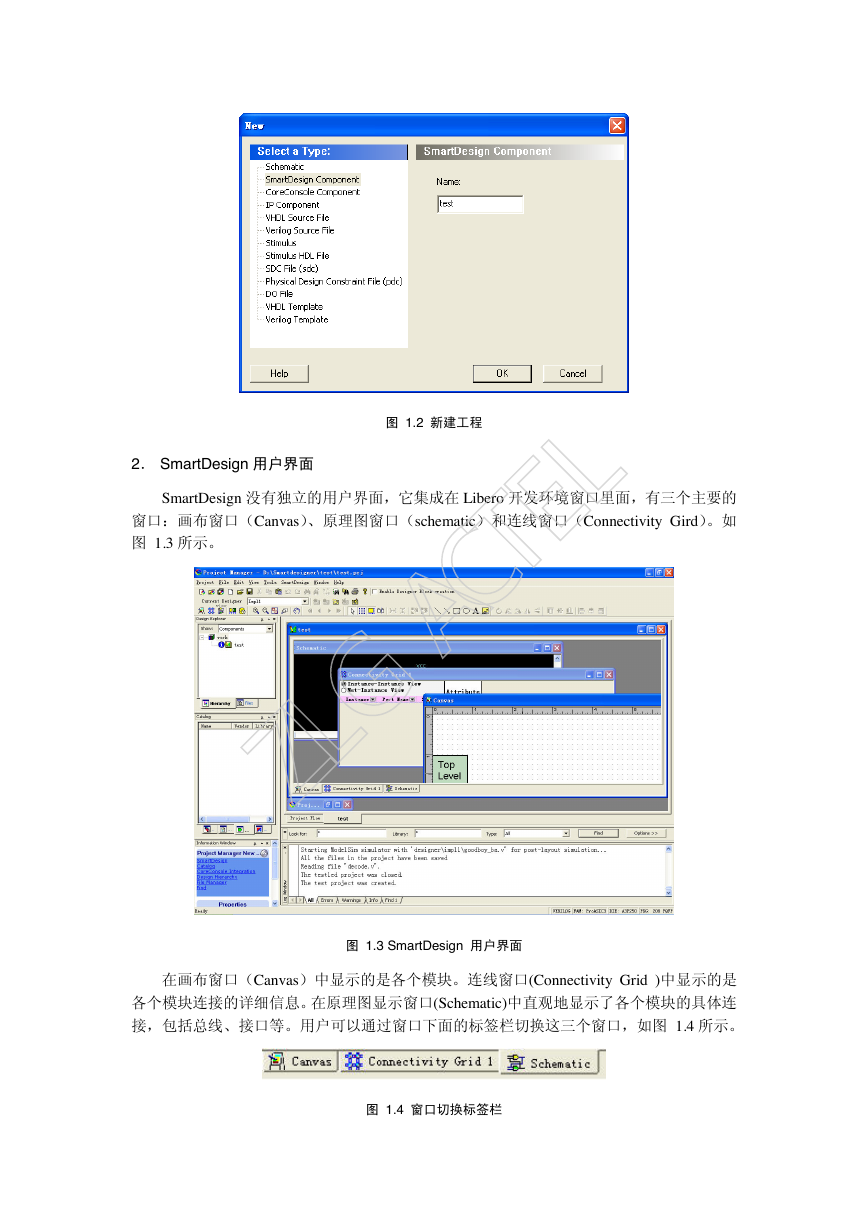

在画布窗口(Canvas)中显示的是各个模块。连线窗口(Connectivity Grid )中显示的是

各个模块连接的详细信息。在原理图显示窗口(Schematic)中直观地显示了各个模块的具体连

接,包括总线、接口等。用户可以通过窗口下面的标签栏切换这三个窗口,如图 1.4 所示。

图 1.4 窗口切换标签栏

ZLG ACTEL�

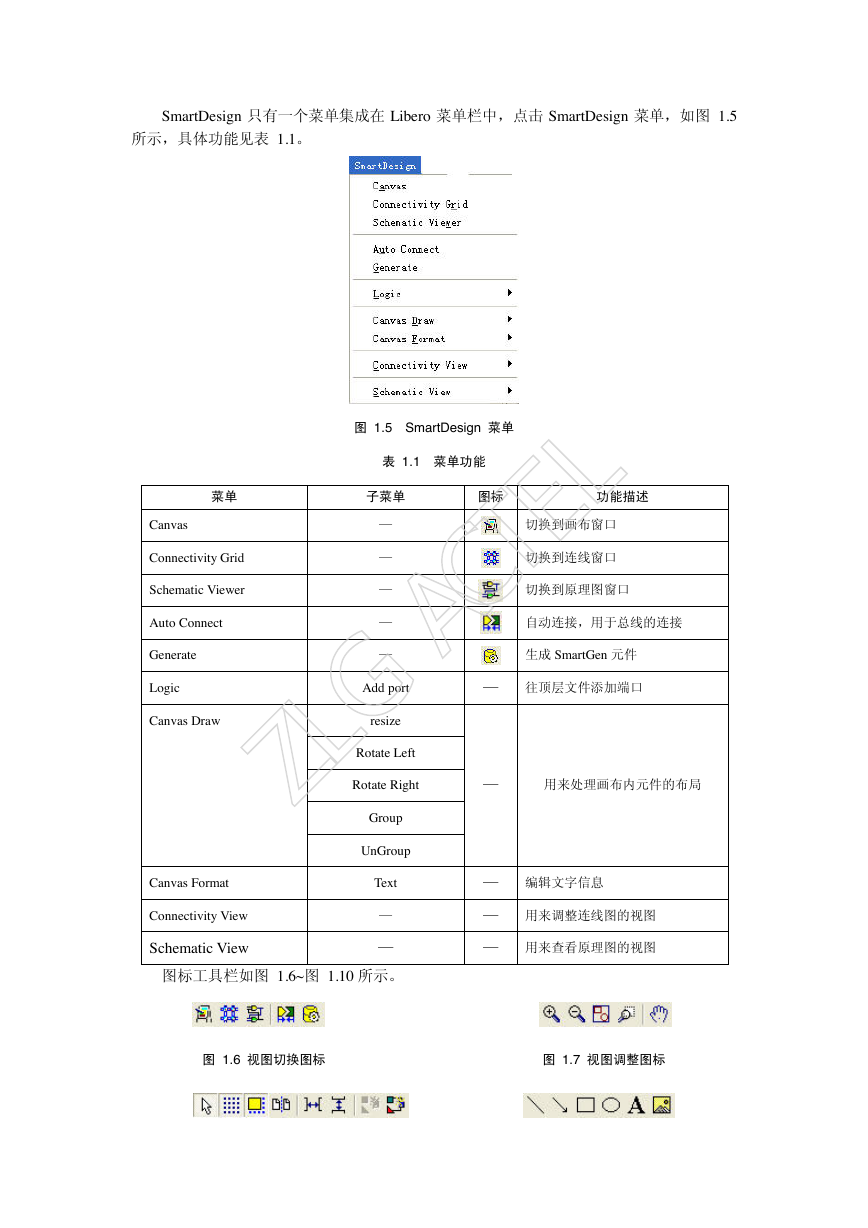

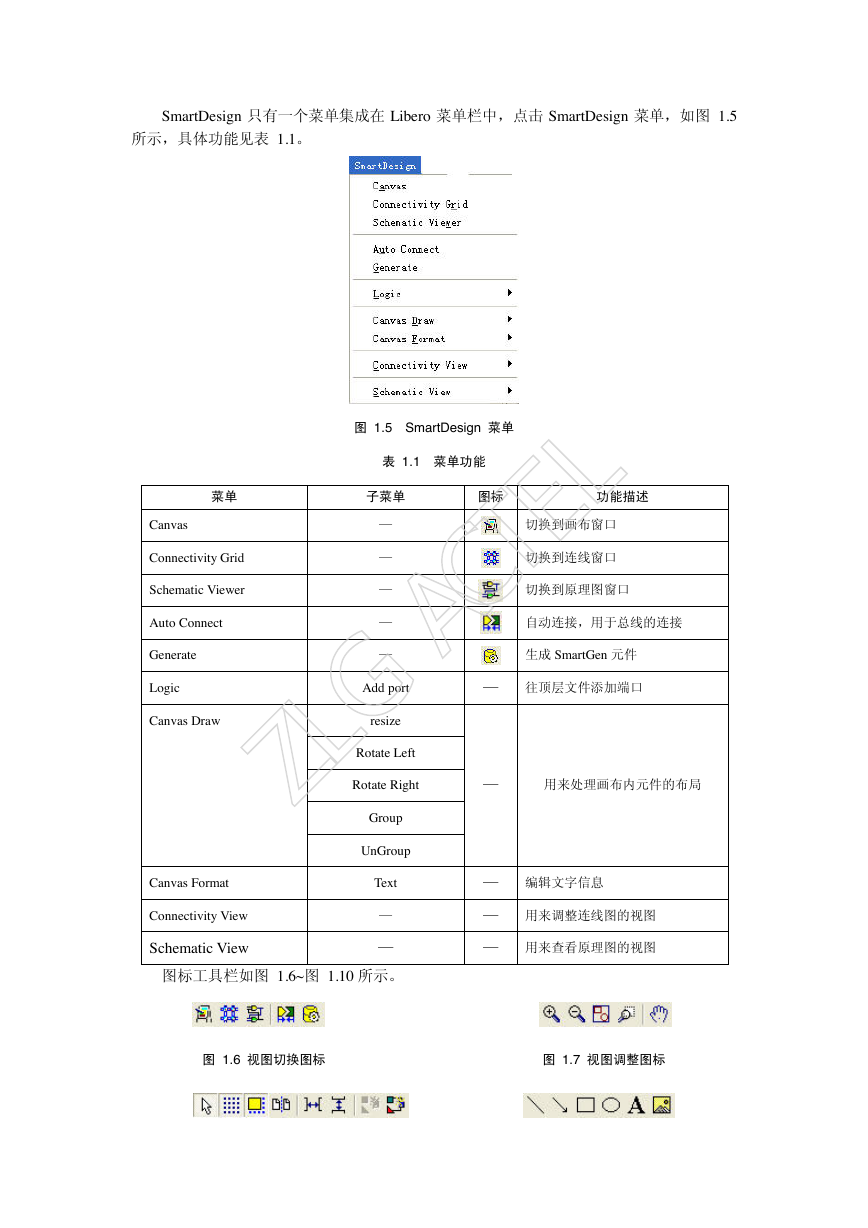

SmartDesign 只有一个菜单集成在 Libero 菜单栏中,点击 SmartDesign 菜单,如图 1.5

所示,具体功能见表 1.1。

图 1.5 SmartDesign 菜单

表 1.1 菜单功能

菜单

子菜单

图标

功能描述

Canvas

Connectivity Grid

Schematic Viewer

Auto Connect

Generate

Logic

Canvas Draw

Canvas Format

Connectivity View

Schematic View

—

—

—

—

—

Add port

resize

Rotate Left

Rotate Right

Group

UnGroup

Text

—

—

切换到画布窗口

切换到连线窗口

切换到原理图窗口

自动连接,用于总线的连接

生成 SmartGen 元件

— 往顶层文件添加端口

—

用来处理画布内元件的布局

— 编辑文字信息

— 用来调整连线图的视图

— 用来查看原理图的视图

图标工具栏如图 1.6~图 1.10 所示。

图 1.6 视图切换图标

图 1.7 视图调整图标

ZLG ACTEL�

图 1.8 画布窗口编辑图标

图 1.9 图形图标

图 1.10 原理图查看图标

图 1.11 图标对齐工具

1.1.3 SmartDesign 操作指南

1. 建立新工程

建立一个 SmartDesign 的工程一般包含以下几个步骤:

(1) 创建新工程。

(2) 加入元件块,用户可以把 HDL 文件、CoreConsole 生成的元件块、SmartGen 生成

的元件块以及其它的 IP core 等添加到 SmartDesign 的工程中。

(3) 互连各个模块,用户可以在连线窗口中互连这些模块。

(4) 生成 SmartDesign 文件。

下面以一个具体工程来介绍如何使用 SmartDesign,这个工程实现的功能是:由 HDL

文件模块负责计时,把计数值送给译码器,译码器译码后点亮开发板上的 LED,HDL 文件

模块还负责把当前八个 LED 状态通过 UART 回传到 PC 机。

工程用到了三个模块:一个 HDL 文件模块、一个 SmartGen 生成的 3-8 译码器、一个

CoreConsole 生成的 UART 模块。

2. 添加元件块

要添加文件块有两种途径:

(1) 从 Libero 窗口左边的文件管理窗口中,可以把文件块元件直接拖入 SmartDesign 的

画布(Canvas)窗口中。

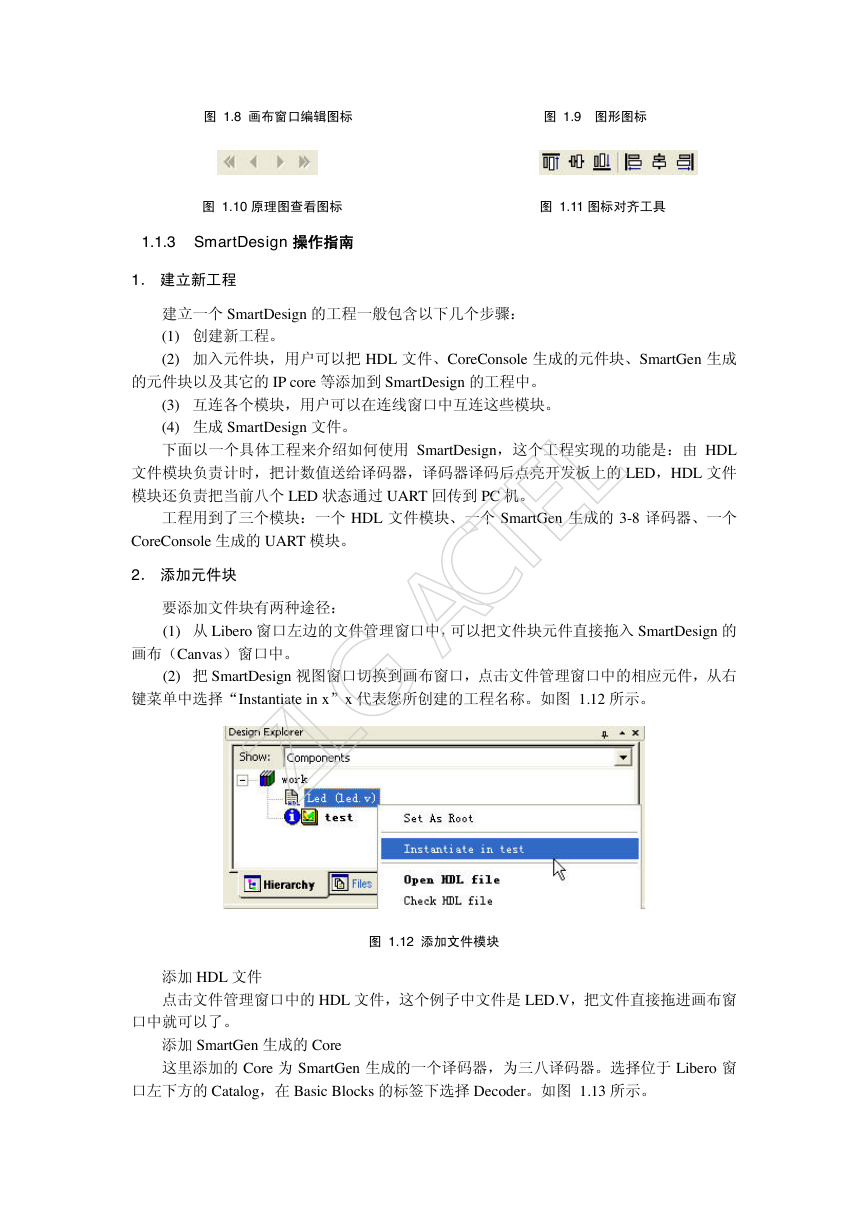

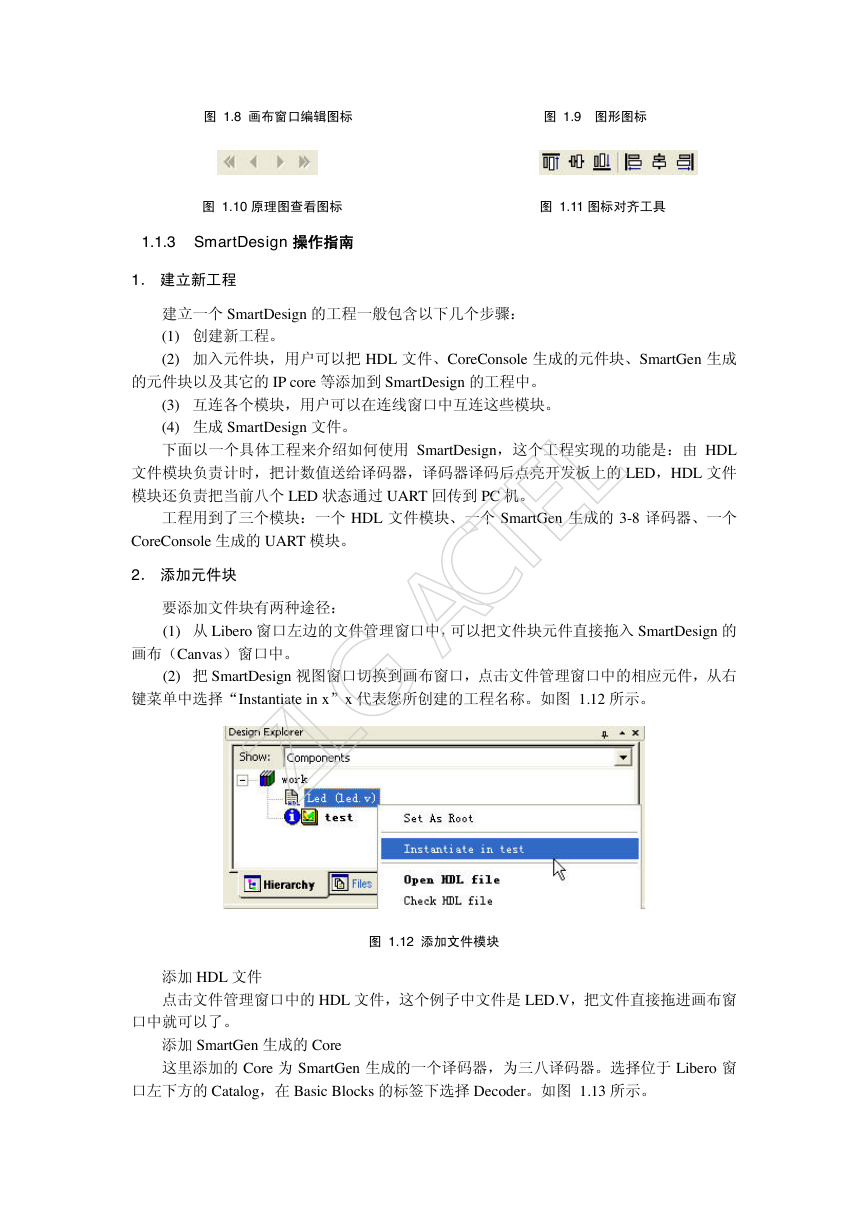

(2) 把 SmartDesign 视图窗口切换到画布窗口,点击文件管理窗口中的相应元件,从右

键菜单中选择“Instantiate in x”x 代表您所创建的工程名称。如图 1.12 所示。

图 1.12 添加文件模块

添加 HDL 文件

点击文件管理窗口中的 HDL 文件,这个例子中文件是 LED.V,把文件直接拖进画布窗

口中就可以了。

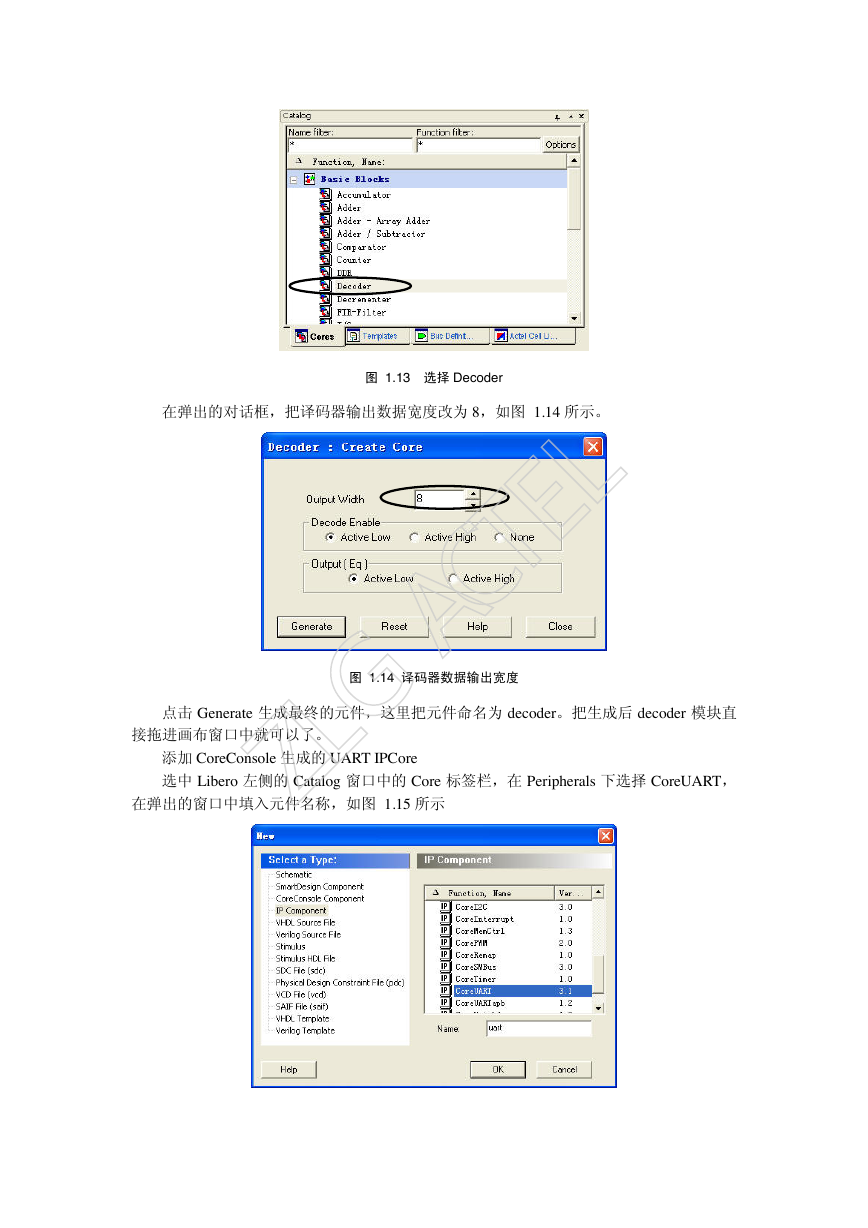

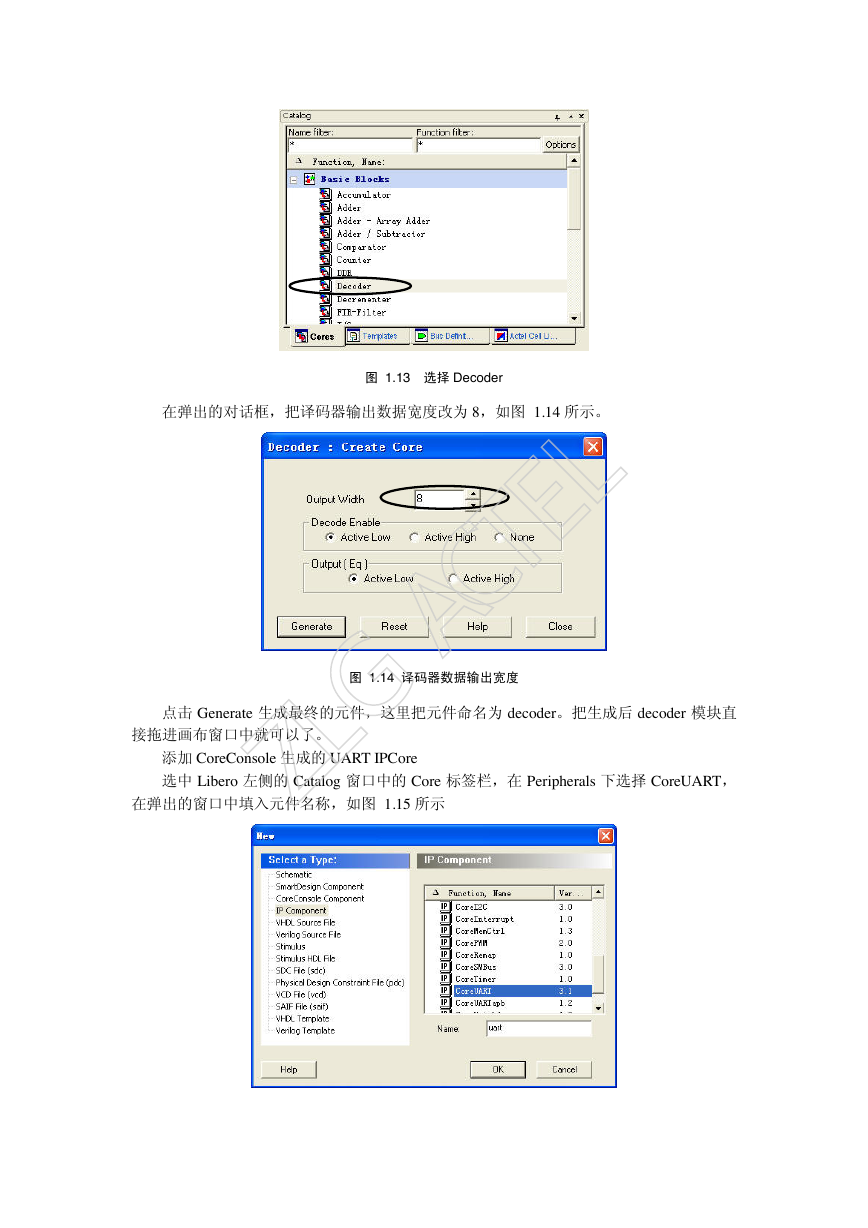

添加 SmartGen 生成的 Core

这里添加的 Core 为 SmartGen 生成的一个译码器,为三八译码器。选择位于 Libero 窗

口左下方的 Catalog,在 Basic Blocks 的标签下选择 Decoder。如图 1.13 所示。

ZLG ACTEL�

图 1.13 选择 Decoder

在弹出的对话框,把译码器输出数据宽度改为 8,如图 1.14 所示。

图 1.14 译码器数据输出宽度

点击 Generate 生成最终的元件,这里把元件命名为 decoder。把生成后 decoder 模块直

接拖进画布窗口中就可以了。

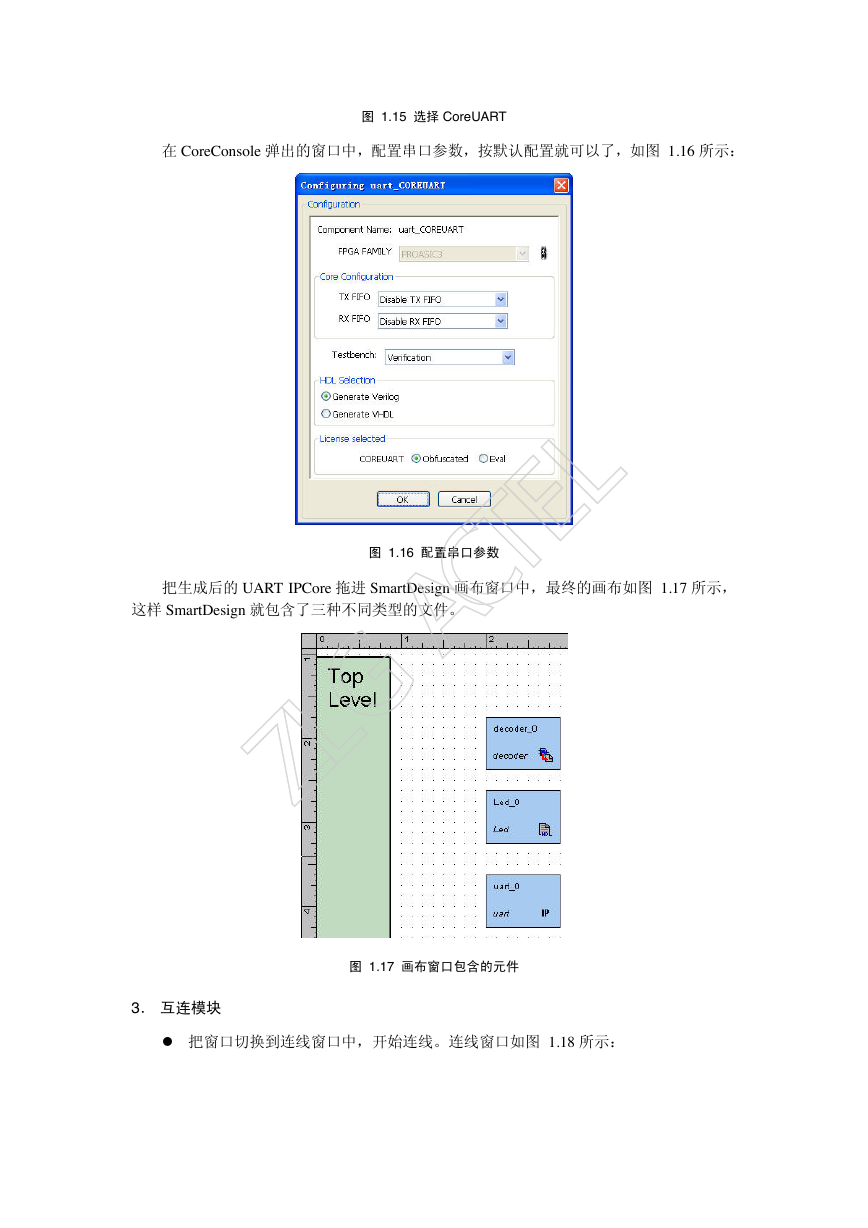

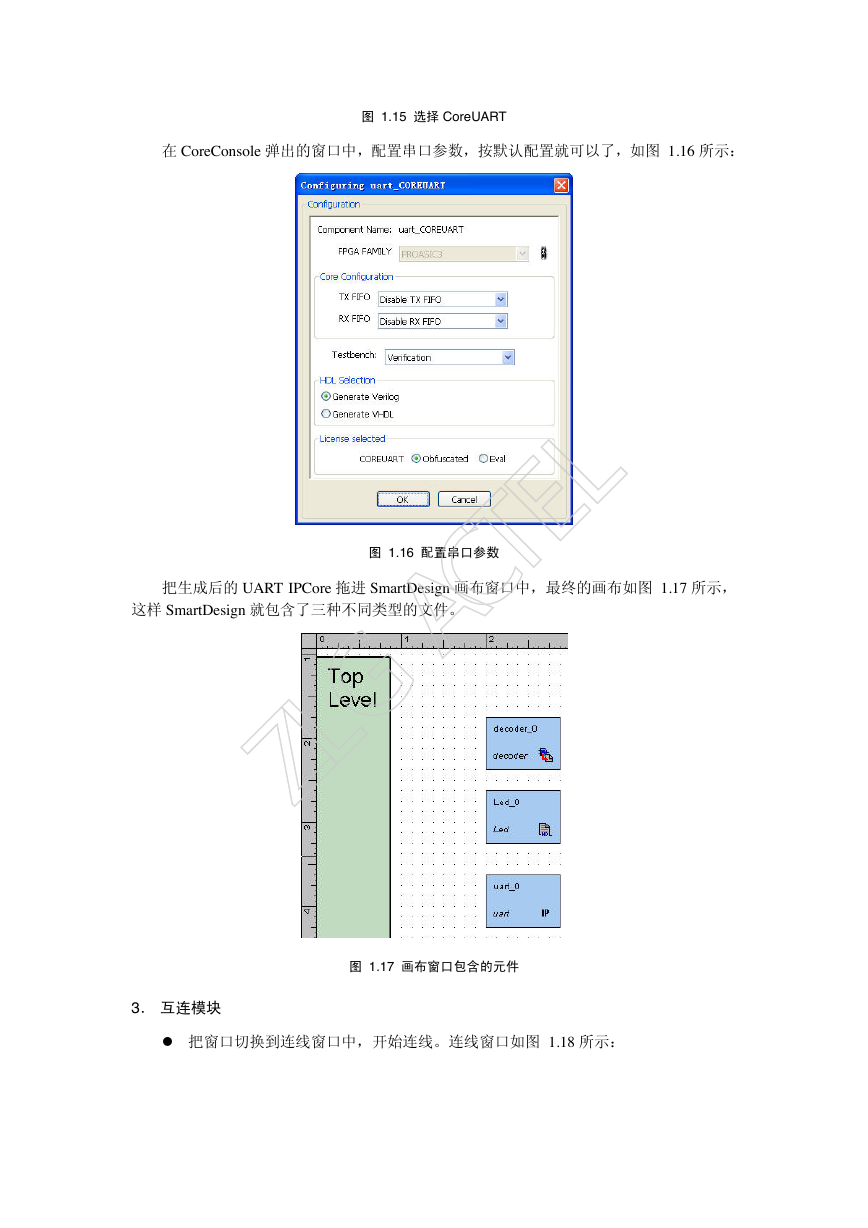

添加 CoreConsole 生成的 UART IPCore

选中 Libero 左侧的 Catalog 窗口中的 Core 标签栏,在 Peripherals 下选择 CoreUART,

在弹出的窗口中填入元件名称,如图 1.15 所示

ZLG ACTEL�

图 1.15 选择 CoreUART

在 CoreConsole 弹出的窗口中,配置串口参数,按默认配置就可以了,如图 1.16 所示:

图 1.16 配置串口参数

把生成后的 UART IPCore 拖进 SmartDesign 画布窗口中,最终的画布如图 1.17 所示,

这样 SmartDesign 就包含了三种不同类型的文件。

图 1.17 画布窗口包含的元件

3. 互连模块

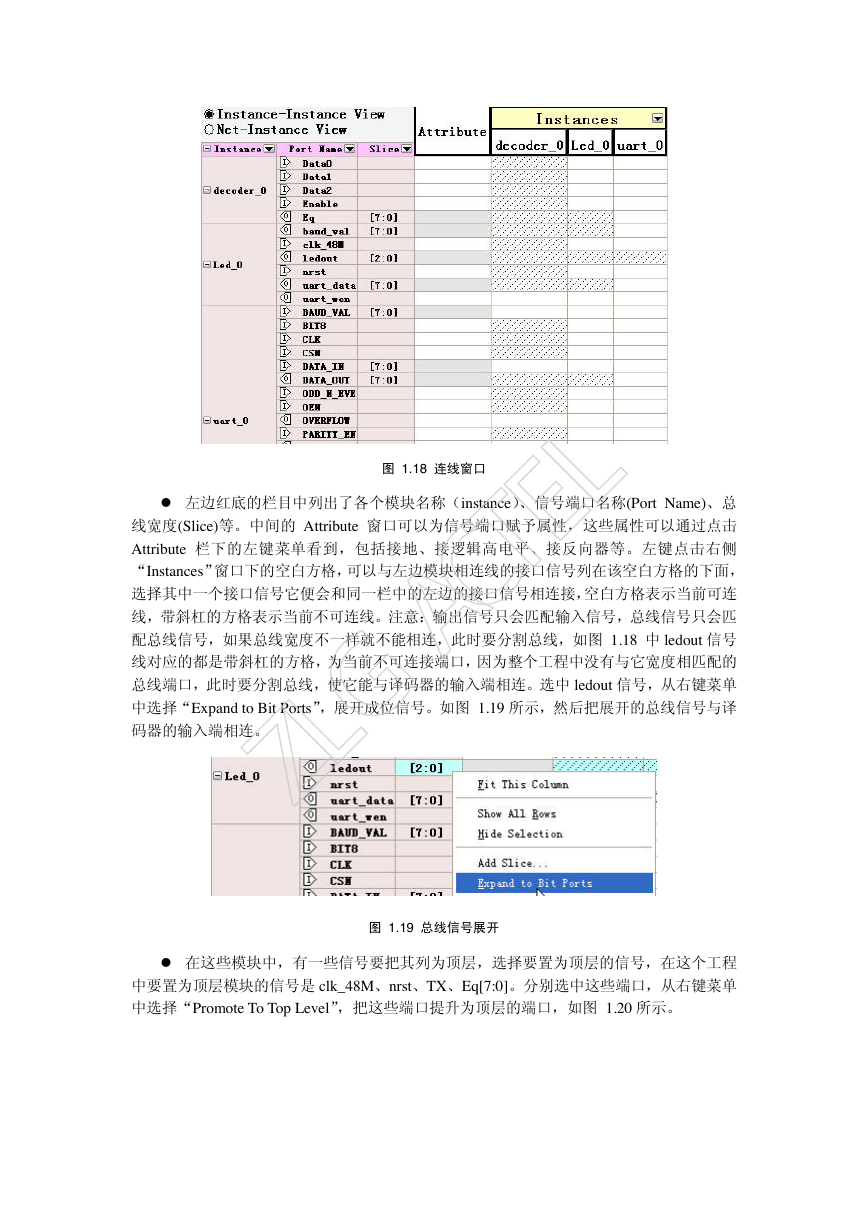

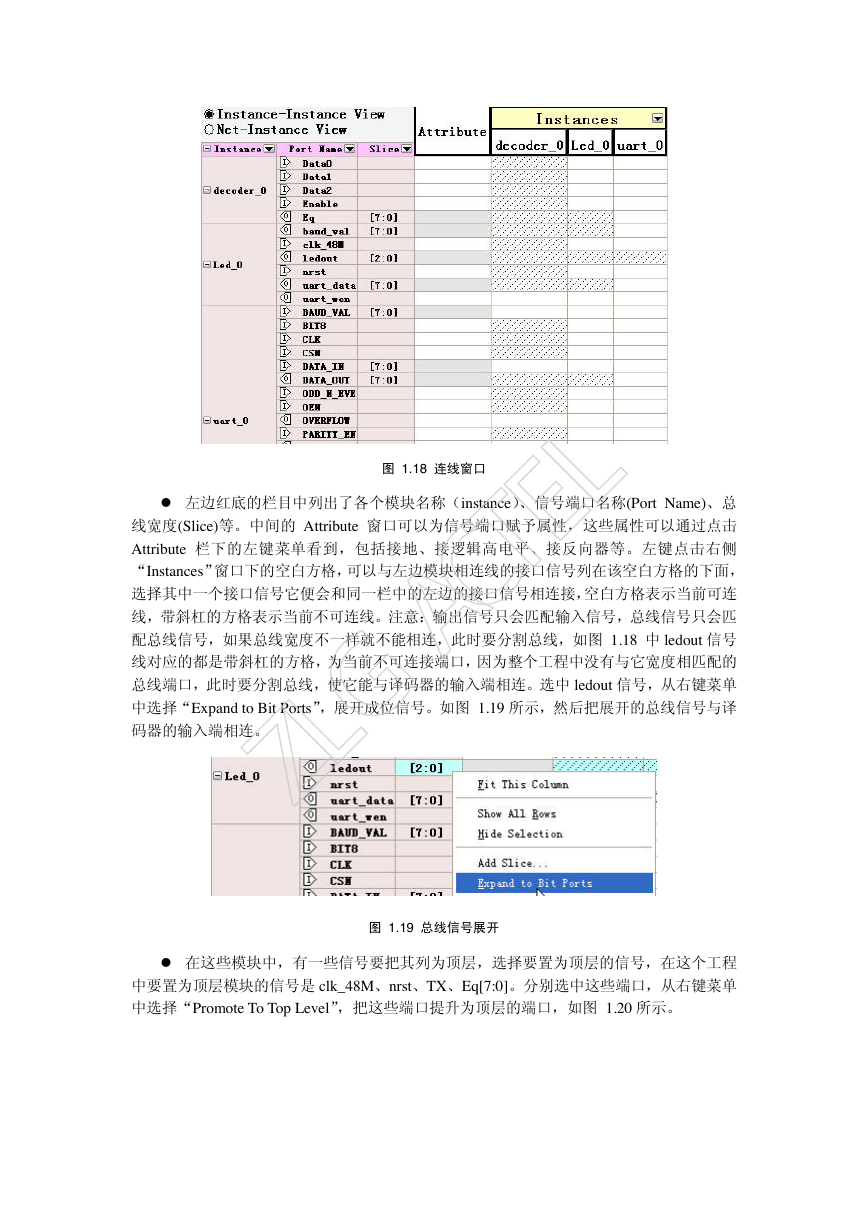

把窗口切换到连线窗口中,开始连线。连线窗口如图 1.18 所示:

ZLG ACTEL�

图 1.18 连线窗口

左边红底的栏目中列出了各个模块名称(instance)、信号端口名称(Port Name)、总

线宽度(Slice)等。中间的 Attribute 窗口可以为信号端口赋予属性,这些属性可以通过点击

Attribute 栏下的左键菜单看到,包括接地、接逻辑高电平、接反向器等。左键点击右侧

“Instances”窗口下的空白方格,可以与左边模块相连线的接口信号列在该空白方格的下面,

选择其中一个接口信号它便会和同一栏中的左边的接口信号相连接,空白方格表示当前可连

线,带斜杠的方格表示当前不可连线。注意:输出信号只会匹配输入信号,总线信号只会匹

配总线信号,如果总线宽度不一样就不能相连,此时要分割总线,如图 1.18 中 ledout 信号

线对应的都是带斜杠的方格,为当前不可连接端口,因为整个工程中没有与它宽度相匹配的

总线端口,此时要分割总线,使它能与译码器的输入端相连。选中 ledout 信号,从右键菜单

中选择“Expand to Bit Ports”,展开成位信号。如图 1.19 所示,然后把展开的总线信号与译

码器的输入端相连。

图 1.19 总线信号展开

在这些模块中,有一些信号要把其列为顶层,选择要置为顶层的信号,在这个工程

中要置为顶层模块的信号是 clk_48M、nrst、TX、Eq[7:0]。分别选中这些端口,从右键菜单

中选择“Promote To Top Level”,把这些端口提升为顶层的端口,如图 1.20 所示。

ZLG ACTEL�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc