AN-1100

应用笔记

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

无线发射机IQ平衡和边带抑制

作者:Yi Zhang

简介

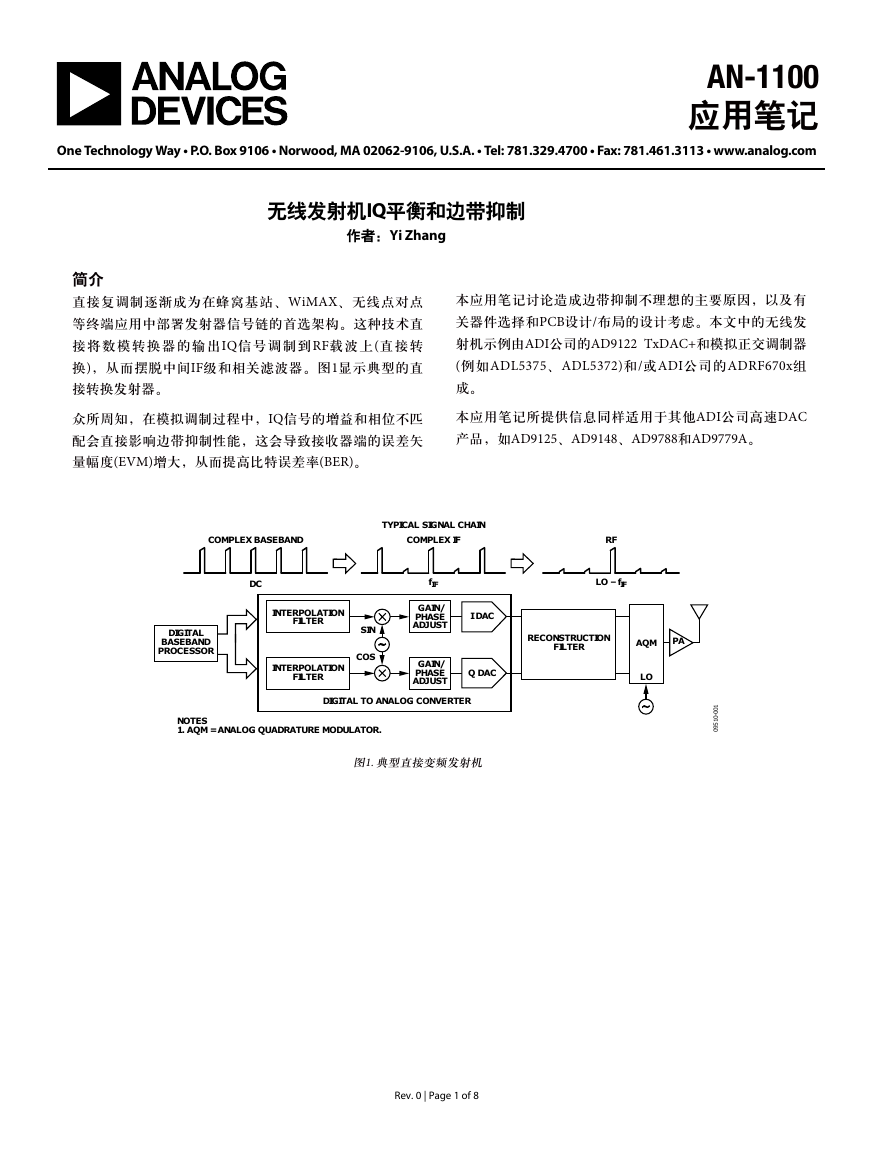

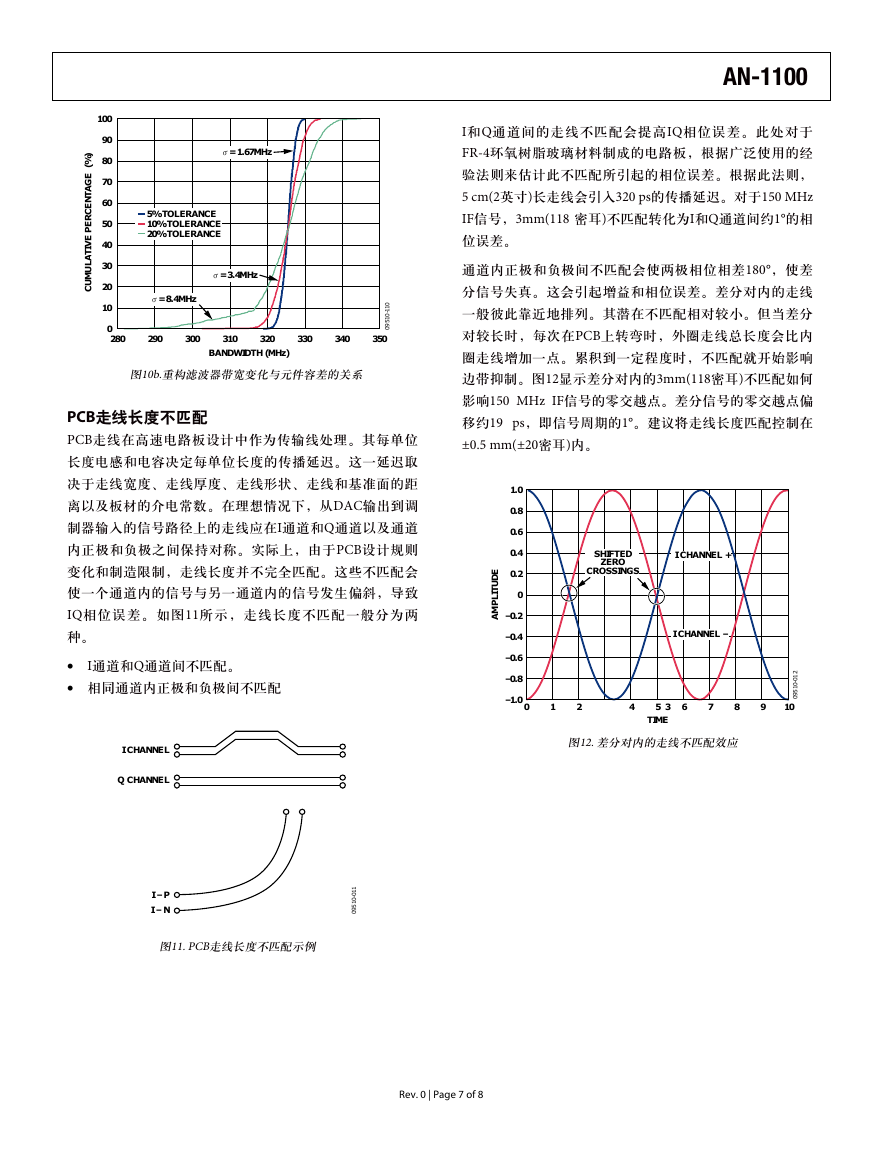

直接复调制逐渐成为在蜂窝基站、WiMAX、无线点对点

等终端应用中部署发射器信号链的首选架构。这种技术直

接将数模转换器的输出IQ信号调制到RF载波上( 直接转

换),从而摆脱中间IF级和相关滤波器。图1显示典型的直

接转换发射器。

众所周知,在模拟调制过程中,IQ信号的增益和相位不匹

配会直接影响边带抑制性能,这会导致接收器端的误差矢

量幅度(EVM)增大,从而提高比特误差率(BER)。

本应用笔记讨论造成边带抑制不理想的主要原因,以及有

关器件选择和PCB设计/布局的设计考虑。本文中的无线发

射机示例由ADI公司的AD9122 TxDAC+和模拟正交调制器

(例如ADL5375、 ADL5372)和/或ADI公司的ADRF670x组

成。

本应用笔记所提供信息同样适用于其他ADI公司高速DAC

产品,如AD9125、AD9148、AD9788和AD9779A。

COMPLEX BASEBAND

TYPICAL SIGNAL CHAIN

COMPLEX IF

DIGITAL

BASEBAND

PROCESSOR

DC

INTERPOLATION

FILTER

INTERPOLATION

FILTER

SIN

COS

fIF

GAIN/

PHASE

ADJUST

GAIN/

PHASE

ADJUST

I DAC

Q DAC

DIGITAL TO ANALOG CONVERTER

NOTES

1. AQM = ANALOG QUADRATURE MODULATOR.

RF

LO – fIF

RECONSTRUCTION

FILTER

AQM

PA

LO

1

0

0

-

0

1

5

9

0

图1. 典型直接变频发射机

Rev. 0 | Page 1 of 8

�

AN-1100

目录

简介.....................................................................................................1

修订历史0..........................................................................................2

边带抑制不理想的原因..................................................................3

结论.....................................................................................................8

修订历史

2010年12月—修订版0:初始版

Rev. 0 | Page 2 of 8

�

边带抑制不理想的原因

FILTER

GAIN/PHASE

MISMATCH

DAC OUTPUT

TERMINATION

MISMATCH

AD9122

DIGITAL

BASEBAND

PROCESSOR

INTERPOLATION

FILTER

I DAC

50Ω

50Ω

MODULATOR

BASEBAND

GAIN/PHASE

MISMATCH

ADL537x/

ADRF670x

LOI

100Ω

DAC 输出相位误差

DAC GAIN/PHASE

MISMATCH

PCB

TRACE

LENGTH

MISMATCH

RECONSTRUCTION FILTER

图1. 典型直接变频发射机

MODULATOR

INPUT

TERMINATION

MISMATCH

AN-1100

MODULATOR

LO GAIN/PHASE

MISMATCH

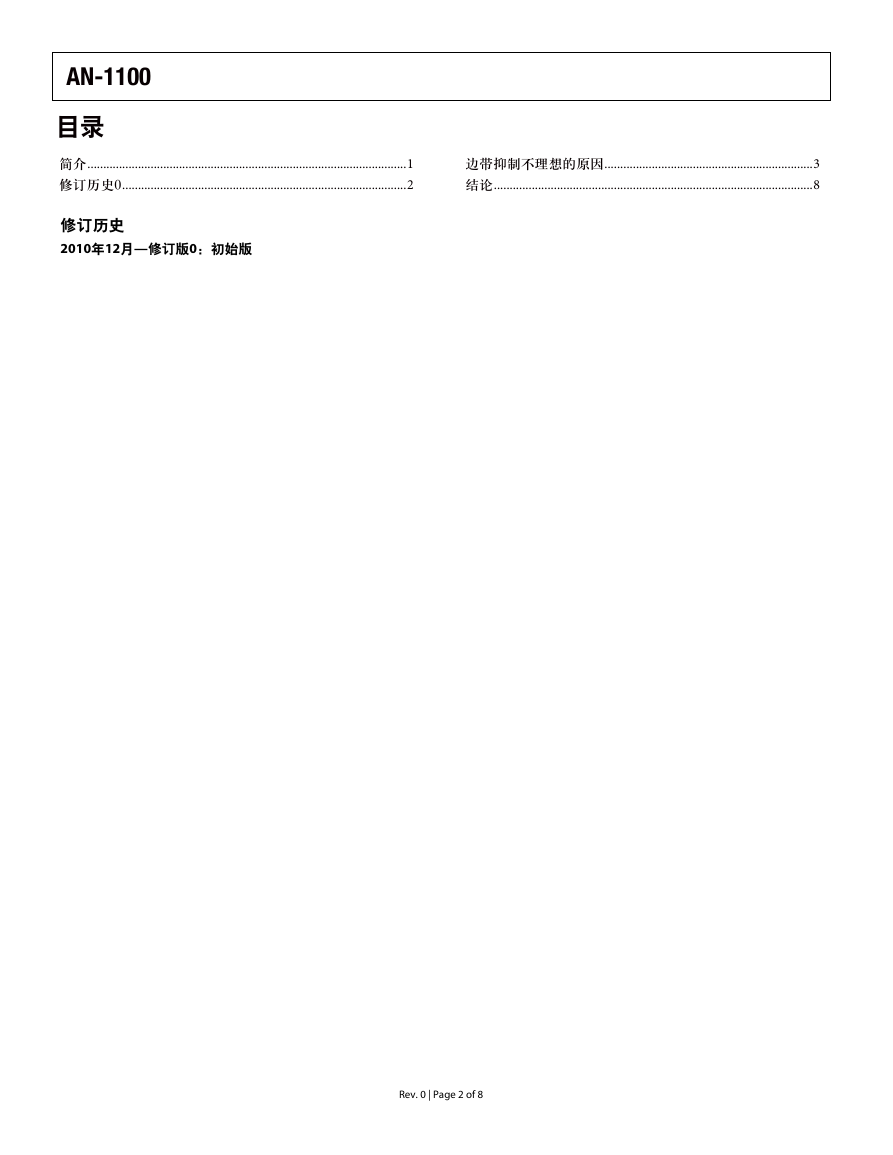

图2显示典型直接转换发射信号链的示意图。鉴于发射机

的对称性,图2仅显示I通道。

潜在不匹配在图中予以标注。本应用笔记假设数字域内的

IQ信号完全匹配。需要讨论的不匹配本质上仅存在于信号

链的模拟部分内。

表1列出了可能引起IQ不匹配的区域。下列章节阐述了这

些潜在不匹配及其潜在影响。

表1. 典型直接转换发射机中的IQ不匹配

不匹配贡献因素 增益不匹配

DAC

DAC输出增益误差

相位不匹配

DAC输出相位误差

IQ MOD

调制器基带增益误差

调制器LO增益误差

调制器基带相位误差

调制器LO相位误差

LOIP

LOIN

1.2V

5kΩ

QUADRATURE

PHASE

SPLITTER

I DAC

FULL SCALE ADJUST

CURRENT

SCALING

I DAC

Q DAC

Q DAC

FULL SCALE ADJUST

2

0

0

-

0

1

5

9

0

IOUT1P

IOUT1N

IOUT2N

IOUT2P

3

0

0

-

0

1

5

9

0

0.1µF

REFIO

FSADJ

10kΩ

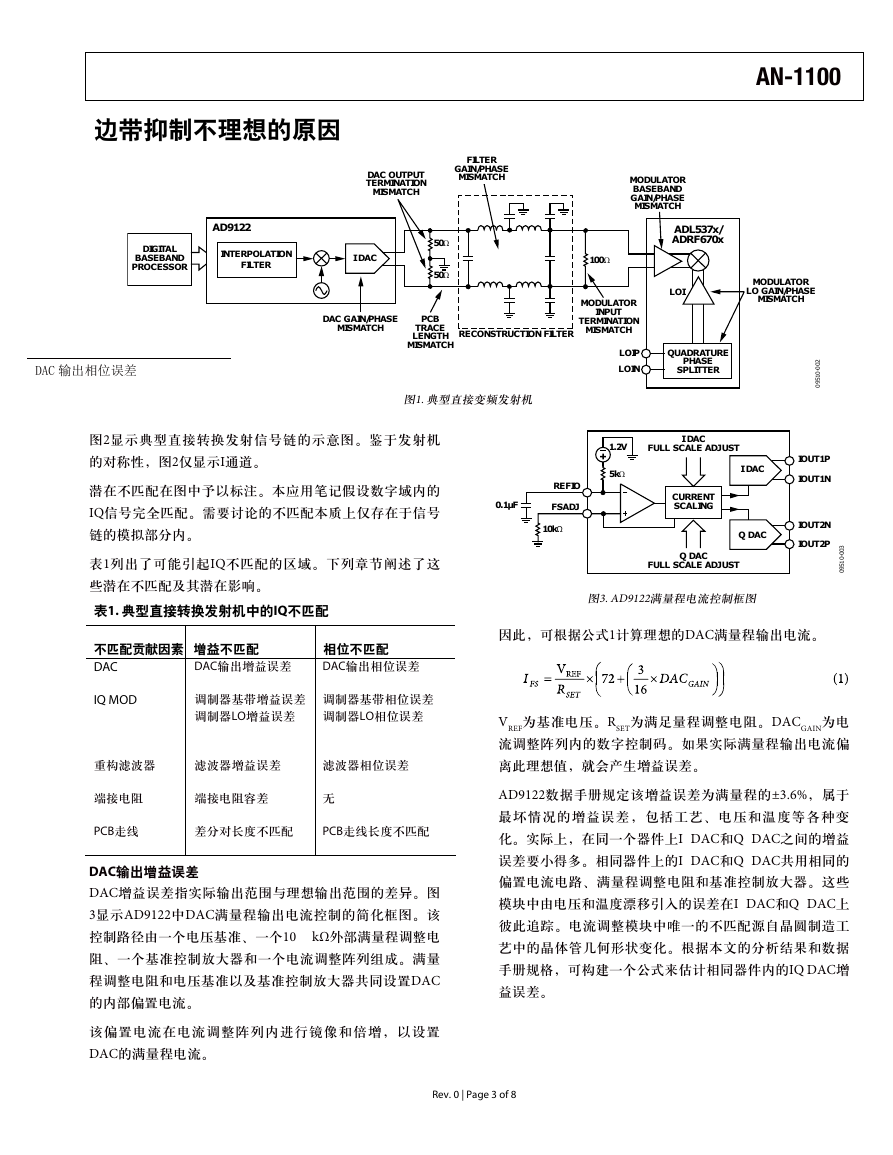

图3. AD9122满量程电流控制框图

因此,可根据公式1计算理想的DAC满量程输出电流。

VREF为基准电压。RSET为满足量程调整电阻。DACGAIN为电

流调整阵列内的数字控制码。如果实际满量程输出电流偏

重构滤波器

滤波器增益误差

滤波器相位误差

离此理想值,就会产生增益误差。

端接电阻

端接电阻容差

无

PCB走线

差分对长度不匹配

PCB走线长度不匹配

DAC输出增益误差

DAC增益误差指实际输出范围与理想输出范围的差异。图

3显示AD9122中DAC满量程输出电流控制的简化框图。该

控制路径由一个电压基准、一个10 k�外部满量程调整电

阻、一个基准控制放大器和一个电流调整阵列组成。满量

程调整电阻和电压基准以及基准控制放大器共同设置DAC

的内部偏置电流。

该偏置电流在电流调整阵列内进行镜像和倍增,以设置

DAC的满量程电流。

AD9122数据手册规定该增益误差为满量程的±3.6%,属于

最坏情况的增益误差,包括工艺、电压和温度等各种变

化。实际上,在同一个器件上I DAC和Q DAC之间的增益

误差要小得多。相同器件上的I DAC和Q DAC共用相同的

偏置电流电路、满量程调整电阻和基准控制放大器。这些

模块中由电压和温度漂移引入的误差在I DAC和Q DAC上

彼此追踪。电流调整模块中唯一的不匹配源自晶圆制造工

艺中的晶体管几何形状变化。根据本文的分析结果和数据

手册规格,可构建一个公式来估计相同器件内的IQ DAC增

益误差。

Rev. 0 | Page 3 of 8

�

AN-1100

如果指定

IMAIN为主DAC线性度所引起的输出电流误差。

IGAIN为增益DAC线性度所引起的输出电流误差。

则IQ DAC增益误差可表示为

代入AD9122数据手册中的数据得出

IQ DAC的实际增益误差可能因器件规格而异,但上述计算

结果表明,相同器件的IQ增益误差一般比DAC数据手册中

指定的增益误差小得多(在此情况下小一个数量级)。本应

用笔记在分析中使用上述计算结果。

DAC输出相位误差

DAC输出相位误差是将相同输入信号馈入到I

DAC和Q

DAC时两个DAC之间的偏差。该偏差来自内部时钟路径的

不匹配以及DAC内核的不匹配。同样,这些不匹配大部分

源于晶圆制造工艺。偏差因晶圆批次和器件而异。数据手

册通常不说明此规格。在AD9122上进行的测量表明,偏差

值一般在20 ps内。对于150 MHz的IF输出,压摆所引起的

IQ相位误差小于1°。

IQ调制器基带增益误差和相位误差

IQ调制器中的基带增益误差和相位误差由基带输入电路中

的不匹配造成,主要源自晶圆制造差异。参考ADL5372数

据手册,1.9 GHz下的增益误差一般为0.09 dB (1%),相同

LO频率下的相位误差为0.21°。

IQ调制器LO增益误差和相位误差

LO增益误差和相位误差指IQ调制器内同相和正交LO信号

间的不匹配。如图4所示,LO输入由正交分相器分成两个

正交信号LOI和LOQ。每个正交LO信号接着通过限幅放大

器,后者向混频器提供限幅驱动信号。

IBBP

IBBN

LOIP

LOIN

QBBN

QBBP

IQ MODULATOR

LOI

QUADRATURE

PHASE

SPLITTER

LOQ

图4. IQ调制器框图

RFOUT

DSOP

4

0

0

-

0

1

5

9

0

下列分析显示LO信号的增益和相位误差如何影响边带抑制

性能。

如果基带IQ信号(Ibb、Qbb))和LO

如下

IQ信号(ILO、QLO)表示

其中:

Gbb和φbb为基带信号中的幅度和相位不平衡。

GLO和φLO为LO信号中的幅度和相位不平衡。

IQ调制器输出端的RF信号可表示为

Rev. 0 | Page 4 of 8

�

应用三角恒等式,干扰边带信号为

此公式表明,LO信号内的增益和相位误差对边带抑制的影

响和基带信号内的增益和相位误差相同。假定基带信号是

理想的,且无用边带镜像功率完全源自于LO信号内的不平

衡,

则镜像功率水平可使用下列边带抑制公式来计算

边带抑制

因而,LO增益和相位误差是IQ调制器的关键优点。出色

的IQ调制器具有LO增益和相位误差低的优点,因此它们

不会影响系统边带抑制性能。但在系统设计中,必须重视

输入LO信号的质量以实现最佳边带抑制性能。即使IO调

制器设计良好,不需要的LO信号仍可能让LO相位误差崩

溃。LO信号的两大关键特性-谐波水平和占空比-对边带

抑制有重大影响。正交分相器拓扑决定IQ调制器所需的

LO信号。

有两种分相器设计在IQ调制器设计中广泛使用:多相分相

器和2XLO分相器。

多相分相器

多相分相器是一种RC-CR移相网络,产生从输入到一个输

出的低通传递函数以及从输入到其他输出的高通传递函

数,如图5所示。如果两个多相分支的R和C值匹配,则不

论输入频率多少,在理想情况下两个输出始终正交。

LO_IN

R

C

C

R

LOQ

5

0

0

-

0

1

5

9

0

LOI

图5. 第一阶多相电路

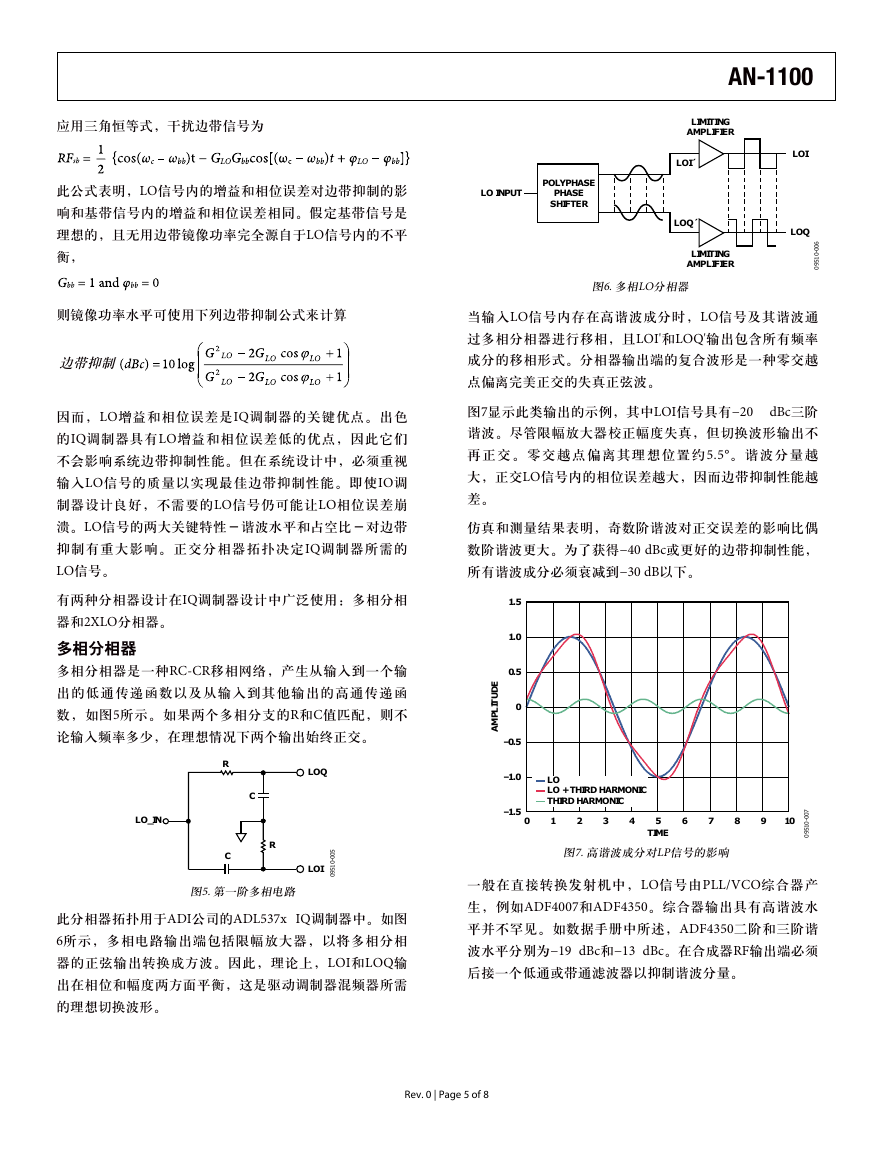

此分相器拓扑用于ADI公司的ADL537x IQ调制器中。如图

6所示,多相电路输出端包括限幅放大器,以将多相分相

器的正弦输出转换成方波。因此,理论上,LOI和LOQ输

出在相位和幅度两方面平衡,这是驱动调制器混频器所需

的理想切换波形。

AN-1100

LO INPUT

POLYPHASE

PHASE

SHIFTER

LIMITING

AMPLIFIER

LOI´

LOQ´

LIMITING

AMPLIFIER

图6. 多相LO分相器

LOI

LOQ

6

0

0

-

0

1

5

9

0

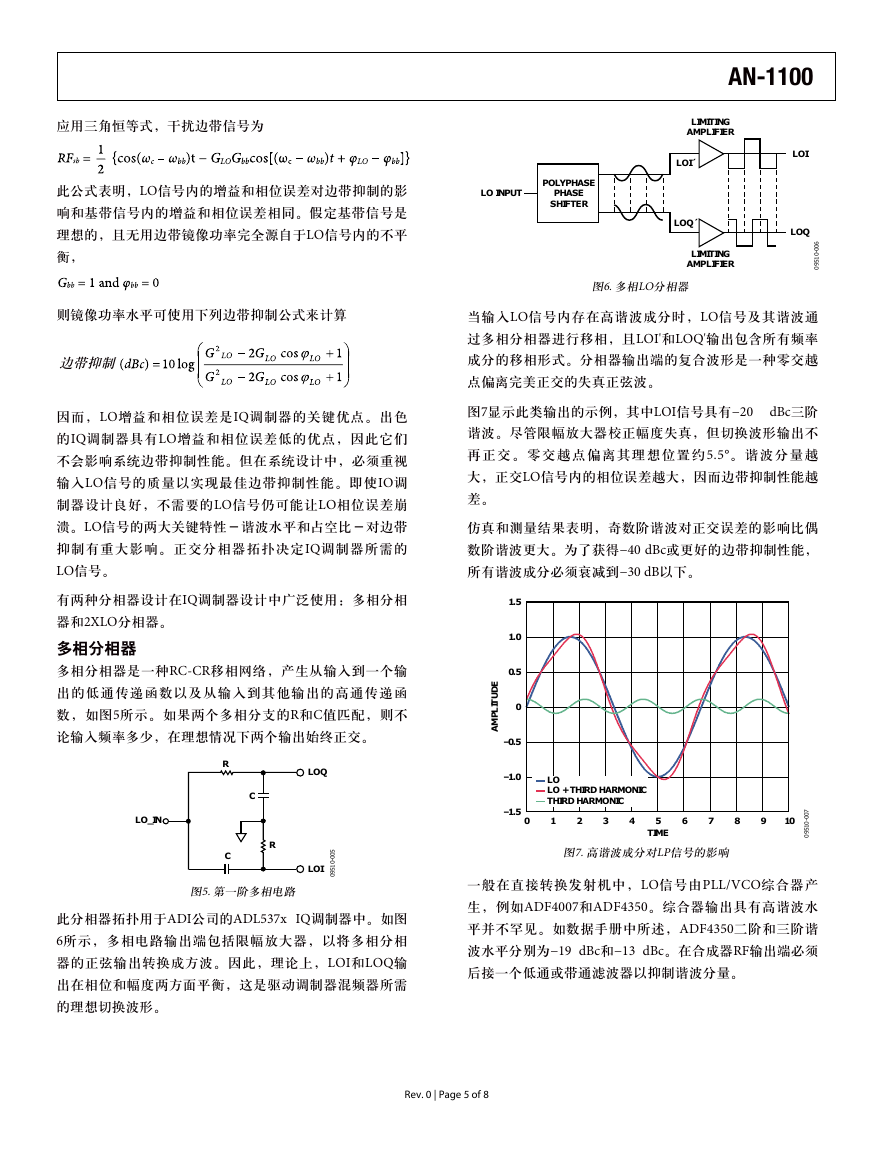

当输入LO信号内存在高谐波成分时,LO信号及其谐波通

过多相分相器进行移相,且LOI'和LOQ'输出包含所有频率

成分的移相形式。分相器输出端的复合波形是一种零交越

点偏离完美正交的失真正弦波。

图7显示此类输出的示例,其中LOI信号具有−20 dBc三阶

谐波。尽管限幅放大器校正幅度失真,但切换波形输出不

再正交。零交越点偏离其理想位置约5.5°。谐波分量越

大,正交LO信号内的相位误差越大,因而边带抑制性能越

差。

仿真和测量结果表明,奇数阶谐波对正交误差的影响比偶

数阶谐波更大。为了获得−40 dBc或更好的边带抑制性能,

所有谐波成分必须衰减到−30 dB以下。

I

E

D

U

T

L

P

M

A

1.5

1.0

0.5

0

–0.5

–1.0

–1.5

LO

LO + THIRD HARMONIC

THIRD HARMONIC

0

1

2

3

4

5

TIME

6

7

8

9

10

7

0

0

-

0

1

5

9

0

图7. 高谐波成分对LP信号的影响

一般在直接转换发射机中,LO信号由PLL/VCO综合器产

生,例如ADF4007和ADF4350。综合器输出具有高谐波水

平并不罕见。如数据手册中所述,ADF4350二阶和三阶谐

波水平分别为−19 dBc和−13 dBc。在合成器RF输出端必须

后接一个低通或带通滤波器以抑制谐波分量。

Rev. 0 | Page 5 of 8

�

AN-1100

有关低通/带通滤波器如何充分抑制LO谐波水平的详情,

请参考CN-0134电路笔记。

2XLO分相器

使用2XLO分相器是另一种产生LO正交信号的途径。图8为

分相器拓扑的框图。与多相分相器不同的是,使用D触发

器和逆变器来产生精确正交的是数字电路。由于其数字性

质,可在较大频率范围内实现出色的正交。

该电路需要以所需LO两倍频率工作的输入LO。另外要求

此输入的占空比为50%。任何占空比非50%的输入均逐度

转化为LO相位误差,因而降低边带抑制性能。

LO

LO

LOI

LOQ

D

LOI

Q

CK

Q

D

Q

LOQ

CK

Q

8

0

0

-

0

1

5

9

0

TIME

图8. 2XLO分相器

PLL/VCO合成器旨在产生50%占空比的RF信号。但是没有

完美的设计。预计占空比会有一定量的变化。应选择在整

个温度和电源电压范围内具有最小占空比变化的元件。LO

走线布局是可能导致占空比失真的另一个根源。差分对内

正负走线的不匹配会改变差分信号的占空比。具体说明见

PCB走线长度不匹配章节。

重构滤波器增益误差和相位误差

重构滤波器旨在抑制采样镜像以及来自DAC的其他高频成

分。其设计一般允许信号在通过滤波器时充分降低幅度失

真和群延迟变化,同时对目标频率成分提供足够的抑制。

通带增益和组延迟是滤波器拓扑和元件值的函数。

元件容差和寄生电容是滤波器增益和相位误差的决定因

素。图9为AD9122评估板(AD9122-M5375-EBZ)上的低

通滤波器设计示意图。滤波器输入端有两个50 � DAC端接

电阻,输出端有一个100 � IQ调制器输入端接电阻。该滤

波器是5阶巴特沃兹滤波器,输入输出均匹配至100 �。

AD9122

IOUT1P

IOUT1N

R1

50Ω

R2

50Ω

33nH

2pF

33nH

20pF

56nH

3.3pF

6pF

R3

100Ω

56nH

20pF

3.3pF

ADL5375

IBBP

IBBN

9

0

0

-

0

1

5

9

0

图 9. AD9122 DAC输出重构滤波器示意图

显然,R1、R2和R3的容差需要尽可能严格,否则这些电阻

的不匹配会直接影响IQ信号的幅度匹配。建议这些电阻的

容差<1%。

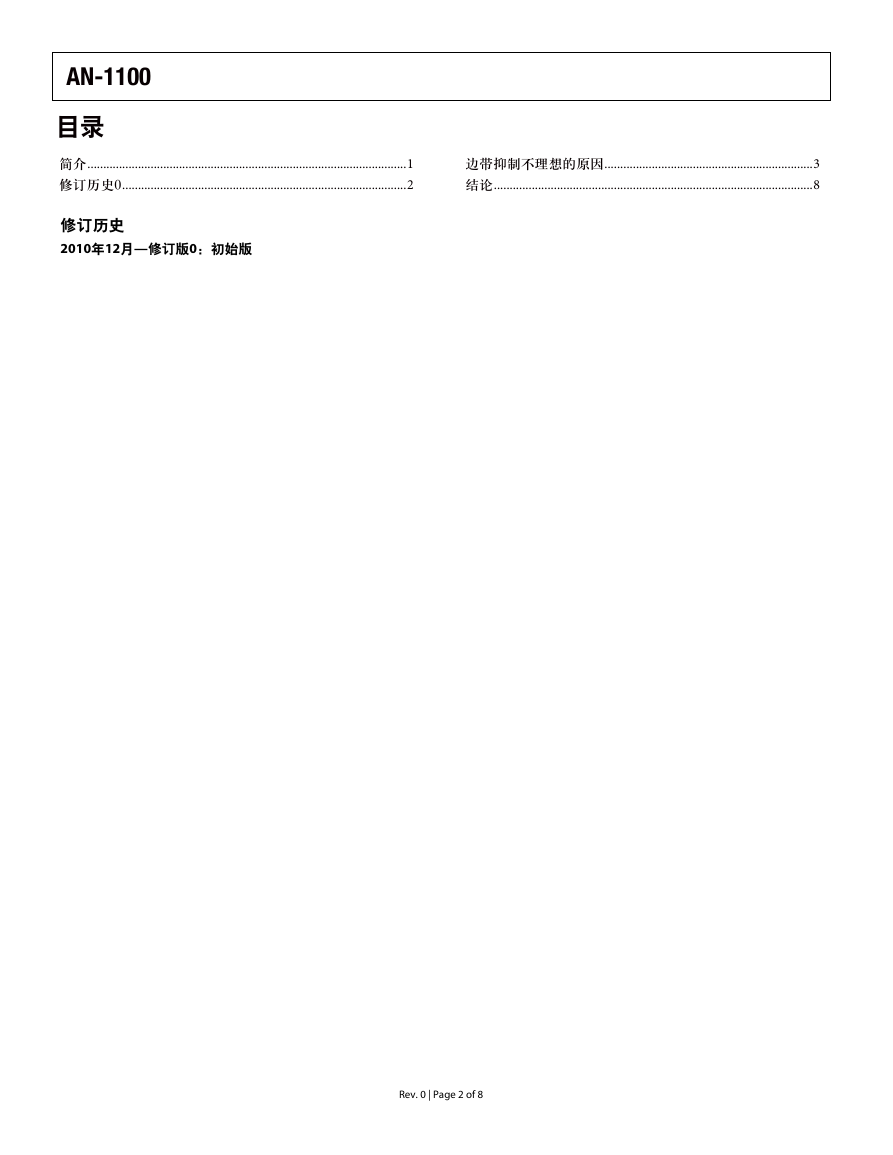

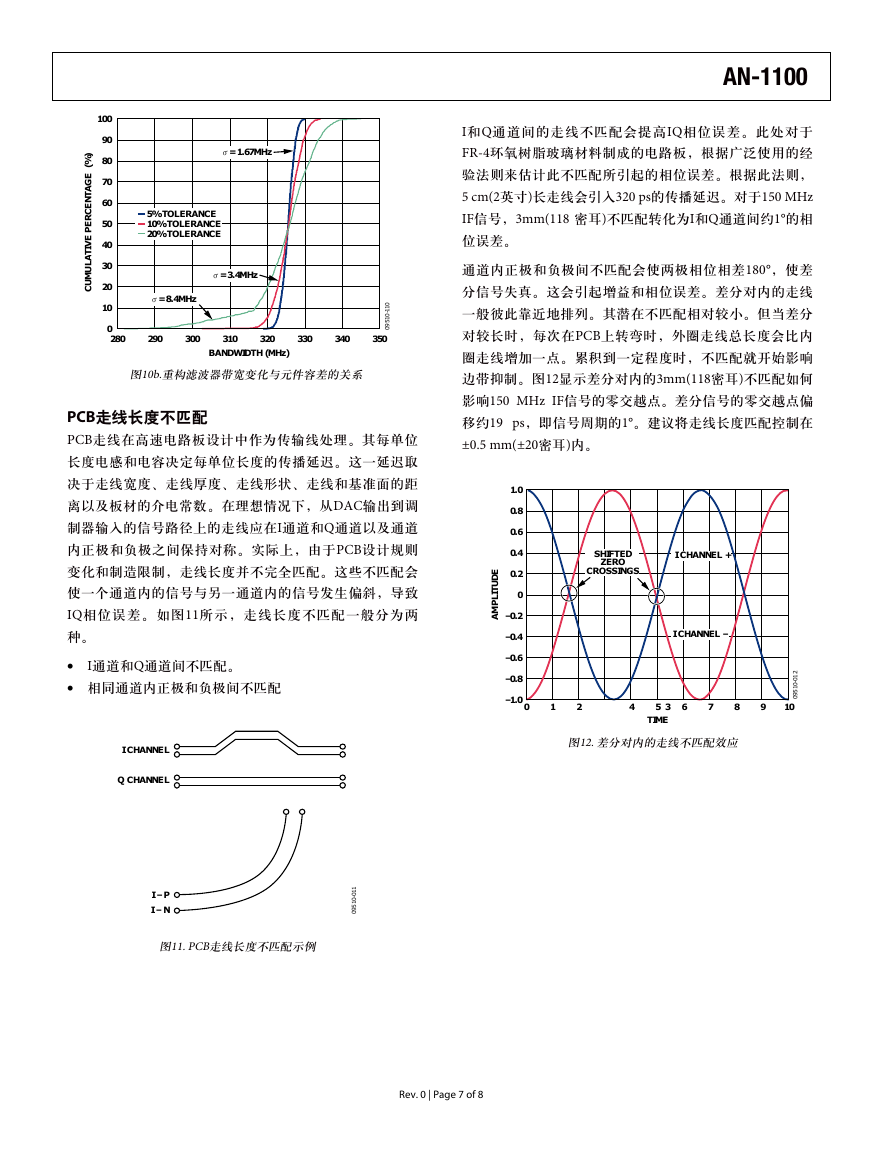

为了显示元件容差如何影响滤波器增益和组延迟,通过运

行蒙特卡洛仿真程序,从150 MHz IF信号的最差拐角提取

这些参数。假定所有元件的容差相同。针对5%、 10%和

20%容差重复运行仿真程序以进行比较。图10a及10b中的

结果表明,群延迟和3 dB带宽的标准偏差和元件容差大致

成正比。容差越大,变化也就越大。

从数字角度看,在10%容差的情况下,滤波器所引入的IQ

相位不平衡有超过三分之一(33%)的概率大于AD9122

TxDAC+。因此,宽松的容差在信号链内更容易增加不平

衡,从而抑制DAC的补偿范围。建议重构滤波器使用<10%

的元件容差。

)

%

(

E

G

A

T

N

E

C

R

E

P

E

V

T

A

L

U

M

U

C

I

100

90

80

70

60

50

40

30

20

10

0

1.80

σ = 50.8ps

σ = 25.4ps

5% TOLERANCE

10% TOLERANCE

20% TOLERANCE

σ = 12.7ps

0

1

0

-

0

1

5

9

0

1.85

1.90

1.95

2.00

2.05

2.10

GROUP DELAY (ns)

图10a.重构滤波器群延迟变化与元件容差的关系

Rev. 0 | Page 6 of 8

�

AN-1100

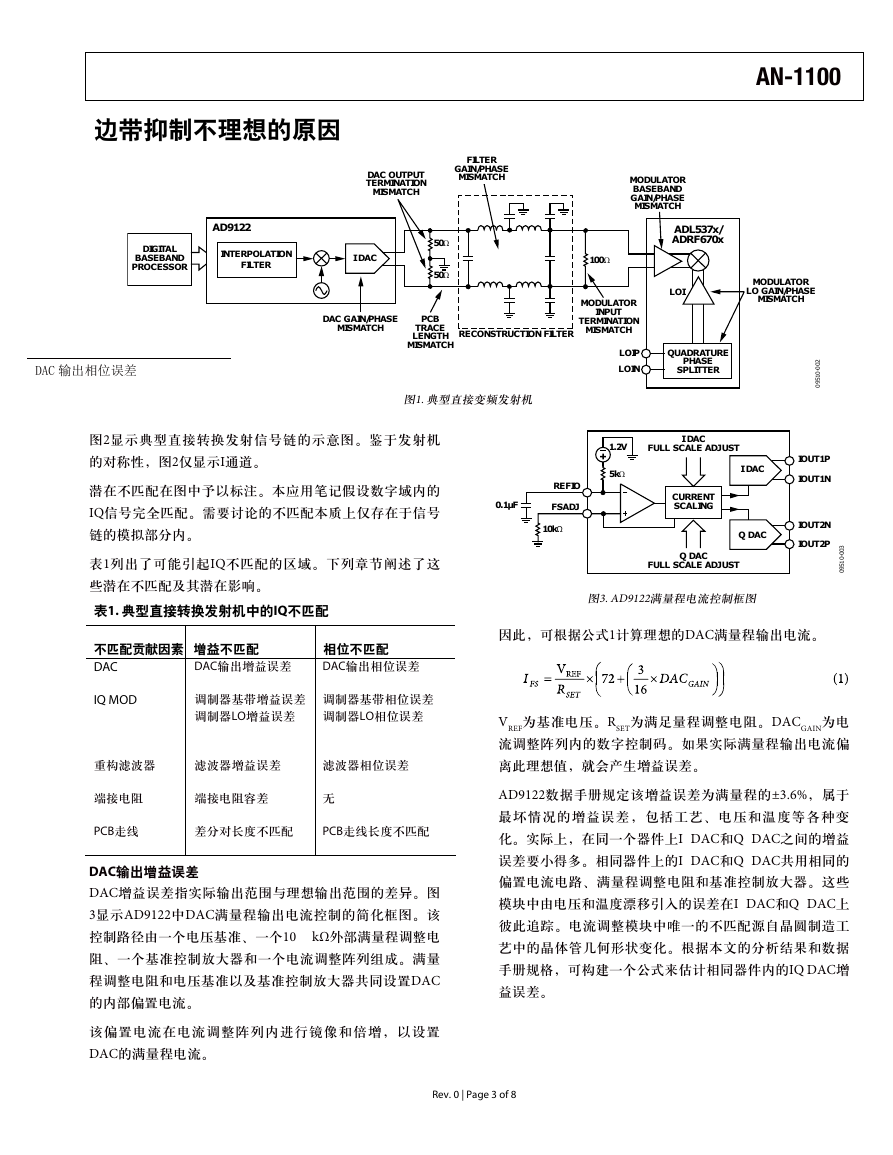

I和Q通道间的走线不匹配会提高IQ相位误差。此处对于

FR-4环氧树脂玻璃材料制成的电路板,根据广泛使用的经

验法则来估计此不匹配所引起的相位误差。根据此法则,

5 cm(2英寸)长走线会引入320 ps的传播延迟。对于150 MHz

IF信号,3mm(118 密耳)不匹配转化为I和Q通道间约1°的相

位误差。

通道内正极和负极间不匹配会使两极相位相差180°,使差

分信号失真。这会引起增益和相位误差。差分对内的走线

一般彼此靠近地排列。其潜在不匹配相对较小。但当差分

对较长时,每次在PCB上转弯时,外圈走线总长度会比内

圈走线增加一点。累积到一定程度时,不匹配就开始影响

边带抑制。图12显示差分对内的3mm(118密耳)不匹配如何

影响150 MHz IF信号的零交越点。差分信号的零交越点偏

移约19 ps,即信号周期的1°。建议将走线长度匹配控制在

±0.5 mm(±20密耳)内。

E

D

U

T

I

L

P

M

A

1.0

0.8

0.6

0.4

0.2

0

–0.2

–0.4

–0.6

–0.8

–1.0

SHIFTED

ZERO

CROSSINGS

I CHANNEL +

I CHANNEL –

0

1

2

4

5

3

TIME

6

7

8

9

10

图12. 差分对内的走线不匹配效应

2

1

0

-

0

1

5

9

0

)

%

(

E

G

A

T

N

E

C

R

E

P

E

V

T

A

L

U

M

U

C

I

100

90

80

70

60

50

40

30

20

10

0

280

σ = 1.67MHz

5% TOLERANCE

10% TOLERANCE

20% TOLERANCE

σ = 3.4MHz

σ = 8.4MHz

0

1

1

-

0

1

5

9

0

290

300

310

320

330

340

350

BANDWIDTH (MHz)

图10b.重构滤波器带宽变化与元件容差的关系

PCB走线长度不匹配

PCB走线在高速电路板设计中作为传输线处理。其每单位

长度电感和电容决定每单位长度的传播延迟。这一延迟取

决于走线宽度、走线厚度、走线形状、走线和基准面的距

离以及板材的介电常数。在理想情况下,从DAC输出到调

制器输入的信号路径上的走线应在I通道和Q通道以及通道

内正极和负极之间保持对称。实际上,由于PCB设计规则

变化和制造限制,走线长度并不完全匹配。这些不匹配会

使一个通道内的信号与另一通道内的信号发生偏斜,导致

IQ相位误差。如图11所示,走线长度不匹配一般分为两

种。

I通道和Q通道间不匹配。

•

• 相同通道内正极和负极间不匹配

I CHANNEL

Q CHANNEL

I – P

I – N

1

1

0

-

0

1

5

9

0

图11. PCB走线长度不匹配示例

Rev. 0 | Page 7 of 8

�

AN-1100

结论

虽然现代高速DAC和IQ调制器不难提供出色的增益和正交

精度,但系统内仍存在引起IQ增益和误差不平衡的其他因

素。使用DAC所提供的增益和正交校正功能可以有效改善

边带抑制性能。但设计系统时必须小心地确保复合误差在

DAC的校正范围内。有关增益和相位误差校准的详情,请

参见AN-1039应用笔记。

表2概述了IQ增益和相位误差的根源以及尽可能降低影响

的设计思路。

表2. IQ增益和相位误差概述

不匹配贡献因素 典型增益不匹配

典型相位不匹配

DAC

MOD基带

MOD LO

重构滤波器

端接电阻

PCB走线

由器件决定(对于

AD9122,< 0.3%)

由器件决定

(对于AD9122,< 1°)

由器件决定(对于

ADL5372,1.9 GHz

时为1%)

由器件决定(对于

ADL5372,1.9 GHz

时为0.21°)

由器件决定。

通过平坦的带通设计

和严格的元件容差

最小化

用干净LO信号

最小化

通过线性相位设计和

严格的元件容差

最小化

通过严格的元件容差

最小化

无

通过良好的差分对长

度匹配最小化

通过良好的PCB走

线长度匹配最小化

©2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

AN09510sc-0-7/11(0)

Rev. 0 | Page 8 of 8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc