VERILOG网表至SPICE网表转换器

CatalystDA

CatalystDA是一个将Verilog结构式网表 (netlist)转换成等效的SPICE格式网表的软件工具,

以用于版图验证或SPICE 仿真。

• 可从Verilog结构式描述中自动生成SPICE网表

• 接受IEEE 1364-2001 Verilog输入文件

• 既可生成Calibre的扩展式SPICE网表,也可生成标准SPICE网表

• 可对Verilog源文件进行语法和句法的检查

• 即使在缺少某些模块定义的情况下,仍可进行Verilog网表的部分转

换

• 可自动建立并连接SPICE电源和接地网路

• 可处理百万门极电路(multi-million gate)的Verilog网表

• CatalystDA可与Guardian LVS结合, 提供一套完整的版图验证解决

方案

• Silvaco强大的加密功能可以用来保护客户和第三方的知识产权

�

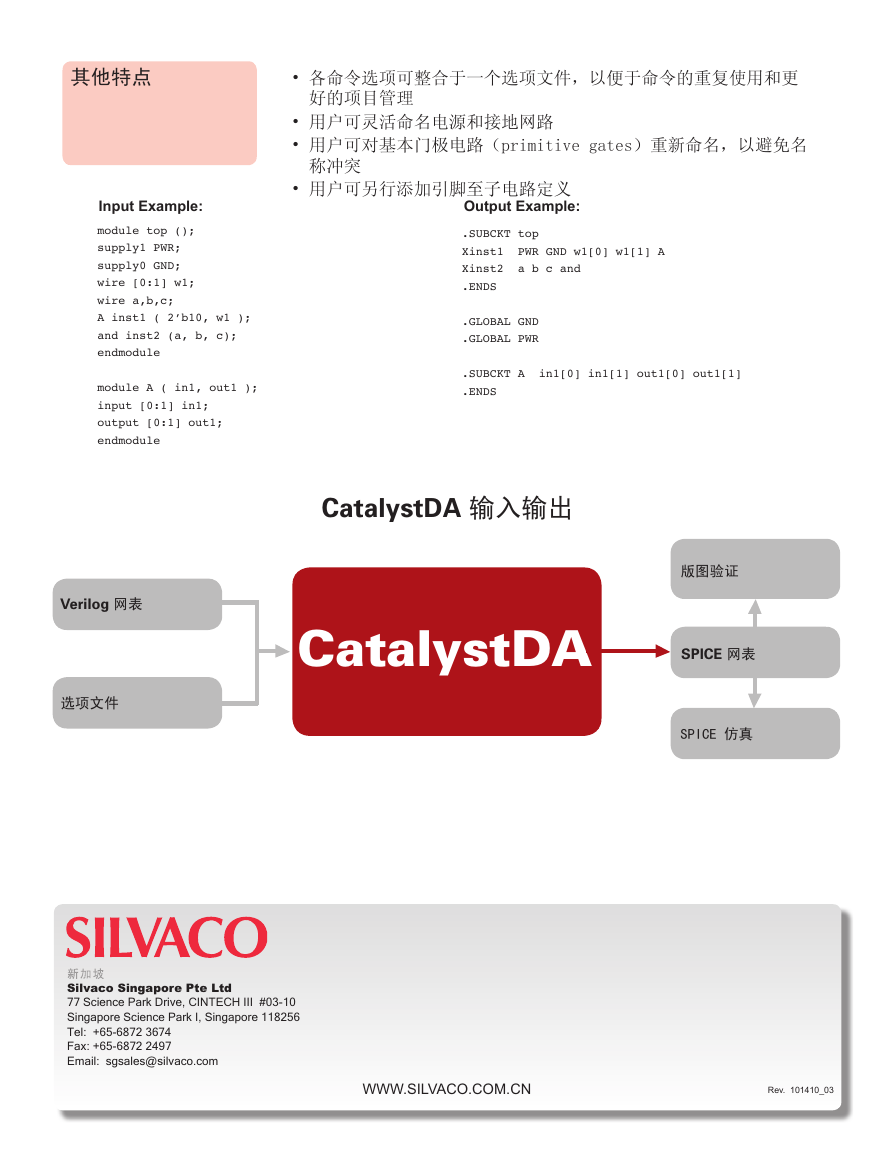

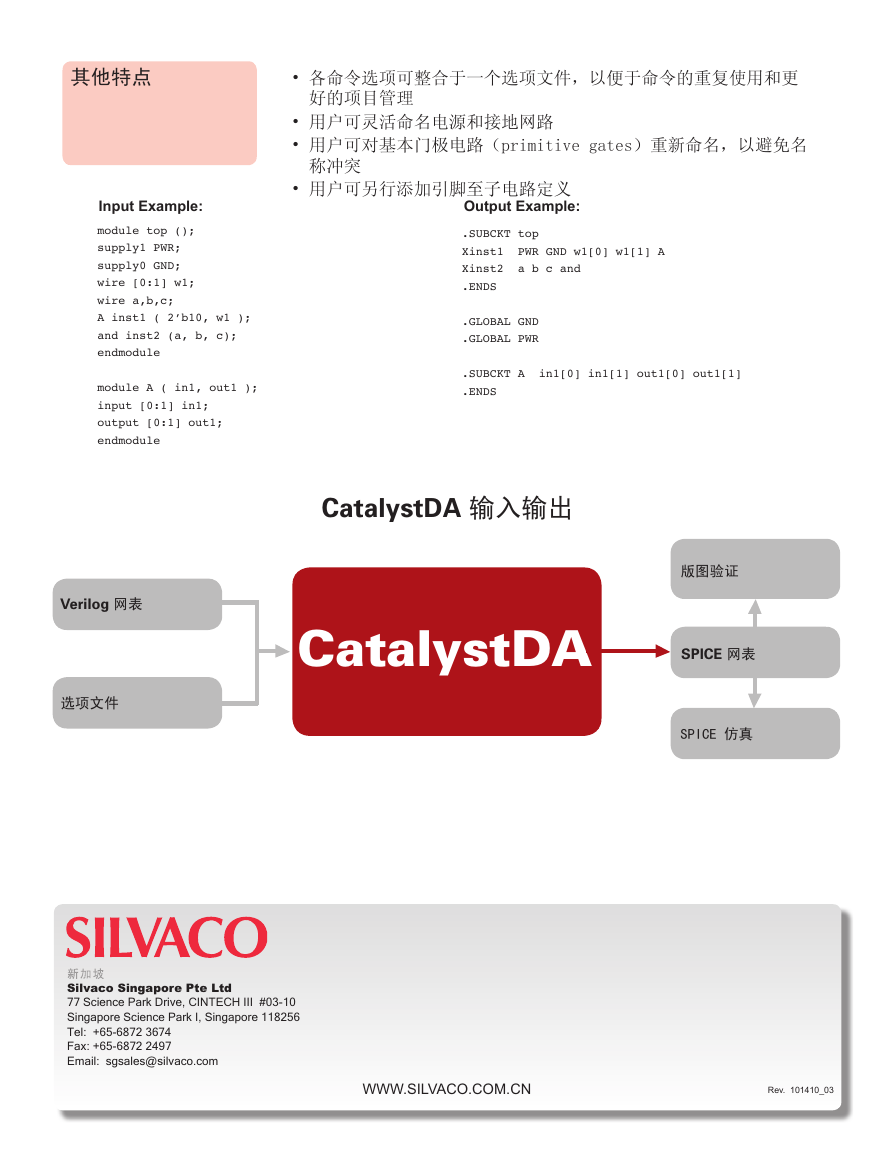

其他特点

• 各命令选项可整合于一个选项文件,以便于命令的重复使用和更

好的项目管理

• 用户可灵活命名电源和接地网路

• 用户可对基本门极电路(primitive gates)重新命名,以避免名

称冲突

• 用户可另行添加引脚至子电路定义

Output Example:

.SUBCKT top

Xinst1 PWR GND w1[0] w1[1] A

Xinst2 a b c and

.ENDS

.GLOBAL GND

.GLOBAL PWR

.SUBCKT A in1[0] in1[1] out1[0] out1[1]

.ENDS

Input Example:

module top ();

supply1 PWR;

supply0 GND;

wire [0:1] w1;

wire a,b,c;

A inst1 ( 2’b10, w1 );

and inst2 (a, b, c);

endmodule

module A ( in1, out1 );

input [0:1] in1;

output [0:1] out1;

endmodule

Verilog 网表

选项文件

CatalystDA 输入输出

CatalystDA

版图验证

SPICE 网表

SPICE 仿真

Silvaco Singapore Pte Ltd

77 Science Park Drive, CINTECH III #03-10

Singapore Science Park I, Singapore 118256

Tel: +65-6872 3674

Fax: +65-6872 2497

Email: sgsales@silvaco.com

WWW.SILVACO.COM.CN

Rev. 101410_03

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc