2

2010 年 2 月

第 33 卷第 1 期

舰 船 电 子 对 抗

SHIPBOARD EL ECTRON IC COUN TERM EASU RE

Feb. 2010

Vol. 33 No. 1

基于 FP GA 与 DDR2 SDRA M 的高速 ADC

采样数据缓冲器设计

徐家刚 ,张永伟 ,徐瑞荣

(船舶重工集团公司 723 所 ,扬州 225001)

摘要 :介绍了一种基于现场可编程门阵列 ( FP GA) 和第二代双倍数据率同步动态随机存取记忆体 (DDR2) 的高速模

数转换 (ADC) 采样数据缓冲器设计方法 ,论述了在 Xilinx V5 FP GA 中如何实现高速同步时钟设计和高速数据同步

接收设计 。

关键词 :现场可编程门阵列 ;模数转换器 ;数据缓冲器

中图分类号 : TP302 ; TN402 文献标识码 :B 文章编号 :CN32

1413 (2010) 01

0104

05

Design of Sampling Data Buffer of High

speed ADC

Based on FPGA and DD R2 SD RAM

rong

XU Jia

gang ,ZHAN G Yong

wei ,XU Rui

( The 723 Institute of CSIC , Yangzhou 225001 ,China)

Abstract :This paper int roduces a kind of design met hod for high

digital co nversion

(ADC) sampling data buffer based on field

p rogrammable gate array ( FP GA) and double data rate

two synchronous dynamic random access memory (DDR2) , discusses how to realize t he design of

high

Key words :field

speed data synchronous receiving in Xilinx V5 FP GA.

speed synchronous clock and high

p rogrammable gate array ;analog

digital converter ;data buffer

to

speed analog

to

0 引 言

高速数据采集系统目前已在雷达 、声纳 、图像处

理 、语音识别 、通信 、瞬态信号测试等领域得到广泛

应用 。它的关键技术是高速 ADC 技术 、高速数据

缓冲存储技术与传输技术 。当大量的高速实时数据

经过模数转换后 , 必须高速存储 ,然后再读回计算

机进行处理 。把高速海量的数据缓存下来进行数字

处理是设计的关键点和难点 。本文针对这些特点 ,

提出了基于 FP GA 与 DDR2 SDRAM 高速采样数

据缓冲器的设计方案 ,实现了高速数据缓存设计 ,并

用于实际工程中 ,取得了较好的效果 。

1 高速 ADC 采样数据缓冲器设计

方案

高速 AD 数据以 L VDS 电平传输至 Virtex

5

收稿日期 : 2009

06

21

系列 FP GA XC5VL X50 T ,这种方式可极大地抑制

共模噪声 ,从而得到比晶体管

晶体管逻辑 ( T TL ) /

互补型金属氧化物半导体 (CMOS) 电平传输更好的

抗干扰效果和更低的辐射噪声 。FP GA 接收数据

后 ,将数据存入自带的 64 位 DDR2 SDRAM (分 2

个 BAN K ,每个 BAN K 由 2 片 M T47 H64M16 拼接

而成) 。DDR2 的信号线分为时钟信号线 C K/ C K、

数据信号线 DQ/ DQS/ DM 、地址信号线 Address/

BA1/ BA0 、命令信号线 RAS/ CA S/ WE、控制信号

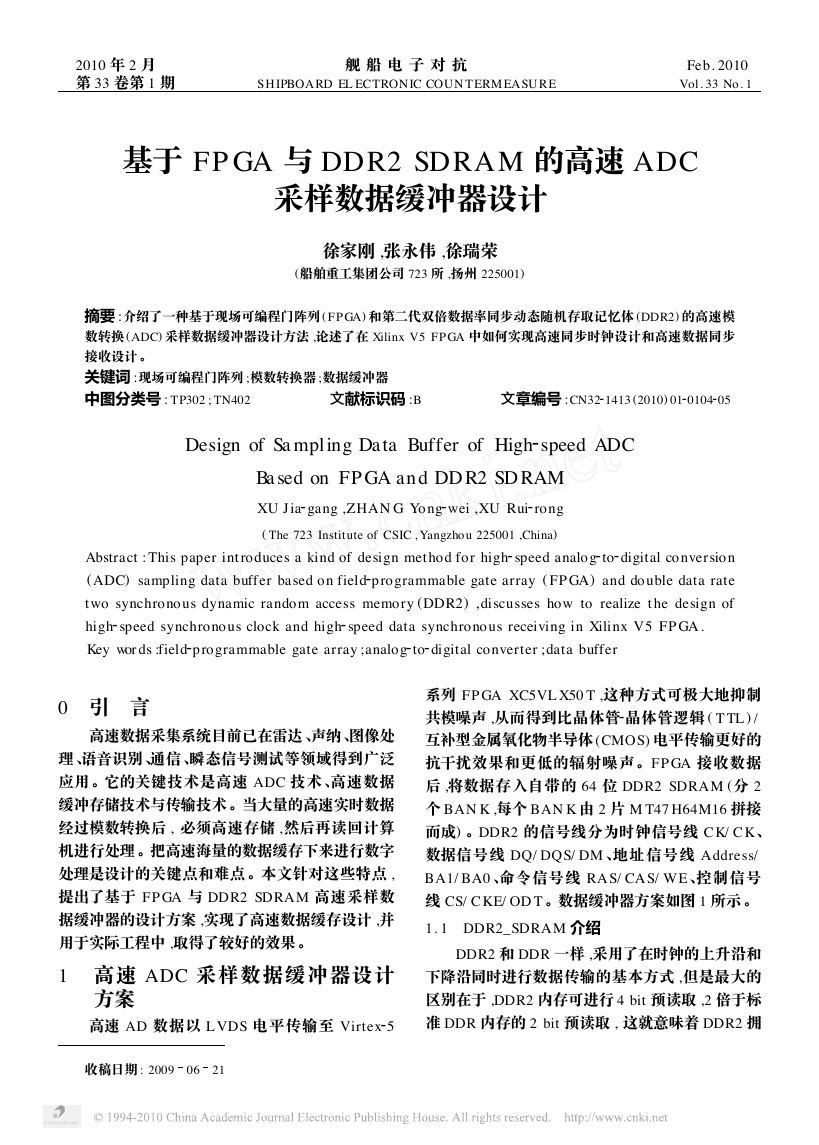

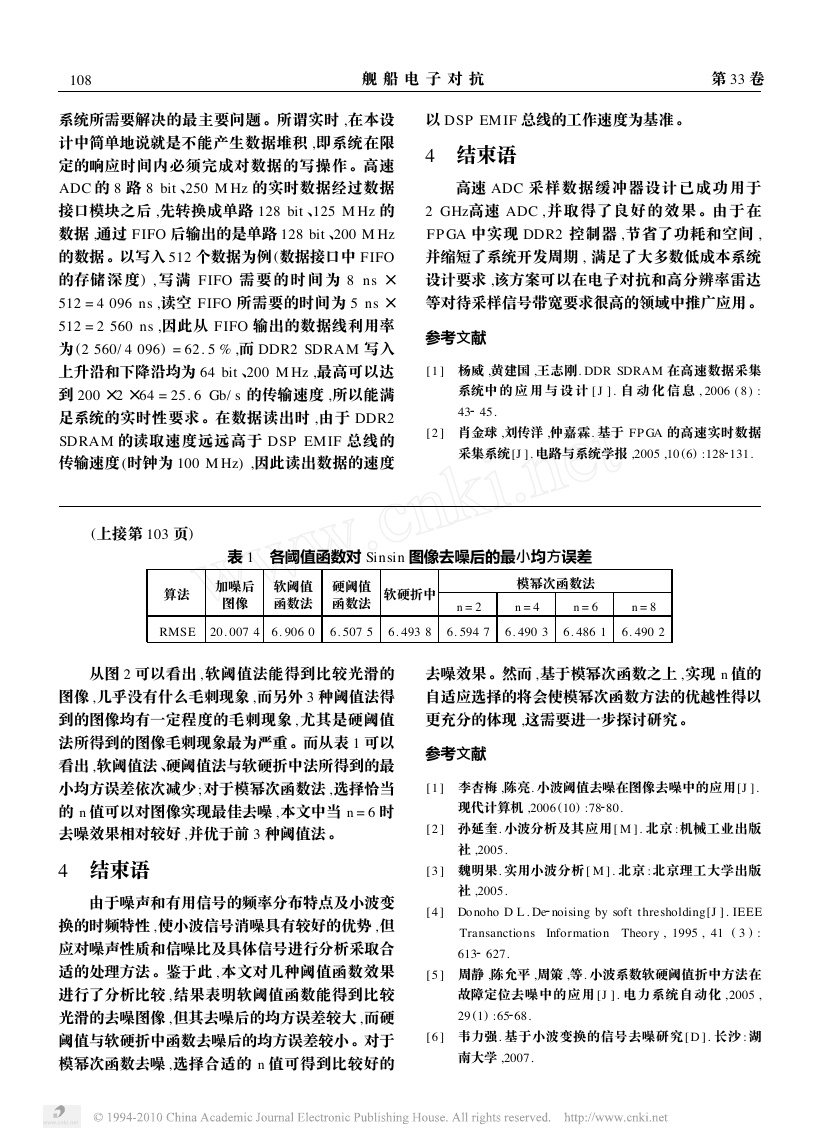

线 CS/ C KE/ OD T 。数据缓冲器方案如图 1 所示 。

1. 1 DDR2_SDRAM 介绍

DDR2 和 DDR 一样 ,采用了在时钟的上升沿和

下降沿同时进行数据传输的基本方式 ,但是最大的

区别在于 ,DDR2 内存可进行 4 bit 预读取 ,2 倍于标

准 DDR 内存的 2 bit 预读取 , 这就意味着 DDR2 拥

�

2

2

第 1 期

徐家刚等 :基于 FP GA 与 DDR2 SDRAM 的高速 ADC 采样数据缓冲器设计

501

512 MB 。DDR2 SDRAM 控制器在 200 M Hz 的时

钟频 率 下 实 现 , 最 高 可 以 达 到 200 ×2 ×64 =

25. 6 Gb/ s 的传输速度 。

5 FP GA 介绍

1. 2 Virtex

本设计中使用的是 Virtex

5 L XT 系列 FP GA ,

5 L XT 平台提供了业界第一个内建 PCI Ex

Virtex

p ress 端点模块和三重模式以太网媒体访问控制器

(MAC) 模块的 FP GA ,为设计人员提供了无需定制

的解决方案 ,可帮助他们节约时间 、降低功耗并节省

宝贵的 FP GA 构造资源 。基于 65 nm Virtex

5 平

台和领先的 Exp ressFabric 新技术 、成熟的 ASMBL

架构 以 及 低 功 耗 三 栅 极 氧 化 层 技 术 , 与 前 一 代

90 nm FP GA 相比 ,Virtex

5 L XT 平台的整体性能

平 均 提 高 30 % , 容 量 提 高 65 % , 动 态 功 耗 降 低

35 %。与软 IP 内核实现方式相比 ,硬 PCI Exp ress

内核可帮助用户节约多达 10 000 个 L U T 和 2 W

的功耗 。

5 L XT 系列的主要特点和创新包括 :

Virtex

(1) 业界功耗最低的收发器 :多达 24 个 Rocket

IO 收发器 ,工作在 100 Mbp s~3. 2 Gbp s 之间 ,每对

收发器/ 接收器的典型功耗小于 100 mW 。

(2) 内建 PCI Exp ress 模块 : 完全兼容的端点

模块 ,与 Rocket IO GTP 收发器配合 ,提供 ×1 , ×

2 , ×4 和 ×8 PCI Exp ress 接口 。

(3) 内 建 三 重 模 式 以 太 网 媒 体 访 问 控 制 器

(MAC) 模块 :4 个独立 10/ 100/ 1 000 Mbp s 模块 ,与

Rocket IO 收发器无缝配合 。

(4) 业界最好的信号完整性 : 8 个可编程的发

送预校正水平和 4 个可编程的接收均衡水平可适应

最苛刻的信道 。带有 Chip scope Pro 软件工具集的

高级诊断功能为工程师提供了最佳的信号完整性解

决方案 。

(5) 最广泛的协议支持 :Virtex

5 Rocket IO 收

发器支持大量业界标准 ,包括 PCI Exp ress 、Gigabit

Et hernet 、XAU I、SON ET/ SD H 、CPRI 和 OBSA I、

串行 RapidIO , HD

SDI 和光纤通道 。

(6) 成品设计解决方案 :全面的基于协议的解

决方案 ,包括软件 、IP 内核 、参考设计 、开发套件 、特

性报告 、协议兼容认证 、协作和设计支持 。

(7) 除 继 承 Virtex

4 FP GA 的 所 有 优 势 外 ,

5 系列器件还提供了一系列增强特性 ,从而

Virtex

简化了存储器接口的设计 ,并成功解决了日益提高

的总线速度所带来的挑战 。

图 1 数据缓冲器原理功能框图

有 2 倍于 DDR 的预读系统命令数据的能力 。举例

来说 , DDR SDRAM 可以采用 200 M Hz 的核心频

率 ( 内部存储单元阵列时钟) 来取得 400 M Hz 的实

际传输速率 , 而 DDR2 SDRAM 采用 100 M Hz 的

核心频率就可以实现 400 M Hz 的实际传输速率了 。

但 DDR2 内存技术最大的突破点其实不在于

所谓的 2 倍于 DDR 的传输能力 ,而是在采用更低发

热量 、更 低 功 耗 ( DDR2 SDRAM 工 作 电 压 只 有

1. 8 V ,而 DDR SDRAM 的工作电压是 2. 5 V) 的情

况下 ,反而获得更快的频率提升 ,突破标准 DDR 的

400 M Hz 的限制 ,另外还增加了 3 个方面的特性 :

(1) DDR2 内存的另一项重要改进是在内存本

身集成了信号终结器 。在并行总线中 ,信号传输到

一端尽头之后不会自动消失 ,而会沿着相反方向反

射回去 ,这样就会与后面传送过来的信号发生碰撞 ,

导致传输数据出错 。一般情况下 ,工作频率越高 ,信

号反射的现象就越严重 。终结器就是用来解决这个

问题的 ,它可以有效地吸收末端信号 ,防止数据反射

的发生 。

(2) DDR2 中还加入了离线驱动调整 (OCD) 技

术 。OCD 的主要功能在于调整 I/ O 接口端的电压 。

通过调整上拉/ 下拉的电阻值使两者电压相等 。这

样通过 OCD 技术减小数据选取脉冲 (DQ S) 与数据

信号 (DQ) 之间的倾斜来提高信号的完整性 ,从而提

高信号品质 。

(3) Po st CAS 主要是为了提高总线的利用效

率 ,可以通过调节 Po st CAS 的值来使得 bank ac

tive 命令和 read/ write 命令不至于发生冲突 , 提高

了总线的利用率 。

本设 计 采 用 的 M T47 H64M16 数 据 位 宽 为

16 bit ,有 8 个 BAN K ,13 条行地址线 ,10 条列地址

线 (行列地址线共用) ,因此每个内存芯片的容量为

8 192 ×1 024 ×8 × 16 bit , 即 1 Gb 。4 片

M T47 H64M16 芯片被分为 2 组 ,每组 2 片 ,就构成

了 64 bit 位 宽 , 总 容 量 为 1 Gb ×4 = 4 Gb , 即

�

601

(8) Virtex

舰 船 电 子 对 抗

第 33 卷

控制 AD 数据的输入和输出 。

(4) 接受数字信号处理器 (DSP) 指令 ,等待由

数据采集状态转为数据搬移状态 。

(5) 缓存从 DDR2 SDRAM 中读出的数据 ,并

通过 EMIF 总线将数据搬移到 DSP 所带的 DDR2

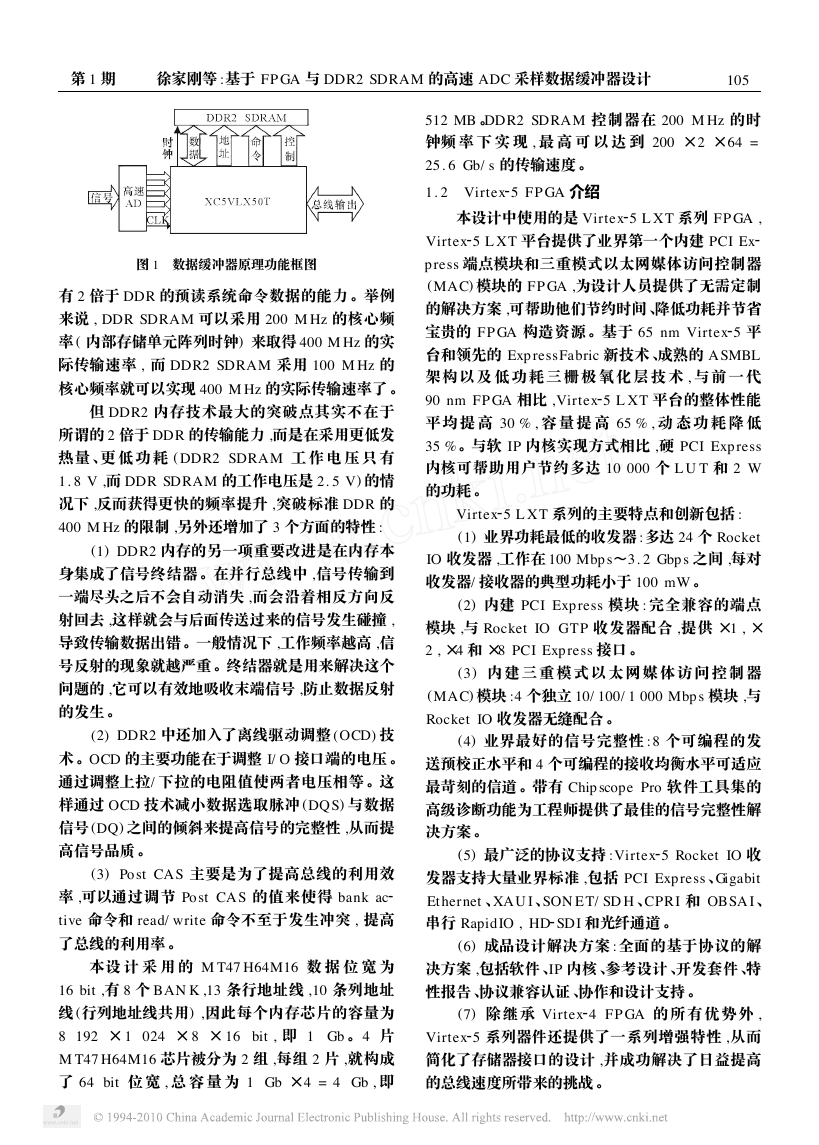

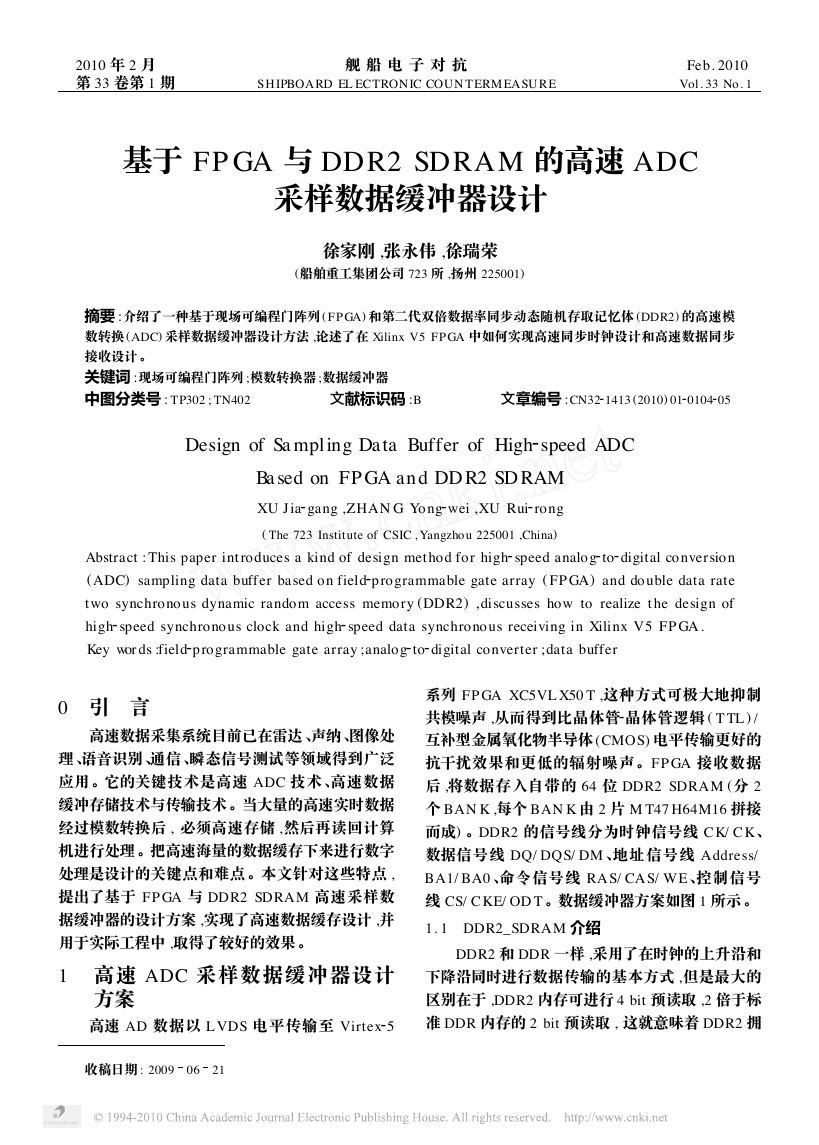

SDRAM 中 。FP GA 功能框图如图 2 所示 。

图 2 FP GA 功能框图

其中数据接口模块将来自外部高速 ADC 的数

据进行缓冲重排 、时钟域的转换 ,并且产生写 、读数

据所需要的指令地址信号 ;数据输入输出缓存模块

将来 自 数 据 接 口 模 块 的 同 步 数 据 、地 址 缓 存 在

FIFO 中 ,随时供 DDR2 控制器读取 ,并将读出的高

速数据进行缓冲 。

DSP 总线接口模块接受来自 DSP 的指令 ,包括

开始采集数据 、所需要的数据长度和触发电平 、停止

采集数据 、开始传送数据等 ,同时产生符合 EMIF 总

线工作时序的数据信号 。DDR2 控制器则直接对

DDR2 SDRAM 进行控制 ,产生符合 DDR2 SDRAM

时序的地址 、控制信号 ,在系统上电之初 ,控制器还

必须对 DDR2 SDRAM 进行初始化 。

2. 1 数据的重排及缓冲

为便于存储器存取 ,首先需将 8 路数据合并成

1 路 64 bit 的数据 (每路舍弃最低 2 位) ,正好与所

用的 DDR2 SDRAM 的单个存储单元的位宽一致 。

DDR2 SDRAM 在 200 M Hz 的工作频率下 ,上升沿

跟下降沿同时传输数据 ,这样在 1 个时钟周期内可

以传输 2 次数据 ,即总共 128 bit 数据 ,而如果在前

端采用 64 bit 位宽的话 ,1 个周期只能传输64 bit ,

显然不利于提高传输效率 ,因此要对这250 M Hz 、

64 bit 位宽的数据进行重排 ,以得到128 bit的位宽 。

数据重排的格式如下 :如原始数据流为 D0 ,Dl ,

D2 ,D3 ,D4 ,D5 , ……(D0 为最先到达的) ,重排后的

数据流为 : (D1D0) 、(D3D2) 、(D5D4) 、……,这样就

组成了 128 bit 的位宽 , 最后从 DDR2 SDRAM 中

5 架构集成了更多的功能 ,使之能

5 器件为存储器接

够超越运行频率的极限 。Virtex

口设计带来的增强功能包括 :

(a) 加入了 Exp ress Fabric 技术 。这种架构提

升可以使内部逻辑块在更高的时钟频率下运行 。基

本的逻辑片查找表 (L U T) 已经从四输入增加到六

输入 ,从而减少了逻辑层次 。Exp ress Fabric 技术

还提供了额外的布线资源 ,使逻辑片内部和可配置

逻辑块 (CLB) 之间可以有更多的直接布线 。

(b) 将最大的 BAN K 尺寸从 64 I/ O (或者在特

定的 Virtex

4 型号/ 封装组合中的 80 I/ O) 减少到

40 I/ O ,同时增加了 bank 的数量 。这样可以在同一

FP GA 上更有效地实现多种 I/ O 电平组合 。另外 ,

每个 bank 内的 I/ O 时钟资源也得以增加 。

(c) 除数字时钟管理器 (DCM) 模块以外 ,还加

入了锁相环模块作为时钟资源 。锁相环 ( PLL ) 在

低抖动时钟生成和输入时钟抖动滤波方面有很大

作用 。

(d ) 增 强 的 block RAM/ FIFO , 容 量 翻 倍

(36 kb) ,同时支持最高 72 bit 的位宽 ,要求纠错码

( ECC) 检测和纠正的应用 ,能够利用内置在每个

block RAM 中的 ECC 编码/ 译码逻辑 ,从而降低了

逻辑块的使用率 ,相对于使用通用逻辑实现而言可

以获得更高的性能 。

(e) 支持双向 I/ O 的片上分立式 Thevenin 终

端的数控阻抗 (DCI) (当驱动是三态时) 。与很多存

储器件系列中实现的片上终端元件 (OD T) 特性类

似 ,该功能主要针对特定的 HS TL 和 SS TL I/ O 标

准 ,而且在 FP GA 向存储器写入数据的时候能够节

省功耗 。

(f) 在封装衬底上直接加入低感抗的旁路电

容 , 通 过 降 低 外 部 旁 路 元 件 简 化 了 印 制 电 路 板

( PCB ) 的布局 。

2 高速数据实时存储设计

高速数据实时存储的控制由 Virtex

5 系列 FP

GA XC5VL X50 T 来完成 ,其主要功能如下 :

(1) FP GA 缓存来自 ADC 的高速采样数据 ,通

过地址产生逻辑完成读 、写地址指令的产生 。

(2) 将数据与地址 (其中包括操作指令) 进行缓

存 ,在 DDR2 控制器的控制下为 DDR2 SDRAM 提

供符合时序要求的数据及地址 。

(3) 对 DDR2 SDRAM 进行直接有效的控制 ,

�

第 1 期

徐家刚等 :基于 FP GA 与 DDR2 SDRAM 的高速 ADC 采样数据缓冲器设计

701

读数据时只需按照此规则还原数据即可 。

采用串并转换的方法来完成数据重排 。主要方

法是将 250 M Hz 的 64 bit 数据流转换成 125 M Hz

的 128 bit 的数据流 。这样 ,经过重排后的采样数据

就可以进入先进先出 ( FIFO) 缓冲了 。

除缓存数据 , FIFO 在本模块中的另一重要作

用就是时钟域的转换 。外部来的 ADC 采样数据跟

外部的 250 M Hz 采样时钟同步 ,而整个系统是基于

一个 200 M Hz 的全局时钟 ,要正确地采集来自外部

的信号 ,必须使数据跟系统时钟同步 。由于 FIFO

的读写可以使用不同的时钟 ,这样可以用125 M Hz

的时钟把128 bit 数据写入 FIFO ,而利用200 M Hz

全局时钟可将数据从 FIFO 中读出 ,这样就完成了

时钟域的转换 ,从而使数据跟系统时钟完全同步 。

2. 2 DSP 总线接口模块

FP GA 与 C6455 DSP 都 通 过 EM IFA 连 接 ,

C6455 通过其 EM IFA 的 CE4 与 FP GA 的异步模

块通信 ,接收 DSP 送过来的指令 ,而通过 EM IFA

的 CE5 与 FP GA 的同步模块通信 ,将数据传送到

DSP 自带的 DDR2 SDRAM 中去 。

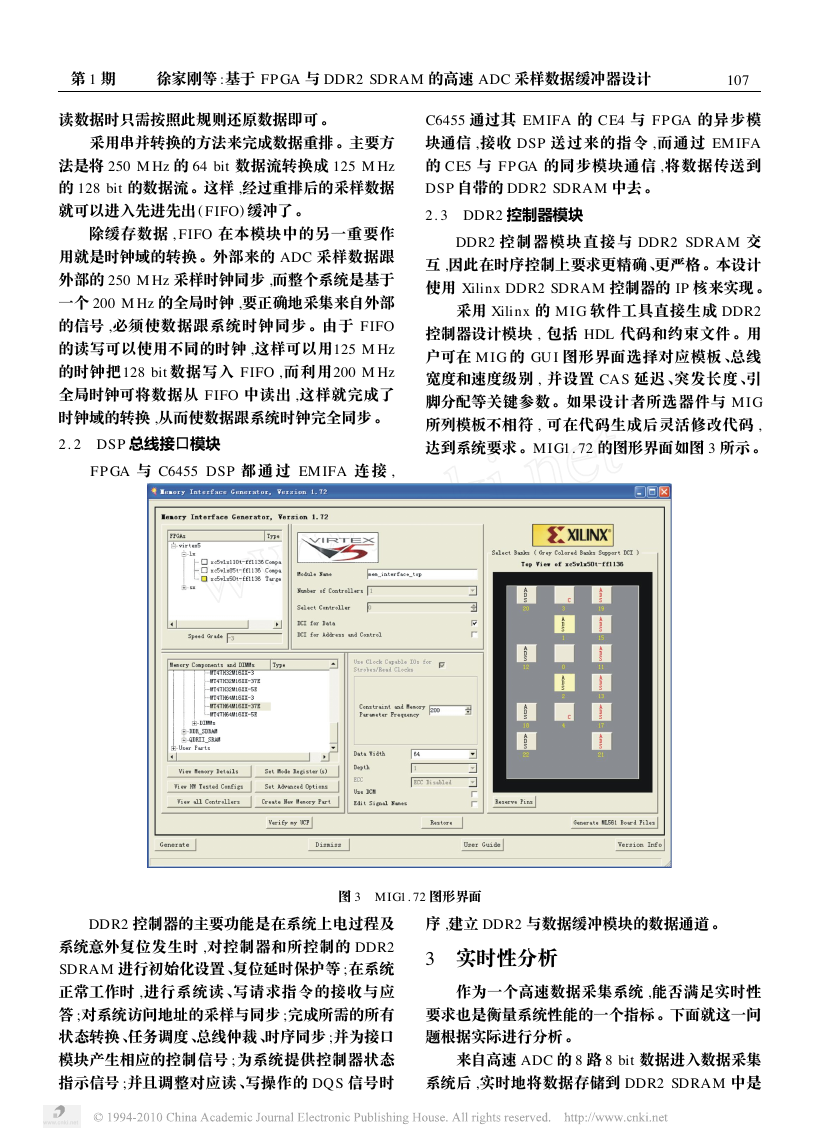

2. 3 DDR2 控制器模块

DDR2 控制器模块直接与 DDR2 SDRAM 交

互 ,因此在时序控制上要求更精确 、更严格 。本设计

使用 Xilinx DDR2 SDRAM 控制器的 IP 核来实现 。

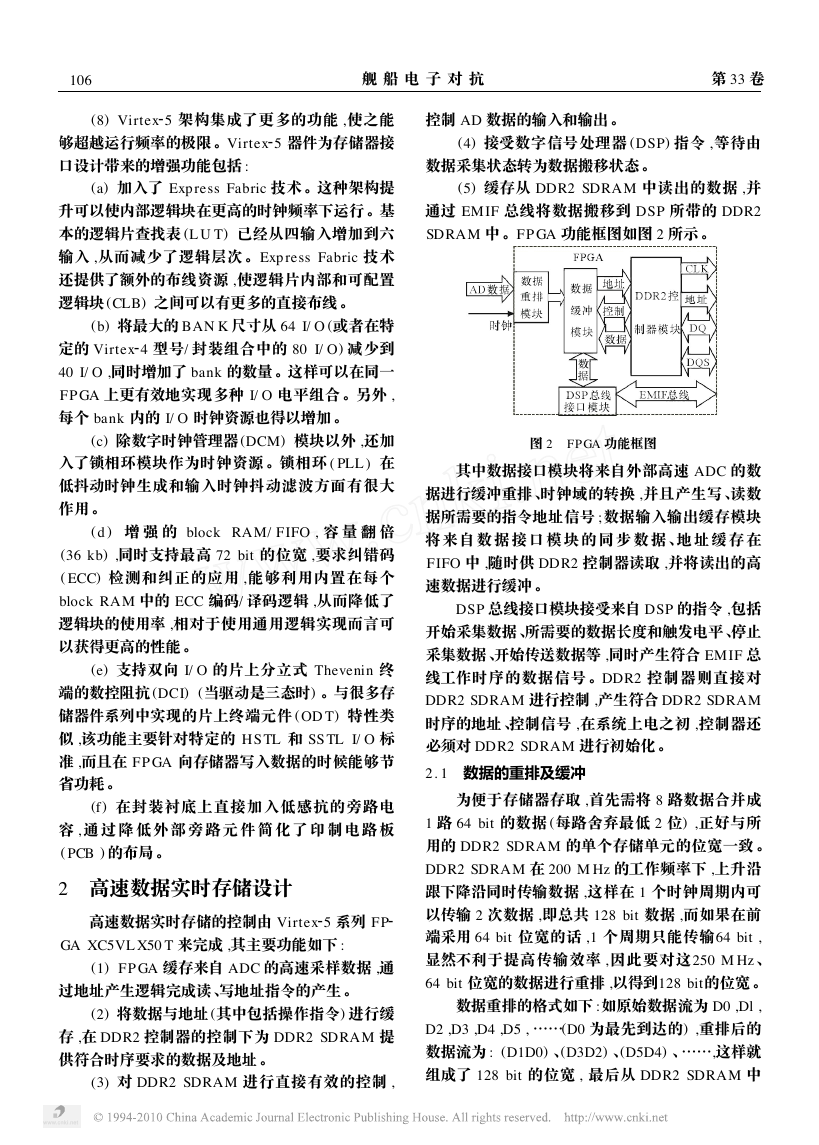

采用 Xilinx 的 M IG 软件工具直接生成 DDR2

控制器设计模块 , 包括 HDL 代码和约束文件 。用

户可在 MIG 的 GU I 图形界面选择对应模板 、总线

宽度和速度级别 , 并设置 CA S 延迟 、突发长度 、引

脚分配等关键参数 。如果设计者所选器件与 M IG

所列模板不相符 , 可在代码生成后灵活修改代码 ,

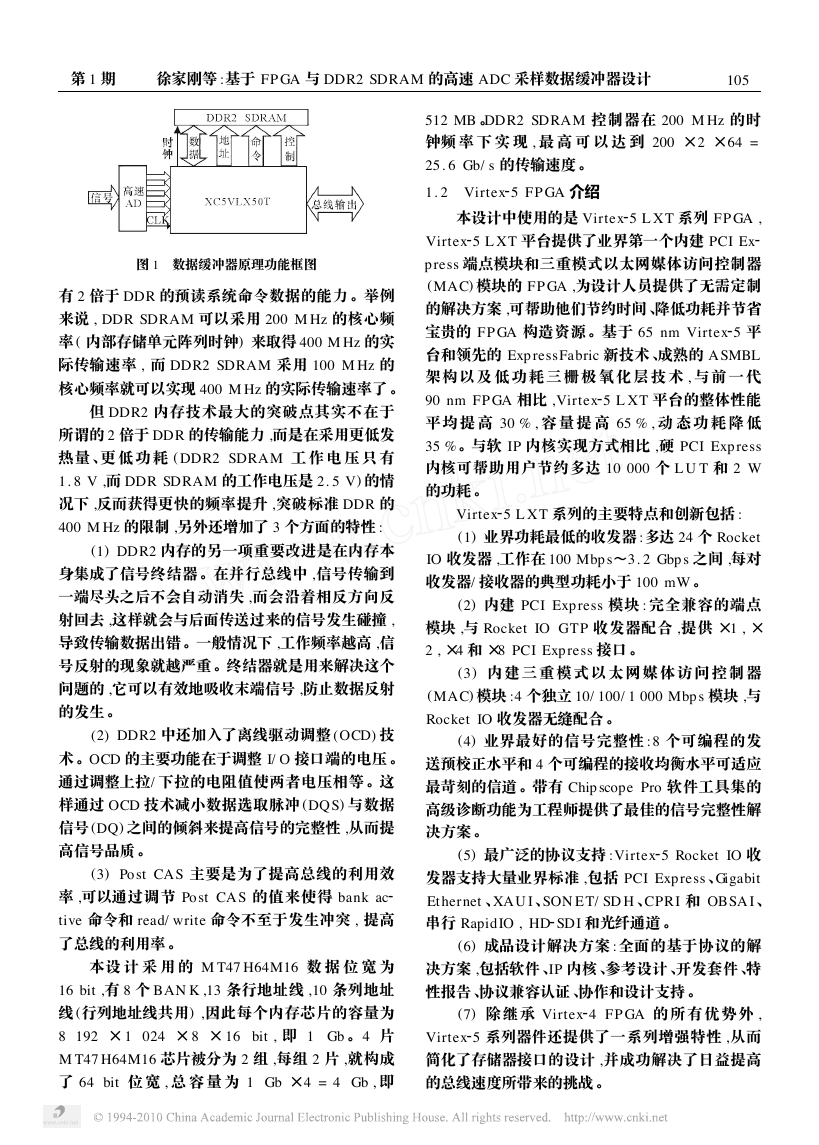

达到系统要求 。MIG1. 72 的图形界面如图 3 所示 。

图 3 MIG1. 72 图形界面

DDR2 控制器的主要功能是在系统上电过程及

系统意外复位发生时 ,对控制器和所控制的 DDR2

SDRAM 进行初始化设置 、复位延时保护等 ;在系统

正常工作时 ,进行系统读 、写请求指令的接收与应

答 ;对系统访问地址的采样与同步 ;完成所需的所有

状态转换 、任务调度 、总线仲裁 、时序同步 ;并为接口

模块产生相应的控制信号 ;为系统提供控制器状态

指示信号 ;并且调整对应读 、写操作的 DQ S 信号时

序 ,建立 DDR2 与数据缓冲模块的数据通道 。

3 实时性分析

作为一个高速数据采集系统 ,能否满足实时性

要求也是衡量系统性能的一个指标 。下面就这一问

题根据实际进行分析 。

来自高速 ADC 的 8 路 8 bit 数据进入数据采集

系统后 ,实时地将数据存储到 DDR2 SDRAM 中是

�

2

第 33 卷

2

2

系统所需要解决的最主要问题 。所谓实时 ,在本设

计中简单地说就是不能产生数据堆积 ,即系统在限

定的响应时间内必须完成对数据的写操作 。高速

ADC 的 8 路 8 bit 、250 M Hz 的实时数据经过数据

接口模块之后 ,先转换成单路 128 bit 、125 M Hz 的

数据 ,通过 FIFO 后输出的是单路 128 bit 、200 M Hz

的数据 。以写入 512 个数据为例 (数据接口中 FIFO

的存储 深 度) , 写 满 FIFO 需 要 的 时 间 为 8 ns ×

512 = 4 096 ns ,读空 FIFO 所需要的时间为 5 ns ×

512 = 2 560 ns ,因此从 FIFO 输出的数据线利用率

为 (2 560/ 4 096) = 62. 5 % ,而 DDR2 SDRAM 写入

上升沿和下降沿均为 64 bit 、200 M Hz ,最高可以达

到 200 ×2 ×64 = 25. 6 Gb/ s 的传输速度 ,所以能满

足系统的实时性要求 。在数据读出时 ,由于 DDR2

SDRAM 的读取速度远远高于 DSP EMIF 总线的

传输速度 (时钟为 100 M Hz) ,因此读出数据的速度

以 DSP EM IF 总线的工作速度为基准 。

4 结束语

高速 ADC 采样数据缓冲器设计已成功用于

2 GHz高速 ADC , 并取得了良好的效果 。由于在

FP GA 中实现 DDR2 控制器 ,节省了功耗和空间 ,

并缩短了系统开发周期 , 满足了大多数低成本系统

设计要求 ,该方案可以在电子对抗和高分辨率雷达

等对待采样信号带宽要求很高的领域中推广应用 。

参考文献

[ 1 ] 杨威 ,黄建国 ,王志刚. DDR SDRAM 在高速数据采集

系统中 的 应 用 与 设 计 [ J ]. 自 动 化 信 息 , 2006 ( 8 ) :

43

45.

[ 2 ] 肖金球 ,刘传洋 ,仲嘉霖. 基于 FP GA 的高速实时数据

采集系统[J ]. 电路与系统学报 ,2005 ,10 (6) :128

131.

801

舰 船 电 子 对 抗

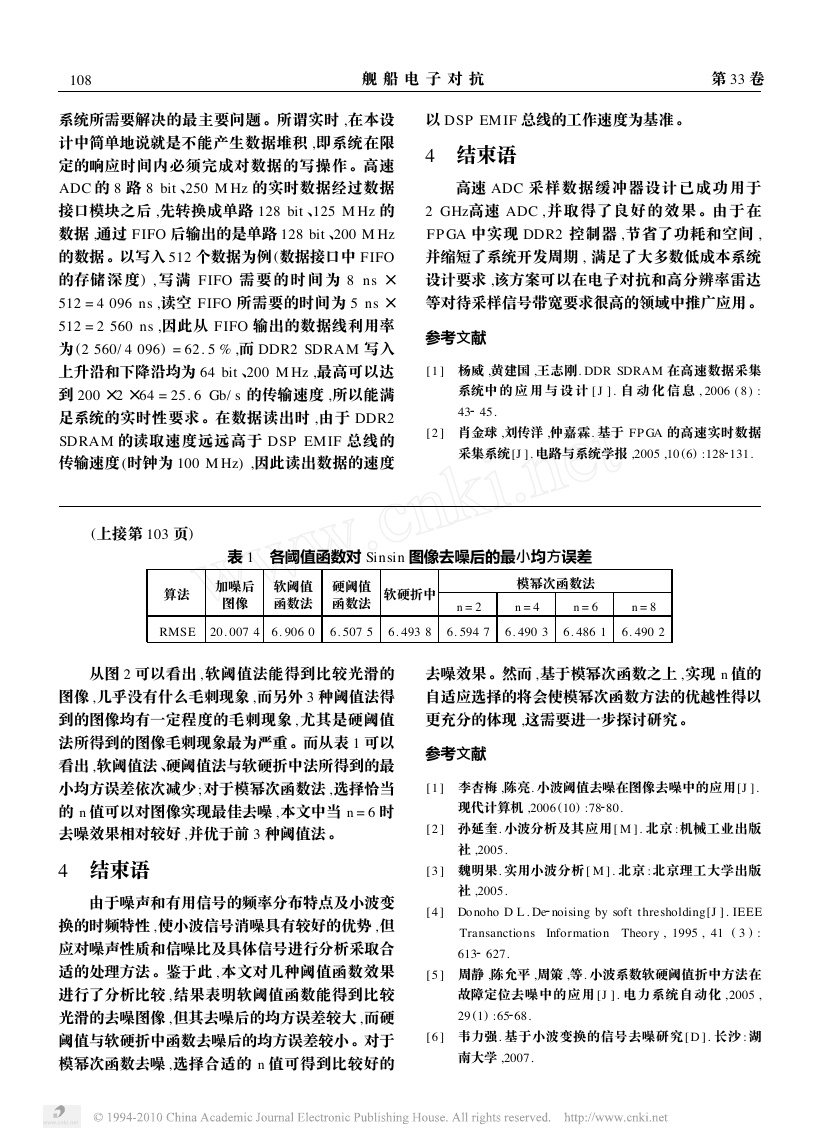

(上接第 103 页)

算法

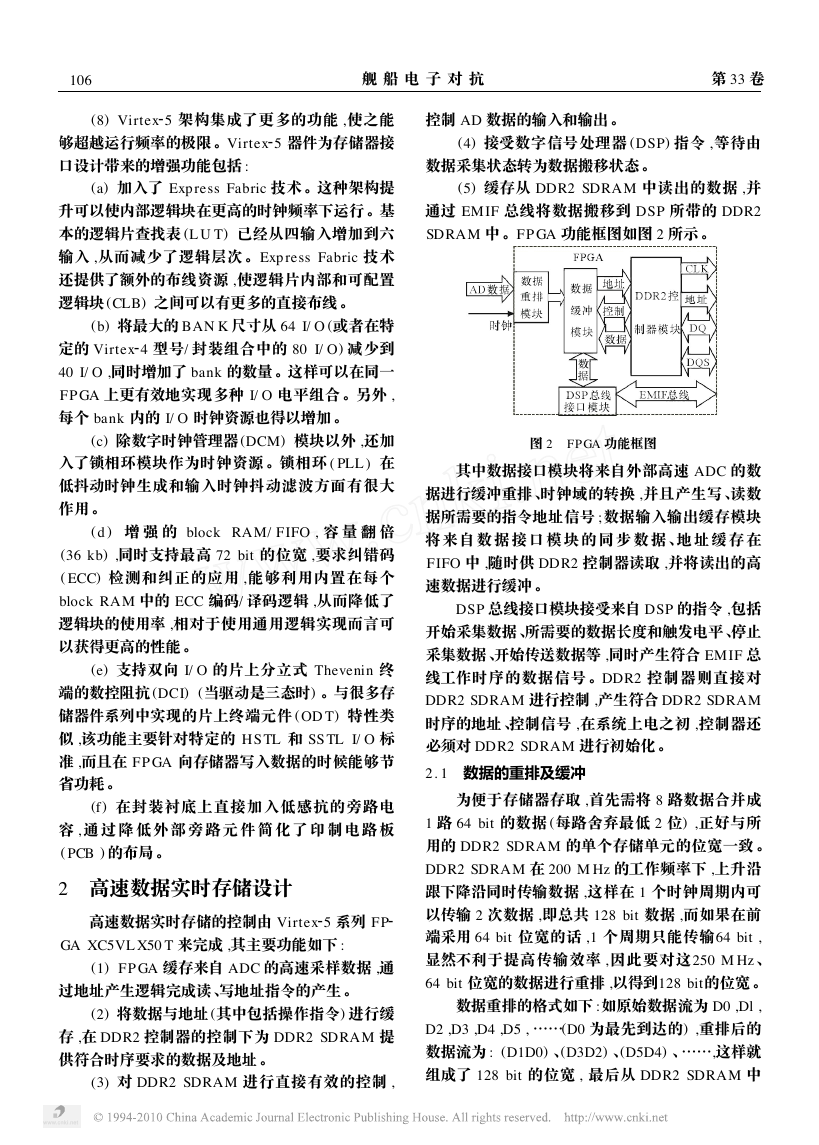

表 1 各阈值函数对 Sinsin 图像去噪后的最小均方误差

模幂次函数法

加噪后

图像

软阈值

函数法

硬阈值

函数法

软硬折中

n = 2

n = 4

n = 6

n = 8

RMSE 20. 007 4 6. 906 0

6. 507 5

6. 493 8

6. 594 7

6. 490 3

6. 486 1

6. 490 2

从图 2 可以看出 , 软阈值法能得到比较光滑的

图像 ,几乎没有什么毛刺现象 ,而另外 3 种阈值法得

到的图像均有一定程度的毛刺现象 , 尤其是硬阈值

法所得到的图像毛刺现象最为严重 。而从表 1 可以

看出 ,软阈值法 、硬阈值法与软硬折中法所得到的最

小均方误差依次减少 ;对于模幂次函数法 ,选择恰当

的 n 值可以对图像实现最佳去噪 ,本文中当 n = 6 时

去噪效果相对较好 ,并优于前 3 种阈值法 。

4 结束语

由于噪声和有用信号的频率分布特点及小波变

换的时频特性 ,使小波信号消噪具有较好的优势 ,但

应对噪声性质和信噪比及具体信号进行分析采取合

适的处理方法 。鉴于此 , 本文对几种阈值函数效果

进行了分析比较 ,结果表明软阈值函数能得到比较

光滑的去噪图像 ,但其去噪后的均方误差较大 ,而硬

阈值与软硬折中函数去噪后的均方误差较小 。对于

模幂次函数去噪 ,选择合适的 n 值可得到比较好的

去噪效果 。然而 ,基于模幂次函数之上 ,实现 n 值的

自适应选择的将会使模幂次函数方法的优越性得以

更充分的体现 ,这需要进一步探讨研究 。

参考文献

[1 ] 李杏梅 ,陈亮. 小波阈值去噪在图像去噪中的应用[J ].

现代计算机 ,2006 (10) :78

80.

[ 2 ] 孙延奎. 小波分析及其应用 [ M ]. 北京 :机械工业出版

社 ,2005.

[ 3 ] 魏明果. 实用小波分析 [ M ]. 北京 :北京理工大学出版

社 ,2005.

[4 ] Donoho D L . De

Transanctions

613

627.

noising by soft thresholding[J ]. IEEE

Information Theory , 1995 , 41 ( 3 ) :

[ 5 ] 周静 ,陈允平 ,周策 ,等. 小波系数软硬阈值折中方法在

故障定位去噪中的应用 [J ]. 电力系统自动化 ,2005 ,

29 (1) :65

68.

[ 6 ] 韦力强. 基于小波变换的信号去噪研究 [ D ]. 长沙 :湖

南大学 ,2007.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc