AXI 总线协议资料整理

第一部分:

1、AXI 简介:AXI(Advanced eXtensible Interface)是一种总线协议,该协议是

ARM 公司提出的 AMBA(Advanced Microcontroller Bus Architecture)3.0 协议中

最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控

制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首

地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易

就行时序收敛。AXI 是 AMBA 中一个新的高性能协议。AXI 技术丰富了现有

的 AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

2、 AXI 特点: 单向通道体系结构。信息流只以单方向传输,简化时钟域间的

桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,

可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优

化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

第二部分:

本部分对 AXI1.0 协议的各章进行整理。

第一章

本章主要介绍 AXI 协议和 AXI 协议定义的基础事务。

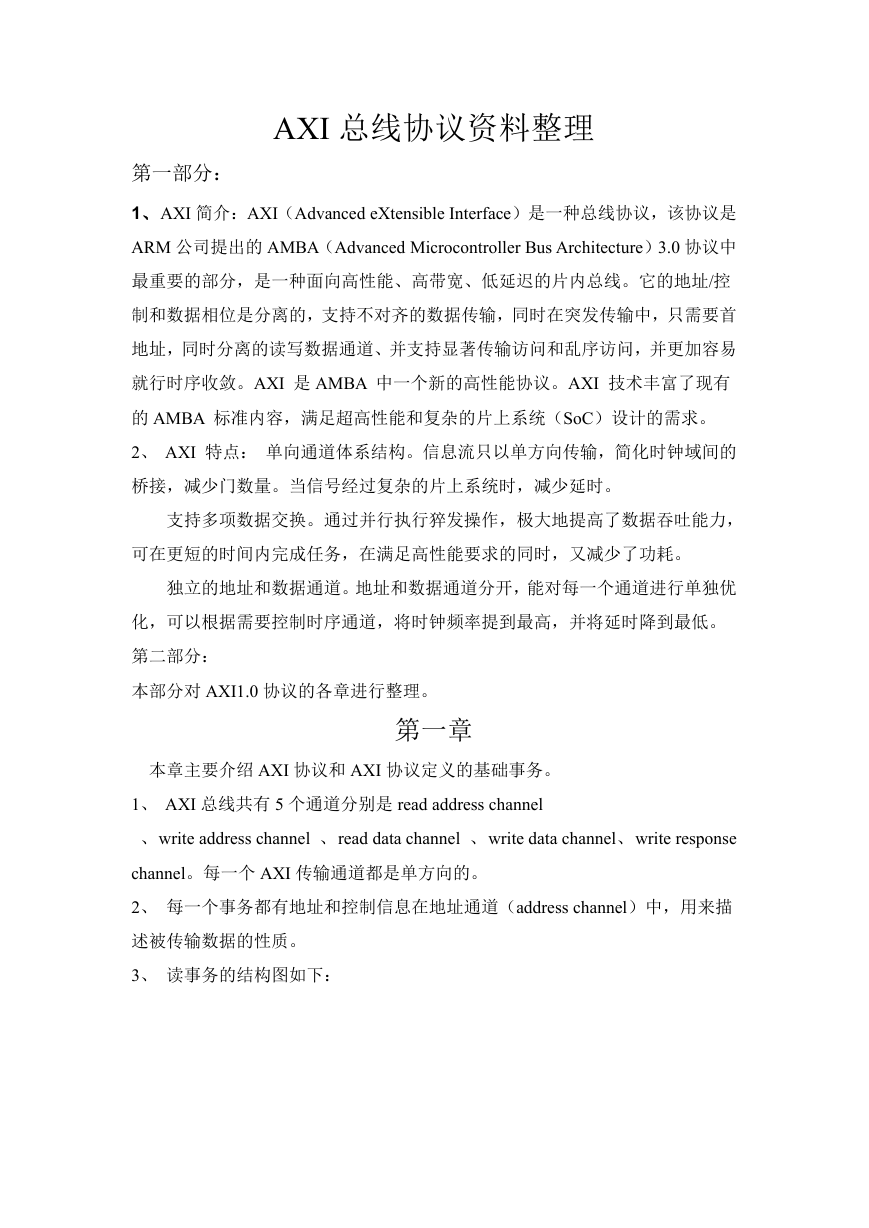

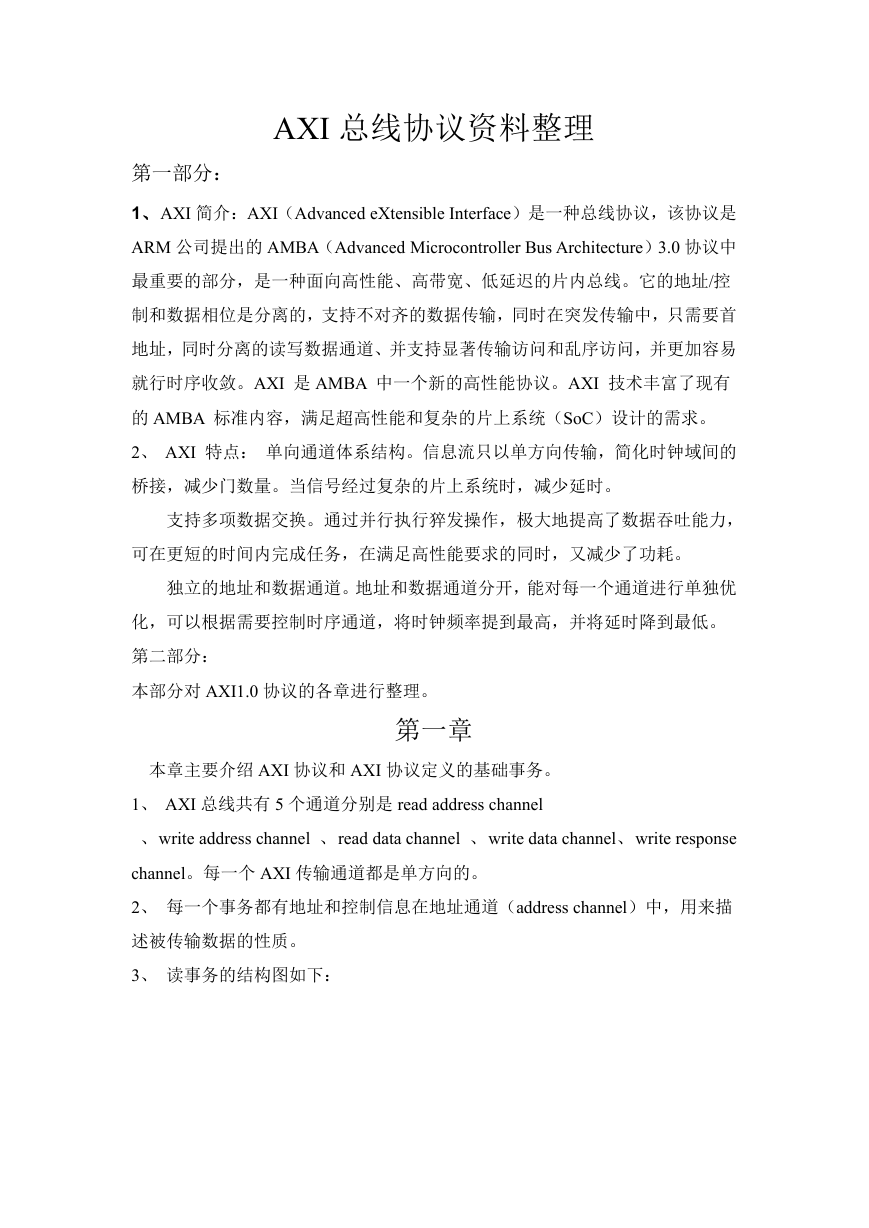

1、 AXI 总线共有 5 个通道分别是 read address channel

、write address channel 、read data channel 、write data channel、write response

channel。每一个 AXI 传输通道都是单方向的。

2、 每一个事务都有地址和控制信息在地址通道(address channel)中,用来描

述被传输数据的性质。

3、 读事务的结构图如下:

�

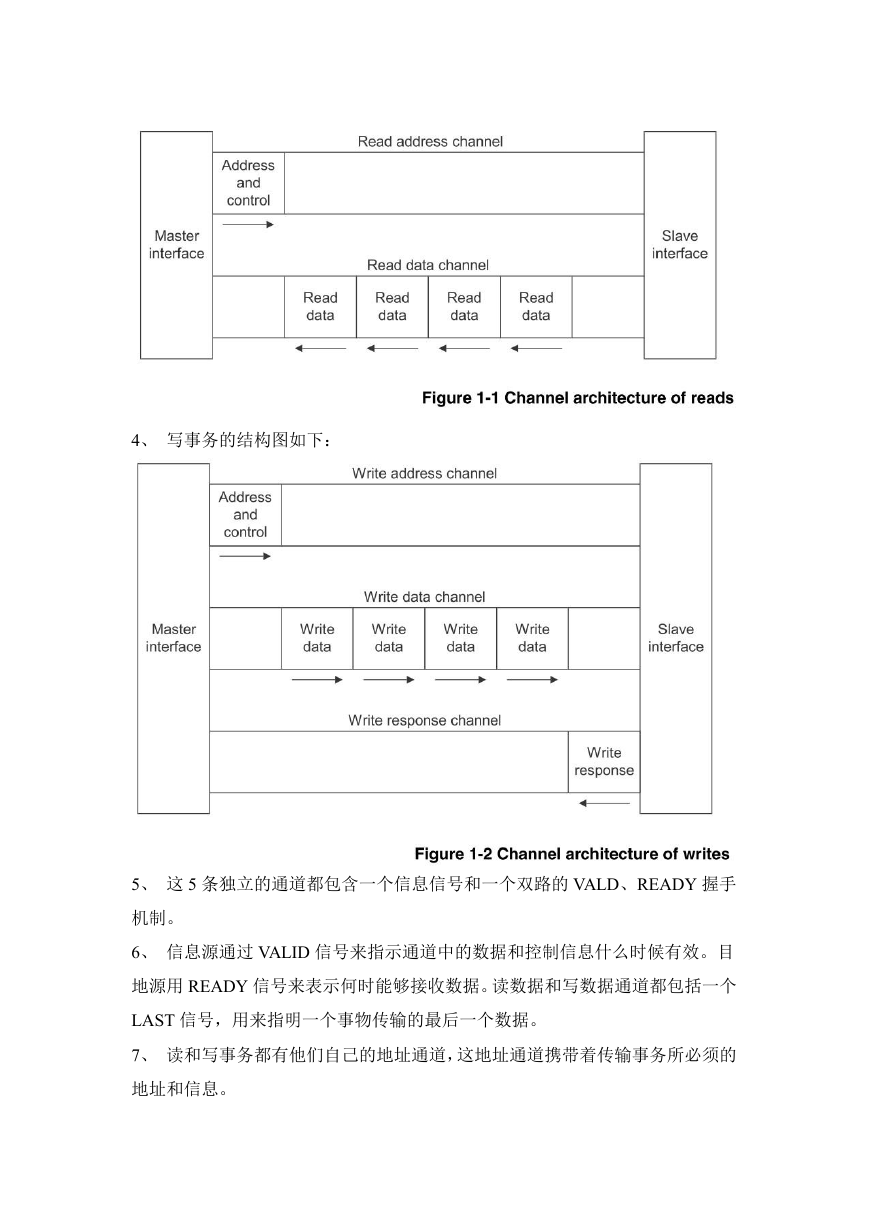

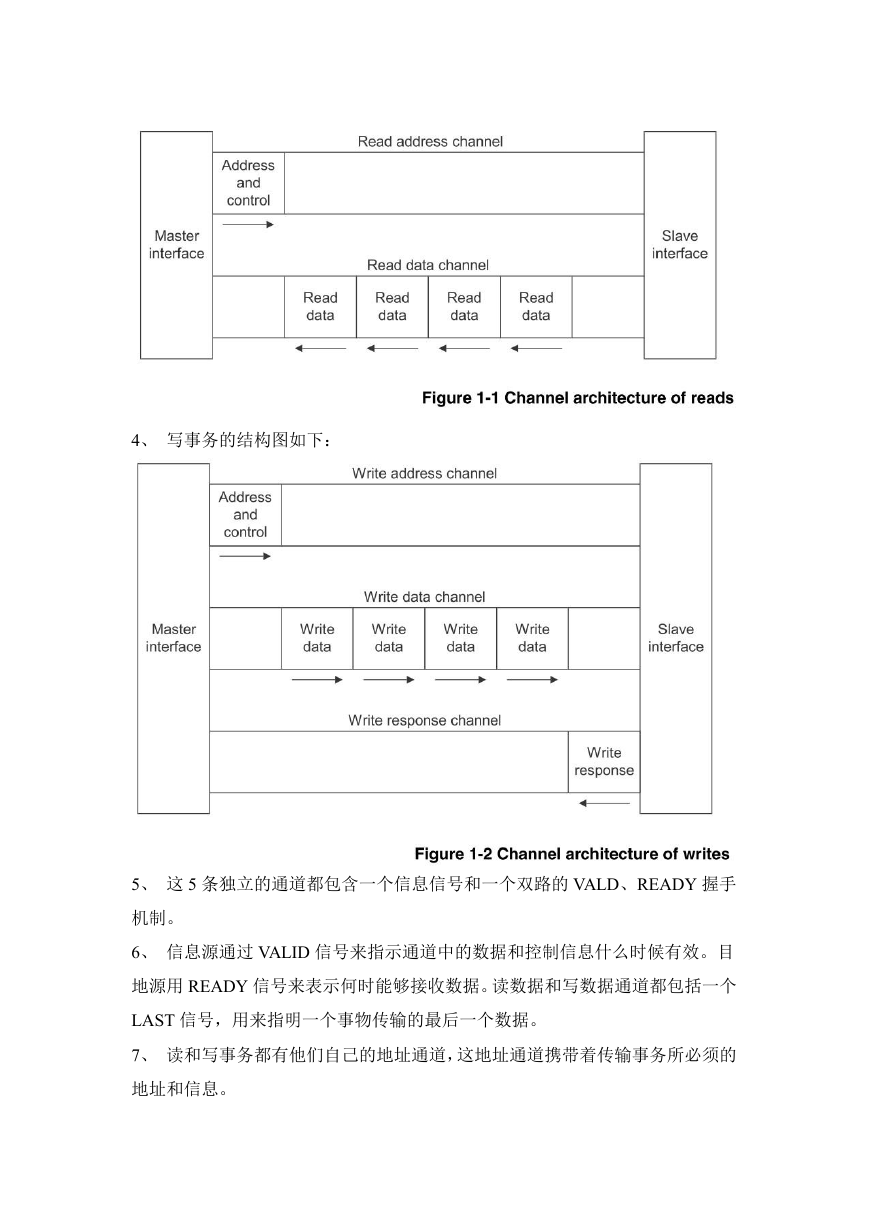

4、 写事务的结构图如下:

5、 这 5 条独立的通道都包含一个信息信号和一个双路的 VALD、READY 握手

机制。

6、 信息源通过 VALID 信号来指示通道中的数据和控制信息什么时候有效。目

地源用 READY 信号来表示何时能够接收数据。读数据和写数据通道都包括一个

LAST 信号,用来指明一个事物传输的最后一个数据。

7、 读和写事务都有他们自己的地址通道,这地址通道携带着传输事务所必须的

地址和信息。

�

8、 读数据通道传送着从设备到主机的读数据和读响应信息。读响应信息指明读

事务的完成状态。

9、 写数据通路传送着主机向设备的写数据。每八个数据都会有一个 byte lane ,

用来指明数据总线上面的哪些 byte 有效。写响应通道提供了设备响应写事务的

一种方式。这完成信号每一次突发式读写会产生一个。

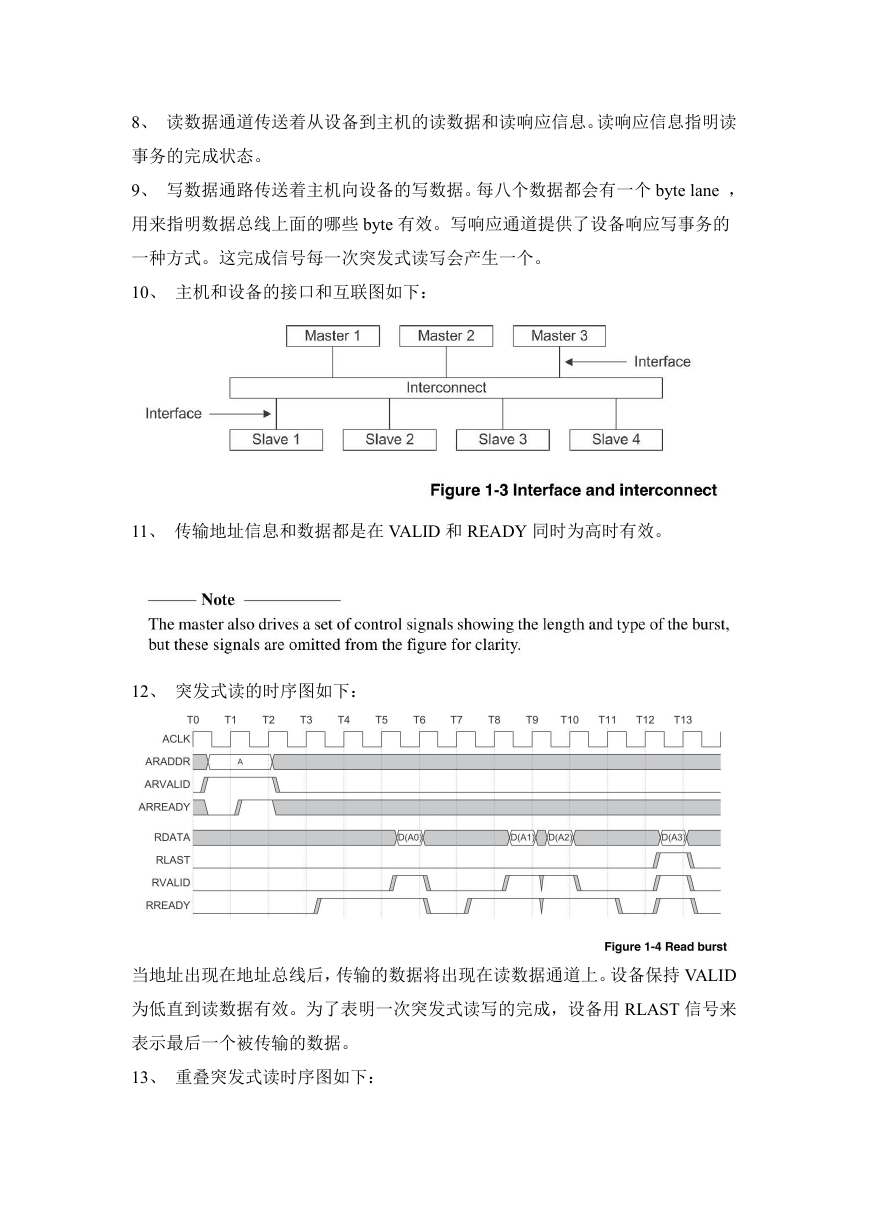

10、 主机和设备的接口和互联图如下:

11、 传输地址信息和数据都是在 VALID 和 READY 同时为高时有效。

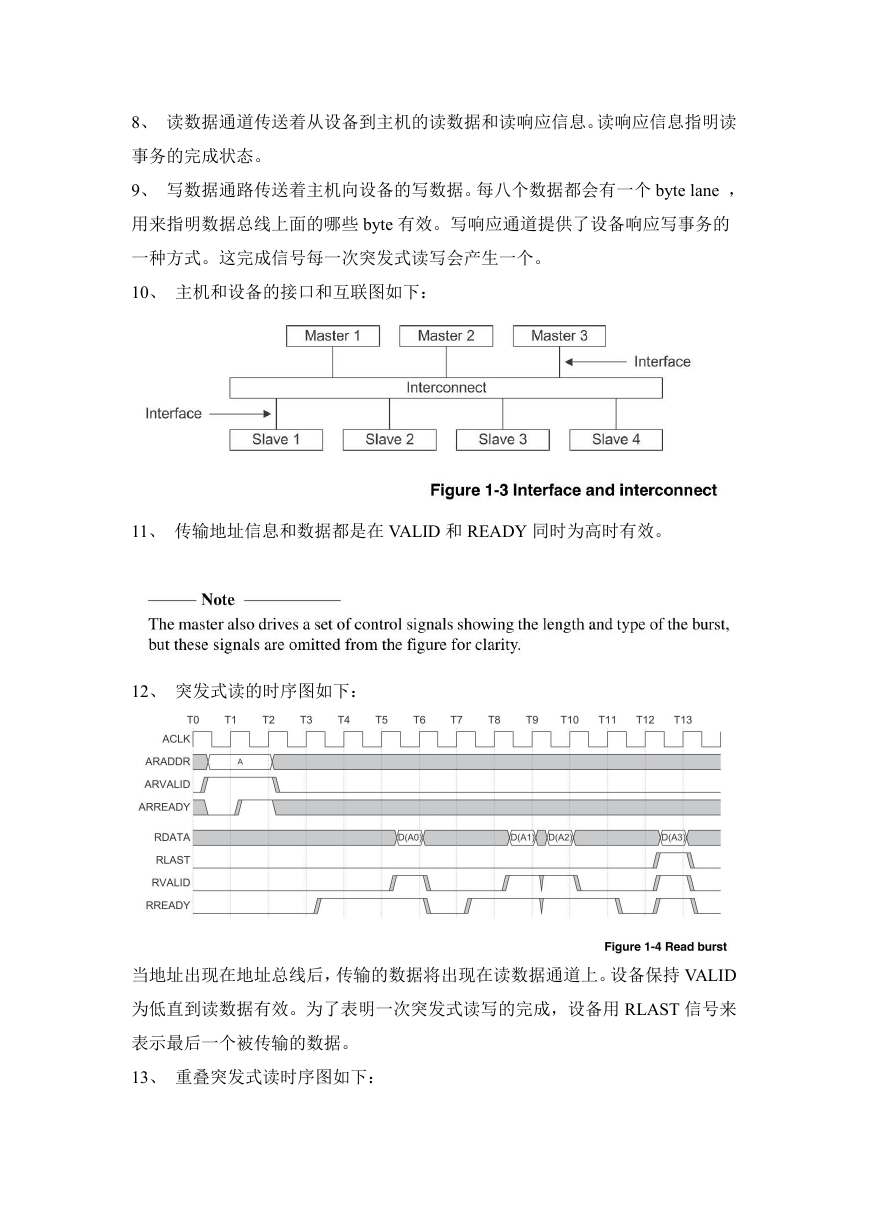

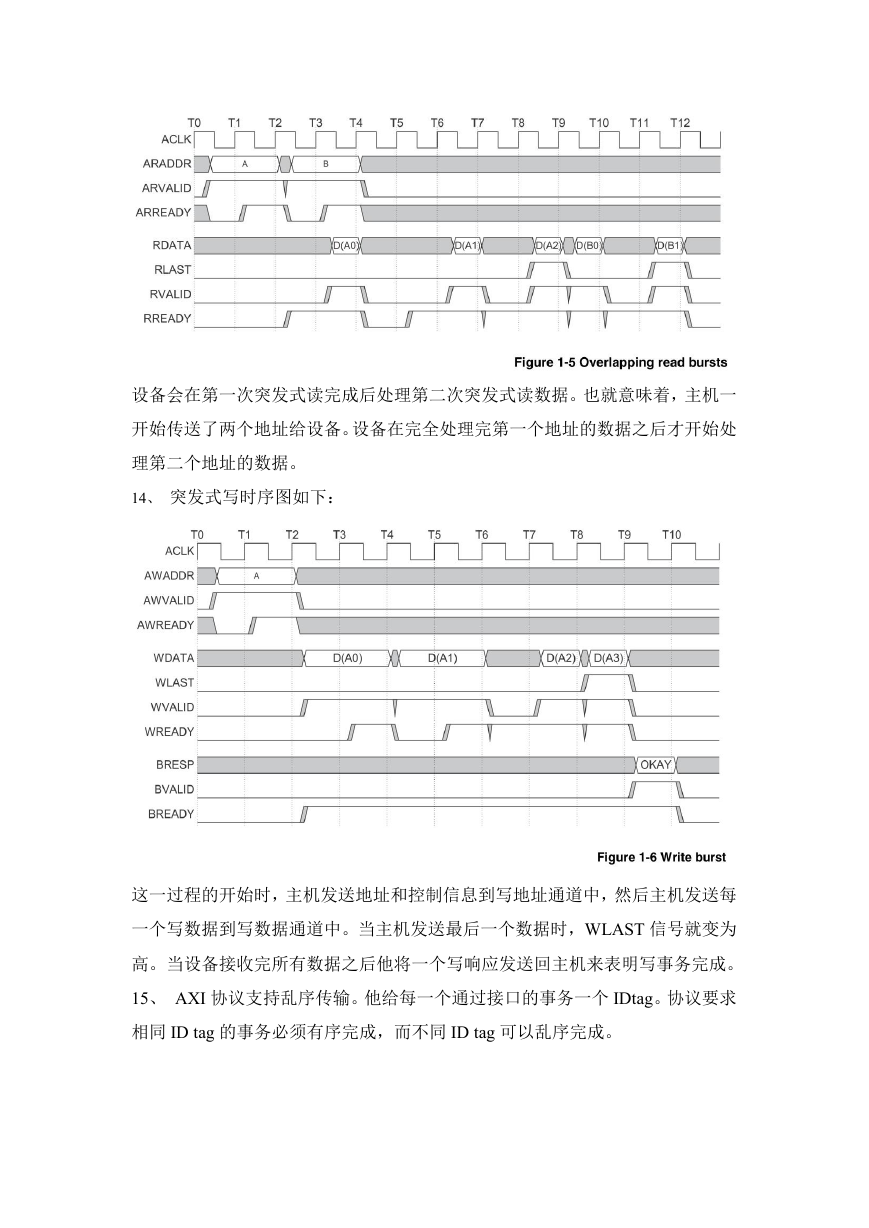

12、 突发式读的时序图如下:

当地址出现在地址总线后,传输的数据将出现在读数据通道上。设备保持 VALID

为低直到读数据有效。为了表明一次突发式读写的完成,设备用 RLAST 信号来

表示最后一个被传输的数据。

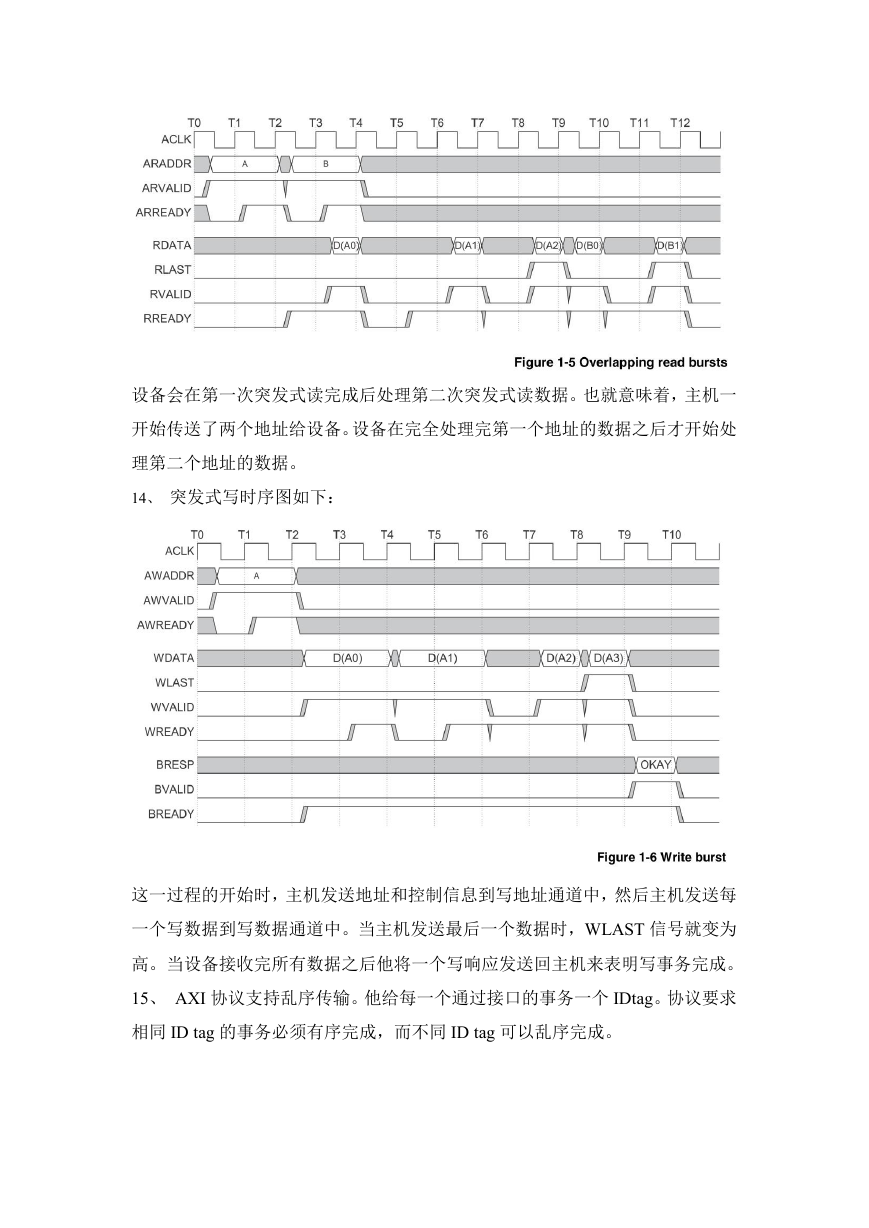

13、 重叠突发式读时序图如下:

�

设备会在第一次突发式读完成后处理第二次突发式读数据。也就意味着,主机一

开始传送了两个地址给设备。设备在完全处理完第一个地址的数据之后才开始处

理第二个地址的数据。

14、 突发式写时序图如下:

这一过程的开始时,主机发送地址和控制信息到写地址通道中,然后主机发送每

一个写数据到写数据通道中。当主机发送最后一个数据时,WLAST 信号就变为

高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。

15、 AXI 协议支持乱序传输。他给每一个通过接口的事务一个 IDtag。协议要求

相同 ID tag 的事务必须有序完成,而不同 ID tag 可以乱序完成。

�

第二章

本章主要介绍一些信号描述,其中包括全局信号、写地址通道信号、写数据

通道信号、写响应通道信号、读地址通道信号、读数据通道信号、低功耗接口信

号。本章的所有表都是以 32 位的数据总线、4 位的写数据闸门、4 位的 ID 段。

1、全局信号

信号

源

描述

ACLK

ARESETn

2、写地址通道信号

Clock source

Reset source

信号

源

描述

全局时钟信号

全局复位信号,低电平有效

主机 写地址 ID,这个信号是写地址信号组的 ID tag。

AWID[3:0]

AWADDR[31:0] 主机 写地址。

AWLEN[3:0]

主机 突发式写的长度。此长度决定突发式写所传输的数据的

个数。

主机 突发式写的大小。

AWSIZE[2:0]

AWBURST[1:0] 主机 突发式写的类型。

AWLOCK[1:0] 主机 锁类型。

AWCACHE[3:0] 主机 Cache 类型。这信号指明事务的 bufferable、cacheable、

write-through、write-back、allocate attributes 信息。

AWPROT[2:0] 主机 保护类型。

AWVALID

主机 写地址有效。

1 = 地址和控制信息有效

0 = 地址和控制信息无效

这个信号会一直保持,直到 AWREADY 变为高。

AWREADY

设备 写地址准备好。这个信号用来指明设备已经准备好接受

地址和控制信息了。

1 = 设备准备好

0 = 设备没准备好

�

3、写数据通道信号

信号

源

描述

主机 写 ID tag,WID 的值必须与 AWID 的值匹配

WID[3:0]

WDATA[31:0] 主机 写的数据。

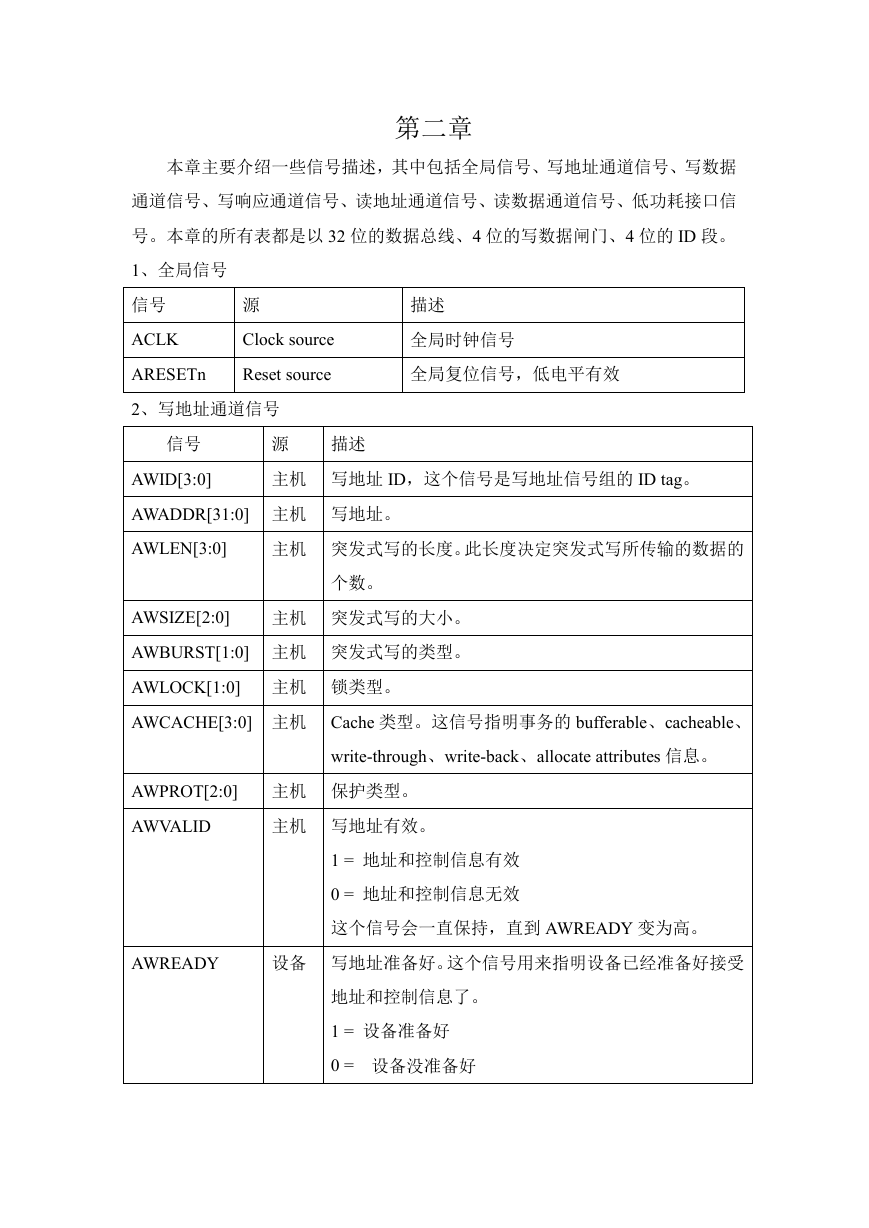

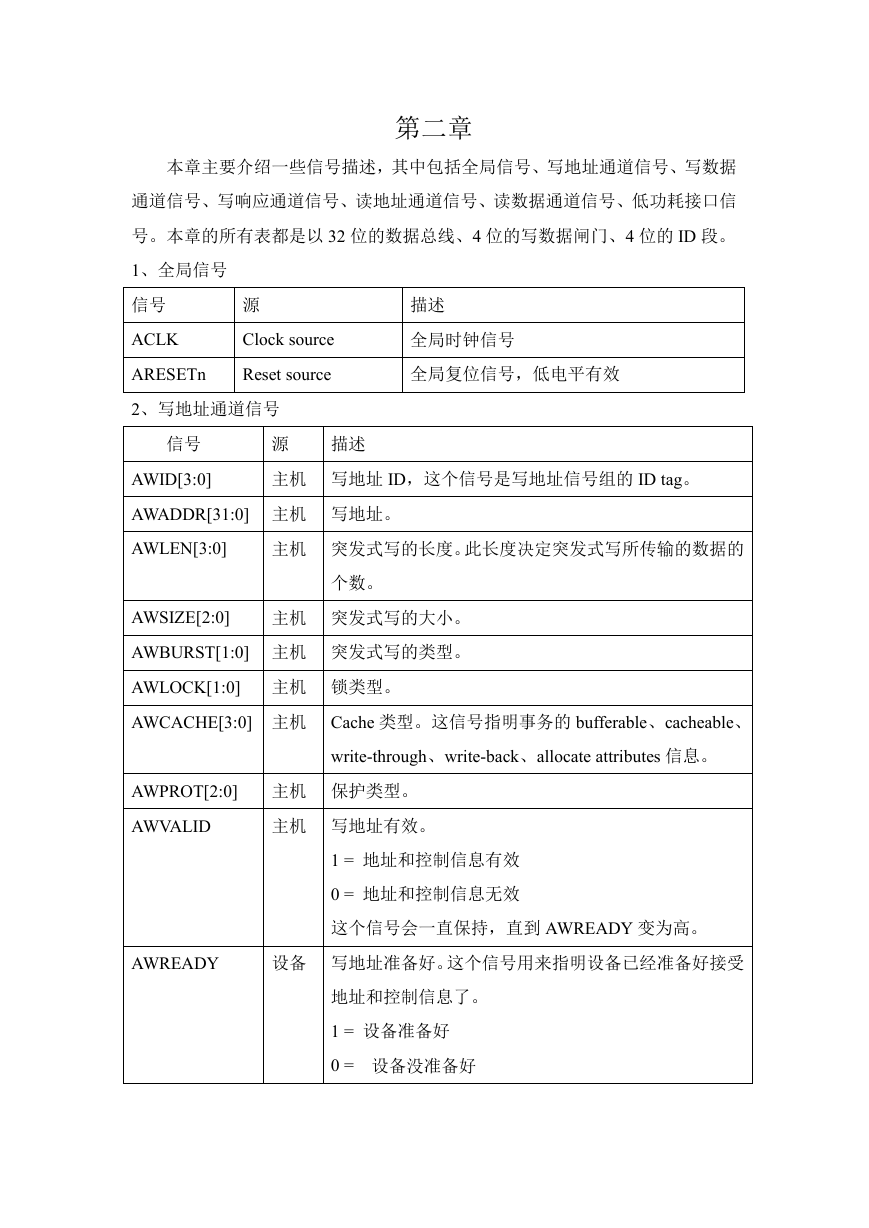

WSTRB[3:0] 主机 写阀门。WSTRB[n]标示的区间为 WDATA[(8*n)+7:(8*n)]

WLAST

WVALID

主机 写的最后一个数据。

主机 写有效

1 = 写数据和阀门有效

0 = 写数据和阀门无效

WREADY

设备 写就绪。指明设备已经准备好接受数据了

1 = 设备就绪

0 = 设备未就绪

4、写响应通道信号

信号

源

描述

BID[3:0]

BRESP[1:0] 设备 写响应。这个信号指明写事务的状态。可能有的响应:

设备 响应 ID , 这个数值必须与 AWID 的数值匹配。

OKAY、EXOKAY、SLVERR、DECERR。

BVALID

设备 写响应有效。

1 = 写响应有效

0 = 写响应无效

BREADY

主机 接受响应就绪。该信号表示主机已经能够接受响应信息。

1 = 主机就绪

0 = 主机未就绪

�

5、读地址通道信号

信号

源

描述

主机 读地址 ID。

ARID[3:0]

ARADDR[31:0] 主机 读地址。

ARLEN[3:0]

ARSIZE[2:0]

ARBURST[1:0] 主机 突发式读类型。

ARLOCK[1:0] 主机 锁类型。

ARCACHE[3:0] 主机 Cache 类型。

ARPROT[2:0] 主机 保护类型。

ARVALID

主机 突发式读长度。

主机 突发式读大小。

主机 读地址有效。信号一直保持,直到 ARREADY 为高。

1 = 地址和控制信息有效

0 = 地址和控制信息无效

ARREADY

设备 读地址就绪。指明设备已经准备好接受数据了。

1 = 设备就绪

0 = 设备未就绪

6、读数据通道信号

信号

源

描述

RID[3:0]

RDATA[31:0]

RRESP[1:0]

RLAST

RVALID

设备 读 ID tag。RID 的数值必须与 ARID 的数值匹配。

设备 读数据。

设备 读响应。这个信号指明读传输的状态:OKAY、

EXOKAY、SLVERR、DECERR。

设备 读事务传送的最后一个数据。

设备 读数据有效。

1 = 读数据有效。

0 = 读数据无效。

�

RREADY

主机 读数据就绪。

1 = 主机就绪

0 = 主机未就绪

7、低功耗接口信号

信号

源

描述

CSYSREQ CLOCK controller

系统低功耗请求。此信号来自系统时钟控制

CSYSACK 外围设备

CACTIVE 外围设备

器,使外围设备进入低功耗状态。

低功耗请求应答。

Clock active

1 = 外围设备时钟请求

0 = 外围设备时钟无请求

第三章

本章介绍主机/设备之间的握手过程以及 READY 和 VALD 握手信号的关系

以及默认值。

1、全部 5 个通道使用相同的 VALID/READY 握手机制传输数据及控制信息。传

输源产生 VLAID 信号来指明何时数据或控制信息有效。而目地源产生 READY

信号来指明已经准备好接受数据或控制信息。传输发生在 VALID 和 READY 信

号同时为高的时候。VALID 和 READY 信号的出现有三种关系。

(1) VALID 先变高 READY 后变高。时序图如下:

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc