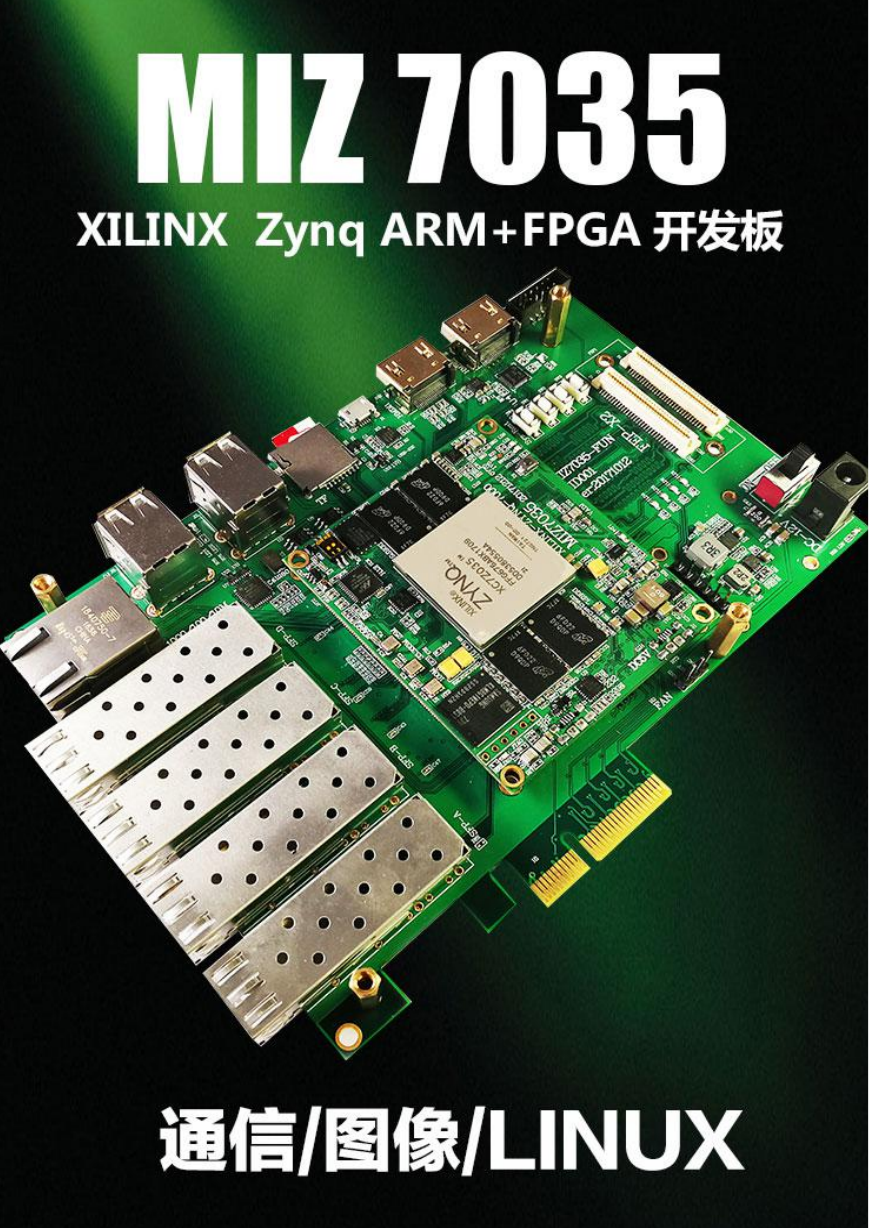

ZYNQ FPGA 修炼秘籍

目录

【第二季】MIZ7035高速通信以及MIG控制器使用

S09_CH01 PCIE_PIO Demo 的分析和测试

1.1基于PCIE IP CORE设计

1.1.1基于64bit的PCIE事务层接口

1.1.2基本的TLP传输类型

1.1.3 TLP FPGA发送端(FPGA应答主机的TLP包)

1.1.3.1 写请求TLP 3-DW 头不带数据

1.1.3.2 写请求TLP 4-DW 头不带数据

1.1.3.3 写请求TLP 3-DW 头带数据

1.1.3.4 写请求TLP 4-DW 头带数据

1.1.3.5 写请求TLP 背靠背传输

1.1.3.6 写请求节流传输(控制s_axis_tx_tvalid)

1.1.3.7 写请求节流传输(控制s_axis_tx_tready)

1.1.3.8 TLP数据在发送端断开传输

1.1.3.9 TLP包被接收方丢弃

1.1.3.10 AXI4-Stream 接口中毒的数据包

1.1.3.11 流模式事务在传输接口上

1.1.3.12 生成ECRC

1.1.4 TLP FPGA接收端(FPGA接收主机的TLP包)

1.1.4.1读请求TLP 3-DW 头不带数据

1.1.4.2读请求TLP 4-DW 头不带数据

1.1.4.3读请求TLP 3-DW 头带数据

1.1.4.4读请求TLP 4-DW 头带数据

1.1.4.5读请求节流传输

1.1.4.6读请求数据连续传输

1.1.4.7读请求背靠背的节流传输

1.1.4.8数据包在接收接口重新排序

1.1.4.9 EP和TD 在64BIT AXI4-Stream接口

1.1.4.10 ECRC错误的情况在接收的64bit数据接口上

1.1.4.11 分组基地址寄存器在AXI4-Stream接口命中

1.1.4.12 AXI4-Stream接收接口在Link-Down事件的包传输

1.1.5 还有很多未翻译的内容说明

1.2 创建PCIE工程

1.3源码分析

1.3.1 PIO_EP_MEM_ACCESS.v

1.3.2 EP_MEN.V

1.3.3 PIO_RX_ENGINE.V

1.3.4 PIO_TX_ENGINE.V

1.4 仿真部分

1.5 添加在线逻辑分析分析数据

1.6编译并且下载

1.7安装windriver及开发板驱动

1.7.1 Windriver安装及使用

1.8测试

1.9 本章节文件夹内容

S09_CH02 PCIE DMA传输设计(64BIT总线)

2.1 PCIE DMA 硬件代码设计

2.1.1 提供的FPGA工程

2.1.2读内存、写内存的概念

2.1.3基于BMD的总线验证设计架构

2.2 PCIE PC软件设计

2.2.1驱动代码分析

2.2.2DMA相关函数源码分析

2.2.3运行程序

2.3下载并调试

2.4 PCIE DMA性能测试

2.4.1增加测速代码

2.4.2 DMA读存储器测试 64bit

2.4.3 DMA写存储器测试 64bit

2.4.4 DMA读存储器测试 128bit

2.4.5 DMA写存储器测试 128bit

2.5本章节文件夹内容

S09_CH03 MFC 上位机编写

3.1概述

3.2 上位机代码

3.2.1 上位机界面设计

3.2.2 根据PCIE的设备ID打开设备

3.3.3 启动读传输

3.3.4启动写传输

3.3.5 线程函数

3.3.6 计算速度的函数

3.3.7 中断的回调函数

3.3.8 关闭软件的时候关闭设备

3.3 测试结果

3.3.1 64bit 总线速度测试

3.3.2 128bit 总线速度测试

3.4 本章节文件夹内容

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc