搭建 SOPC 流程

1.cpu_0:

Component Library->Nios II Processor->Nios II/f( Reset Vector:Memory:cfi_flash_0,Exce

ption Vector: Memory:sdram_0,括号里的一会儿才能添加)->Next->Instrction Cache:4Kbytes,

Data Cache:2Kbytes->Next->Next->Next->Level 1->Next->Finish

2.tri_state_bridge_0:

Bridges and Adapters->Memory Mapped->Avalon-MM Tristate Bridge->Finish(一会儿还

要添加东西,在最后一个步骤中)

3.cfi_flash_0:

Memories and Memory Controlers->Flash->Flash Memory Interface(CFI)->Presets:Custo

m,Address Width(bits):22,Data Width(bits):8->Next->Setup:40,Wait:160,Hold:40,Units:ns->Finis

h.

4.sdram_0:

Memories and Memory Controlers->SDRAM->SDRAM Controller->Presets:Custom,Data

width Bits:16,Architecture Chip select:1,Banks:4,Address widths Row:12,Column:8->保持默认

->Finish

5. 设置 Reset Vector:Memory:

现在双击 cpu_0(第一个建的模块名字),设置 Reset Vector:Memory:cfi_flash_0,Exception

Vector: Memory:sdram_0->Finish

�

6.epce_flash_controller:

Memories and Memory Controlers->Flash->EPCS Serial Flash Controller->(保持默认)Fini

sh.单击刚建好的 epce_flash_controller_0,按快捷键 Ctrl+R,重命名为 epce_flash_controller.

7.jtag_uart_0:

Interface Protocols->Serial->JTAG UART->(保持默认)Finish.

8.uart_0:

Interface Protocols->Serial->UART(RS-232 Serial Port)->(保持默认)Finish.

9.timer_0:

Peripherals->Microcontrolle Peripherals->Interval Timer->(保持默认)Finish.

10.timer_1:

Peripherals->Microcontrolle Peripherals->Interval Timer->(保持默认)Finish.

11.解决错误

现在有两个错误,分别是:

Error: cpu_0.instruction_master: cpu_0.jtag_debug_module (0x800..0xfff) overlaps cfi_fl

ash_0.s1 (0x0..0x3fffff)

Error: cpu_0.data_master: cpu_0.jtag_debug_module (0x800..0xfff) overlaps cfi_flash_0.

s1 (0x0..0x3fffff)//具体操作中,错误可能不完全相同,但是都是地址冲突类型的错误。

重新分配 Address:菜单栏中的 System->Auto-Assign Base Address

�

重新分配 IRQ:菜单栏中的 System->Auto-Assign IRQs

12.lcd_16207_0:

Peripherals->Display->Character LCD->(保持默认)Finish.选中刚建好的 lcd_0,按快捷键 Ct

rl+R 重命名为 lcd_16207_0.

13.led_red:

Peripherals->Microcontroller Peripherals->PIO(Parallel I/O)->Width(1-32btis):18,Direction:

Output ports only,Reset Value:0x0->Next->Next->Next->Finish.选中刚建好的 pio_0,按快捷键

Ctrl+R 重命名为 led_red(PS:这里是设置输出模块,输出的终点是 LEDR 灯).

14.led_green:

Peripherals->Microcontroller Peripherals->PIO(Parallel I/O)->Width(1-32btis):9,Direction:O

utput ports only,Reset Value:0x0->Next->Next->Next->Finish.选中刚建好的 pio_0,按快捷键 C

trl+R 重命名为 led_green(PS:这里是设置输出模块,输出的终点是 LEDG 灯).

15.button_pio:

Peripherals->Microcontroller Peripherals->PIO(Parallel I/O)->Width(1-32btis):4,Direction:In

put ports only->Next->Edge capture register √Synchronously capture,·Falling edge(下降沿),

Interrupt √Generate IRQ,·Edge->Next->Next->Finish.选中刚建好的 pio_0,按快捷键 Ctrl+R

重命名为 button_pio(PS:这里是设置输入模块,输入为四个按键,边缘触发,下降沿有效).

16.switch_pio:

Peripherals->Microcontroller Peripherals->PIO(Parallel I/O)->Width(1-32btis):18,Direction:I

nput ports only->Next->Next->Next->Finish.选中刚建好的 pio_0,按快捷键 Ctrl+R 重命名为 s

witch_pio(PS:这里是设置输入模块,输入为 18 个拨动开关)

�

17.SEG7_Display:

这个是自己建模块,因为系统没有自带。(PS:官方的 demonstration 中已经给了相应的 V

erilog HDL 代码,所以我们需要的工作仅仅是建造新模块,而代码不需要我们写。)

建造的过程如下:

①将 DE2_demonstrations\DE2_SD_Card_Audio 中的 SEG7_LUT.v 和 SEG7_LUT_8.v 复制到

自己工程目录下

②回到 SOPC Builder,File->New component->Next->Add->选择刚才复制到工程目录下的

SEG7_LUT.v 和 SEG7_LUT_8.v 两个文件,添加->这时会提示添加成功的信息:Analyzing SEG7_L

UT.v Completed->Close,这是发现两个文件加入到了列表中,把 SEG7_LUT-8 后面的 Top 点上,

这时候会提示成功信息 Analyzing SEG7_LUT_8.v Completed,老样子,Close->Next 设置输入

/输出信号,使七段数码管控制器的输入/输出信号与 Avalon 总线信号匹配。具体配置看下图

->Next->Associated Clock:clock_sink(PS:此时下方不会出现任何错误)->Next->Group:DE2

User Logic->Finish->Yes,save.这时会回到 SOPC Builder 界面,在左面发现多了一个 DE2 User

Logic,里面有 SEG7_LUT_8,双击 SEG7_LUT_8,Finish,这时会添加 SEG7_LUT_8_0,选中新添

加的 SEG7_LUT_8_0,按快捷键 Ctrl+R,重命名为 SEG7_Display.

�

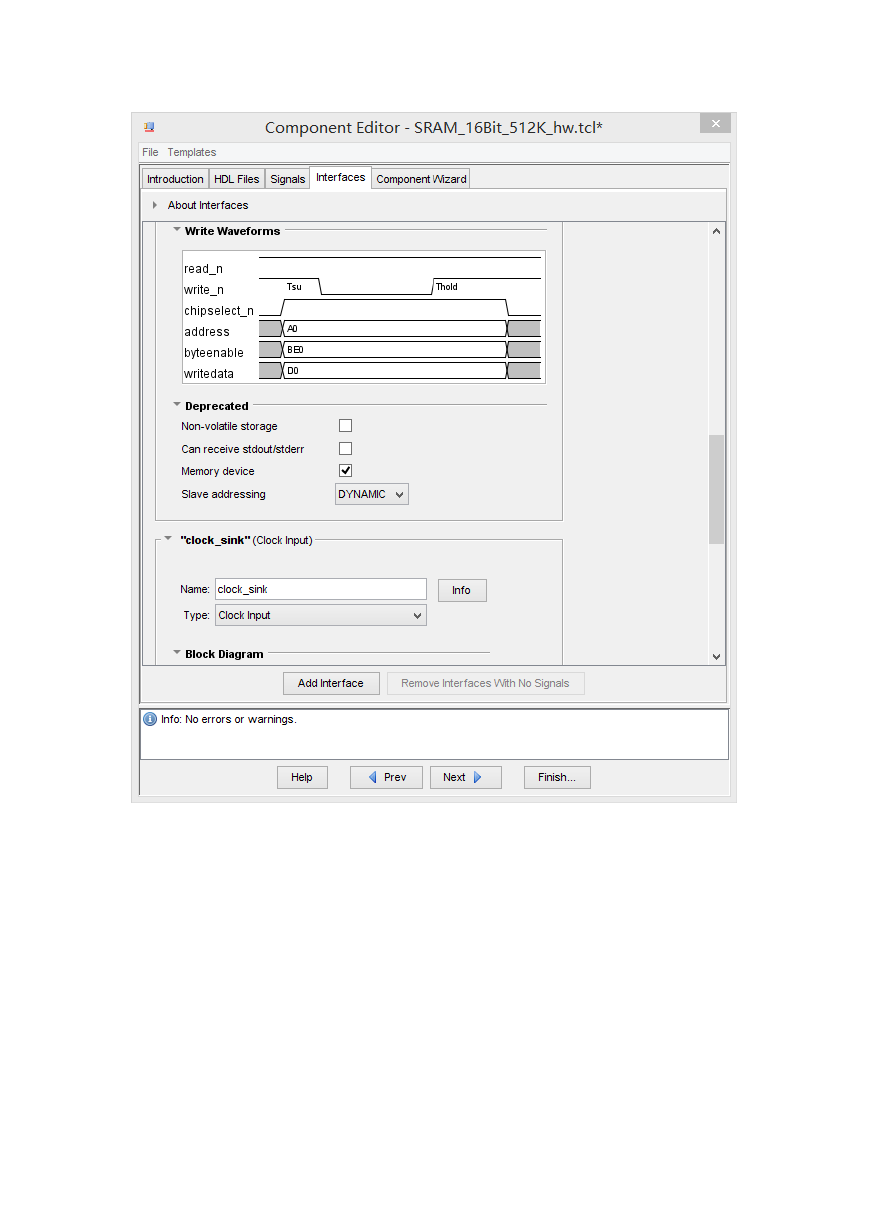

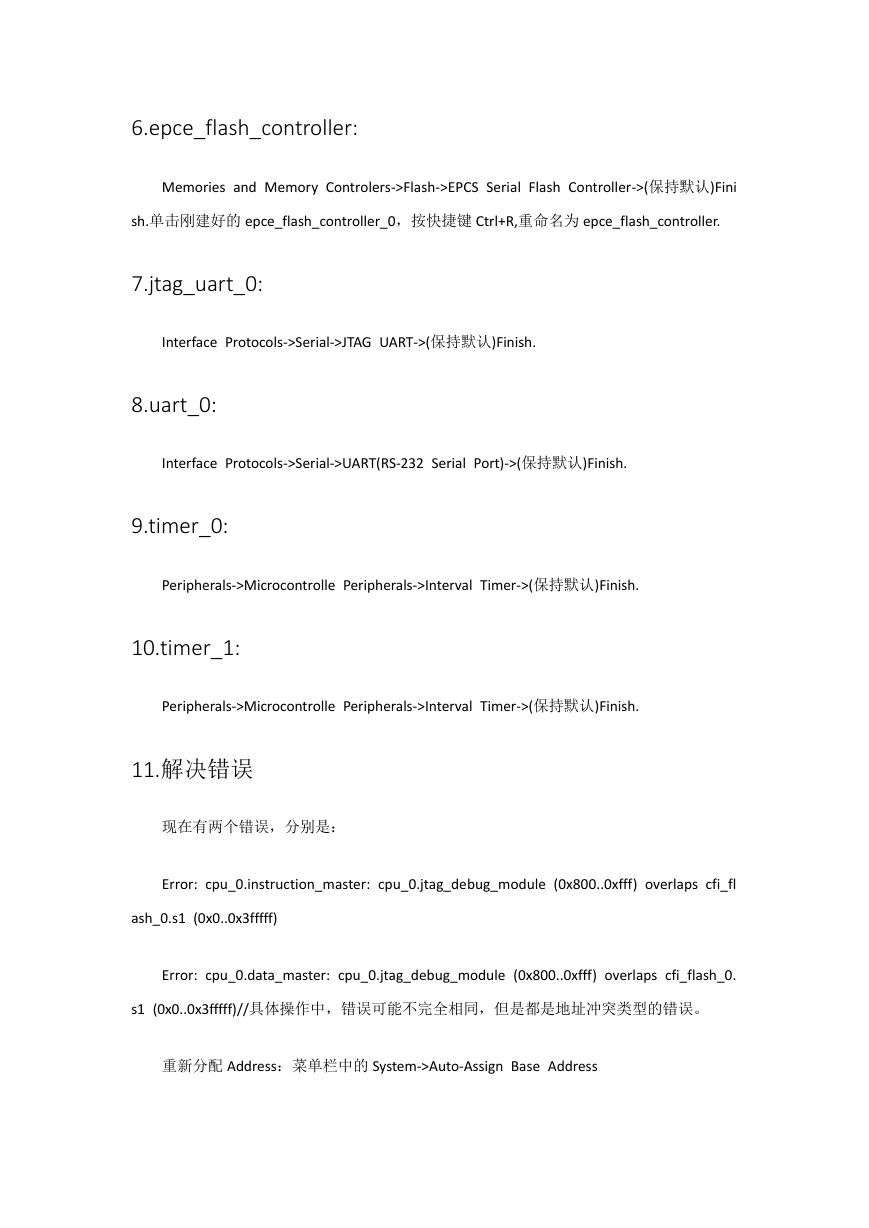

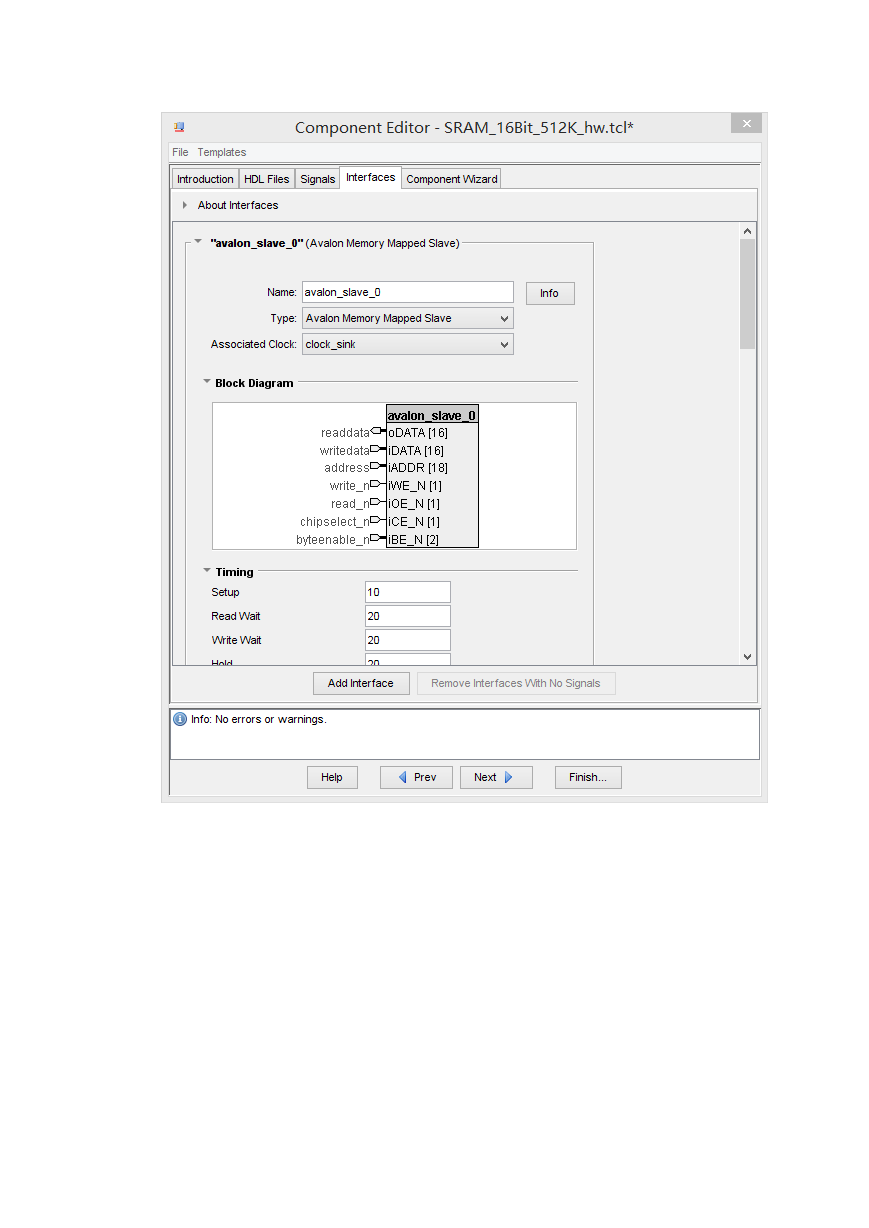

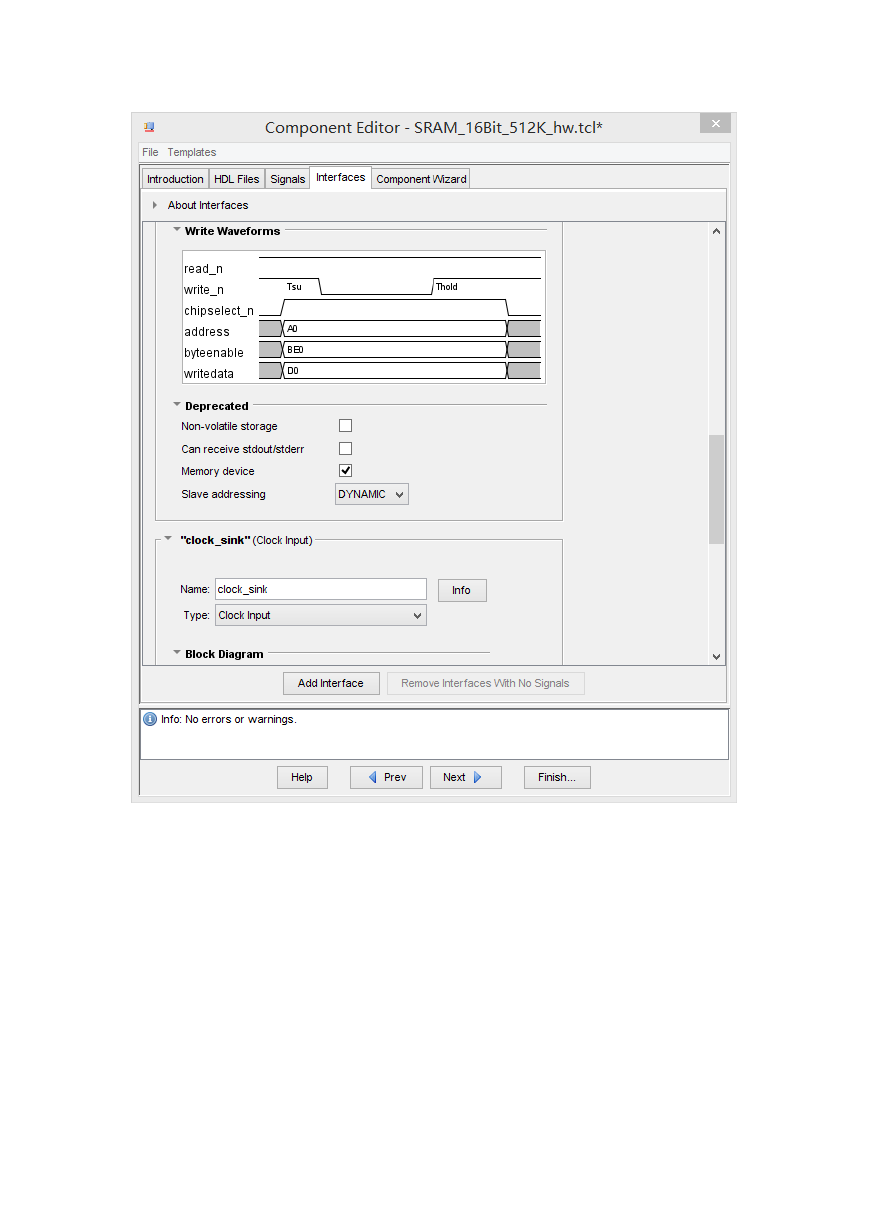

18.sram_0:

这一步和上一步类似

①将 DE2_demonstrations\DE2_SD_Card_Audio 中的 SRAM_16Bit_512K.v 复制到自己工程

目录下

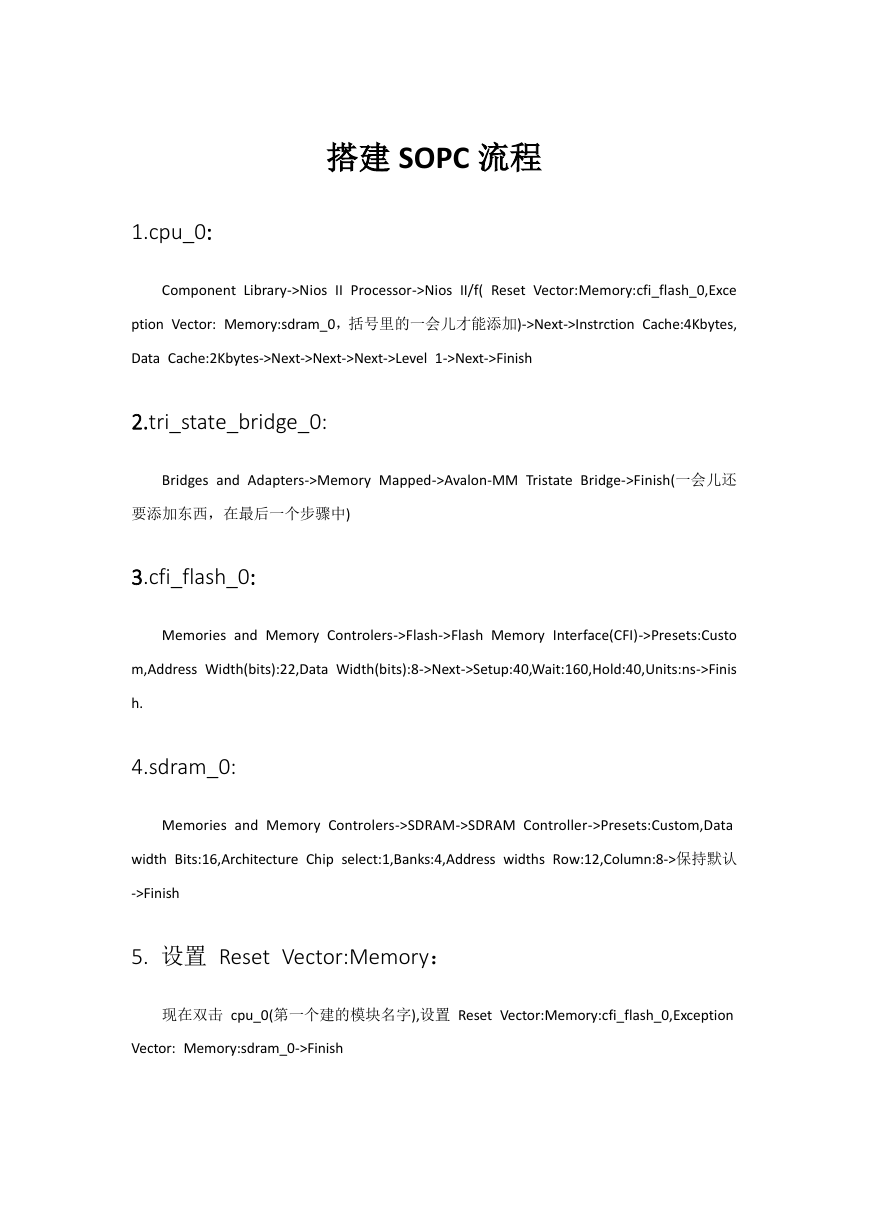

②回到 SOPC Builder,File->New component->Next->Add->选择刚才复制到工程目录下的

SRAM_16Bit_512K.v 文件,添加->这时会提示添加成功的信息:Analyzing SRAM_16Bit_512K.v

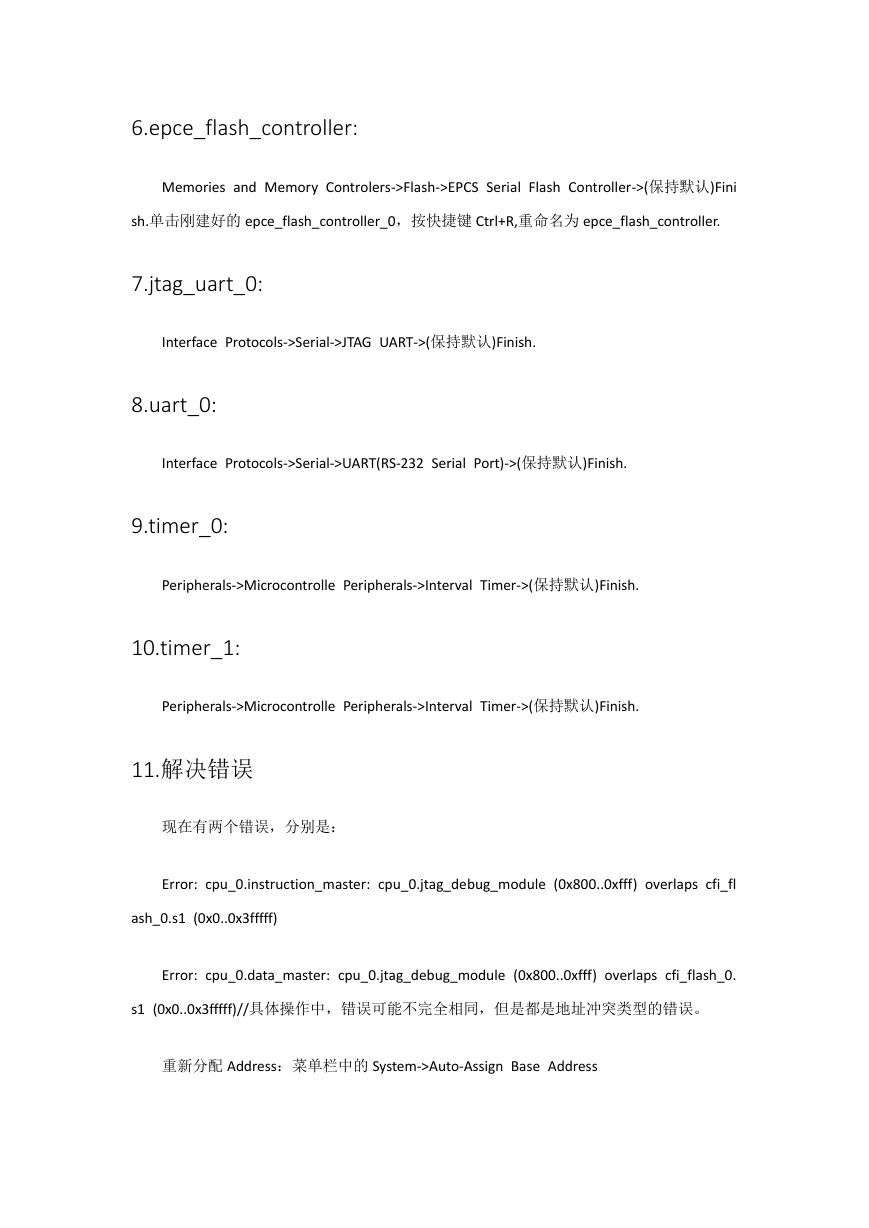

Completed->Close->Next->设置信号的格式,具体配置看下图

见 SRAM_16Bit_512K_Signals.png->Next->详细设置见下图

�

�

�

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc