Cover

Title Page

Copyright Page

PREFACE

Acknowledgments

CONTENTS

CHAPTER 1 Introductory Concepts

1-1 Digital and Analog Quantities

1-2 Binary Digits, Logic Levels, and Digital Waveforms

1-3 Basic Logic Functions

1-4 Combinational and Sequential Logic Functions

1-5 Introduction to Programmable Logic

1-6 Fixed-Function Logic Devices

1-7 Test and Measurement Instruments

1-8 Introduction to Troubleshooting

CHAPTER 2 Number Systems, Operations, and Codes

2-1 Decimal Numbers

2-2 Binary Numbers

2-3 Decimal-to-Binary Conversion

2-4 Binary Arithmetic

2-5 Complements of Binary Numbers

2-6 Signed Numbers

2-7 Arithmetic Operations with Signed Numbers

2-8 Hexadecimal Numbers

2-9 Octal Numbers

2-10 Binary Coded Decimal (BCD)

2-11 Digital Codes

2-12 Error Codes

CHAPTER 3 Logic Gates

3-1 The Inverter

3-2 The AND Gate

3-3 The OR Gate

3-4 The NAND Gate

3-5 The NOR Gate

3-6 The Exclusive-OR and Exclusive-NOR Gates

3-7 Programmable Logic

3-8 Fixed-Function Logic Gates

3-9 Troubleshooting

CHAPTER 4 Boolean Algebra and Logic Simplification

4-1 Boolean Operations and Expressions

4-2 Laws and Rules of Boolean Algebra

4-3 DeMorgan's Theorems

4-4 Boolean Analysis of Logic Circuits

4-5 Logic Simplification Using Boolean Algebra

4-6 Standard Forms of Boolean Expressions

4-7 Boolean Expressions and Truth Tables

4-8 The Karnaugh Map

4-9 Karnaugh Map SOP Minimization

4-10 Karnaugh Map POS Minimization

4-11 The Quine-McCluskey Method

4-12 Boolean Expressions with VHDL

Applied Logic

CHAPTER 5 Combinational Logic Analysis

5-1 Basic Combinational Logic Circuits

5-2 Implementing Combinational Logic

5-3 The Universal Property of NAND and NOR gates

5-4 Combinational Logic Using NAND and NOR Gates

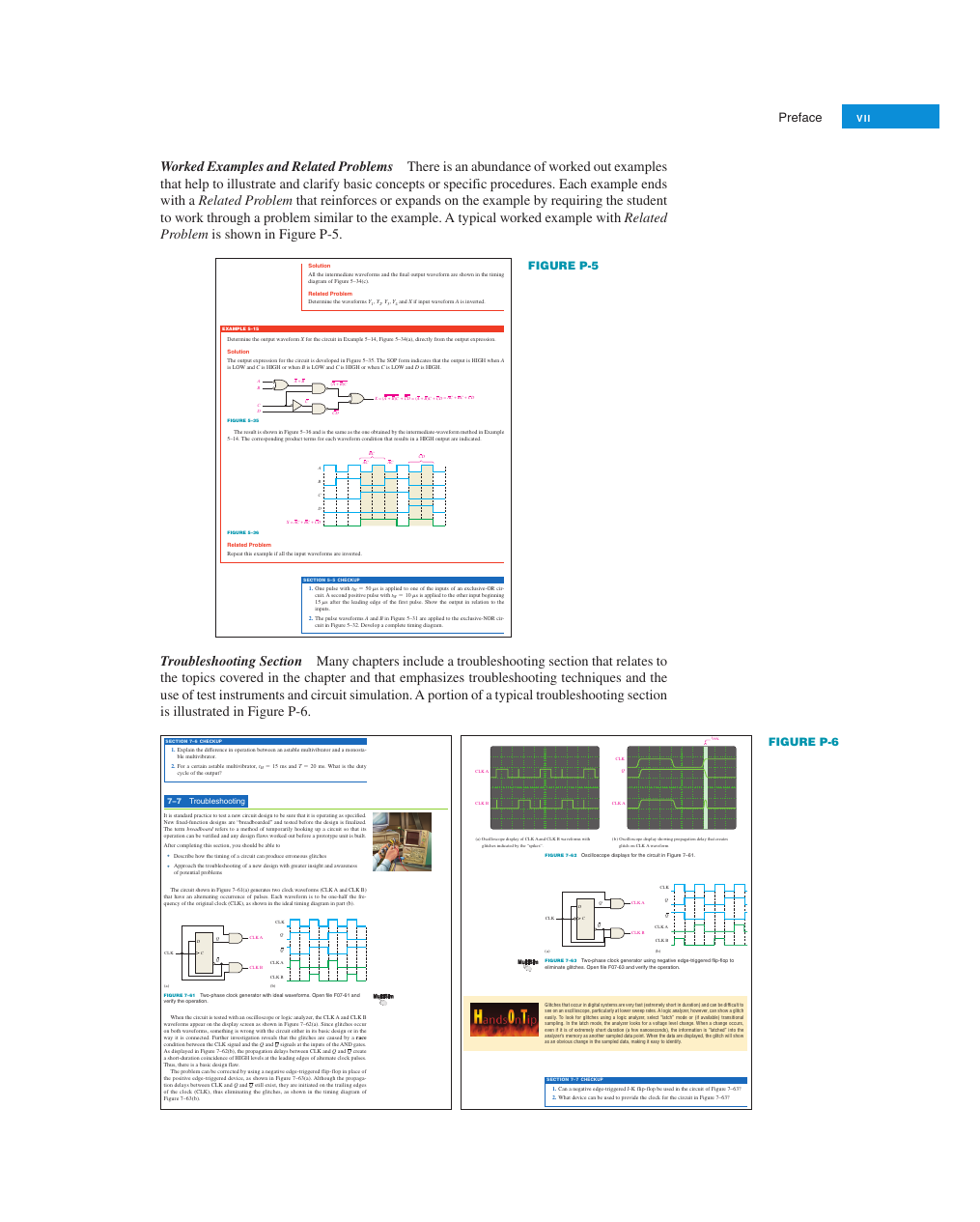

5-5 Pulse Waveform Operation

5-6 Combinational Logic with VHDL

5-7 Troubleshooting

Applied Logic

CHAPTER 6 Functions of Combinational Logic

6-1 Half and Full Adders

6-2 Parallel Binary Adders

6-3 Ripple Carry and Look-Ahead Carry Adders

6-4 Comparators

6-5 Decoders

6-6 Encoders

6-7 Code Converters

6-8 Multiplexers (Data Selectors)

6-9 Demultiplexers

6-10 Parity Generators/Checkers

6-11 Troubleshooting

Applied Logic

CHAPTER 7 Latches, Flip-Flops, and Timers

7-1 Latches

7-2 Flip-Flops

7-3 Flip-Flop Operating Characteristics

7-4 Flip-Flop Applications

7-5 One-Shots

7-6 The Astable Multivibrator

7-7 Troubleshooting

Applied Logic

CHAPTER 8 Shift Registers

8-1 Shift Register Operations

8-2 Types of Shift Register Data I/Os

8-3 Bidirectional Shift Registers

8-4 Shift Register Counters

8-5 Shift Register Applications

8-6 Logic Symbols with Dependency Notation

8-7 Troubleshooting

Applied Logic

CHAPTER 9 Counters

9-1 Finite State Machines

9-2 Asynchronous Counters

9-3 Synchronous Counters

9-4 Up/Down Synchronous Counters

9-5 Design of Synchronous Counters

9-6 Cascaded Counters

9-7 Counter Decoding

9-8 Counter Applications

9-9 Logic Symbols with Dependency Notation

9-10 Troubleshooting

Applied Logic

CHAPTER 10 Programmable Logic

10-1 Simple Programmable Logic Devices (SPLDs)

10-2 Complex Programmable Logic Devices (CPLDs)

10-3 Macrocell Modes

10-4 Field-Programmable Gate Arrays (FPGAs)

10-5 Programmable Logic software

10-6 Boundary Scan Logic

10-7 Troubleshooting

Applied Logic

CHAPTER 11 Data Storage

11-1 Semiconductor Memory Basics

11-2 The Random-Access Memory (RAM)

11-3 The Read-Only Memory (ROM)

11-4 Programmable ROMs

11-5 The Flash Memory

11-6 Memory Expansion

11-7 Special Types of Memories

11-8 Magnetic and Optical Storage

11-9 Memory Hierarchy

11-10 Cloud Storage

11-11 Troubleshooting

CHAPTER 12 Signal Conversion and Processing

12-1 Analog-to-Digital Conversion

12-2 Methods of Analog-to-Digital Conversion

12-3 Methods of Digital-to-Analog Conversion

12-4 Digital Signal Processing

12-5 The Digital Signal Processor (DSP)

CHAPTER 13 Data Transmission

13-1 Data Transmission Media

13-2 Methods and Modes of Data Transmission

13-3 Modulation of Analog Signals with Digital Data

13-4 Modulation of Digital Signals with Analog Data

13-5 Multiplexing and Demultiplexing

13-6 Bus Basics

13-7 Parallel Buses

13-8 The Universal Serial Bus (USB)

13-9 Other Serial Buses

13-10 Bus Interfacing

CHAPTER 14 Data Processing and Control

14-1 The Computer System

14-2 Practical Computer System Considerations

14-3 The Processor: Basic Operation

14-4 The Processor: Addressing Modes

14-5 The Processor: Special Operations

14-6 Operating Systems and Hardware

14-7 Programming

14-8 Microcontrollers and Embedded Systems

14-9 System on Chip (SoC)

ANSWERS TO ODD-NUMBERED PROBLEMS

GLOSSARY

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

R

S

T

U

V

W

Z

INDEX

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

R

S

T

U

V

W

X

Z

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc