�

Verilog:

Frequently

Asked

Questions

Shivakumar Chonnad

Needamangalam Balachander

Verilog:

Frequently

Asked

Questions

Language, Applications and

Extensions

Springer

�

eBook ISBN:

Print ISBN:

0-387-22899-3

0-387-22834-9

©2004 Springer Science + Business Media, Inc.

Print ©2004 Springer Science + Business Media, Inc.

Boston

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic,

mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Springer's eBookstore at:

and the Springer Global Website Online at:

http://www.ebooks.kluweronline.com

http://www.springeronline.com

�

To our wives, Manjula Chonnad

and jayanthi Balachander

To our children, Akshata Chonnad,

Puja Balachander, and Manya Balachander

�

Contents

Dedication

Contributing Authors

Foreword

Preface

Acknowledgments

1

BASIC VERILOG

1.1 Assignments

1.1.1

1.1.2

1.1.3

1.1.4

What are the differences between continuous and procedural

assignments?

What are the differences between assignments in initial and

always constructs?

What are the differences between blocking and nonblocking

assignments?

How can I model a bi-directional net with assignments

influencing both source and destination?

v

xvii

xix

xxi

xxvii

1

1

1

2

3

4

�

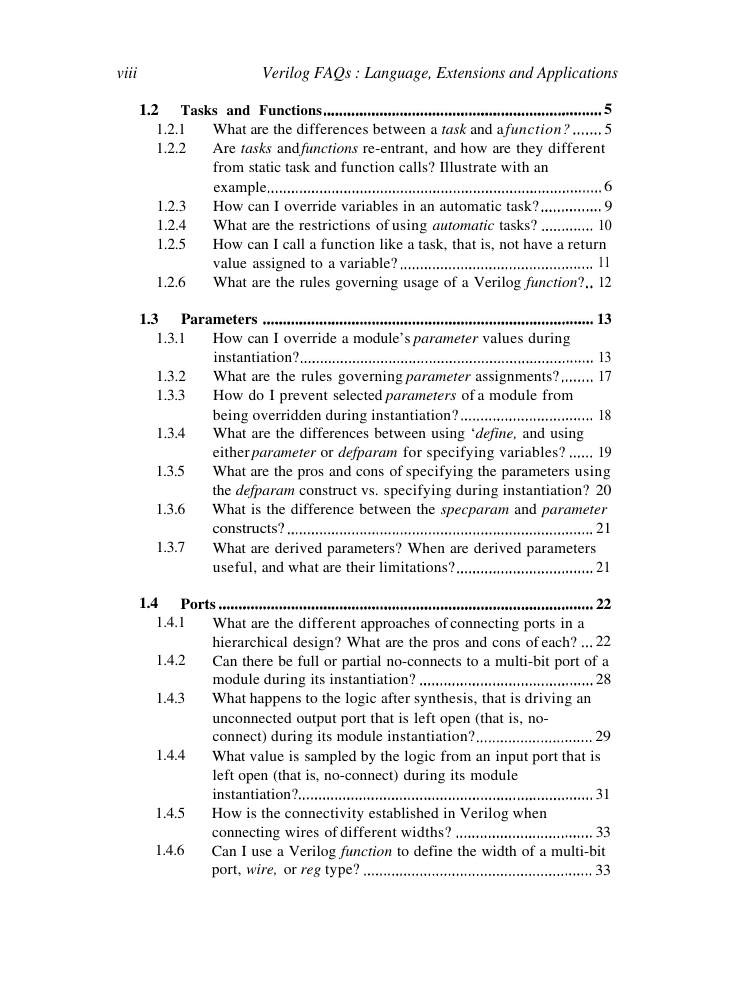

viii

1.2

1.2.1

1.2.2

1.2.3

1.2.4

1.2.5

1.2.6

Verilog FAQs : Language, Extensions and Applications

Tasks and Functions

5

5

What are the differences between a task and a function?

Are tasks and functions re-entrant, and how are they different

from static task and function calls? Illustrate with an

6

example

9

How can I override variables in an automatic task?

10

What are the restrictions of using automatic tasks?

How can I call a function like a task, that is, not have a return

11

value assigned to a variable?

12

What are the rules governing usage of a Verilog function?

1.3

Parameters

13

1.3.1

1.3.2

1.3.3

1.3.4

1.3.5

1.3.6

1.3.7

13

17

How can I override a module’s parameter values during

instantiation?

What are the rules governing parameter assignments?

How do I prevent selected parameters of a module from

being overridden during instantiation?

What are the differences between using ‘define, and using

19

either parameter or defparam for specifying variables?

What are the pros and cons of specifying the parameters using

the defparam construct vs. specifying during instantiation?

20

What is the difference between the specparam and parameter

21

constructs?

What are derived parameters? When are derived parameters

useful, and what are their limitations?

21

18

1.4

Ports

22

1.4.1

1.4.2

1.4.3

1.4.4

1.4.5

1.4.6

What are the different approaches of connecting ports in a

22

hierarchical design? What are the pros and cons of each?

Can there be full or partial no-connects to a multi-bit port of a

module during its instantiation?

28

What happens to the logic after synthesis, that is driving an

unconnected output port that is left open (that is, no-

connect) during its module instantiation?

What value is sampled by the logic from an input port that is

left open (that is, no-connect) during its module

instantiation?

How is the connectivity established in Verilog when

connecting wires of different widths?

33

Can I use a Verilog function to define the width of a multi-bit

port, wire, or reg type?

33

29

31

�

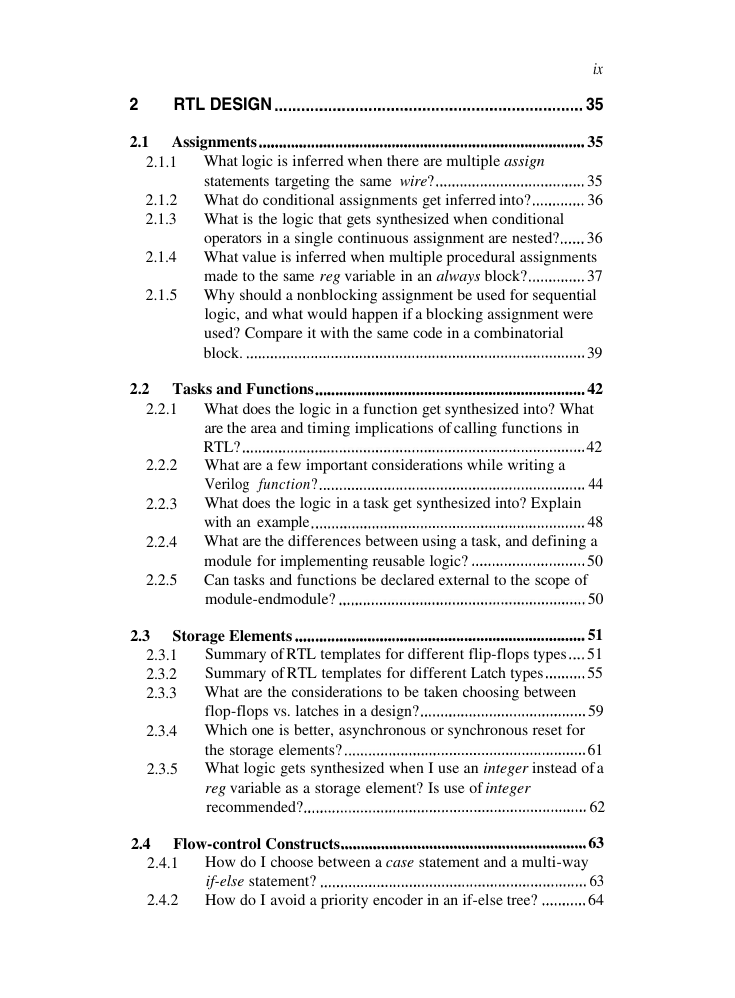

2

RTL DESIGN

2.1

Assignments

ix

35

35

2.1.1

2.1.2

2.1.3

2.1.4

2.1.5

35

36

What logic is inferred when there are multiple assign

statements targeting the same wire?

What do conditional assignments get inferred into?

What is the logic that gets synthesized when conditional

operators in a single continuous assignment are nested?

36

What value is inferred when multiple procedural assignments

made to the same reg variable in an always block?

37

Why should a nonblocking assignment be used for sequential

logic, and what would happen if a blocking assignment were

used? Compare it with the same code in a combinatorial

block.

39

2.2

Tasks and Functions

42

2.2.1

2.2.2

2.2.3

2.2.4

2.2.5

What does the logic in a function get synthesized into? What

are the area and timing implications of calling functions in

RTL?

What are a few important considerations while writing a

Verilog function?

What does the logic in a task get synthesized into? Explain

with an example

48

What are the differences between using a task, and defining a

module for implementing reusable logic?

50

Can tasks and functions be declared external to the scope of

module-endmodule?

42

44

50

2.3

Storage Elements

51

51

55

2.3.1

2.3.2

2.3.3

2.3.4

2.3.5

Summary of RTL templates for different flip-flops types

Summary of RTL templates for different Latch types

What are the considerations to be taken choosing between

flop-flops vs. latches in a design?

Which one is better, asynchronous or synchronous reset for

the storage elements?

61

What logic gets synthesized when I use an integer instead of a

reg variable as a storage element? Is use of integer

recommended?

59

62

2.4

Flow-control Constructs

63

2.4.1

2.4.2

How do I choose between a case statement and a multi-way

if-else statement?

How do I avoid a priority encoder in an if-else tree?

63

64

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc