芯驿电子科技(上海)有限公司

芯驿电子科技(上海)有限公司

021-67676997

www.alinx.cn

www.heijin.org

GTX 光纤通信测试例程

光纤通信测试例程

黑金动力社区 2018-08-13

黑金动力社区

黑金动力社区

黑金动力社区

1 实验简介

Xilinx 的 Kintex-7 系列 FPGA

FPGA 集成了 GTX 串行高速收发器,可以实现高速串行数据通信。在

串行高速收发器,可以实现高速串行数据通信。在

AX7325 开发板上,FPGA 的 GT

GTX 其中的 8 个收发器通道中 4 路连接到 4 路 SFP

SFP 光模块接口, 另外

4 路连接到 QSFP 光模块接口,

光模块接口,用户只需要另外购买 SPF 的光模块就可以实现光纤的数据传输。本

的光模块就可以实现光纤的数据传输。本

实验将介绍通过光纤连接实现光模块之间的数据收发和眼图的测试

将介绍通过光纤连接实现光模块之间的数据收发和眼图的测试。

2 实验原理

2.1 GTX 介绍

AX7325 的 FPGA 芯片(XC7K325TFFG900

XC7K325TFFG900)自带 16 路高速 GTX 串行高速收发器通道,

串行高速收发器通道, 每通道的

收发速度为高达 12.5 Gb/s。GTX

GTX 收发器支持不同的串行传输接口或协议,比如

收发器支持不同的串行传输接口或协议,比如 PCIE 1.1/2.0/3.0 接

口、万兆网 XUAI 接口、OC-48

48、串行 RapidIO 接口、 SATA(Serial ATA) 接口、

接口、数字分量串行接口

(SDI)等等。

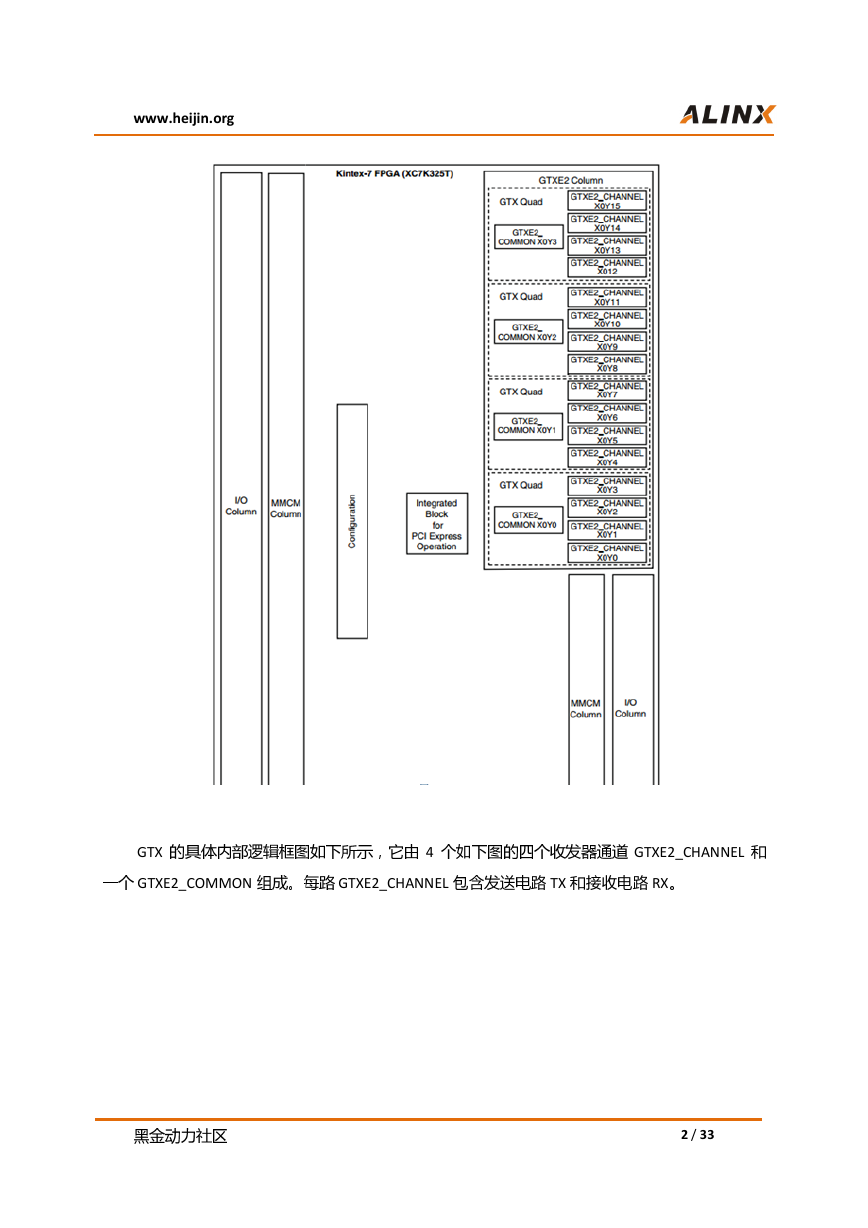

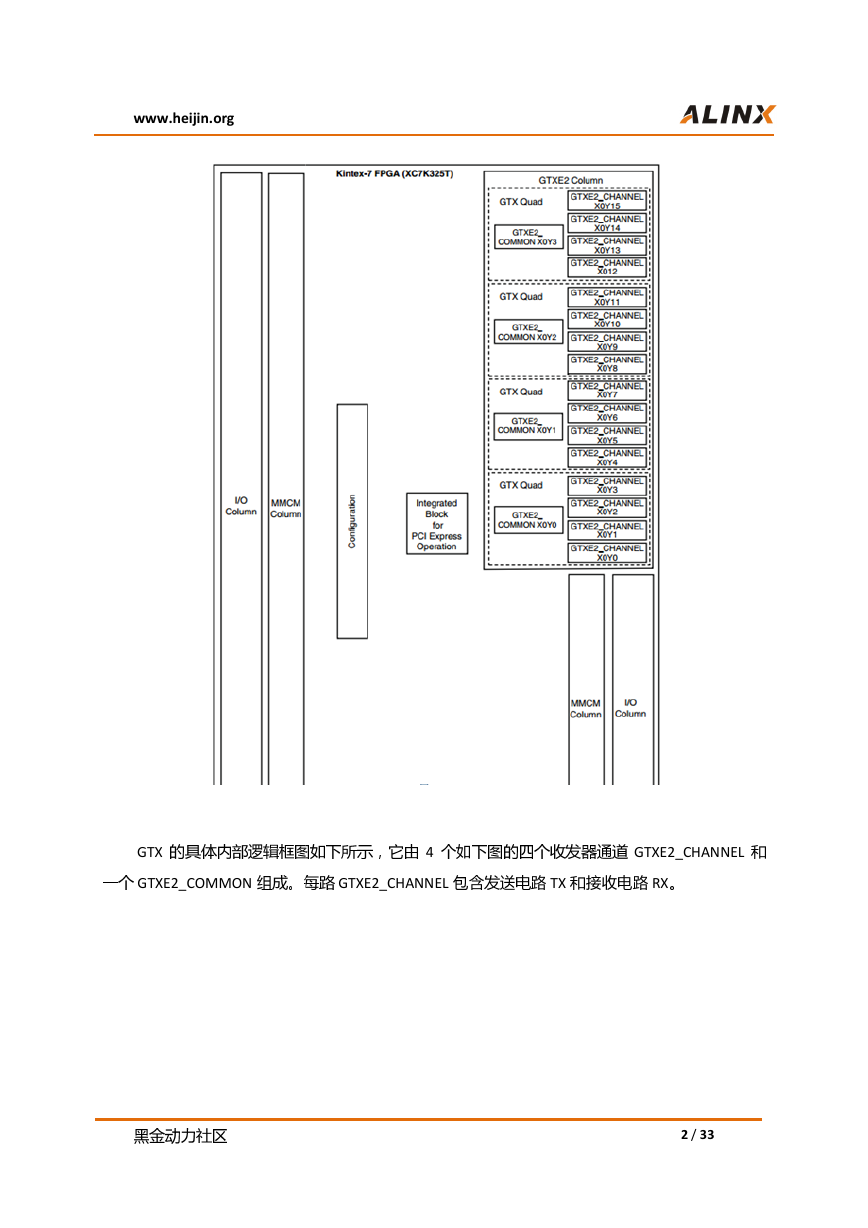

Xilinx 以 Quad 来对串行高速收发器进行分组,四个串行高速收发器和一个

来对串行高速收发器进行分组,四个串行高速收发器和一个 COMMOM(QPLL)

来对串行高速收发器进行分组,四个串行高速收发器和一个

组成一个 Quad,每一个串行高速收发器称为一个

,每一个串行高速收发器称为一个 Channel(通道),下图为

通道),下图为 16 路 GTX 收发器在

Kintex-7 FPGA 芯片中的示意图:

芯片中的示意图:

黑金 FPGA

版权所有

1 / 33

�

www.heijin.org

GTX 的具体内部逻辑框图如下所示,它由

的具体内部逻辑框图如下所示,它由 4 个如下图的四个收发器通道

四个收发器通道 GTXE2_CHANNEL 和

一个 GTXE2_COMMON 组成。每路

组成。每路 GTXE2_CHANNEL 包含发送电路 TX 和接收电路

和接收电路 RX。

黑金动力社区

2 / 33

�

www.heijin.org

每个 GTXE2_CHANNEL 的逻辑电路如下图所示:

的逻辑电路如下图所示:

黑金动力社区

3 / 33

�

www.heijin.org

GTXE2_CHANNEL 的发送端和接收端功能是独立的,均由

的发送端和接收端功能是独立的,均由 PMA(Physical Media Attachment

PMA(Physical Media Attachment,物

理媒介适配层)和 PCS(Physical Coding Sublayer

PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中

两个子层组成。其中 PMA 子层包含

高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。

后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS 子层包含

后加重、接收均衡、时钟发生器及时钟恢复等电路。

8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路。

编解码、缓冲区、通道绑定和时钟修正等电路。

GTX 发送和接收处理流程:

发送和接收处理流程:

首先用户逻辑数据经过 8B/10B

8B/10B 编码后,进入一个发送缓存区(Phase Adjust FIFO

Phase Adjust FIFO),该缓冲

区主要是 PMA 子层和 PCS 子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,

子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,

子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,

最后经过高速 Serdes 进行并串转换

进行并串转换(PISO),有必要的话,可以进行预加重(TX Pre

TX Pre-emphasis)、后加

重。值得一提的是,如果在 PCB

PCB 设计时不慎将 TXP 和 TXN 差分引脚交叉连接,则可以通过极性控

差分引脚交叉连接,则可以通过极性控

制(Polarity)来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需

来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需

来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需

要注意的是 RX 接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。

接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。

GTX 的参考时钟

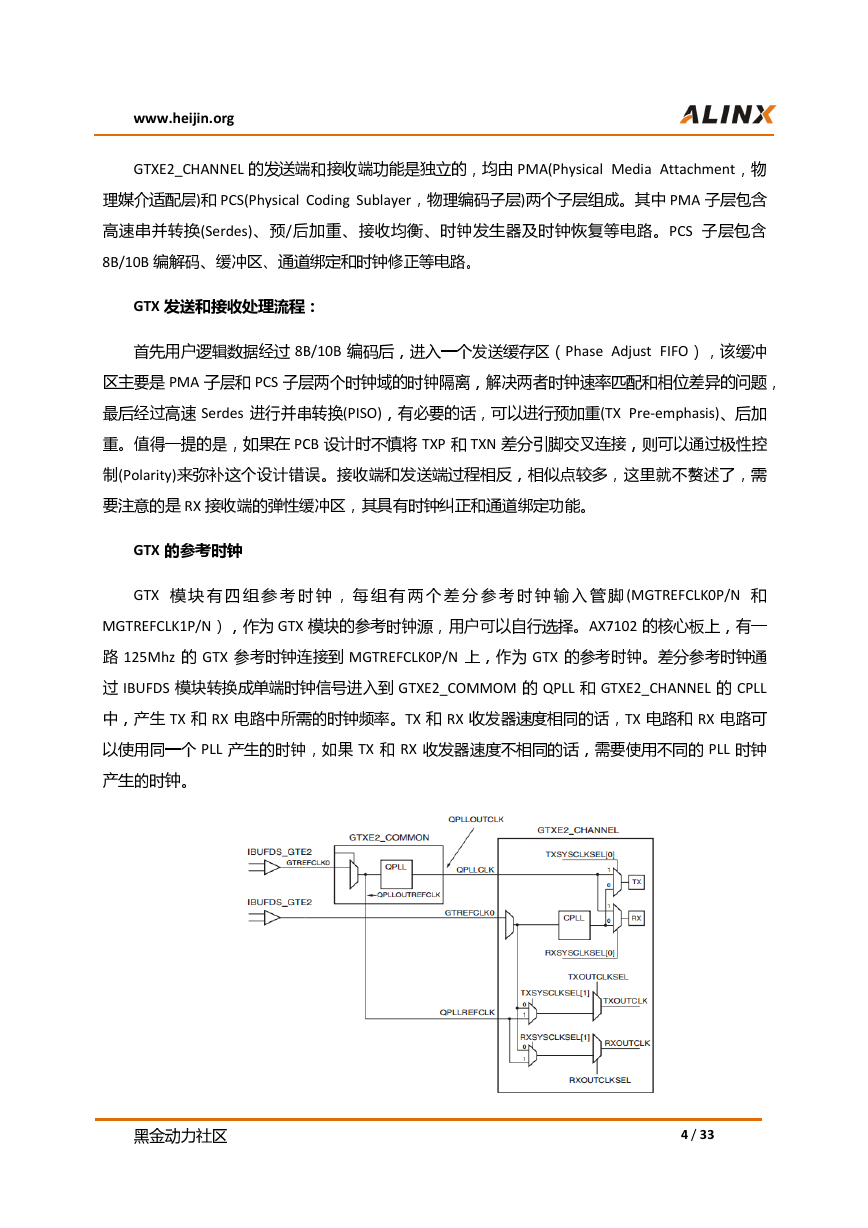

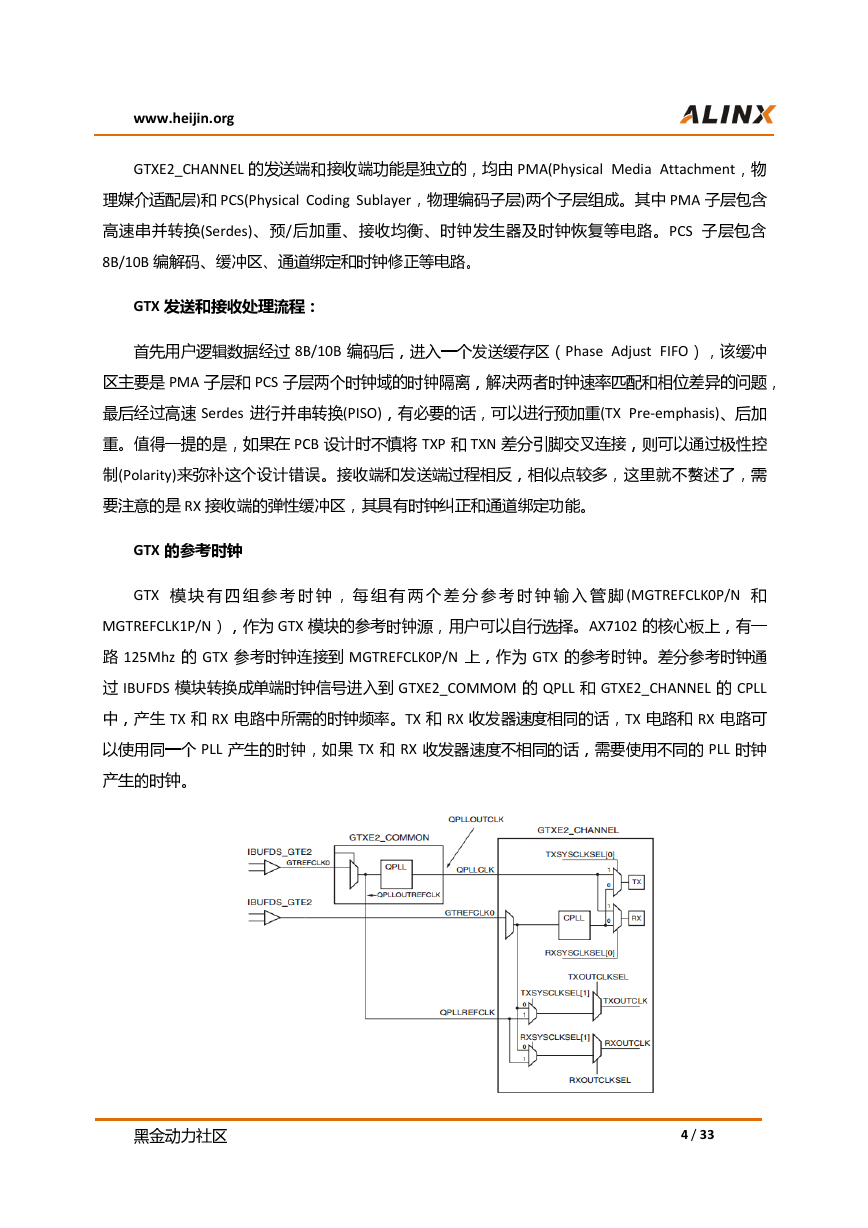

GTX 模 块 有 四 组 参 考 时 钟 , 每 组

有 两 个 差 分 参 考 时 钟 输 入 管 脚 (MGTREFCLK0P/N 和

有 四 组 参 考 时 钟 , 每 组 有 两 个 差 分 参 考 时 钟 输 入 管 脚

MGTREFCLK1P/N),作为 GTX

GTX 模块的参考时钟源,用户可以自行选择。AX7102

AX7102 的核心板上,有一

路 125Mhz 的 GTX 参考时钟连接到

参考时钟连接到 MGTREFCLK0P/N 上,作为 GTX 的参考时钟。差分参考时钟通

的参考时钟。差分参考时钟通

过 IBUFDS 模块转换成单端时钟信号进入到

模块转换成单端时钟信号进入到 GTXE2_COMMOM 的 QPLL 和 GTXE2_CHANNEL

GTXE2_CHANNEL 的 CPLL

中,产生 TX 和 RX 电路中所需的时钟频率。

电路中所需的时钟频率。TX 和 RX 收发器速度相同的话,

收发器速度相同的话,TX 电路和 RX 电路可

以使用同一个 PLL 产生的时钟,如果

产生的时钟,如果 TX 和 RX 收发器速度不相同的话,需要使用不同的

收发器速度不相同的话,需要使用不同的 PLL 时钟

产生的时钟。

黑金动力社区

4 / 33

�

www.heijin.org

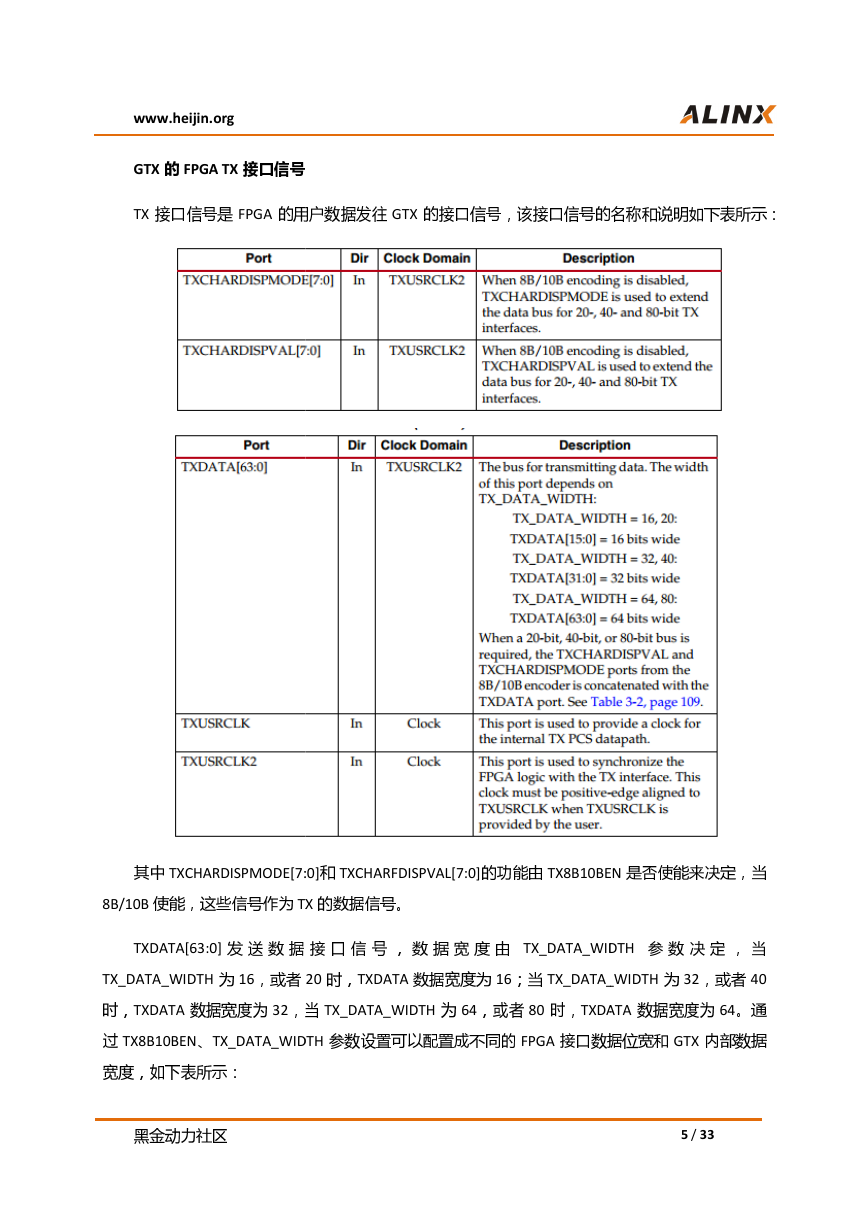

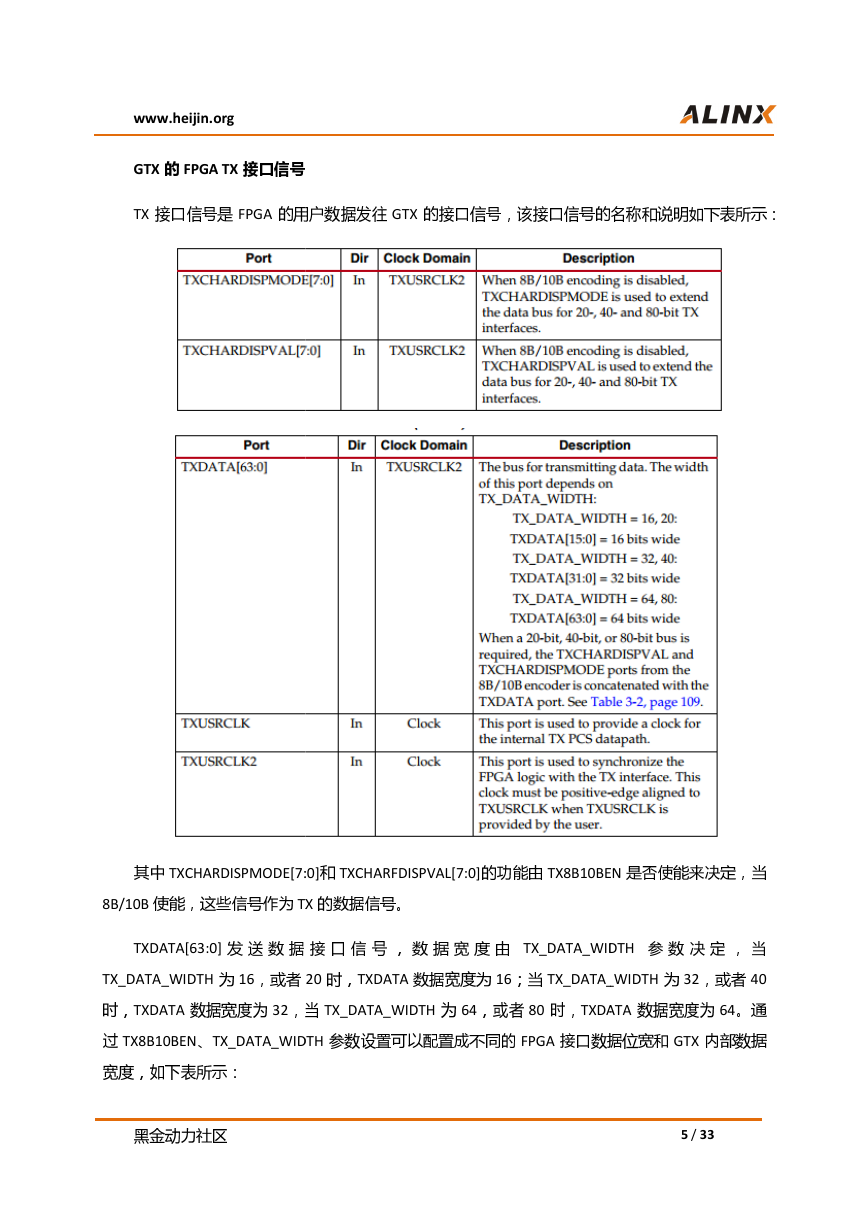

GTX 的 FPGA TX 接口信号

TX 接口信号是 FPGA 的用户数据发往

的用户数据发往 GTX 的接口信号,该接口信号的名称和说明如下表所示:

的接口信号,该接口信号的名称和说明如下表所示:

其中 TXCHARDISPMODE[7:0]

:0]和 TXCHARFDISPVAL[7:0]的功能由 TX8B10BEN

TX8B10BEN 是否使能来决定,当

8B/10B 使能,这些信号作为 TX

TX 的数据信号。

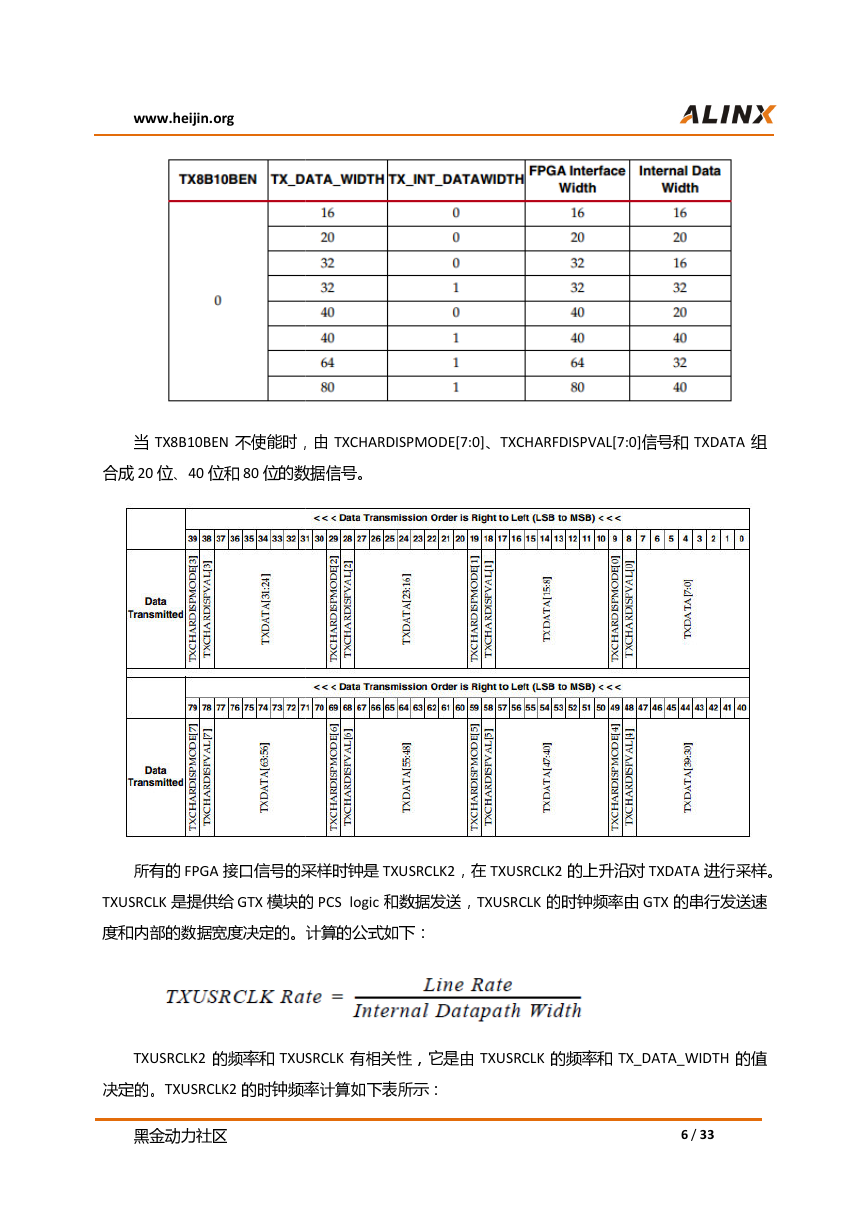

TXDATA[63:0] 发 送 数 据 接 口 信 号 , 数 据 宽 度 由

发 送 数 据 接 口 信 号 , 数 据 宽 度 由 TX_DATA_WIDTH

TX_DATA_WIDTH 参 数 决 定 , 当

TX_DATA_WIDTH 为 16,或者

,或者 20 时,TXDATA 数据宽度为 16;当 TX_DATA_WIDTH

TX_DATA_WIDTH 为 32,或者 40

时,TXDATA 数据宽度为 32,当

当 TX_DATA_WIDTH 为 64,或者 80 时,TXDATA

TXDATA 数据宽度为 64。通

过 TX8B10BEN、TX_DATA_WIDTH

TX_DATA_WIDTH 参数设置可以配置成不同的 FPGA 接口数据位宽和

接口数据位宽和 GTX 内部数据

宽度,如下表所示:

黑金动力社区

5 / 33

�

www.heijin.org

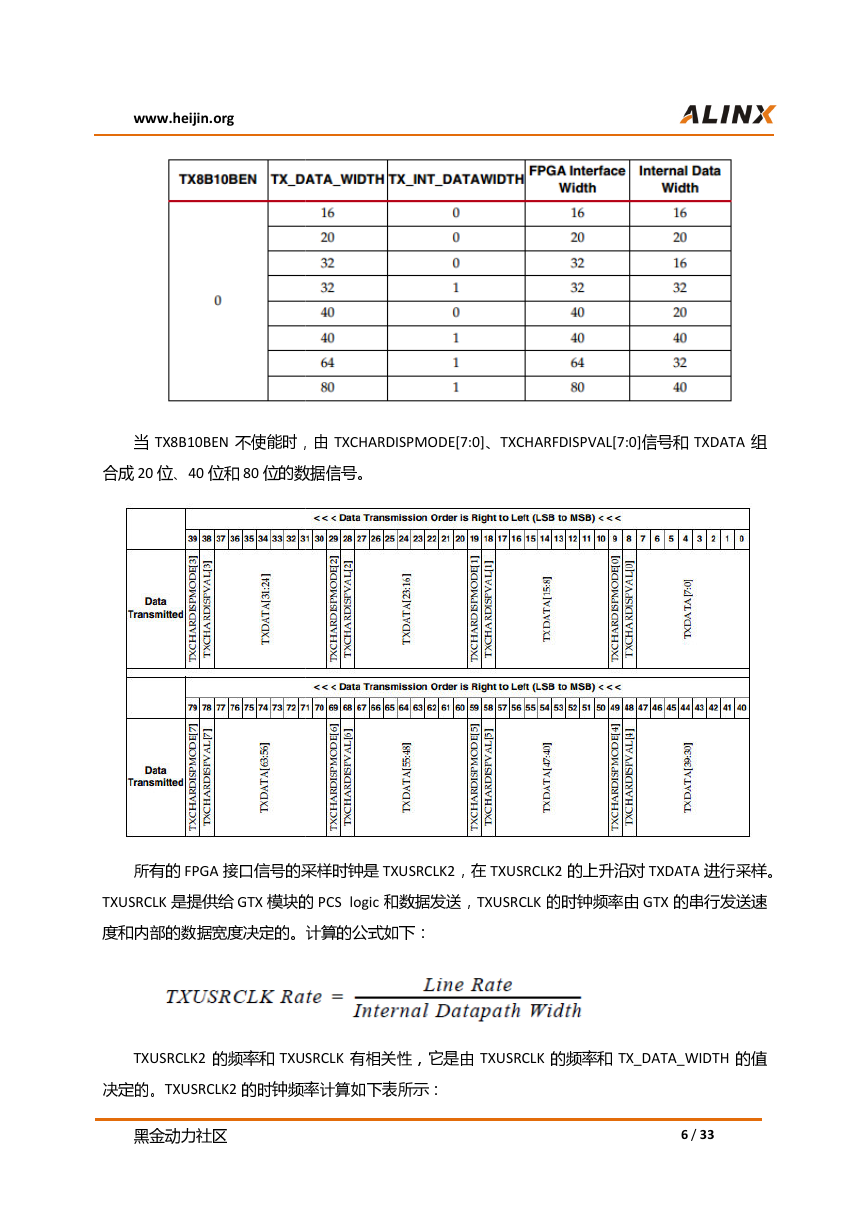

当 TX8B10BEN 不使能时,由

不使能时,由 TXCHARDISPMODE[7:0]、TXCHARFDISPVAL[

TXCHARFDISPVAL[7:0]信号和 TXDATA 组

合成 20 位、40 位和 80 位的数据信号。

的数据信号。

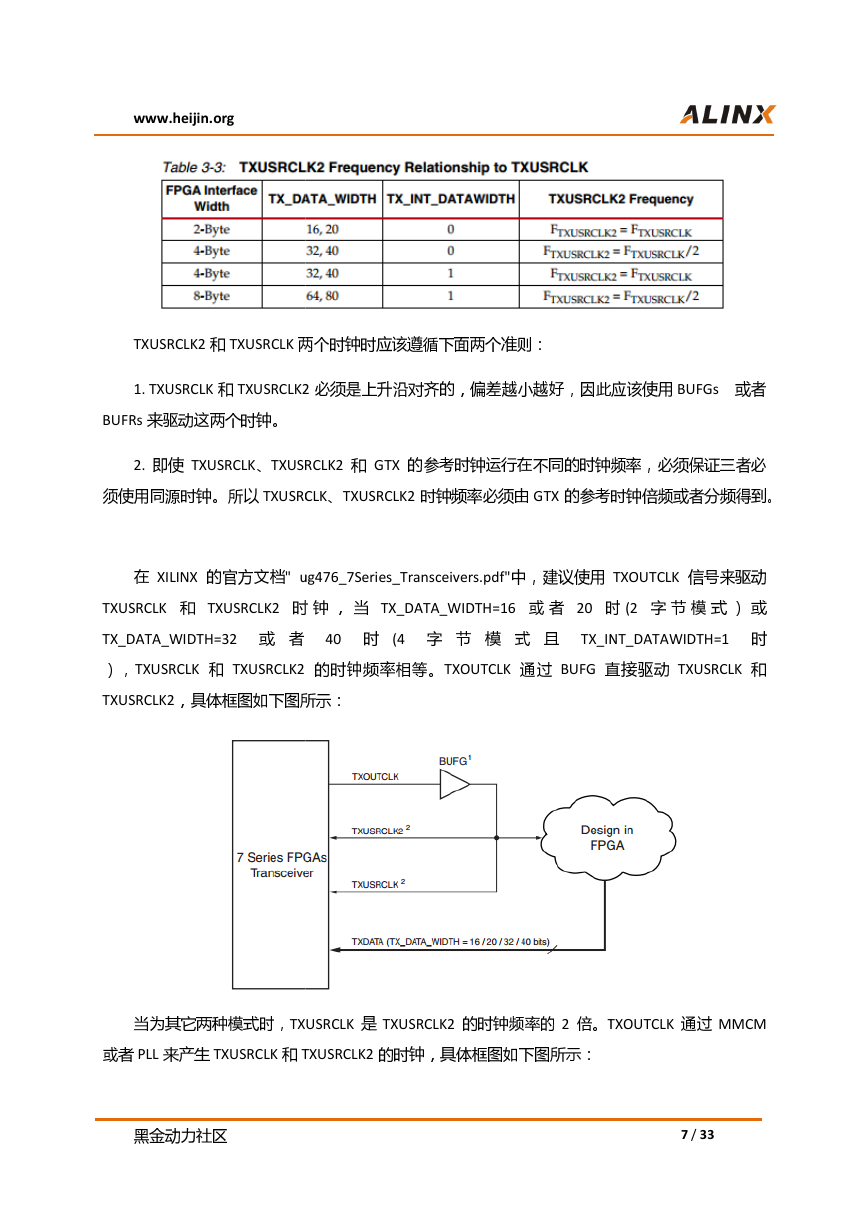

所有的 FPGA 接口信号的采样时钟是

接口信号的采样时钟是 TXUSRCLK2,在 TXUSRCLK2 的上升沿对

的上升沿对 TXDATA 进行采样。

TXUSRCLK 是提供给 GTX 模块的

模块的 PCS logic 和数据发送,TXUSRCLK 的时钟频率由

的时钟频率由 GTX 的串行发送速

度和内部的数据宽度决定的。计算的公式如下:

度和内部的数据宽度决定的。计算的公式如下:

TXUSRCLK2 的频率和 TXUSRCLK

TXUSRCLK 有相关性,它是由 TXUSRCLK 的频率和

的频率和 TX_DATA_WIDTH 的值

决定的。TXUSRCLK2 的时钟频率计算如下表所示:

的时钟频率计算如下表所示:

黑金动力社区

6 / 33

�

www.heijin.org

TXUSRCLK2 和 TXUSRCLK 两个时钟时应该遵循下面两个准则:

两个时钟时应该遵循下面两个准则:

1. TXUSRCLK 和 TXUSRCLK2

TXUSRCLK2 必须是上升沿对齐的,偏差越小越好,因此应该使用

必须是上升沿对齐的,偏差越小越好,因此应该使用 BUFGs 或者

BUFRs 来驱动这两个时钟。

2. 即使 TXUSRCLK、TXUSRCLK2

TXUSRCLK2 和 GTX 的参考时钟运行在不同的时钟频率,必须保证三者必

的参考时钟运行在不同的时钟频率,必须保证三者必

须使用同源时钟。所以 TXUSRCLK

TXUSRCLK、TXUSRCLK2 时钟频率必须由 GTX 的参考时钟倍频或者分频得到。

的参考时钟倍频或者分频得到。

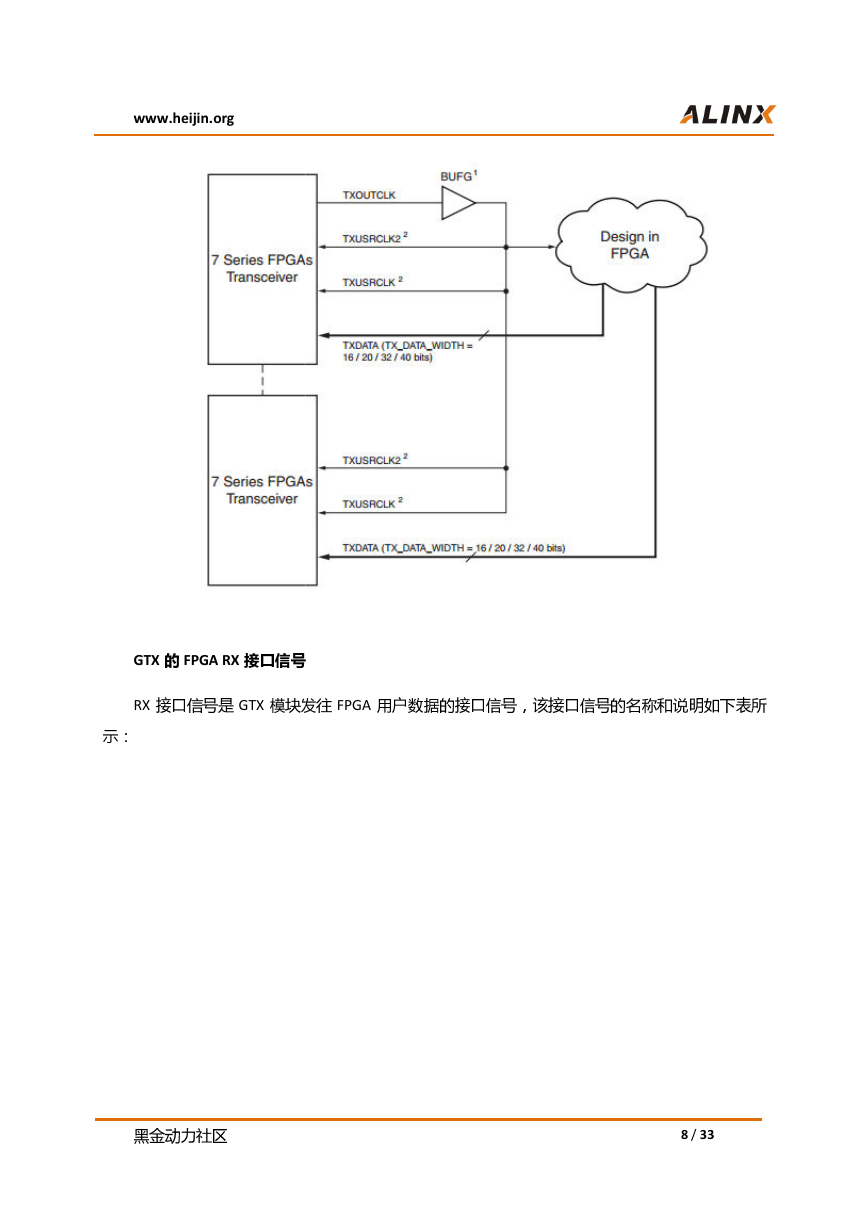

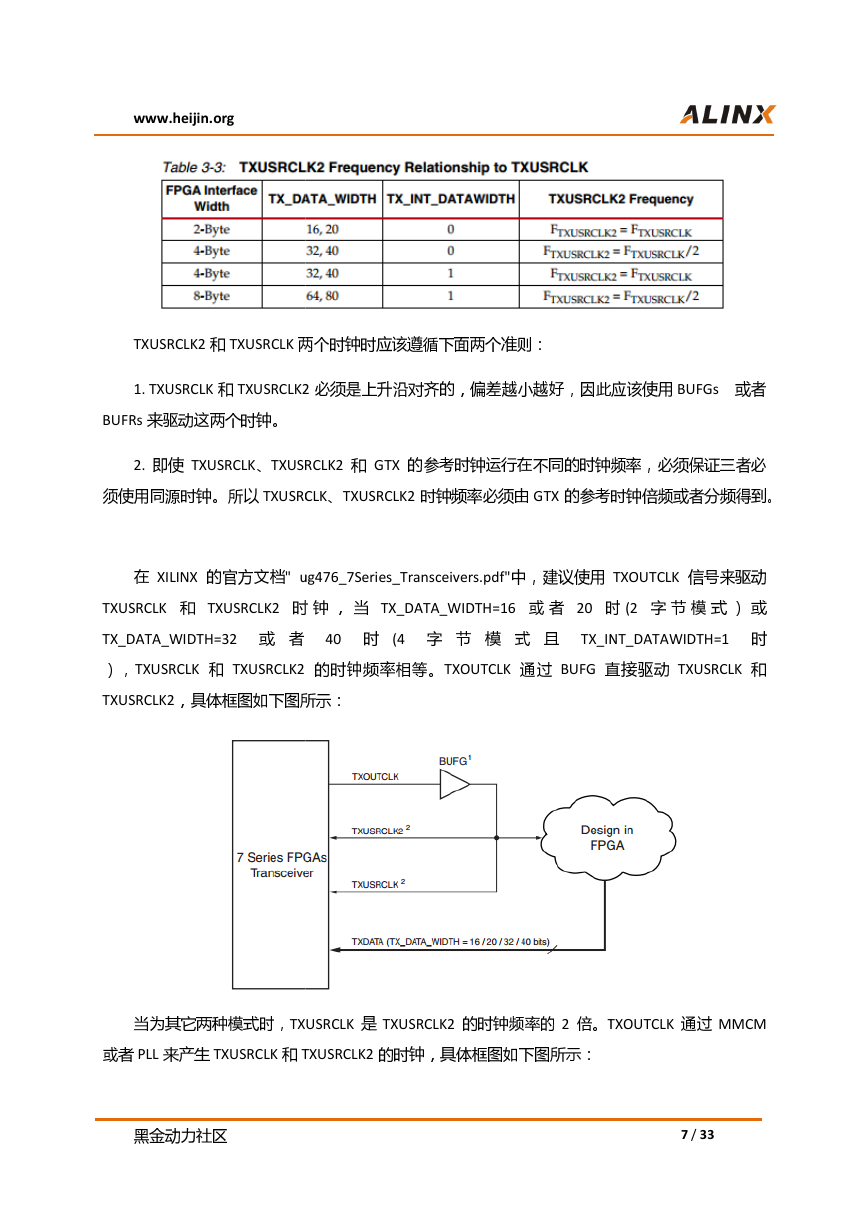

在 XILINX 的官方文档" ug4

ug476_7Series_Transceivers.pdf"中,建议使用

中,建议使用 TXOUTCLK 信号来驱动

TXUSRCLK 和 TXUSRCLK2 时 钟 , 当

时 钟 , 当 TX_DATA_WIDTH=16 或 者 20 时

时 (2 字 节 模 式 ) 或

TX_DATA_WIDTH=32 或 者

或 者 40 时 (4 字 节 模 式 且 TX_INT_DATAWIDTH

TX_INT_DATAWIDTH=1 时

),TXUSRCLK 和 TXUSRCLK2

TXUSRCLK2 的时钟频率相等。TXOUTCLK 通过 BUFG 直接驱动

直接驱动 TXUSRCLK 和

TXUSRCLK2,具体框图如下图所示:

,具体框图如下图所示:

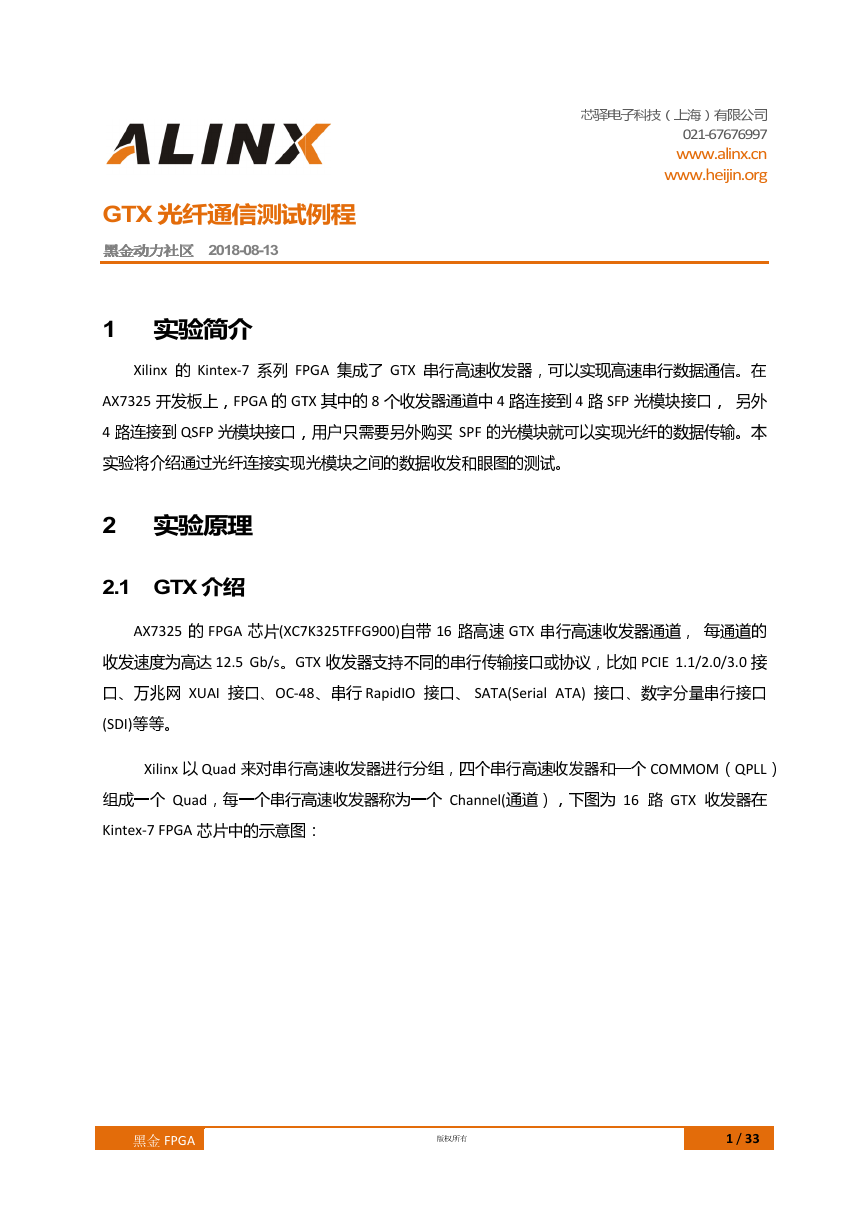

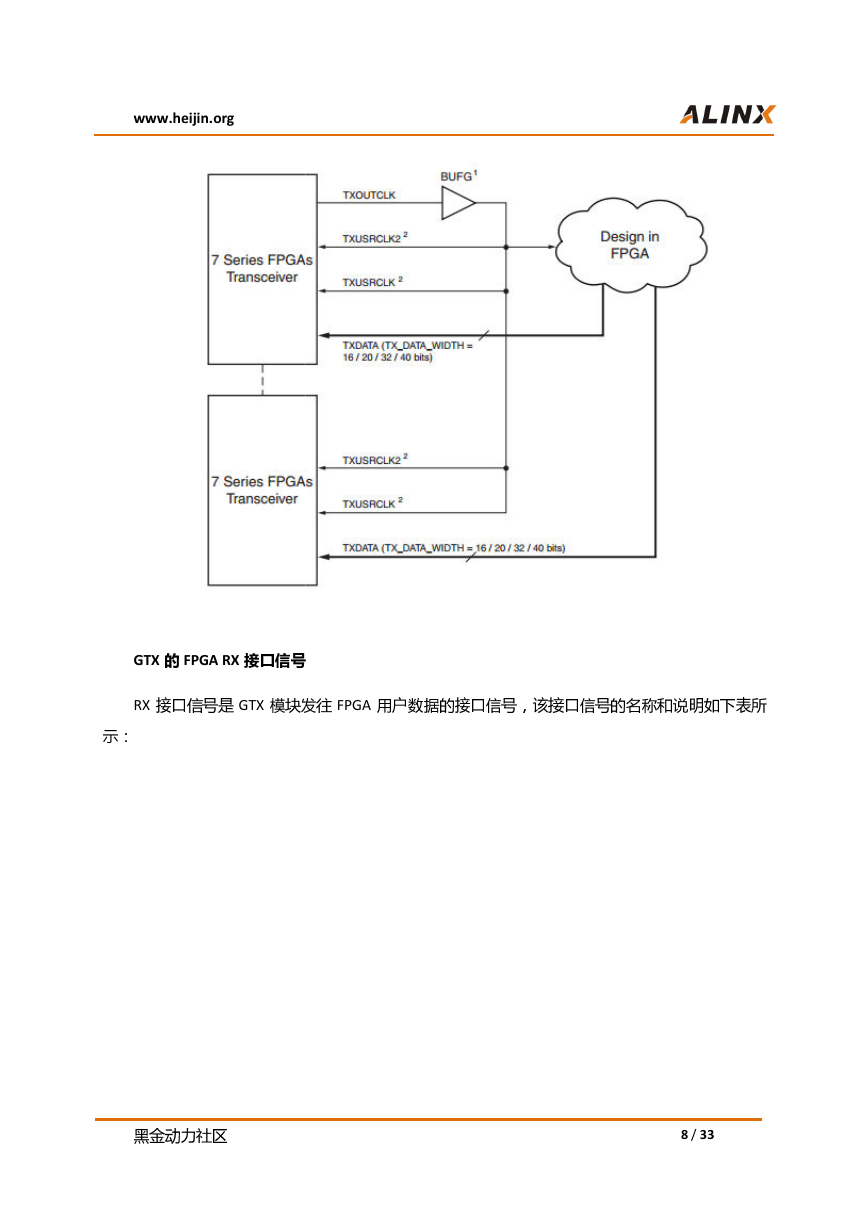

当为其它两种模式时,TXUSRCLK

TXUSRCLK 是 TXUSRCLK2 的时钟频率的 2 倍。TXOUTCLK

TXOUTCLK 通过 MMCM

或者 PLL 来产生 TXUSRCLK 和 TXUSRCLK2

TXUSRCLK2 的时钟,具体框图如下图所示:

黑金动力社区

7 / 33

�

www.heijin.org

GTX 的 FPGA RX 接口信号

接口信号

RX 接口信号是 GTX 模块发往

模块发往 FPGA 用户数据的接口信号,该接口信号的名称和说明如下表所

用户数据的接口信号,该接口信号的名称和说明如下表所

示:

黑金动力社区

8 / 33

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc