BlueCore® CSR8675 WLCSP

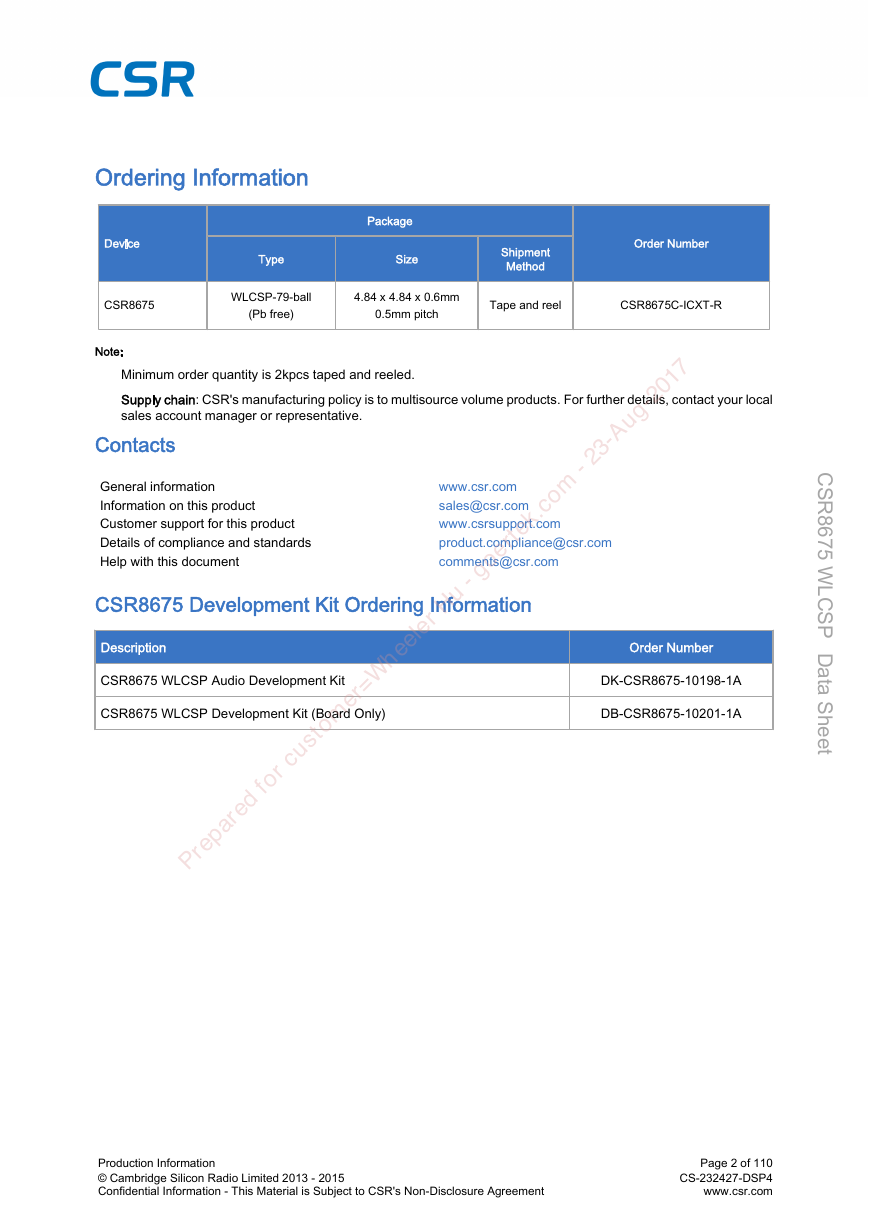

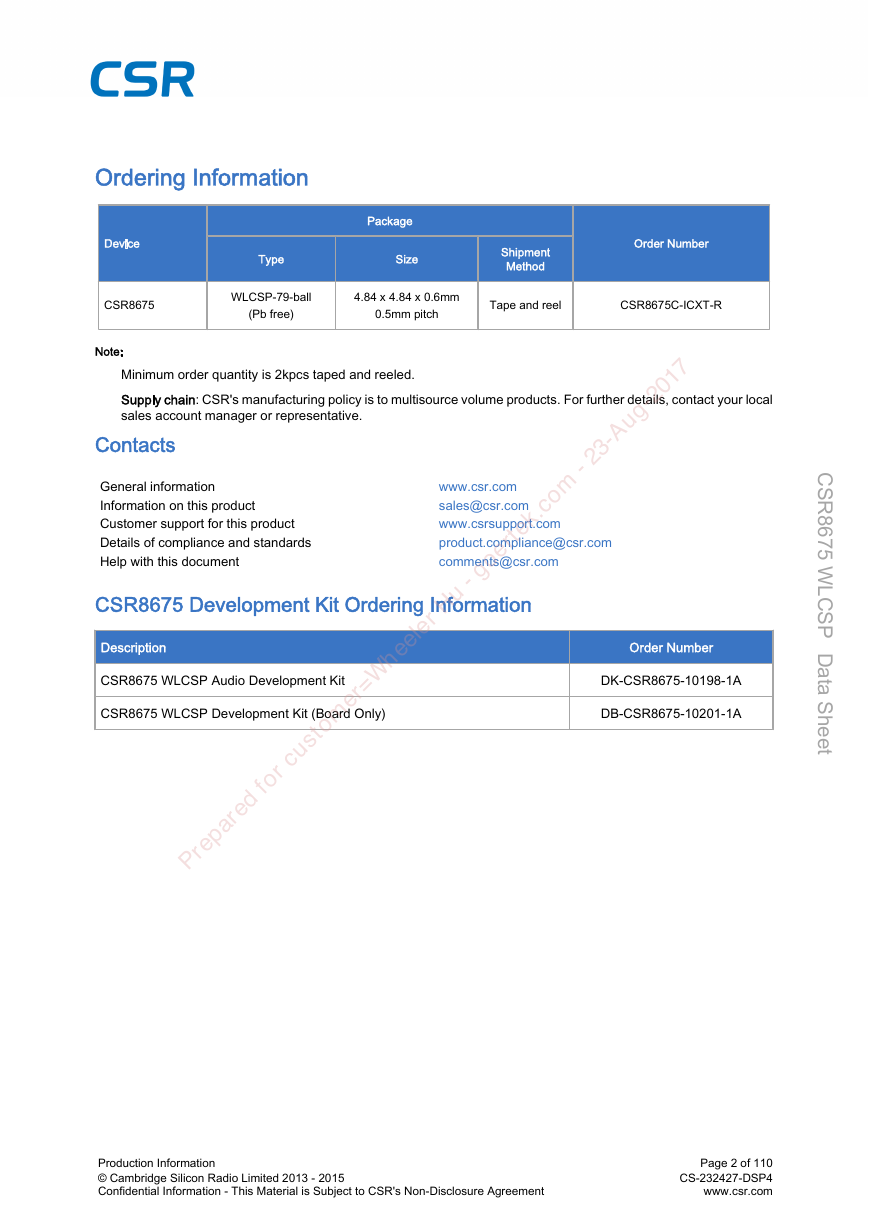

Ordering Information

Contacts

CSR8675 Development Kit Ordering Information

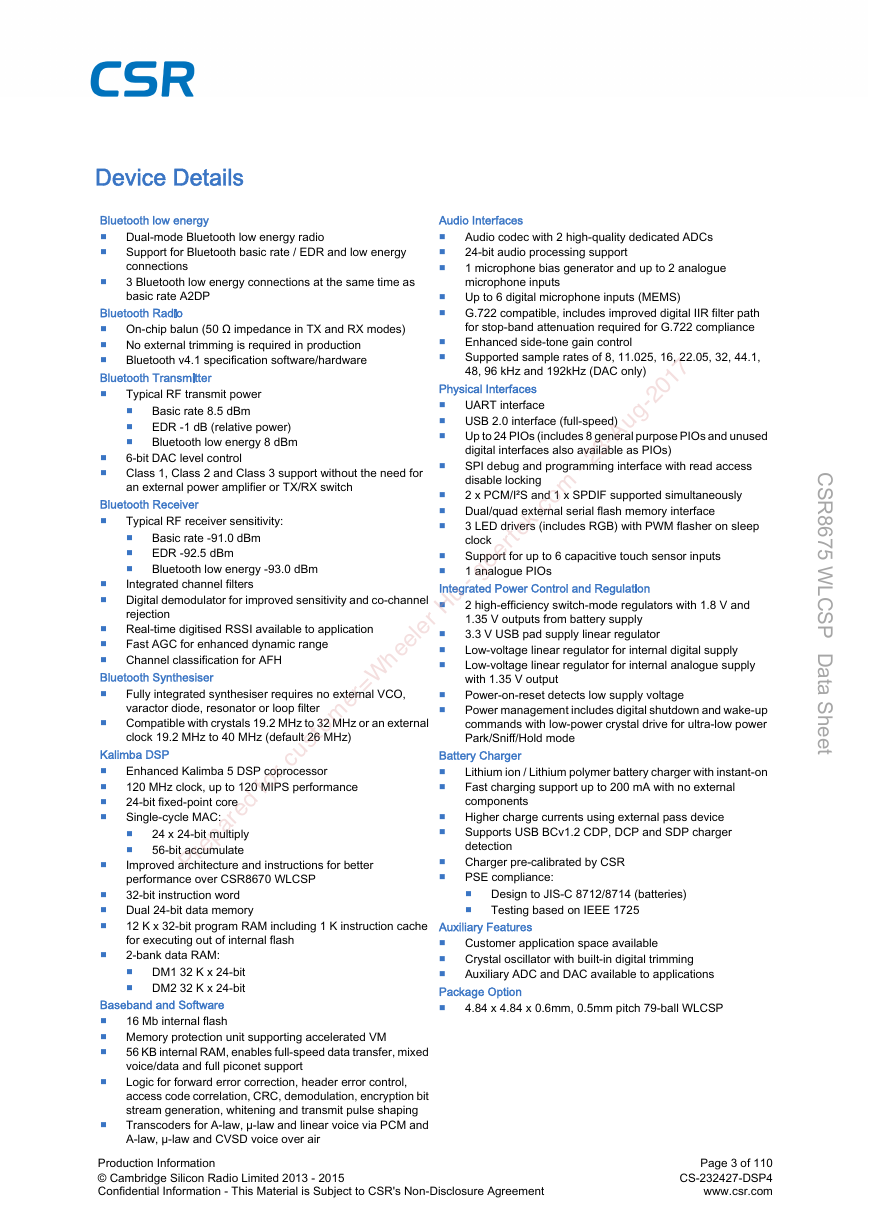

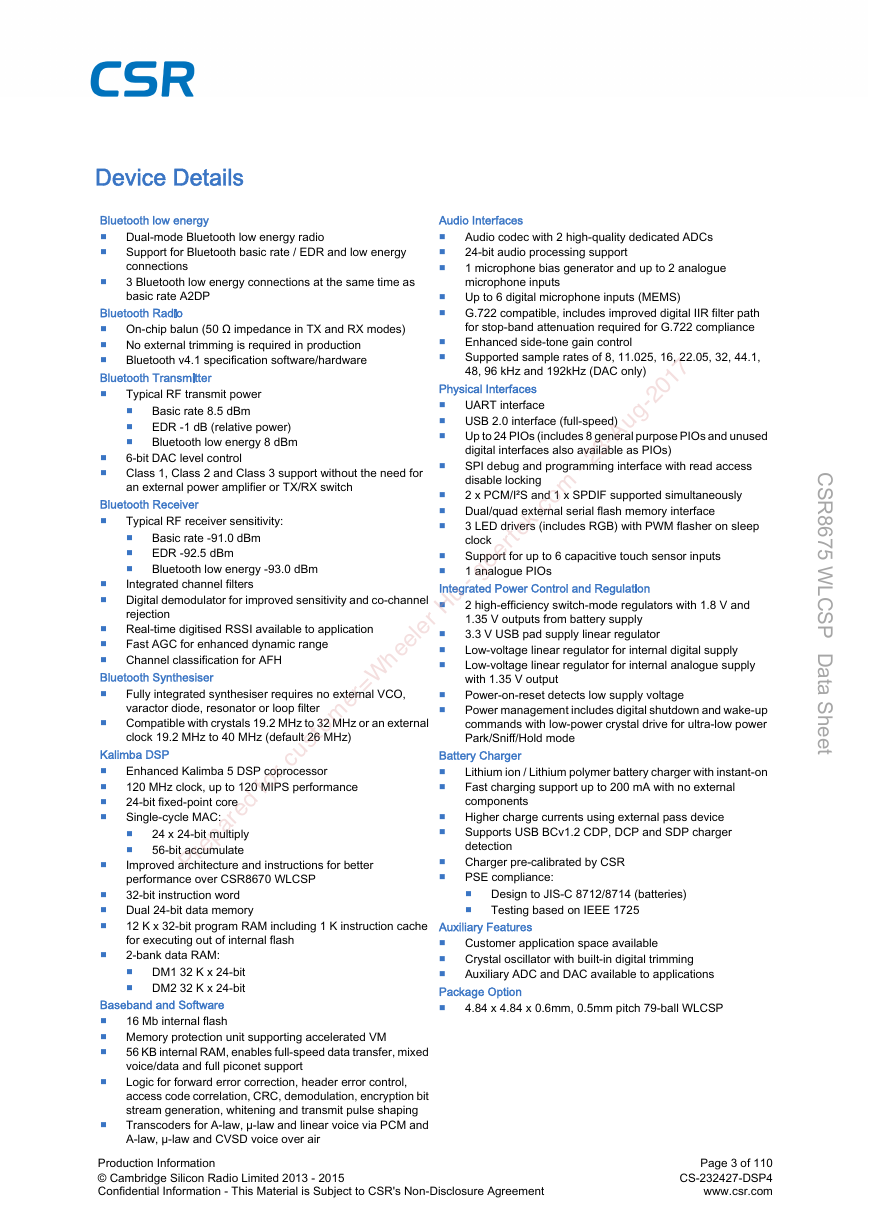

Device Details

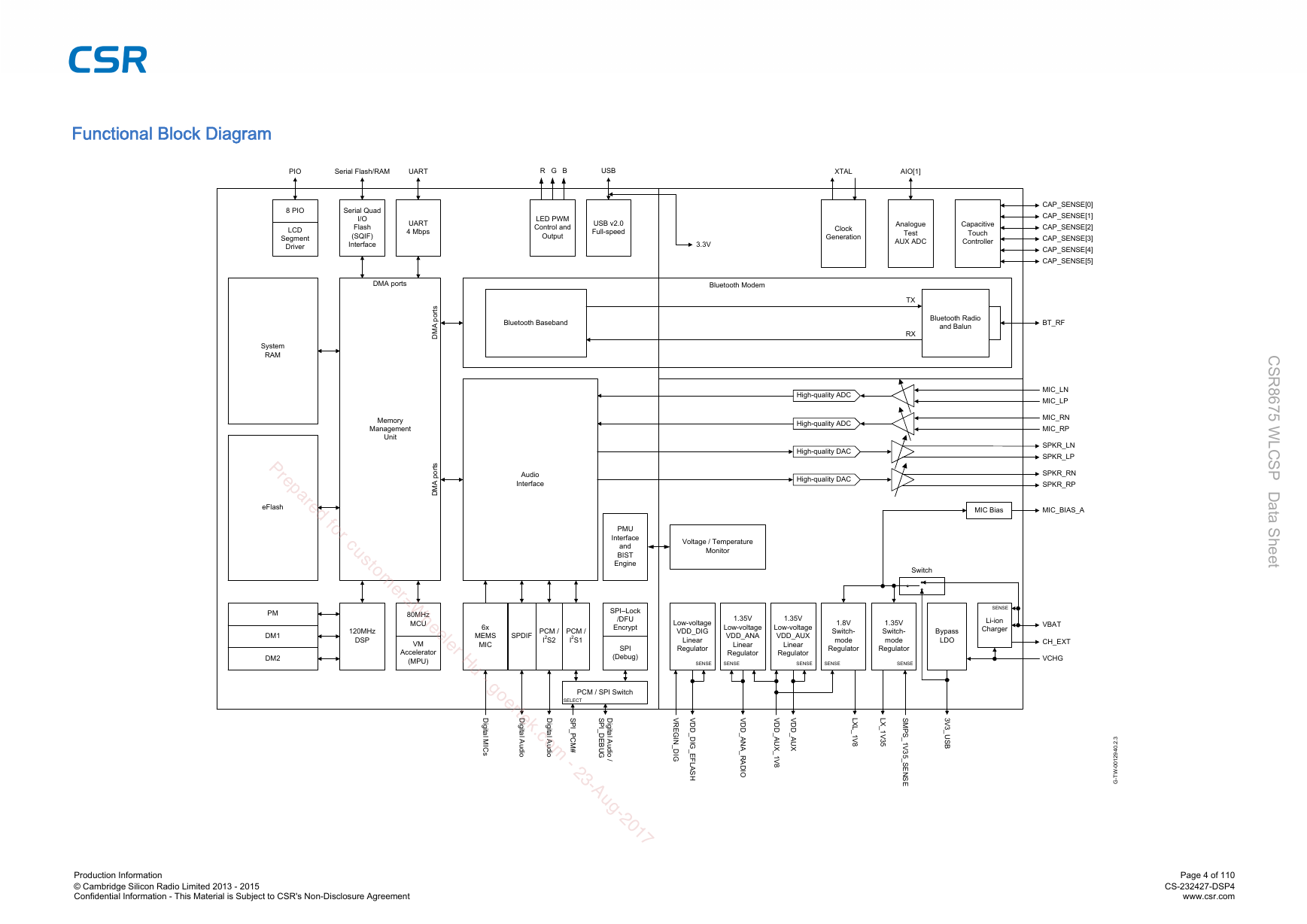

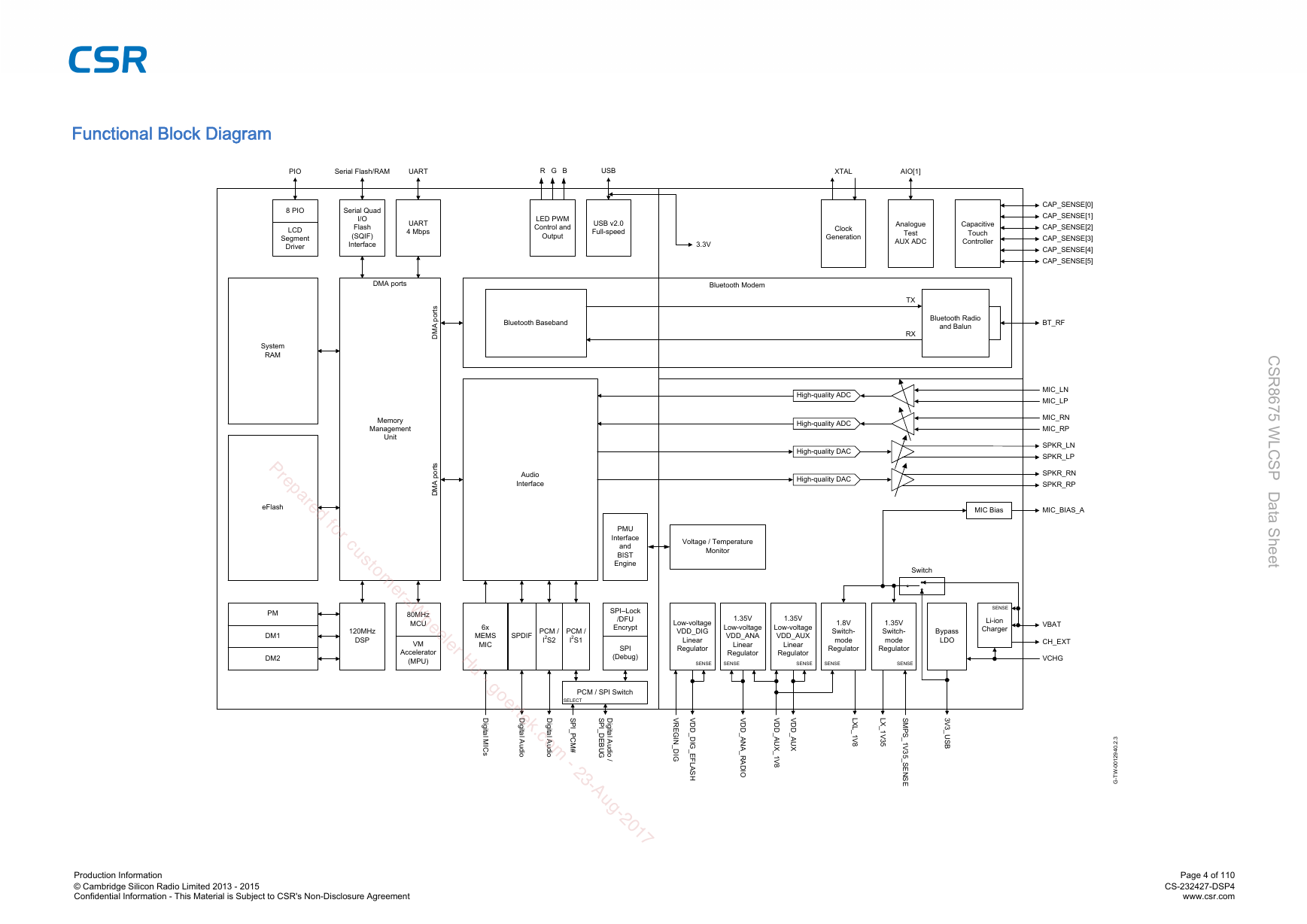

Functional Block Diagram

Document History

Status Information

Contents

List of Figures

List of Tables

List of Equations

1 Package Information

1.1 Pinout Diagram

1.2 Device Terminal Functions

1.3 Package Dimensions

1.4 PCB Design and Assembly Considerations

1.5 Typical Solder Reflow Profile

2 System Architecture

3 Bluetooth Modem

3.1 RF Ports

3.1.1 BT_RF

3.2 RF Receiver

3.2.1 Low Noise Amplifier

3.2.2 RSSI Analogue to Digital Converter

3.3 RF Transmitter

3.3.1 IQ Modulator

3.3.2 Power Amplifier

3.4 Bluetooth Radio Synthesiser

3.5 Baseband

3.5.1 Burst Mode Controller

3.5.2 Physical Layer Hardware Engine

4 Clock Generation

4.1 Clock Architecture

4.2 Input Frequencies and PS Key Settings

4.3 External Reference Clock

4.3.1 Input: XTAL_IN

4.3.2 XTAL_IN Impedance in External Mode

4.3.3 Clock Timing Accuracy

4.4 Crystal Oscillator: XTAL_IN and XTAL_OUT

4.4.1 Crystal Calibration

4.4.2 Crystal Specification

5 Bluetooth Stack Microcontroller

5.1 VM Accelerator

6 Kalimba DSP

7 Memory Interface and Management

7.1 Memory Management Unit

7.2 System RAM

7.3 Kalimba DSP RAM

7.4 eFlash Memory (16 Mb)

7.5 Serial Quad I/O Flash Interface (SQIF)

8 Serial Interfaces

8.1 USB Interface

8.2 UART Interface

8.2.1 UART Configuration While Reset is Active

8.3 Programming and Debug Interface

8.3.1 Instruction Cycle

8.3.2 Multi-slave Operation

8.3.3 SPI-lock

8.4 Software-driven I²C Interface

9 Interfaces

9.1 Programmable I/O Ports, PIO

9.2 Analogue I/O Ports, AIO

9.3 Capacitive Touch Sensor

9.3.1 Capacitive Range Control:

9.3.2 Sampling Front End

9.3.3 ADC

9.3.4 Digital Signal Conditioning (Digital Processing)

9.3.5 Software Signal Conditioning (Firmware)

9.3.6 VM

9.4 LED Drivers

10 Audio Interface

10.1 Audio Input and Output

10.2 Audio Codec Interface

10.2.1 Audio Codec Block Diagram

10.2.2 Codec Set-up

10.2.3 ADC

10.2.4 ADC Sample Rate Selection

10.2.5 ADC Audio Input Gain

10.2.6 ADC Pre-amplifier and ADC Analogue Gain

10.2.7 ADC Digital Gain

10.2.8 ADC Digital IIR Filter

10.2.9 DAC

10.2.10 DAC Sample Rate Selection

10.2.11 DAC Digital Gain

10.2.12 DAC Analogue Gain

10.2.13 DAC Digital FIR Filter

10.2.14 IEC 60958 Interface

10.2.15 Microphone Input

10.2.16 Digital Microphone Inputs

10.2.17 Line Input

10.2.18 Output Stage

10.2.19 Mono Operation

10.2.20 Side Tone

10.2.21 Integrated Digital IIR Filter

10.3 PCM1 and PCM2 Interface

10.3.1 PCM Interface Master/Slave

10.3.2 Long Frame Sync

10.3.3 Short Frame Sync

10.3.4 Multi-slot Operation

10.3.5 GCI Interface

10.3.6 Slots and Sample Formats

10.3.7 Additional Features

10.3.8 PCM Timing Information

10.3.9 PCM_CLK and PCM_SYNC Generation

10.3.10 PCM Configuration

10.4 I²S1 and I²S2 Interface

11 WLAN Coexistence Interface

12 Power Control and Regulation

12.1 1.8V Switch-mode Regulator

12.2 1.35V Switch-mode Regulator

12.3 Inductor Choice

12.4 1.8V and 1.35V Switch-mode Regulators Combined

12.5 Bypass LDO Linear Regulator

12.6 Low-voltage VDD_DIG Linear Regulator

12.7 Low-voltage VDD_AUX Linear Regulator

12.8 Low-voltage VDD_ANA Linear Regulator

12.9 Voltage Regulator Enable

12.10 External Regulators and Power Sequencing

12.11 Reset, RST#

12.11.1 Digital Pin States on Reset

12.11.2 Status After Reset

12.12 Automatic Reset Protection

13 Battery Charger

13.1 Battery Charger Hardware Operating Modes

13.1.1 Disabled Mode

13.1.2 Trickle Charge Mode

13.1.3 Fast Charge Mode

13.1.4 Standby Mode

13.1.5 Error Mode

13.2 Battery Charger Trimming and Calibration

13.3 VM Battery Charger Control

13.4 Battery Charger Firmware and PS Keys

13.5 External Mode

14 Example Application Schematic

15 Example Application Using Different Power Supply Configurations

16 Electrical Characteristics

16.1 Absolute Maximum Ratings

16.2 Recommended Operating Conditions

16.3 Input/Output Terminal Characteristics

16.3.1 Regulators: Available For External Use

16.3.1.1 1.8V Switch-mode Regulator

16.3.1.2 Combined 1.8V and 1.35V Switch-mode Regulator

16.3.1.3 Bypass LDO Regulator

16.3.2 Regulators: For Internal Use Only

16.3.2.1 1.35V Switch-mode Regulator

16.3.2.2 Low-voltage VDD_DIG Linear Regulator

16.3.2.3 Low-voltage VDD_AUX Linear Regulator

16.3.2.4 Low-voltage VDD_ANA Linear Regulator

16.3.3 Regulator Enable

16.3.4 Battery Charger

16.3.5 Reset

16.3.6 USB

16.3.7 Clocks

16.3.8 Stereo Codec: Analogue to Digital Converter

16.3.9 Stereo Codec: Digital to Analogue Converter

16.3.10 Digital

16.3.11 LED Driver Pads

16.3.12 Auxiliary ADC

16.3.13 Auxiliary DAC

16.4 ESD Protection

16.4.1 USB Electrostatic Discharge Immunity

17 Power Consumption

18 CSR Green Semiconductor Products and RoHS Compliance

19 Software

19.1 On-chip Software

19.1.1 Stand-alone CSR8675 WLCSP and Kalimba DSP Applications

19.1.2 BlueCore HCI Stack

19.1.2.1 Latest Features of the HCI Stack

19.2 Off-chip Software

19.2.1 CSR8675 Development Kit

19.2.1.1 Audio Development Kit Software

19.2.2 eXtension Program Support

20 Tape and Reel Information

20.1 Tape Orientation

20.2 Tape Dimensions

20.3 Reel Information

20.4 Moisture Sensitivity Level

21 Document References

Terms and Definitions

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc