MT7621A

Network Processor

FOR stonexu@ zioncom.net USE ONLY

MEDIATEK CONFIDENTIAL

MT7621A

DATASHEET

Page 1 of 45

MT7621A_Data_Sheet_v0.4

loginid=stonexu@zioncom.net,time=2014-05-29 11:44:05,ip=183.16.164.220,doctitle=MT7621A_Datasheet_v0_4.docx,company=Zioncom Technology Co.LTD(吉翁)_RLT

�

Gigabit Switch

bits)

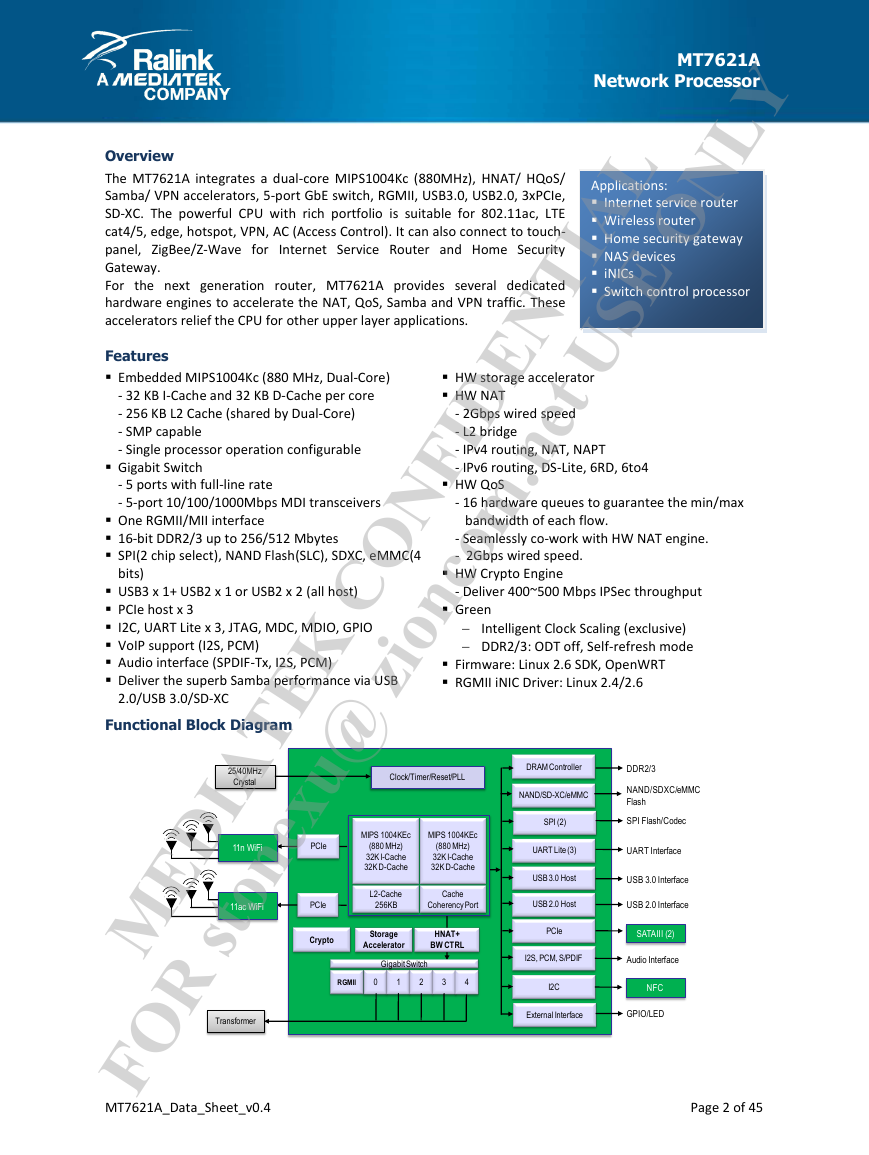

Overview

MT7621A

Network Processor

HW storage accelerator

HW NAT

- 2Gbps wired speed

- L2 bridge

- IPv4 routing, NAT, NAPT

- IPv6 routing, DS-Lite, 6RD, 6to4

HW QoS

- 32 KB I-Cache and 32 KB D-Cache per core

- 256 KB L2 Cache (shared by Dual-Core)

- SMP capable

- Single processor operation configurable

- 5 ports with full-line rate

- 5-port 10/100/1000Mbps MDI transceivers

One RGMII/MII interface

16-bit DDR2/3 up to 256/512 Mbytes

SPI(2 chip select), NAND Flash(SLC), SDXC, eMMC(4

Applications:

Internet service router

Wireless router

Home security gateway

NAS devices

iNICs

Switch control processor

The MT7621A integrates a dual-core MIPS1004Kc (880MHz), HNAT/ HQoS/

Samba/ VPN accelerators, 5-port GbE switch, RGMII, USB3.0, USB2.0, 3xPCIe,

SD-XC. The powerful CPU with rich portfolio is suitable for 802.11ac, LTE

cat4/5, edge, hotspot, VPN, AC (Access Control). It can also connect to touch-

panel, ZigBee/Z-Wave for Internet Service Router and Home Security

Gateway.

For the next generation router, MT7621A provides several dedicated

hardware engines to accelerate the NAT, QoS, Samba and VPN traffic. These

accelerators relief the CPU for other upper layer applications.

Features

Embedded MIPS1004Kc (880 MHz, Dual-Core)

FOR stonexu@ zioncom.net USE ONLY

MEDIATEK CONFIDENTIAL

USB3 x 1+ USB2 x 1 or USB2 x 2 (all host)

PCIe host x 3

I2C, UART Lite x 3, JTAG, MDC, MDIO, GPIO

VoIP support (I2S, PCM)

Audio interface (SPDIF-Tx, I2S, PCM)

Deliver the superb Samba performance via USB

- 16 hardware queues to guarantee the min/max

bandwidth of each flow.

- Seamlessly co-work with HW NAT engine.

- 2Gbps wired speed.

Intelligent Clock Scaling (exclusive)

DDR2/3: ODT off, Self-refresh mode

Firmware: Linux 2.6 SDK, OpenWRT

RGMII iNIC Driver: Linux 2.4/2.6

HW Crypto Engine

- Deliver 400~500 Mbps IPSec throughput

Green

2.0/USB 3.0/SD-XC

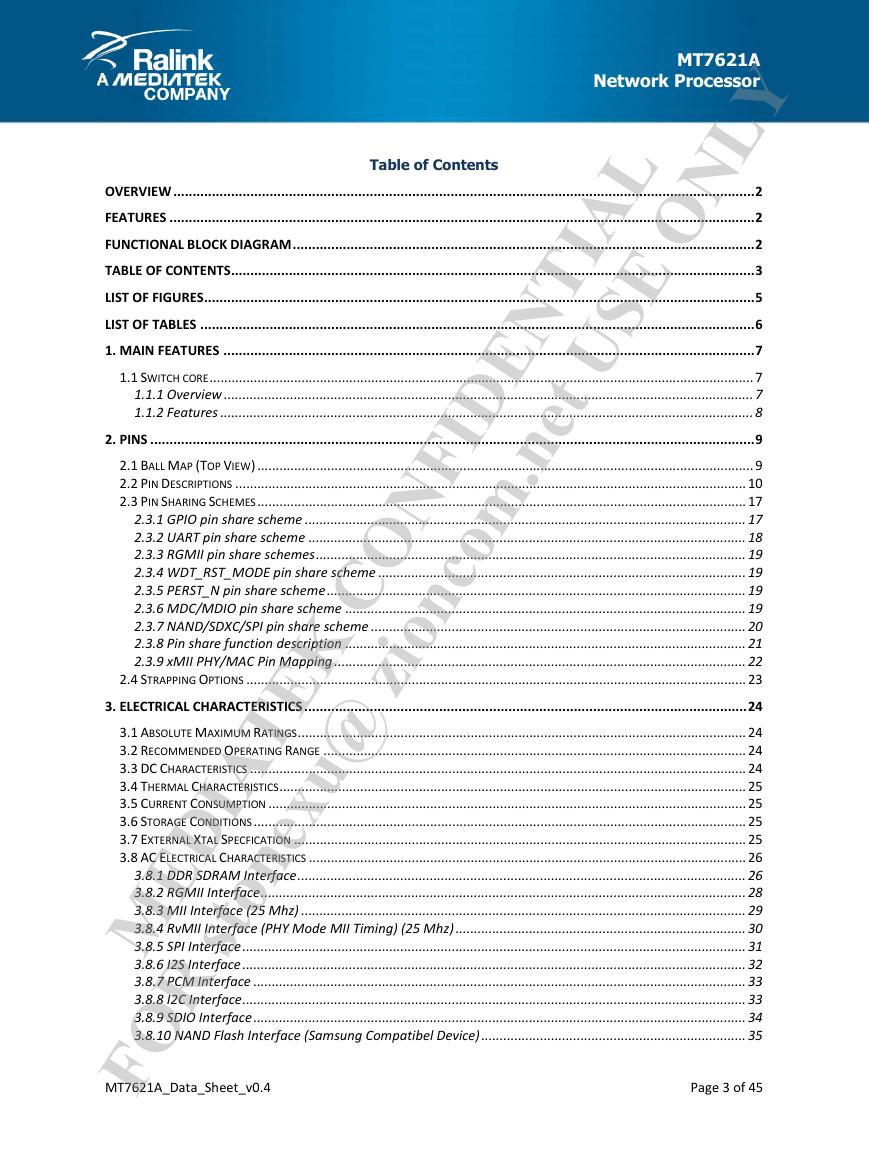

Functional Block Diagram

MT7621A_Data_Sheet_v0.4

loginid=stonexu@zioncom.net,time=2014-05-29 11:44:05,ip=183.16.164.220,doctitle=MT7621A_Datasheet_v0_4.docx,company=Zioncom Technology Co.LTD(吉翁)_RLT

Page 2 of 45

Clock/Timer/Reset/PLLDRAM ControllerSPI (2) PCIeUSB 3.0 HostUART Lite (3) External Interface25/40MHz CrystalDDR2/3NAND/SDXC/eMMCFlashSPI Flash/CodecUART InterfaceUSB 3.0 Interface USB 2.0 InterfaceSATAAudio InterfaceGPIO/LEDNAND/SD-XC/eMMCI2CI2S, PCM, S/PDIFHNAT+BW CTRLCrypto11n WiFiPCIeStorage AcceleratorUSB 2.0 HostMIPS 1004KEc(880 MHz)32K I-Cache32K D-CacheMIPS 1004KEc(880 MHz)32K I-Cache32K D-CacheL2-Cache 256KBCache Coherency PortPCIeNFCSATAIII (2)11ac WiFi01234Gigabit SwitchTransformerRGMII�

MT7621A

Network Processor

Table of Contents

LIST OF FIGURES ............................................................................................................................................... 5

LIST OF TABLES ................................................................................................................................................ 6

1. MAIN FEATURES .......................................................................................................................................... 7

2. PINS ............................................................................................................................................................. 9

OVERVIEW ....................................................................................................................................................... 2

FEATURES ........................................................................................................................................................ 2

FUNCTIONAL BLOCK DIAGRAM ........................................................................................................................ 2

TABLE OF CONTENTS ........................................................................................................................................ 3

1.1 SWITCH CORE .................................................................................................................................................... 7

1.1.1 Overview ................................................................................................................................................ 7

1.1.2 Features ................................................................................................................................................. 8

FOR stonexu@ zioncom.net USE ONLY

MEDIATEK CONFIDENTIAL

3.1 ABSOLUTE MAXIMUM RATINGS .......................................................................................................................... 24

3.2 RECOMMENDED OPERATING RANGE ................................................................................................................... 24

3.3 DC CHARACTERISTICS ....................................................................................................................................... 24

3.4 THERMAL CHARACTERISTICS ............................................................................................................................... 25

3.5 CURRENT CONSUMPTION .................................................................................................................................. 25

3.6 STORAGE CONDITIONS ...................................................................................................................................... 25

3.7 EXTERNAL XTAL SPECFICATION ........................................................................................................................... 25

3.8 AC ELECTRICAL CHARACTERISTICS ....................................................................................................................... 26

3.8.1 DDR SDRAM Interface .......................................................................................................................... 26

3.8.2 RGMII Interface .................................................................................................................................... 28

3.8.3 MII Interface (25 Mhz) ......................................................................................................................... 29

3.8.4 RvMII Interface (PHY Mode MII Timing) (25 Mhz) ............................................................................... 30

3.8.5 SPI Interface ......................................................................................................................................... 31

3.8.6 I2S Interface ......................................................................................................................................... 32

3.8.7 PCM Interface ...................................................................................................................................... 33

3.8.8 I2C Interface ......................................................................................................................................... 33

3.8.9 SDIO Interface ...................................................................................................................................... 34

3.8.10 NAND Flash Interface (Samsung Compatibel Device) ........................................................................ 35

2.1 BALL MAP (TOP VIEW) ....................................................................................................................................... 9

2.2 PIN DESCRIPTIONS ........................................................................................................................................... 10

2.3 PIN SHARING SCHEMES ..................................................................................................................................... 17

2.3.1 GPIO pin share scheme ........................................................................................................................ 17

2.3.2 UART pin share scheme ....................................................................................................................... 18

2.3.3 RGMII pin share schemes ..................................................................................................................... 19

2.3.4 WDT_RST_MODE pin share scheme .................................................................................................... 19

2.3.5 PERST_N pin share scheme .................................................................................................................. 19

2.3.6 MDC/MDIO pin share scheme ............................................................................................................. 19

2.3.7 NAND/SDXC/SPI pin share scheme ...................................................................................................... 20

2.3.8 Pin share function description ............................................................................................................. 21

2.3.9 xMII PHY/MAC Pin Mapping ................................................................................................................ 22

2.4 STRAPPING OPTIONS ........................................................................................................................................ 23

3. ELECTRICAL CHARACTERISTICS ................................................................................................................... 24

MT7621A_Data_Sheet_v0.4

loginid=stonexu@zioncom.net,time=2014-05-29 11:44:05,ip=183.16.164.220,doctitle=MT7621A_Datasheet_v0_4.docx,company=Zioncom Technology Co.LTD(吉翁)_RLT

Page 3 of 45

�

MT7621A

Network Processor

3.8.11 Power On Sequence ........................................................................................................................... 38

6. REVISION HISTORY ..................................................................................................................................... 45

5. ABBREVIATIONS ......................................................................................................................................... 42

4. PACKAGE INFORMATION ........................................................................................................................... 39

4.1 DIMENSIONS - TFBGA (11.7 MM X 13.6 MM) ..................................................................................................... 39

4.1.1 Diagram Key ........................................................................................................................................ 40

4.2 REFLOW PROFILE GUIDELINE .............................................................................................................................. 40

4.3 TOP MARKING ................................................................................................................................................ 41

4.4 ORDERING INFORMATION .................................................................................................................................. 41

FOR stonexu@ zioncom.net USE ONLY

MEDIATEK CONFIDENTIAL

MT7621A_Data_Sheet_v0.4

loginid=stonexu@zioncom.net,time=2014-05-29 11:44:05,ip=183.16.164.220,doctitle=MT7621A_Datasheet_v0_4.docx,company=Zioncom Technology Co.LTD(吉翁)_RLT

Page 4 of 45

�

MT7621A

Network Processor

List of Figures

FIGURE 2-1 MII MII PHY ..................................................................................................................................... 22

FIGURE 2-2 RVMII MII MAC ................................................................................................................................ 22

FIGURE 2-3 RGMII RGMII PHY ............................................................................................................................. 22

FIGURE 2-4 RGMII RGMII MAC ........................................................................................................................... 22

FIGURE 3-1 DDR2 SDRAM COMMAND TIMING ............................................................................................................ 26

FIGURE 3-2 DDR2 SDRAM WRITE TIMING ................................................................................................................... 26

FIGURE 3-3 DDR2 SDRAM READ TIMING .................................................................................................................... 27

FIGURE 3-4 RGMII TIMING ........................................................................................................................................ 28

FIGURE 3-5 MII TIMING ............................................................................................................................................. 29

FIGURE 3-6 RVMII TIMING ......................................................................................................................................... 30

FIGURE 3-7 SPI TIMING ............................................................................................................................................. 31

FIGURE 3-8 I2S TIMING ............................................................................................................................................. 32

FIGURE 3-9 PCM TIMING ........................................................................................................................................... 33

FIGURE 3-10 I2C TIMING ........................................................................................................................................... 33

FIGURE 3-11 SDIO TIMING ........................................................................................................................................ 34

FIGURE 3-12 NAND FLASH COMMAND TIMING ............................................................................................................. 35

FIGURE 3-13 NAND FLASH ADDRESS LATCH TIMING ....................................................................................................... 35

FIGURE 3-14 NAND FLASH WRITE TIMING ................................................................................................................... 36

FIGURE 3-15 NAND FLASH READ TIMING ..................................................................................................................... 36

FIGURE 3-16 POWER ON SEQUENCE ............................................................................................................................ 38

FIGURE 4-1 PACKAGE DIMENSION ................................................................................................................................ 39

FIGURE 4-2 REFLOW PROFILE ....................................................................................................................................... 41

FIGURE 4-3 TOP MARKING .......................................................................................................................................... 41

FOR stonexu@ zioncom.net USE ONLY

MEDIATEK CONFIDENTIAL

MT7621A_Data_Sheet_v0.4

loginid=stonexu@zioncom.net,time=2014-05-29 11:44:05,ip=183.16.164.220,doctitle=MT7621A_Datasheet_v0_4.docx,company=Zioncom Technology Co.LTD(吉翁)_RLT

Page 5 of 45

�

MT7621A

Network Processor

List of Tables

TABLE 1-1 MAIN FEATURES ........................................................................................................................................... 7

TABLE 2-1 BALL MAP .................................................................................................................................................. 9

TABLE 2-2 PIN DESCRIPTION ....................................................................................................................................... 10

TABLE 2-3 GPIO PIN SHARE ....................................................................................................................................... 17

TABLE 2-4 UART_1 PIN SHARE ................................................................................................................................... 18

TABLE 2-5 UART_2 PIN SHARE ................................................................................................................................... 18

TABLE 2-6 UART_3 PIN SHARE ................................................................................................................................... 18

TABLE 2-7 RGMII PIN SHARE ...................................................................................................................................... 19

TABLE 2-8 WDT_RST PIN SHARE ................................................................................................................................ 19

TABLE 2-9PERST_N PIN SHARE .................................................................................................................................. 19

TABLE 2-10 MDC/MDIO PIN SHARE ........................................................................................................................... 19

TABLE 2-11 NAND PIN SHARE .................................................................................................................................... 20

TABLE 2-12 STRAPPING .............................................................................................................................................. 23

TABLE 3-1 ABSOLUTE MAXIMUM RATINGS .................................................................................................................... 24

TABLE 3-2 RECOMMENDED OPERATING RANGE .............................................................................................................. 24

TABLE 3-3 DC CHARACTERISTICS .................................................................................................................................. 24

TABLE 3-4 THERMAL CHARACTERISTICS ......................................................................................................................... 25

TABLE 3-5 CURRENT CONSUMPTION ............................................................................................................................. 25

TABLE 3-6 EXTERNAL XTAL SPECIFICATIONS .................................................................................................................... 25

TABLE 3-7 DDR2 SDRAM INTERFACE DIAGRAM KEY ...................................................................................................... 27

TABLE 3-8 RGMII INTERFACE DIAGRAM KEY .................................................................................................................. 28

TABLE 3-9 MII INTERFACE DIAGRAM KEY ...................................................................................................................... 29

TABLE 3-10 RVMII INTERFACE DIAGRAM KEY ................................................................................................................ 30

TABLE 3-11 SPI INTERFACE DIAGRAM KEY ..................................................................................................................... 31

TABLE 3-12 I2S INTERFACE DIAGRAM KEY ..................................................................................................................... 32

TABLE 3-13 PCM INTERFACE DIAGRAM KEY .................................................................................................................. 33

TABLE 3-14 I2S INTERFACE DIAGRAM KEY ..................................................................................................................... 33

TABLE 3-15 SDIO INTERFACE DIAGRAM KEY .................................................................................................................. 34

TABLE 3-16 NAND INTERFACE DIAGRAM KEY ................................................................................................................ 36

TABLE 3-17 POWER ON SEQUENCE DIAGRAM KEY .......................................................................................................... 38

TABLE 4-1 PACKAGE DIAGRAM KEY .............................................................................................................................. 40

FOR stonexu@ zioncom.net USE ONLY

MEDIATEK CONFIDENTIAL

MT7621A_Data_Sheet_v0.4

loginid=stonexu@zioncom.net,time=2014-05-29 11:44:05,ip=183.16.164.220,doctitle=MT7621A_Datasheet_v0_4.docx,company=Zioncom Technology Co.LTD(吉翁)_RLT

Page 6 of 45

�

DRAM Controller

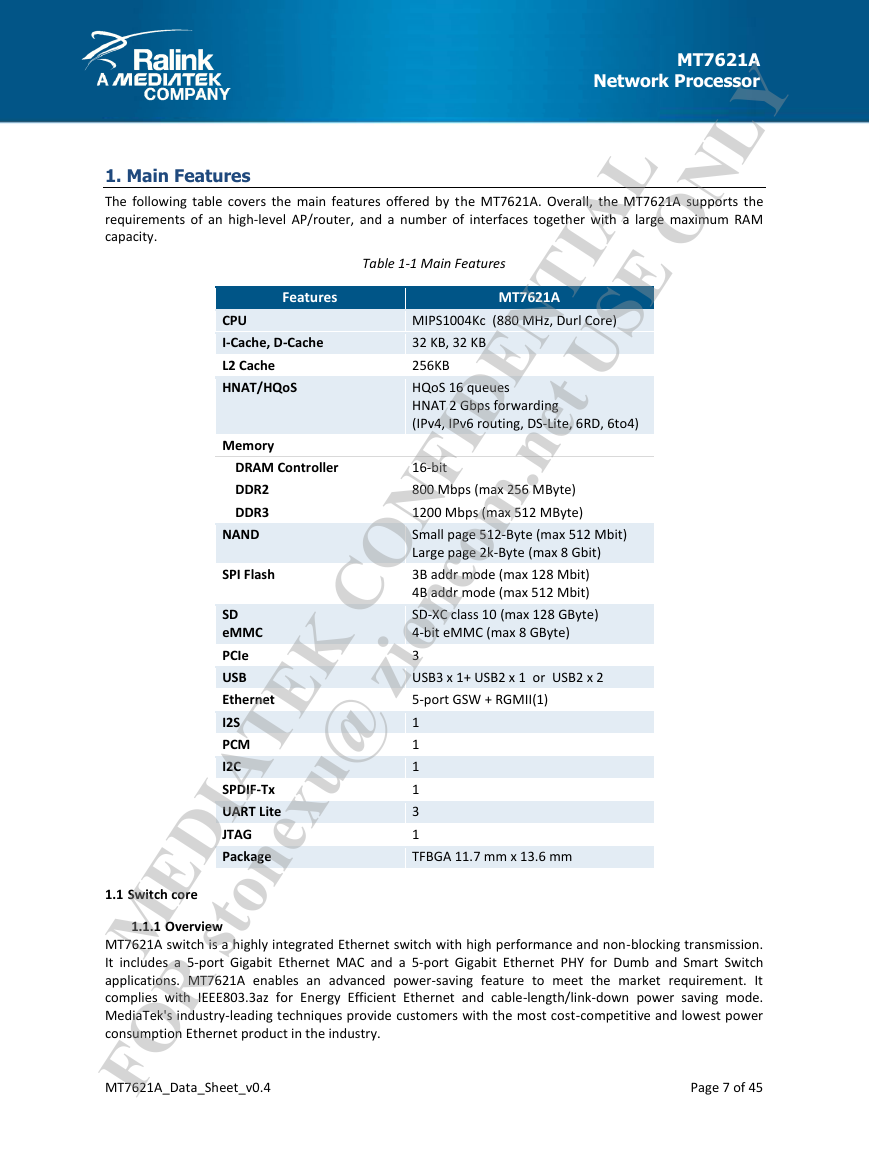

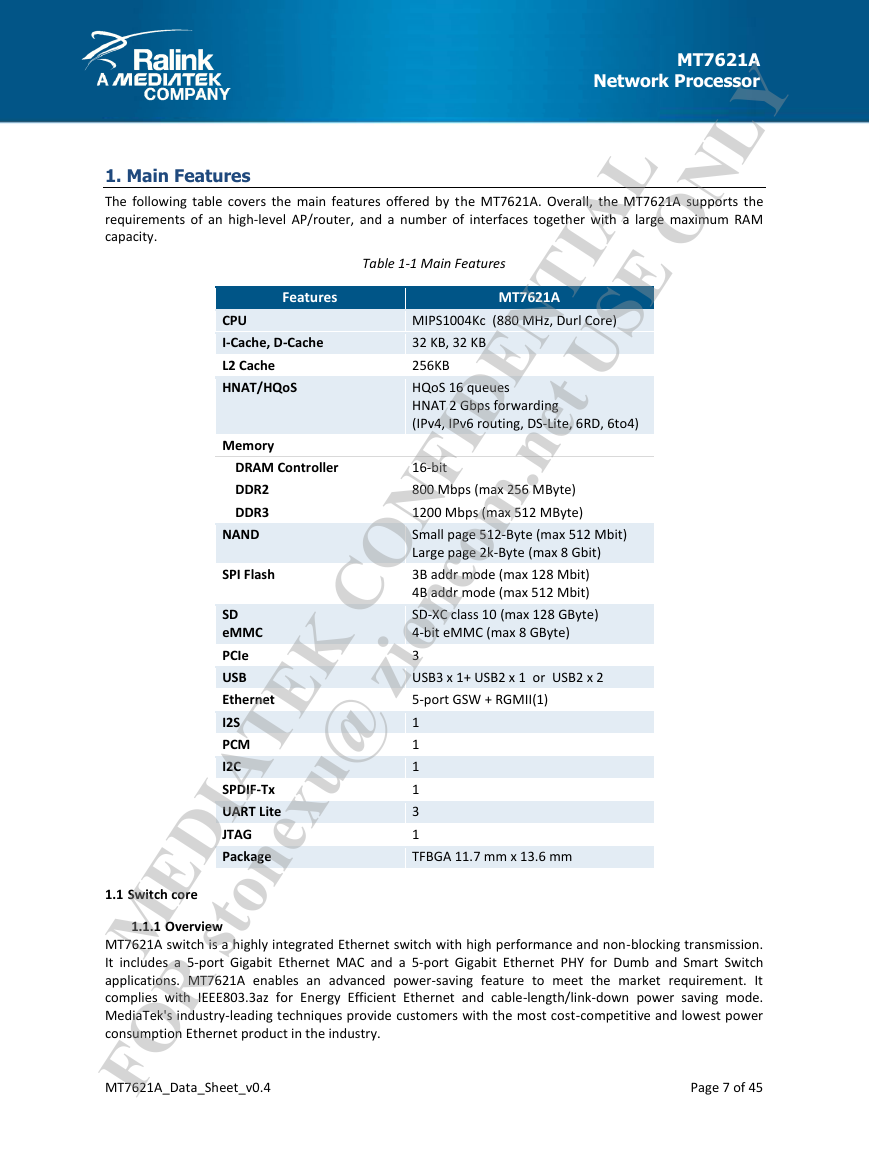

Table 1-1 Main Features

1. Main Features

256KB

16-bit

Features

MT7621A

Memory

DDR2

DDR3

NAND

SPI Flash

800 Mbps (max 256 MByte)

1200 Mbps (max 512 MByte)

MT7621A

Network Processor

MIPS1004Kc (880 MHz, Durl Core)

32 KB, 32 KB

CPU

I-Cache, D-Cache

L2 Cache

HNAT/HQoS

HQoS 16 queues

HNAT 2 Gbps forwarding

(IPv4, IPv6 routing, DS-Lite, 6RD, 6to4)

The following table covers the main features offered by the MT7621A. Overall, the MT7621A supports the

requirements of an high-level AP/router, and a number of interfaces together with a large maximum RAM

capacity.

FOR stonexu@ zioncom.net USE ONLY

MEDIATEK CONFIDENTIAL

MT7621A switch is a highly integrated Ethernet switch with high performance and non-blocking transmission.

It includes a 5-port Gigabit Ethernet MAC and a 5-port Gigabit Ethernet PHY for Dumb and Smart Switch

applications. MT7621A enables an advanced power-saving feature to meet the market requirement. It

complies with IEEE803.3az for Energy Efficient Ethernet and cable-length/link-down power saving mode.

MediaTek's industry-leading techniques provide customers with the most cost-competitive and lowest power

consumption Ethernet product in the industry.

SD

eMMC

PCIe

USB

Ethernet

I2S

PCM

I2C

SPDIF-Tx

UART Lite

JTAG

Package

Small page 512-Byte (max 512 Mbit)

Large page 2k-Byte (max 8 Gbit)

SD-XC class 10 (max 128 GByte)

4-bit eMMC (max 8 GByte)

3B addr mode (max 128 Mbit)

4B addr mode (max 512 Mbit)

USB3 x 1+ USB2 x 1 or USB2 x 2

1.1 Switch core

1.1.1 Overview

5-port GSW + RGMII(1)

3

1

1

1

1

3

1

TFBGA 11.7 mm x 13.6 mm

MT7621A_Data_Sheet_v0.4

loginid=stonexu@zioncom.net,time=2014-05-29 11:44:05,ip=183.16.164.220,doctitle=MT7621A_Datasheet_v0_4.docx,company=Zioncom Technology Co.LTD(吉翁)_RLT

Page 7 of 45

�

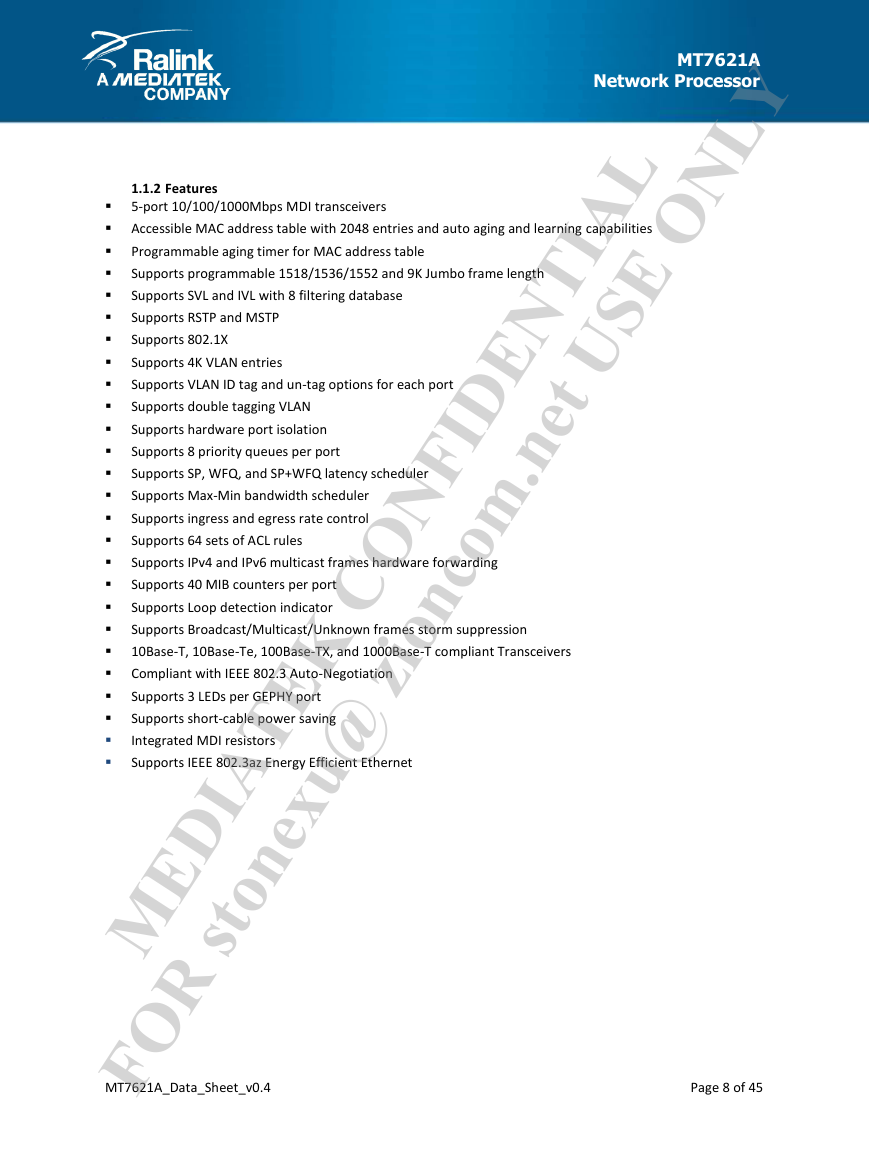

Supports RSTP and MSTP

Supports 802.1X

Supports 4K VLAN entries

Supports 64 sets of ACL rules

Supports double tagging VLAN

Supports hardware port isolation

Supports 8 priority queues per port

Supports ingress and egress rate control

Supports Max-Min bandwidth scheduler

Supports SVL and IVL with 8 filtering database

Programmable aging timer for MAC address table

Supports SP, WFQ, and SP+WFQ latency scheduler

Supports VLAN ID tag and un-tag options for each port

Supports IPv4 and IPv6 multicast frames hardware forwarding

Supports programmable 1518/1536/1552 and 9K Jumbo frame length

MT7621A

Network Processor

1.1.2 Features

5-port 10/100/1000Mbps MDI transceivers

Accessible MAC address table with 2048 entries and auto aging and learning capabilities

FOR stonexu@ zioncom.net USE ONLY

MEDIATEK CONFIDENTIAL

10Base-T, 10Base-Te, 100Base-TX, and 1000Base-T compliant Transceivers

Supports Broadcast/Multicast/Unknown frames storm suppression

Supports IEEE 802.3az Energy Efficient Ethernet

Compliant with IEEE 802.3 Auto-Negotiation

Supports 40 MIB counters per port

Supports short-cable power saving

Supports Loop detection indicator

Supports 3 LEDs per GEPHY port

Integrated MDI resistors

MT7621A_Data_Sheet_v0.4

loginid=stonexu@zioncom.net,time=2014-05-29 11:44:05,ip=183.16.164.220,doctitle=MT7621A_Datasheet_v0_4.docx,company=Zioncom Technology Co.LTD(吉翁)_RLT

Page 8 of 45

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc