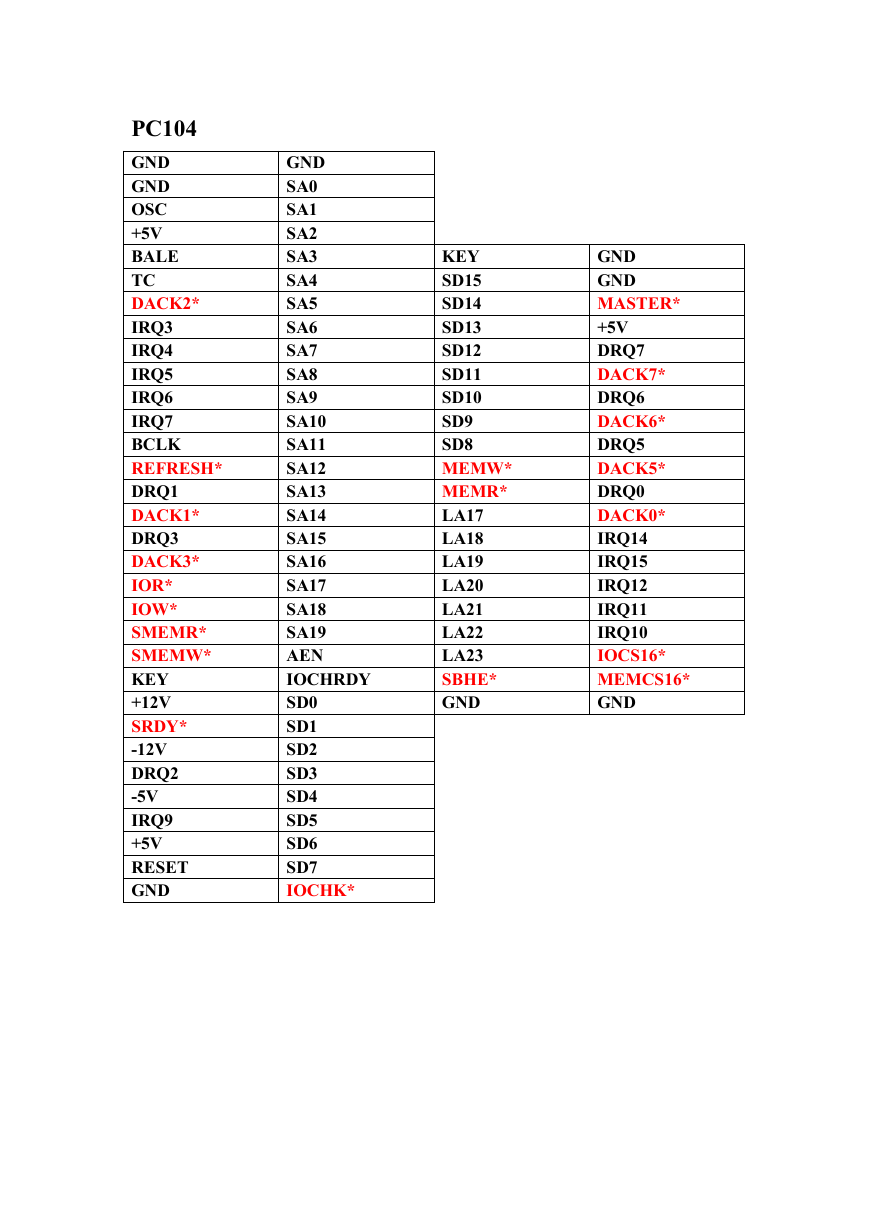

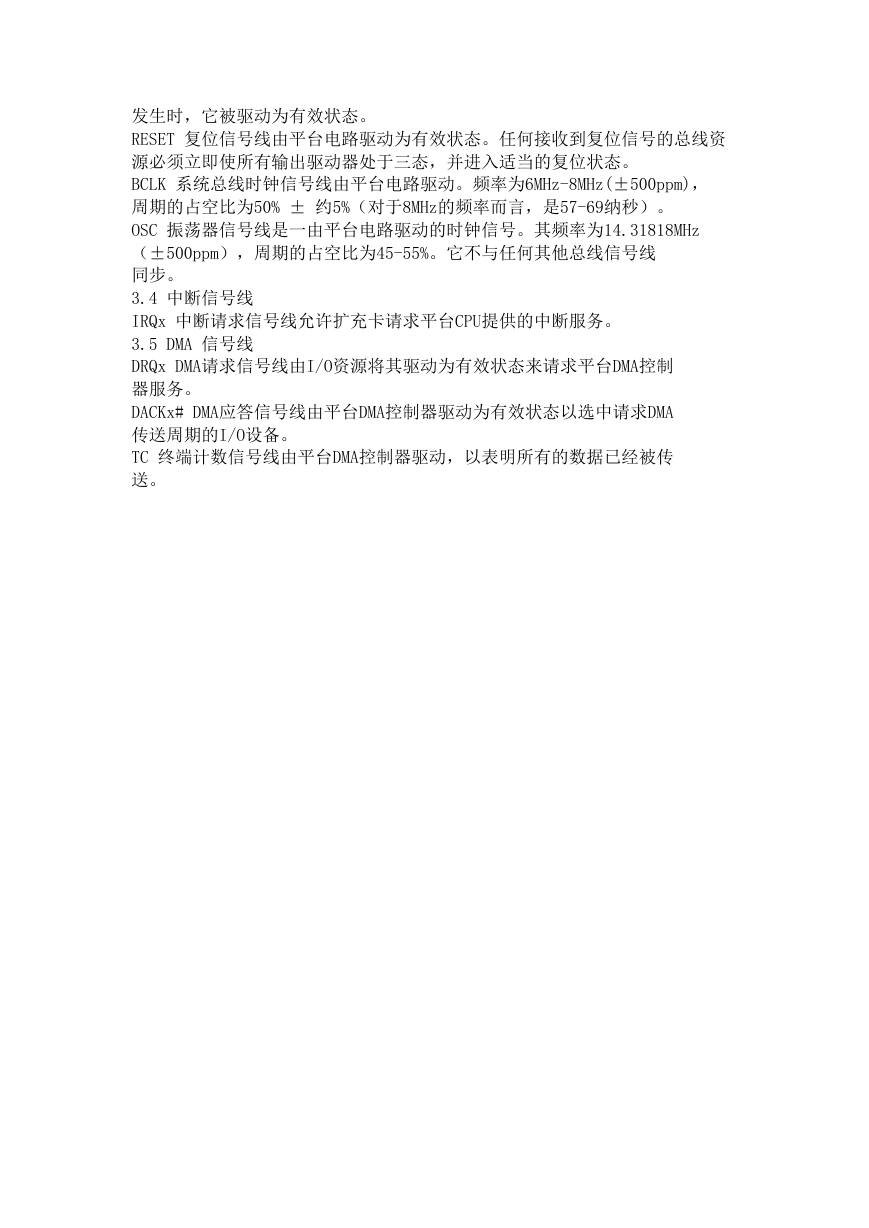

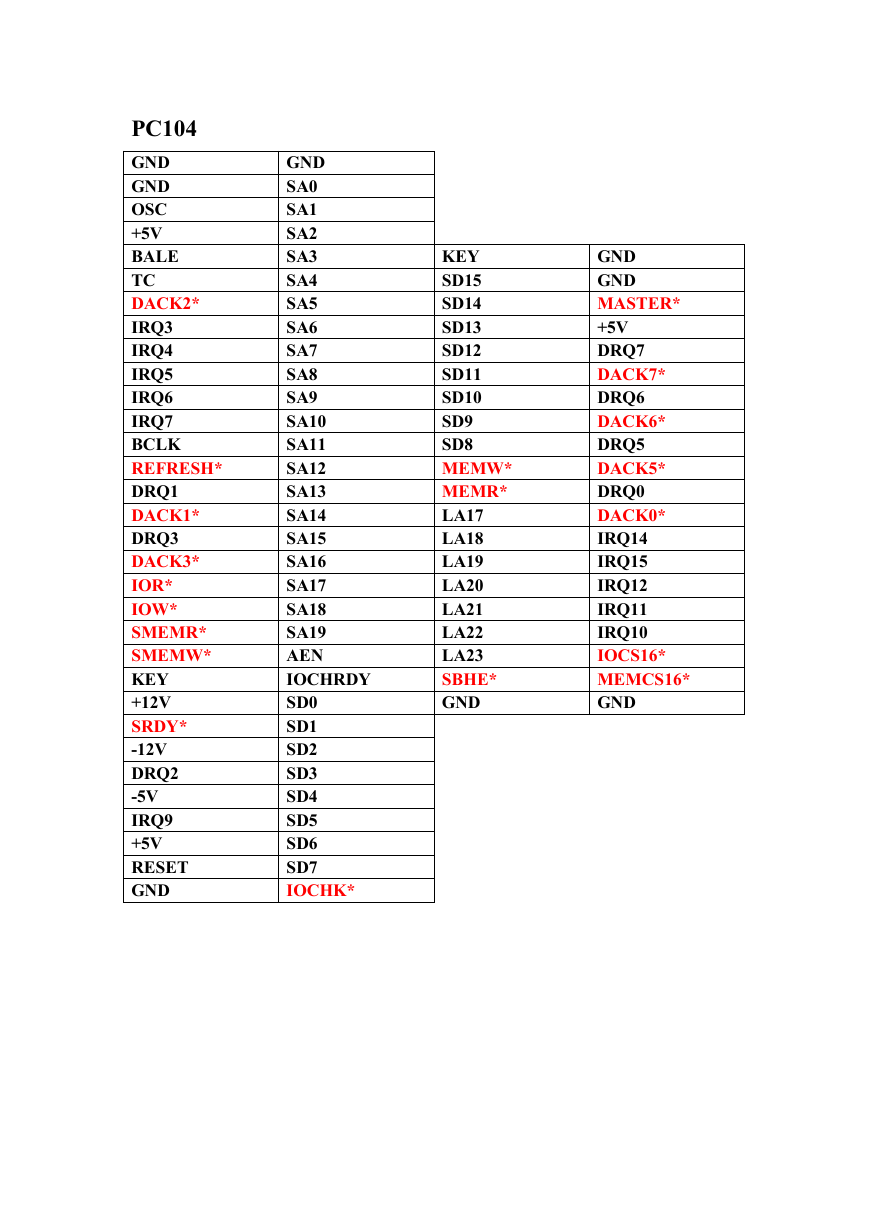

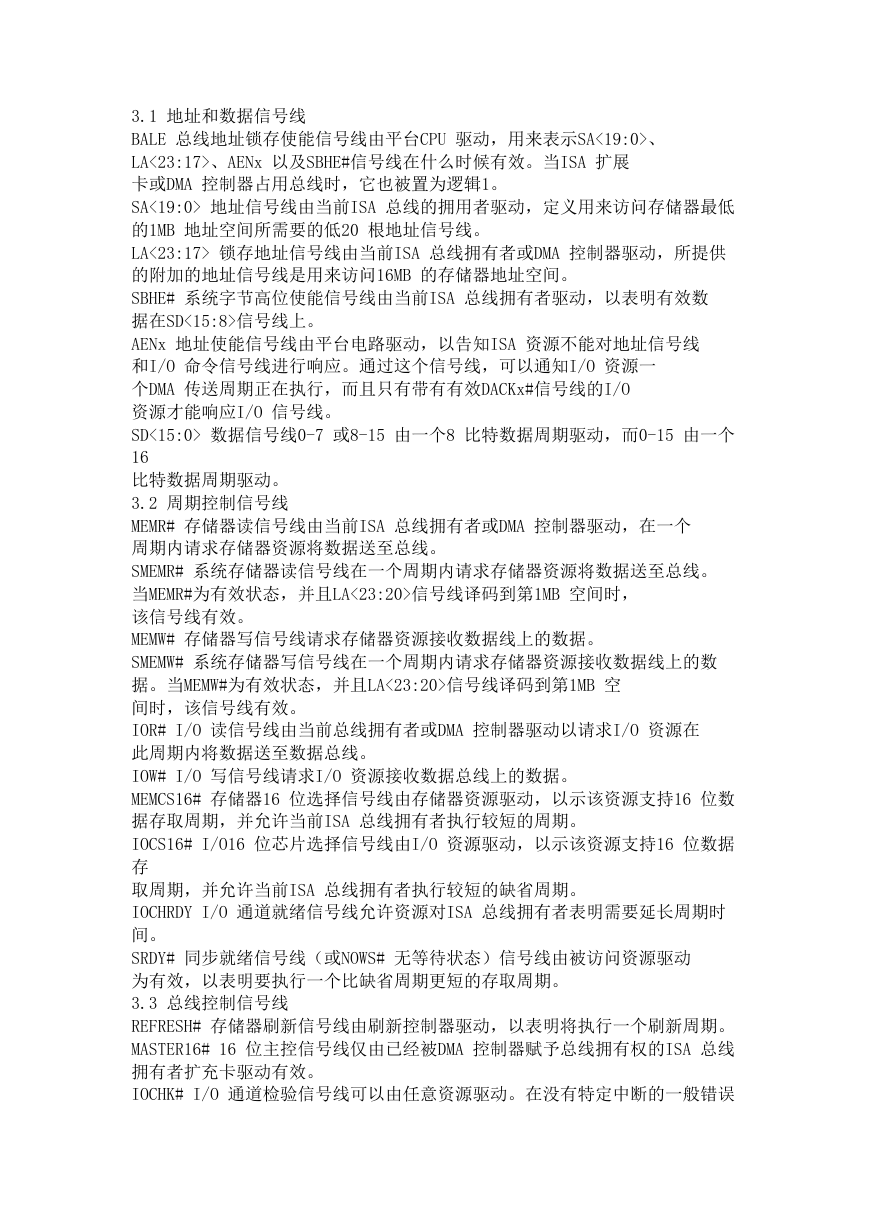

PC104

GND

GND

OSC

+5V

BALE

TC

DACK2*

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

BCLK

REFRESH*

DRQ1

DACK1*

DRQ3

DACK3*

IOR*

IOW*

SMEMR*

SMEMW*

KEY

+12V

SRDY*

-12V

DRQ2

-5V

IRQ9

+5V

RESET

GND

GND

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

SA19

AEN

IOCHRDY

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

IOCHK*

KEY

SD15

SD14

SD13

SD12

SD11

SD10

SD9

SD8

MEMW*

MEMR*

LA17

LA18

LA19

LA20

LA21

LA22

LA23

SBHE*

GND

GND

GND

MASTER*

+5V

DRQ7

DACK7*

DRQ6

DACK6*

DRQ5

DACK5*

DRQ0

DACK0*

IRQ14

IRQ15

IRQ12

IRQ11

IRQ10

IOCS16*

MEMCS16*

GND

�

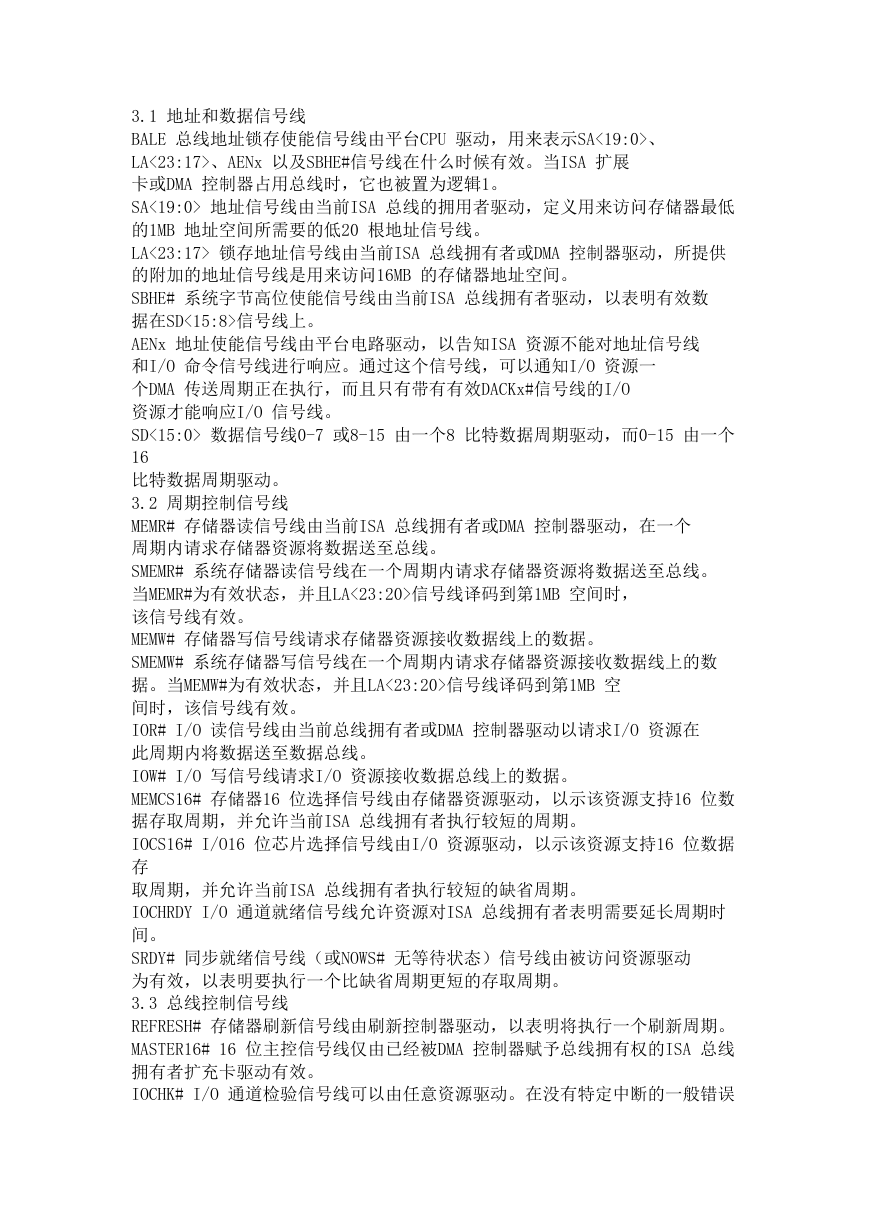

3.1 地址和数据信号线

BALE 总线地址锁存使能信号线由平台CPU 驱动,用来表示SA<19:0>、

LA<23:17>、AENx 以及SBHE#信号线在什么时候有效。当ISA 扩展

卡或DMA 控制器占用总线时,它也被置为逻辑1。

SA<19:0> 地址信号线由当前ISA 总线的拥用者驱动,定义用来访问存储器最低

的1MB 地址空间所需要的低20 根地址信号线。

LA<23:17> 锁存地址信号线由当前ISA 总线拥有者或DMA 控制器驱动,所提供

的附加的地址信号线是用来访问16MB 的存储器地址空间。

SBHE# 系统字节高位使能信号线由当前ISA 总线拥有者驱动,以表明有效数

据在SD<15:8>信号线上。

AENx 地址使能信号线由平台电路驱动,以告知ISA 资源不能对地址信号线

和I/O 命令信号线进行响应。通过这个信号线,可以通知I/O 资源一

个DMA 传送周期正在执行,而且只有带有有效DACKx#信号线的I/O

资源才能响应I/O 信号线。

SD<15:0> 数据信号线0-7 或8-15 由一个8 比特数据周期驱动,而0-15 由一个

16

比特数据周期驱动。

3.2 周期控制信号线

MEMR# 存储器读信号线由当前ISA 总线拥有者或DMA 控制器驱动,在一个

周期内请求存储器资源将数据送至总线。

SMEMR# 系统存储器读信号线在一个周期内请求存储器资源将数据送至总线。

当MEMR#为有效状态,并且LA<23:20>信号线译码到第1MB 空间时,

该信号线有效。

MEMW# 存储器写信号线请求存储器资源接收数据线上的数据。

SMEMW# 系统存储器写信号线在一个周期内请求存储器资源接收数据线上的数

据。当MEMW#为有效状态,并且LA<23:20>信号线译码到第1MB 空

间时,该信号线有效。

IOR# I/O 读信号线由当前总线拥有者或DMA 控制器驱动以请求I/O 资源在

此周期内将数据送至数据总线。

IOW# I/O 写信号线请求I/O 资源接收数据总线上的数据。

MEMCS16# 存储器16 位选择信号线由存储器资源驱动,以示该资源支持16 位数

据存取周期,并允许当前ISA 总线拥有者执行较短的周期。

IOCS16# I/O16 位芯片选择信号线由I/O 资源驱动,以示该资源支持16 位数据

存

取周期,并允许当前ISA 总线拥有者执行较短的缺省周期。

IOCHRDY I/O 通道就绪信号线允许资源对ISA 总线拥有者表明需要延长周期时

间。

SRDY# 同步就绪信号线(或NOWS# 无等待状态)信号线由被访问资源驱动

为有效,以表明要执行一个比缺省周期更短的存取周期。

3.3 总线控制信号线

REFRESH# 存储器刷新信号线由刷新控制器驱动,以表明将执行一个刷新周期。

MASTER16# 16 位主控信号线仅由已经被DMA 控制器赋予总线拥有权的ISA 总线

拥有者扩充卡驱动有效。

IOCHK# I/O 通道检验信号线可以由任意资源驱动。在没有特定中断的一般错误

�

发生时,它被驱动为有效状态。

RESET 复位信号线由平台电路驱动为有效状态。任何接收到复位信号的总线资

源必须立即使所有输出驱动器处于三态,并进入适当的复位状态。

BCLK 系统总线时钟信号线由平台电路驱动。频率为6MHz-8MHz(±500ppm),

周期的占空比为50% ± 约5%(对于8MHz的频率而言,是57-69纳秒)。

OSC 振荡器信号线是一由平台电路驱动的时钟信号。其频率为14.31818MHz

(±500ppm),周期的占空比为45-55%。它不与任何其他总线信号线

同步。

3.4 中断信号线

IRQx 中断请求信号线允许扩充卡请求平台CPU提供的中断服务。

3.5 DMA 信号线

DRQx DMA请求信号线由I/O资源将其驱动为有效状态来请求平台DMA控制

器服务。

DACKx# DMA应答信号线由平台DMA控制器驱动为有效状态以选中请求DMA

传送周期的I/O设备。

TC 终端计数信号线由平台DMA控制器驱动,以表明所有的数据已经被传

送。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc