About this Document

Important Notice

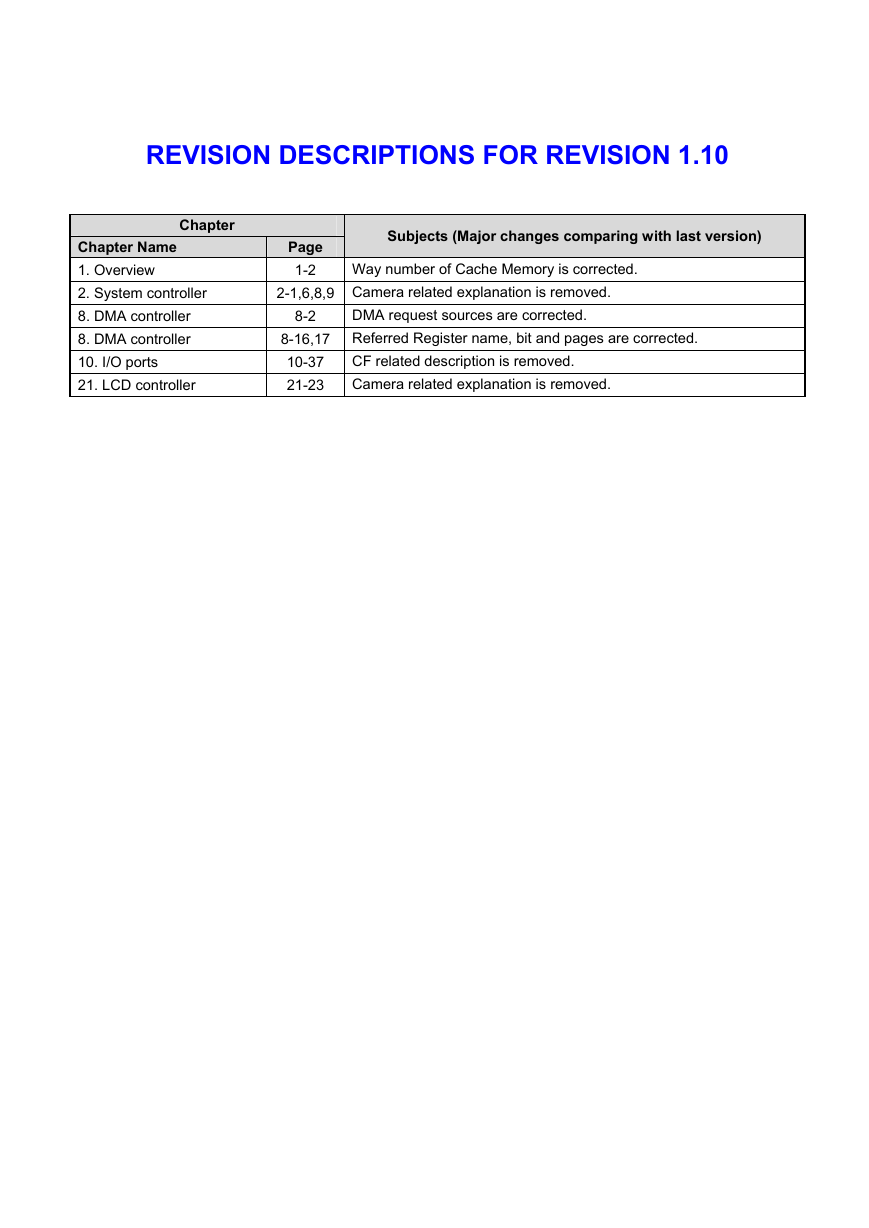

Notification of Revisions

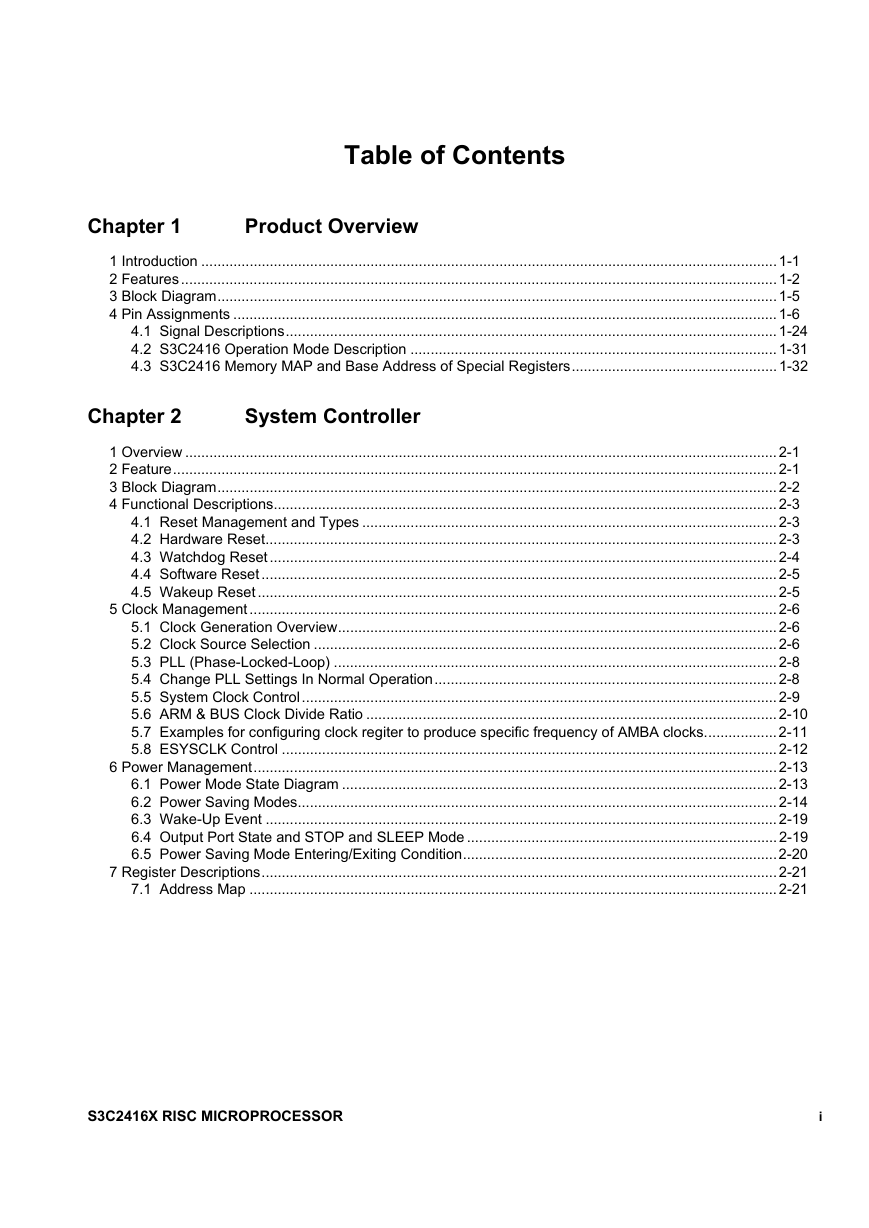

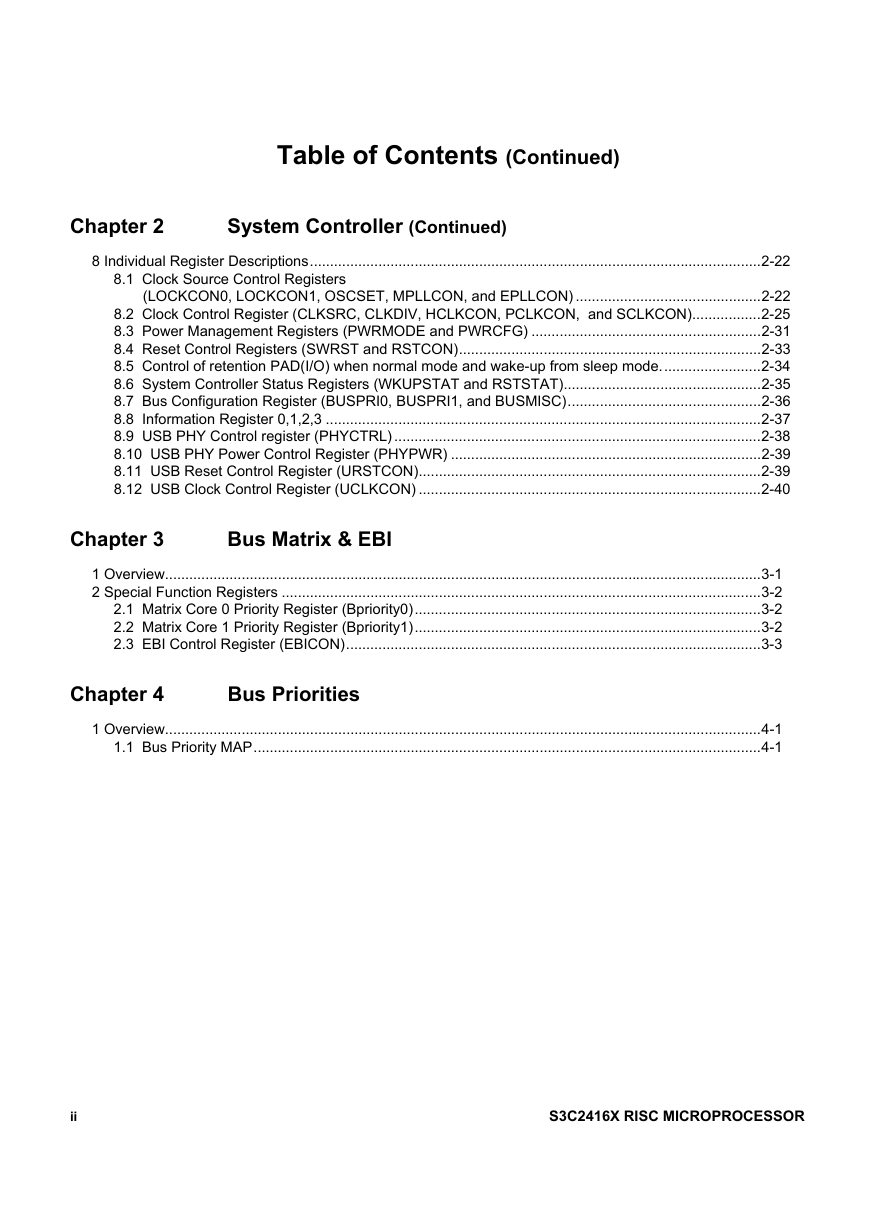

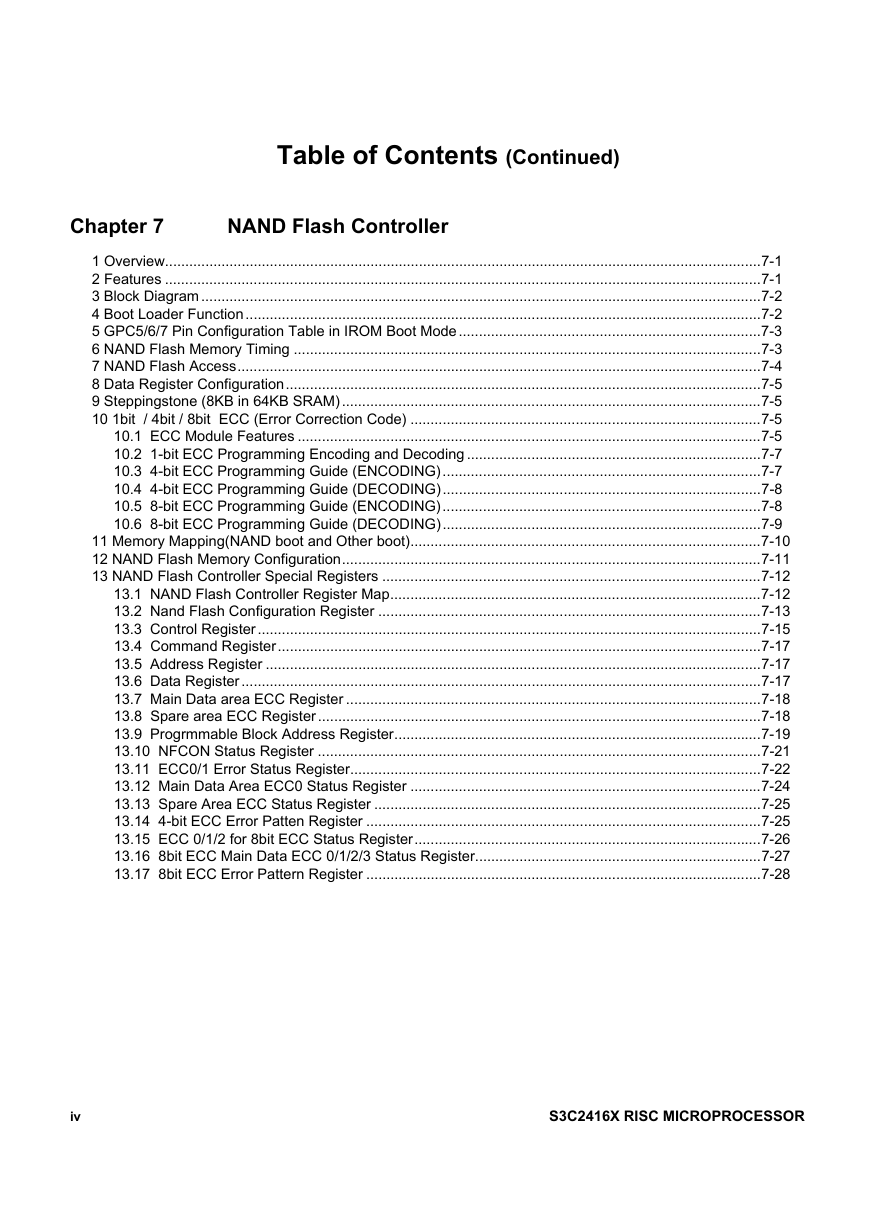

Table of Contents

Lists of Figures

Lists of Tables

01-Overview

1 INTRODUCTION

2 FEATURES

3 BLOCK DIAGRAM

4 PIN ASSIGNMENTS

02-SYSCON

1 OVERVIEW

2 FEATURE

3 BLOCK DIAGRAM

4 FUNCTIONAL DESCRIPTIONS

5 CLOCK MANAGEMENT

6 POWER MANAGEMENT

7 REGISTER DESCRIPTIONS

8 INDIVIDUAL REGISTER DESCRIPTIONS

03-MATRIX & EBI

1 OVERVIEW

2 SPECIAL FUNCTION REGISTERS

04-Bus Priority

1 OVERVIEW

05-SMC

1 OVERVIEW

2 FEATURE

3 BLOCK DIAGRAM

4 SPECIAL REGISTERS

06-DRAMC

1 OVERVIEW

2 BLOCK DIAGRAM

3 MOBILE DRAM INITIALIZATION SEQUENCE

07-Nand Flash

1 OVERVIEW

2 FEATURES

3 BLOCK DIAGRAM

4 BOOT LOADER FUNCTION

5 GPC5/6/7 PIN CONFIGURATION TABLE IN IROM BOOT MODE

6 NAND FLASH MEMORY TIMING

7 NAND FLASH ACCESS

8 DATA REGISTER CONFIGURATION

9 STEPPINGSTONE (8KB IN 64KB SRAM)

10 1BIT / 4BIT / 8BIT ECC (ERROR CORRECTION CODE)

11 MEMORY MAPPING(NAND BOOT AND OTHER BOOT)

12 NAND FLASH MEMORY CONFIGURATION

13 NAND FLASH CONTROLLER SPECIAL REGISTERS

08-DMA controller

1 OVERVIEW

2 DMA REQUEST SOURCES

3 DMA OPERATION

4 DMA SPECIAL REGISTERS

09-Interrupt controller

1 OVERVIEW

2 INTERRUPT CONTROLLER SPECIAL REGISTERS

10-IOport

1 OVERVIEW

2 PORT CONTROL DESCRIPTIONS

Caution

3 I/O PORT CONTROL REGISTER

4 GPIO ALIVE & SLEEP PART

11-Watchdog

1 OVERVIEW

2 WATCHDOG TIMER OPERATION

3 WATCHDOG TIMER SPECIAL REGISTERS

12-PWM Timer

1 OVERVIEW

2 PWM TIMER OPERATION

3 PWM TIMER CONTROL REGISTERS

13-RTC

1 OVERVIEW

NOTES

14-UART

1 OVERVIEW

2 BLOCK DIAGRAM

3 UART SPECIAL REGISTERS

15-USB HOST Controller

1 OVERVIEW

16-USB 2.0 Device

1 OVERVIEW

2 BLOCK DIAGRAM

3 TO ACTIVATE USB PORT1 FOR USB 2.0 FUNCTION

4 SIE (SERIAL INTERFACE ENGINE)

5 UPH (UNIVERSAL PROTOCOL HANDLER)

6 UTMI (USB 2.0 TRANSCEIVER MACROCELL INTERFACE)

7 USB 2.0 FUNCTION CONTROLLER SPECIAL REGISTERS

8 REGISTERS

17-IIC bus interface

1 OVERVIEW

2 IIC-BUS INTERFACE SPECIAL REGISTERS

18-2D

1 INTRODUCTION

2 COLOR FORMAT CONVERSION

3 COMMAND FIFO

4 RENDERING PIPELINE

5 REGISTER DESCRIPTIONS

19-HSSPI

1 OVERVIEW

2 FEATURES

3 SIGNAL DESCRIPTIONS

4 OPERATION

5 SPECIAL FUNCTION REGISTER DESCRIPTIONS

20-HSMMC

1 OVERVIEW

2 FEATURES

3 BLOCK DIAGRAM

4 SEQUENCE

5 SDI SPECIAL REGISTERS

21-LCD controller

1 OVERVIEW

2 FUNCTIONAL DESCRIPTION

3 WINDOW BLENDING

4 VTIME CONTROLLER OPERATION

5 VIRTUAL DISPLAY

6 RGB INTERFACE I/O

7 LCD CPU INTERFACE I/O (i80-SYSTEM I/F)

8 PROGRAMMER’S MODEL

22-TSADC

1 OVERVIEW

2 ADC & TOUCH SCREEN INTERFACE OPERATION

3 ADC AND TOUCH SCREEN INTERFACE SPECIAL REGISTERS

23-IIS Multi Audio Interface

1 OVERVIEW

2 FEATURE

3 SIGNALS

4 BLOCK DIAGRAM

5 FUNCTIONAL DESCRIPTIONS

6 AUDIO SERIAL DATA FORMAT

7 PROGRAMMING GUIDE

8 IIS-BUS INTERFACE SPECIAL REGISTERS

24-AC97 Controller

1 OVERVIEW

2 AC97 CONTROLLER OPERATION

3 OPERATION FLOW CHART

4 AC-LINK DIGITAL INTERFACE PROTOCOL

Slot 0: Tag Phase

Slot 1: Command Address Port

Slot 2: Command Data Port

Slot 3: PCM Playback Left channel

Slot 4: PCM Playback Right channel

Slot 0: Tag Phase

Slot 1: Status Address Port/SLOTREQ bits

Slot 2: Status Data Port

Slot 3: PCM Record Left channel

Slot 4: PCM Right channel audio

Slot 6: Microphone Record Data

5 AC97 POWER-DOWN

6 CODEC RESET

7 AC97 CONTROLLER STATE DIAGRAM

8 AC97 CONTROLLER SPECIAL REGISTERS

25-PCM Audio Interface

1 OVERVIEW

2 PCM AUDIO INTERFACE

3 PCM TIMING

26-ELECTRICAL DATA

1 ABSOLUTE MAXIMUM RATINGS

2 RECOMMENDED OPERATING CONDITIONS

3 D.C. ELECTRICAL CHARACTERISTICS

4 A.C. ELECTRICAL CHARACTERISTICS

27-MECHANICAL DATA

1 PACKAGE DIMENSIONS

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc