基于 FPGA 的十通道逻辑分析仪设计教程

小梅哥编写, 可适用于芯航线 FPGA 学习套件, 作者保留一切所有权

2016 年 7 月 11 日星期一

设计初衷

基于 FPGA 的十通道逻辑分析仪为芯航线为用户编写的精品例程,旨在通过例程给大家展示

一个原理正确、代码规范、架构科学、层次清晰的示例设计方案,本实例中的所有模块均由

小梅哥亲自编写并仿真测试通过,大家可以直接提取并用于自己的设计中。

基本功能介绍

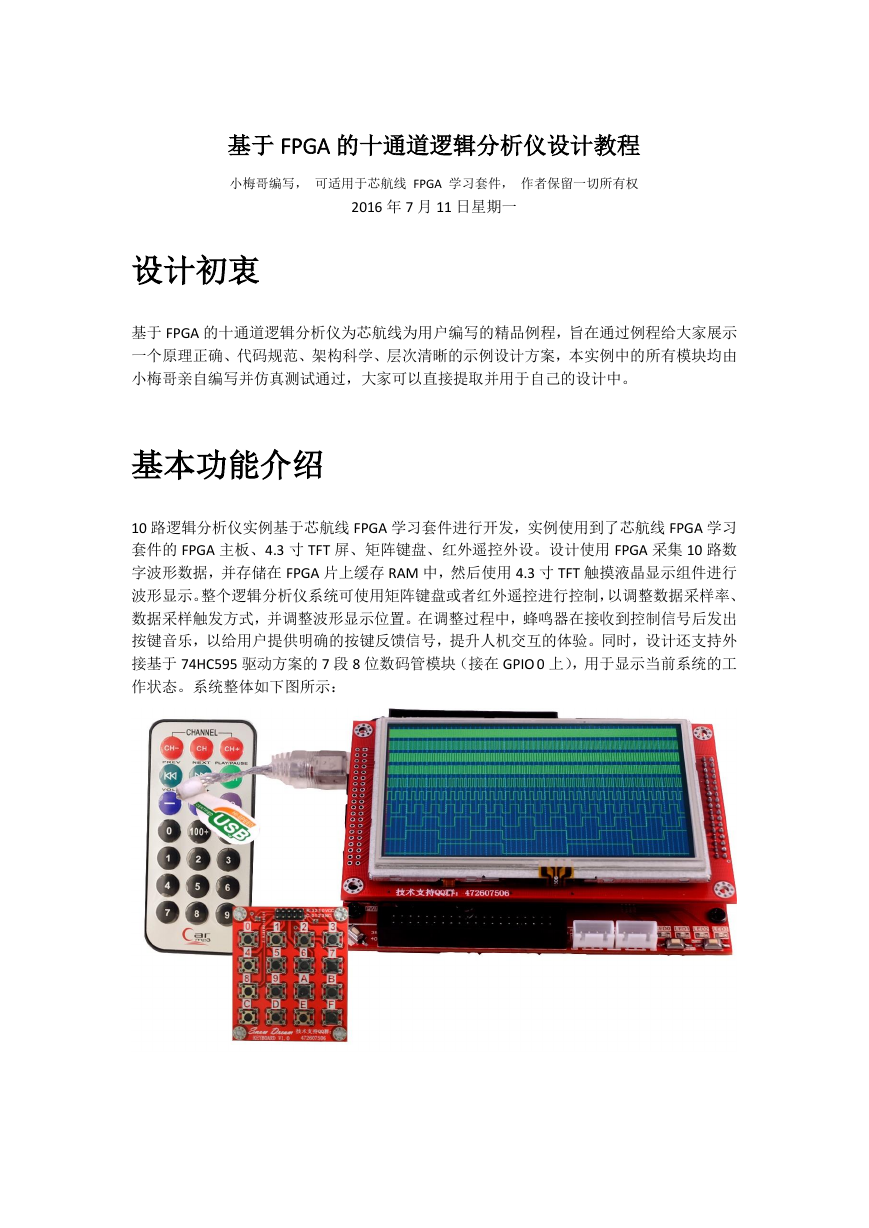

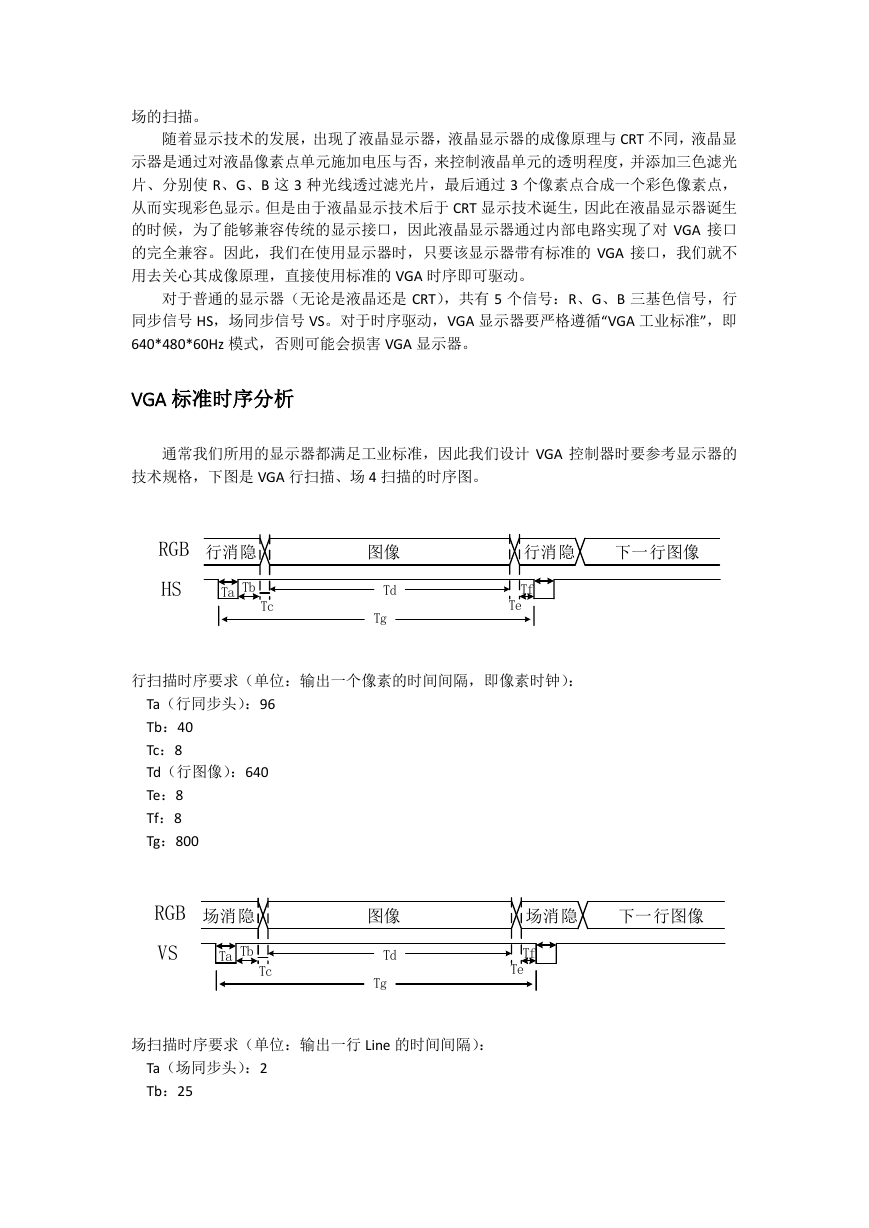

10 路逻辑分析仪实例基于芯航线 FPGA 学习套件进行开发,实例使用到了芯航线 FPGA 学习

套件的 FPGA 主板、4.3 寸 TFT 屏、矩阵键盘、红外遥控外设。设计使用 FPGA 采集 10 路数

字波形数据,并存储在 FPGA 片上缓存 RAM 中,然后使用 4.3 寸 TFT 触摸液晶显示组件进行

波形显示。整个逻辑分析仪系统可使用矩阵键盘或者红外遥控进行控制,以调整数据采样率、

数据采样触发方式,并调整波形显示位置。在调整过程中,蜂鸣器在接收到控制信号后发出

按键音乐,以给用户提供明确的按键反馈信号,提升人机交互的体验。同时,设计还支持外

接基于 74HC595 驱动方案的 7 段 8 位数码管模块(接在 GPIO 0 上),用于显示当前系统的工

作状态。系统整体如下图所示:

�

基本组件设计

矩阵键盘驱动设计

矩阵键盘原理与驱动设计

本例中,矩阵键盘主要用于实现人机交互的控制信号输入部分,通过矩阵键盘输入控制

信号,来实现控制数据采样率、数据采样触发方式,并调整波形显示位置等功能,矩阵键盘

的具体设计思路和方案见《芯航线 FPGA 数字系统设计教程+实例解析》“芯航线 FPGA 数字

逻辑设计精品教程”部分的“FPGA 矩阵键盘驱动设计与验证”小节,本实例直接使用该小节

设计的矩阵键盘驱动模块,因此不再重复介绍。设计完成的矩阵键盘驱动模块如下图所示。

模块每个信号的功能简介如下。

端口类型

Input

Input

Input

端口名

Clk

Rst_n

描述

系统时钟 50MHz

系统复位,低有效

Key_Board_Row_i 矩阵键盘行控制线,按键未按下为高电平

Output

Key_Board_Col_o 矩阵键盘列控制线,驱动列信号为低,实现

Output

Output

Key_Value

Key_Flag

按键状态扫描,

输出键盘键值

按键检查成功标志信号,每当按键检测成

功,产生一个时钟周期的高脉冲

矩阵键盘驱动使用示例

在使用本模块时,只需要将 Clk 连接到系统时钟输入,Rst_n 连接到系统复位引脚/信号,

Key_Board_Row_i 和 Key_Board_Col_o 分别与矩阵键盘的行列引脚相连即可。然后每次当按

下一次按键,待本模块进行抖动滤除并确认得到了按键按下信息后,会在 Key_Value 端口上

输出当前检测到的按键值,并驱动 Key_Flag 信号产生一个时钟周期的高脉冲,其他模块在

使用矩阵键盘的扫描结果时,只需要在 Key_Flag 信号有效时(高脉冲期间)读取 Key_Value

的值,并根据 Key_Value 的值进行相应的操作即可,例如,使用矩阵键盘的 1、3、5、7 键

简单控制 4 个 LED 灯状态翻转的代码即可如下编写:

always@(posedge Clk or negedge Rst_n)

Key4x4_BoardClkRst_nKey_Board_Row_i[3:0]Key_Board_Col_o[3:0]Key_Value[3:0]Key_Flag�

if(!Rst_n) //复位时使 4 位 LED 全灭

LED <= 4'b1111;

else if(Key_Flag)begin //Key_Flag 高脉冲时有效

case(Key_Value)

4'd1:LED[0] <= ~LED[0];//按键 1,翻转 LED0

4'd3:LED[1] <= ~LED[1];//按键 3,翻转 LED1

4'd5:LED[2] <= ~LED[2];//按键 5,翻转 LED2

4'd7:LED[3] <= ~LED[3];//按键 7,翻转 LED3

default:LED <= LED; //其他按键,忽略,不对 LED 进行任何操作

endcase

end

红外遥控解码驱动设计

红外遥控解码与驱动设计

本例中,红外遥控作为另一个输入设备,实现与矩阵键盘相同的功能,即用于实现人机

交互的控制信号输入部分。通过红外遥控发射按键信号,并由 FPGA 解码红外接收器接收到

的红外按键信号,得到按键信息,然后根据按键信息来实现控制数据采样率、数据采样触发

方式,并调整波形显示位置等功能,红外遥控解码的具体设计思路和方案见《小梅哥 FPGA

设计思想与验证方法视频教程》“19_HT6221 红外遥控解码”一集视频教程,以及配套文档教

程,见《芯航线 FPGA 数字系统设计教程+实例解析》“FPGA 设计思想与验证方法视频教程

实验精讲手册”部分的“十九、 HT6221 红外遥控解码”小节,本实例直接使用该小节设计的

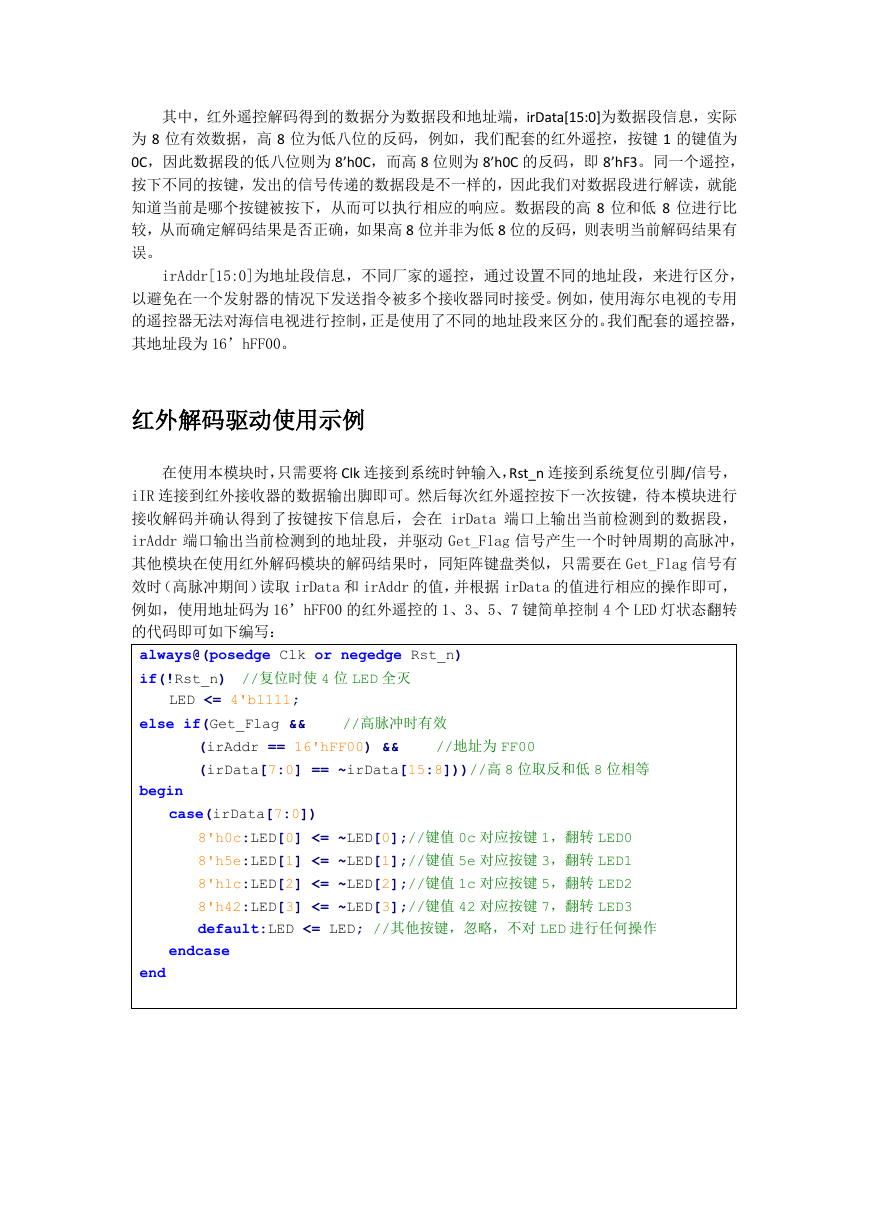

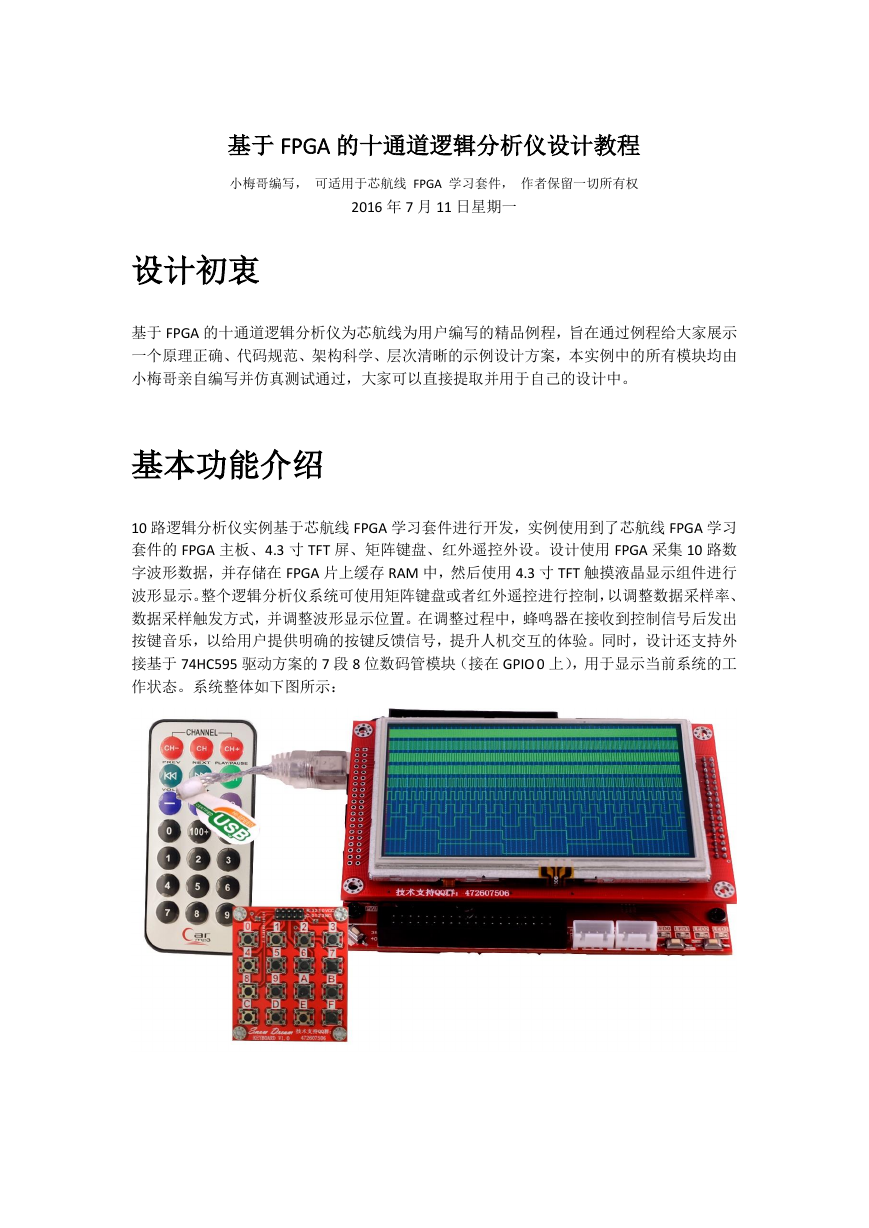

红外遥控解码模块,因此不再重复介绍。设计完成的矩阵键盘驱动模块如下图所示。

模块每个信号的功能简介如下。

端口类型

Input

Input

Input

Output

Output

Output

端口名

Clk50M

Rst_n

iIR

Get_Flag

irData

irAddr

描述

系统时钟 50MHz

系统复位,低有效

红外遥控接收器信号脚

红外解码成功标志信号,每当解码成功,该

信号产生一个时钟周期的高脉冲

红外解码得到的数据段,识别不同按键

红外解码得到的地址段,区分不同遥控器发

出的数据。

ir_decodeClk50MRst_nirAddr[15:0]irData[15:0]Get_FlagiIR�

其中,红外遥控解码得到的数据分为数据段和地址端,irData[15:0]为数据段信息,实际

为 8 位有效数据,高 8 位为低八位的反码,例如,我们配套的红外遥控,按键 1 的键值为

0C,因此数据段的低八位则为 8’h0C,而高 8 位则为 8’h0C 的反码,即 8’hF3。同一个遥控,

按下不同的按键,发出的信号传递的数据段是不一样的,因此我们对数据段进行解读,就能

知道当前是哪个按键被按下,从而可以执行相应的响应。数据段的高 8 位和低 8 位进行比

较,从而确定解码结果是否正确,如果高 8 位并非为低 8 位的反码,则表明当前解码结果有

误。

irAddr[15:0]为地址段信息,不同厂家的遥控,通过设置不同的地址段,来进行区分,

以避免在一个发射器的情况下发送指令被多个接收器同时接受。例如,使用海尔电视的专用

的遥控器无法对海信电视进行控制,正是使用了不同的地址段来区分的。我们配套的遥控器,

其地址段为 16’hFF00。

红外解码驱动使用示例

在使用本模块时,只需要将 Clk 连接到系统时钟输入,Rst_n 连接到系统复位引脚/信号,

iIR 连接到红外接收器的数据输出脚即可。然后每次红外遥控按下一次按键,待本模块进行

接收解码并确认得到了按键按下信息后,会在 irData 端口上输出当前检测到的数据段,

irAddr 端口输出当前检测到的地址段,并驱动 Get_Flag 信号产生一个时钟周期的高脉冲,

其他模块在使用红外解码模块的解码结果时,同矩阵键盘类似,只需要在 Get_Flag 信号有

效时(高脉冲期间)读取 irData 和 irAddr 的值,并根据 irData 的值进行相应的操作即可,

例如,使用地址码为 16’hFF00 的红外遥控的 1、3、5、7 键简单控制 4 个 LED 灯状态翻转

的代码即可如下编写:

always@(posedge Clk or negedge Rst_n)

if(!Rst_n) //复位时使 4 位 LED 全灭

LED <= 4'b1111;

else if(Get_Flag && //高脉冲时有效

(irAddr == 16'hFF00) && //地址为 FF00

(irData[7:0] == ~irData[15:8]))//高 8 位取反和低 8 位相等

begin

case(irData[7:0])

8'h0c:LED[0] <= ~LED[0];//键值 0c 对应按键 1,翻转 LED0

8'h5e:LED[1] <= ~LED[1];//键值 5e 对应按键 3,翻转 LED1

8'h1c:LED[2] <= ~LED[2];//键值 1c 对应按键 5,翻转 LED2

8'h42:LED[3] <= ~LED[3];//键值 42 对应按键 7,翻转 LED3

default:LED <= LED; //其他按键,忽略,不对 LED 进行任何操作

endcase

end

�

PS2 键盘驱动设计

PS2 键盘驱动设计

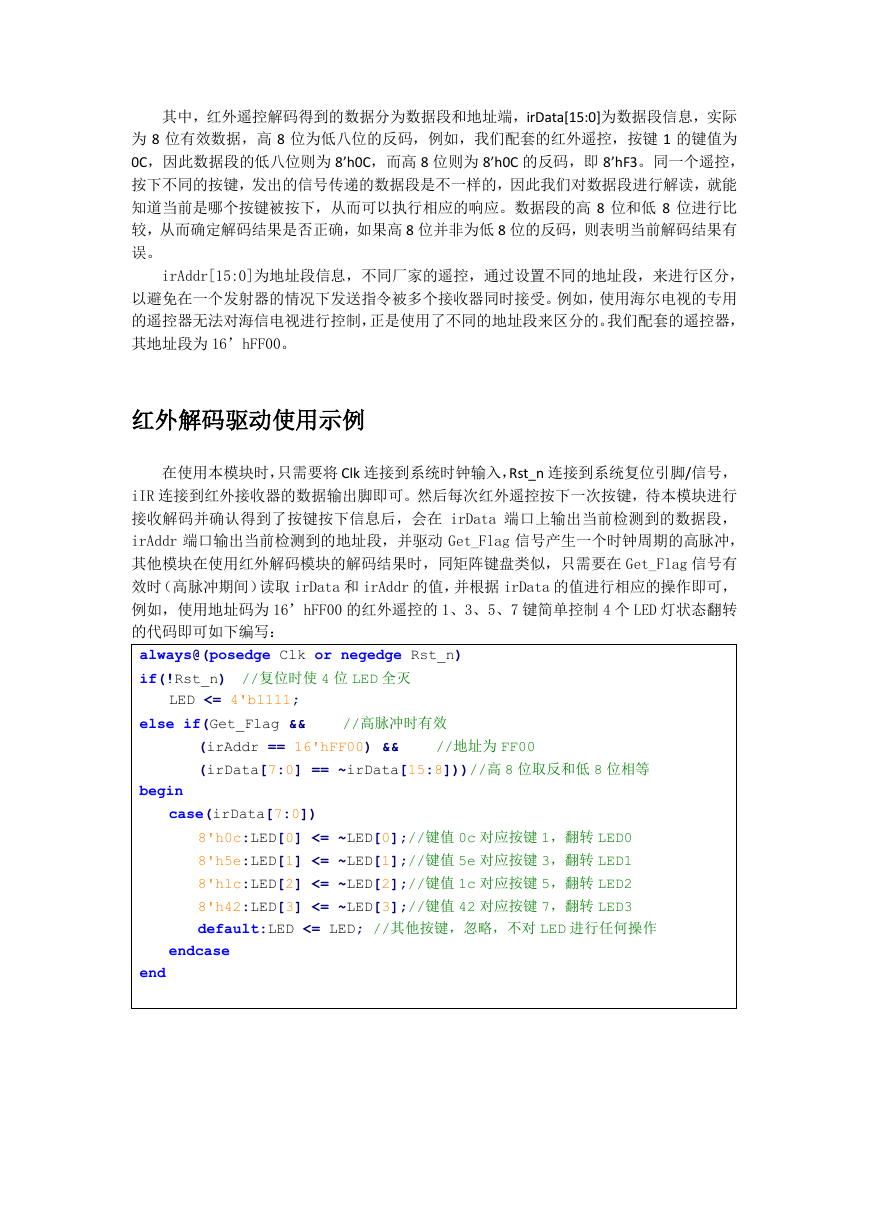

本例中,PS2 键盘作为第三个可选输入设备,实现与矩阵键盘、红外遥控相同的功能,

即用于实现人机交互的控制信号输入部分。使用时,如果开发板上外接了 PS2 键盘,那么按

下 PS2 键盘上对应按键,则 FPGA 对 PS2 键盘产生的数据进行解码,从而得到按键信息,然

后根据按键信息来实现控制数据采样率、数据采样触发方式,并调整波形显示位置等功能,

PS2 键盘驱动的的具体设计思路和方案见《芯航线 FPGA 数字系统设计教程+实例解析》“芯

航线 FPGA 数字逻辑设计精品教程”部分的“PS2 键盘解码驱动设计与验证”小节,本实例直

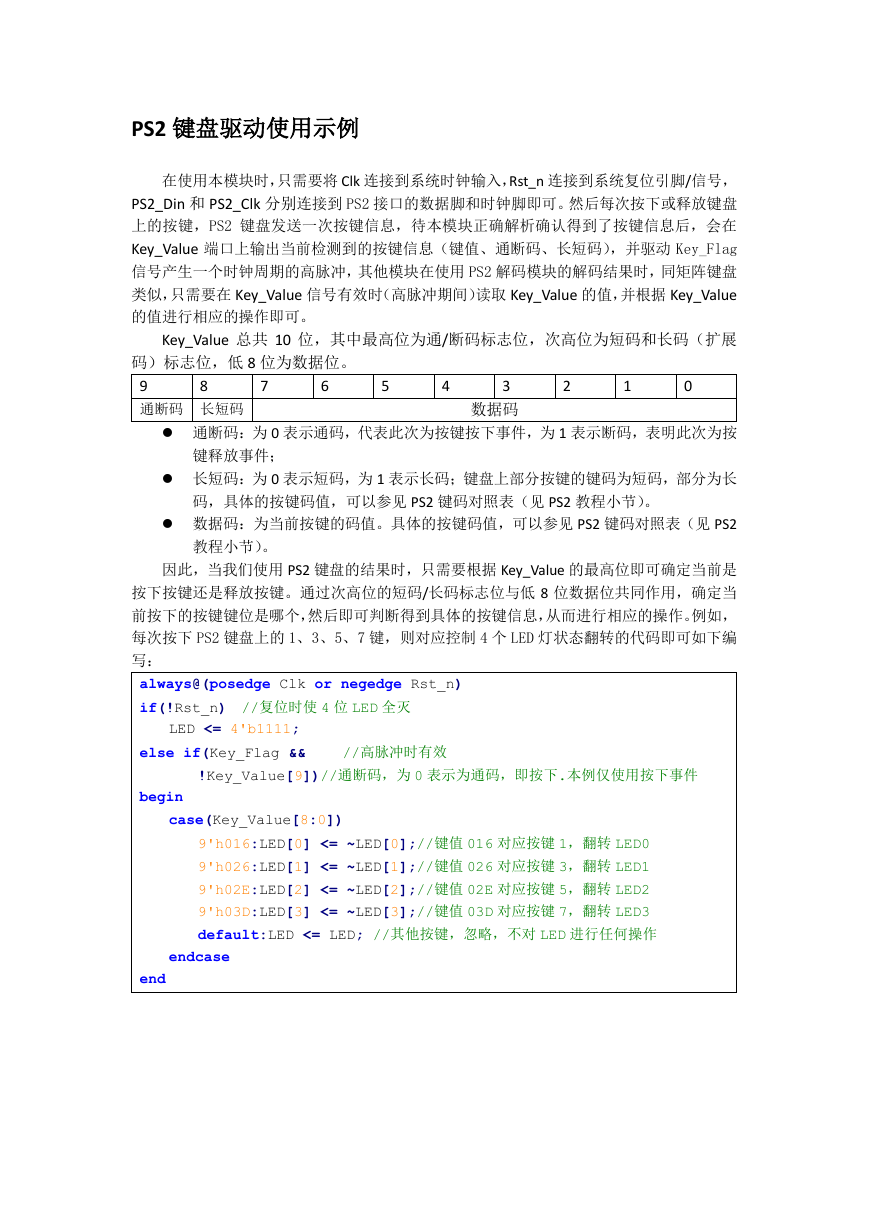

接使用该小节设计的 PS2 键盘驱动模块,因此不再重复介绍。设计完成的 PS2 键盘驱动模块

如下图所示。

详细端口名及其意义如下

端口名

端口功能或意义

端口说明

Rst_n

Clk

PS2_Din

PS2_Clk

全局复位

系统时钟输入端口,默认 50M

PS2 接口数据线

PS2 接口时钟线

Key_Value

按键检测结果输出,总共 10 位,其中最高位为通/断码标志

位,为 0 表示通码,为 1 表示断码(按键释放);次高位为短

码和长码(扩展码)标志位,为 0 表示短码,为 1 表示长码;

低 8 位为数据位。

Key_Flag

按键检测成功标志信号,每当解码成功,该信号产生一个时钟

周期的高脉冲

PS2_Key_Board_DriverClkRst_nkey_value[9:0]key_flagPS2_DinPS2_Clk�

PS2 键盘驱动使用示例

在使用本模块时,只需要将 Clk 连接到系统时钟输入,Rst_n 连接到系统复位引脚/信号,

PS2_Din 和 PS2_Clk 分别连接到 PS2 接口的数据脚和时钟脚即可。然后每次按下或释放键盘

上的按键,PS2 键盘发送一次按键信息,待本模块正确解析确认得到了按键信息后,会在

Key_Value 端口上输出当前检测到的按键信息(键值、通断码、长短码),并驱动 Key_Flag

信号产生一个时钟周期的高脉冲,其他模块在使用 PS2 解码模块的解码结果时,同矩阵键盘

类似,只需要在 Key_Value 信号有效时(高脉冲期间)读取 Key_Value 的值,并根据 Key_Value

的值进行相应的操作即可。

Key_Value 总共 10 位,其中最高位为通/断码标志位,次高位为短码和长码(扩展

码)标志位,低 8 位为数据位。

9

通断码 长短码

8

7

6

5

4

3

数据码

2

1

0

通断码:为 0 表示通码,代表此次为按键按下事件,为 1 表示断码,表明此次为按

键释放事件;

长短码:为 0 表示短码,为 1 表示长码;键盘上部分按键的键码为短码,部分为长

码,具体的按键码值,可以参见 PS2 键码对照表(见 PS2 教程小节)。

数据码:为当前按键的码值。具体的按键码值,可以参见 PS2 键码对照表(见 PS2

教程小节)。

因此,当我们使用 PS2 键盘的结果时,只需要根据 Key_Value 的最高位即可确定当前是

按下按键还是释放按键。通过次高位的短码/长码标志位与低 8 位数据位共同作用,确定当

前按下的按键键位是哪个,然后即可判断得到具体的按键信息,从而进行相应的操作。例如,

每次按下 PS2 键盘上的 1、3、5、7 键,则对应控制 4 个 LED 灯状态翻转的代码即可如下编

写:

always@(posedge Clk or negedge Rst_n)

if(!Rst_n) //复位时使 4 位 LED 全灭

LED <= 4'b1111;

else if(Key_Flag && //高脉冲时有效

!Key_Value[9])//通断码,为 0 表示为通码,即按下.本例仅使用按下事件

begin

case(Key_Value[8:0])

9'h016:LED[0] <= ~LED[0];//键值 016 对应按键 1,翻转 LED0

9'h026:LED[1] <= ~LED[1];//键值 026 对应按键 3,翻转 LED1

9'h02E:LED[2] <= ~LED[2];//键值 02E 对应按键 5,翻转 LED2

9'h03D:LED[3] <= ~LED[3];//键值 03D 对应按键 7,翻转 LED3

default:LED <= LED; //其他按键,忽略,不对 LED 进行任何操作

endcase

end

�

VGA 控制器设计

VGA 标准介绍

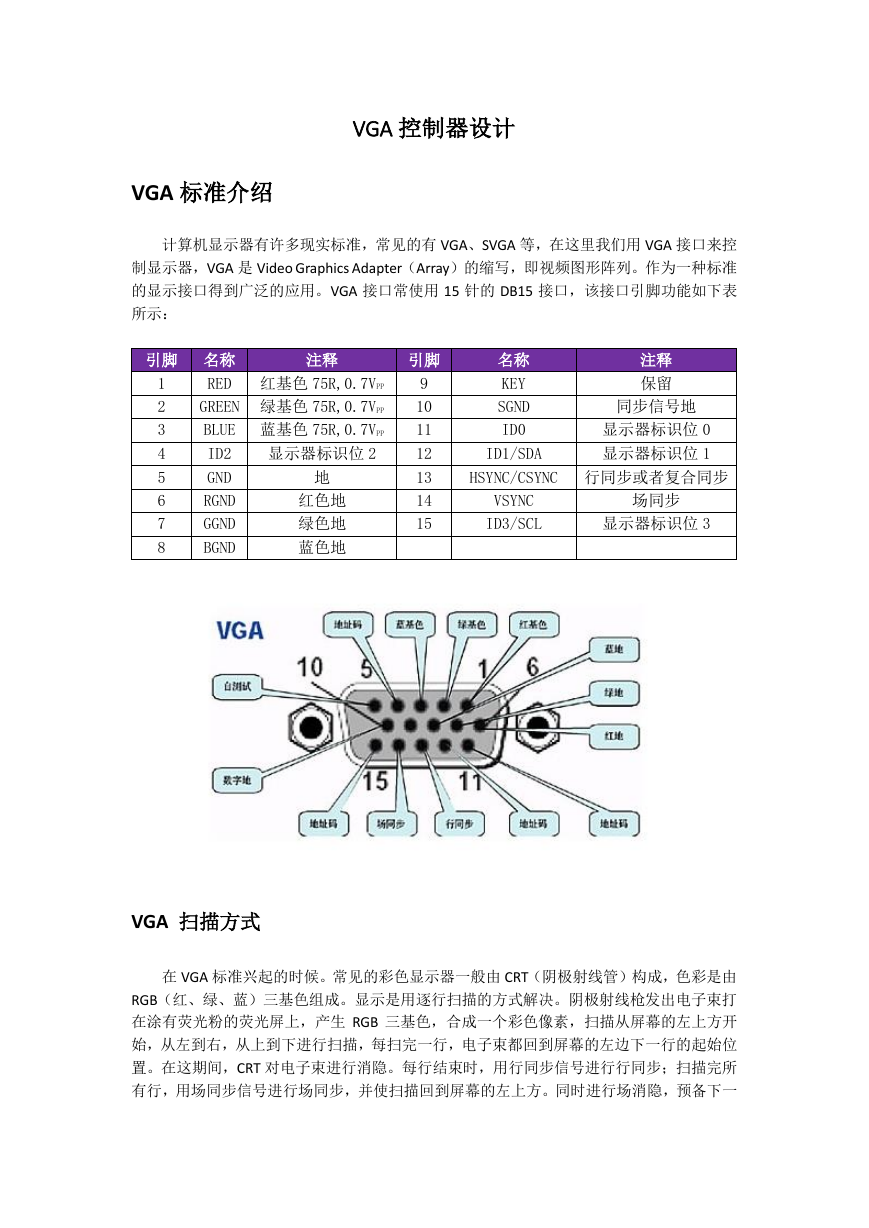

计算机显示器有许多现实标准,常见的有 VGA、SVGA 等,在这里我们用 VGA 接口来控

制显示器,VGA 是 Video Graphics Adapter(Array)的缩写,即视频图形阵列。作为一种标准

的显示接口得到广泛的应用。VGA 接口常使用 15 针的 DB15 接口,该接口引脚功能如下表

所示:

引脚 名称

注释

引脚

RED 红基色 75R,0.7VPP

GREEN 绿基色 75R,0.7VPP

BLUE 蓝基色 75R,0.7VPP

ID2 显示器标识位 2

GND

RGND

GGND

BGND

红色地

绿色地

蓝色地

地

9

10

11

12

13

14

15

1

2

3

4

5

6

7

8

名称

KEY

SGND

ID0

ID1/SDA

注释

保留

同步信号地

显示器标识位 0

显示器标识位 1

HSYNC/CSYNC 行同步或者复合同步

VSYNC

ID3/SCL

场同步

显示器标识位 3

VGA 扫描方式

在 VGA 标准兴起的时候。常见的彩色显示器一般由 CRT(阴极射线管)构成,色彩是由

RGB(红、绿、蓝)三基色组成。显示是用逐行扫描的方式解决。阴极射线枪发出电子束打

在涂有荧光粉的荧光屏上,产生 RGB 三基色,合成一个彩色像素,扫描从屏幕的左上方开

始,从左到右,从上到下进行扫描,每扫完一行,电子束都回到屏幕的左边下一行的起始位

置。在这期间,CRT 对电子束进行消隐。每行结束时,用行同步信号进行行同步;扫描完所

有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方。同时进行场消隐,预备下一

�

场的扫描。

随着显示技术的发展,出现了液晶显示器,液晶显示器的成像原理与 CRT 不同,液晶显

示器是通过对液晶像素点单元施加电压与否,来控制液晶单元的透明程度,并添加三色滤光

片、分别使 R、G、B 这 3 种光线透过滤光片,最后通过 3 个像素点合成一个彩色像素点,

从而实现彩色显示。但是由于液晶显示技术后于 CRT 显示技术诞生,因此在液晶显示器诞生

的时候,为了能够兼容传统的显示接口,因此液晶显示器通过内部电路实现了对 VGA 接口

的完全兼容。因此,我们在使用显示器时,只要该显示器带有标准的 VGA 接口,我们就不

用去关心其成像原理,直接使用标准的 VGA 时序即可驱动。

对于普通的显示器(无论是液晶还是 CRT),共有 5 个信号:R、G、B 三基色信号,行

同步信号 HS,场同步信号 VS。对于时序驱动,VGA 显示器要严格遵循“VGA 工业标准”,即

640*480*60Hz 模式,否则可能会损害 VGA 显示器。

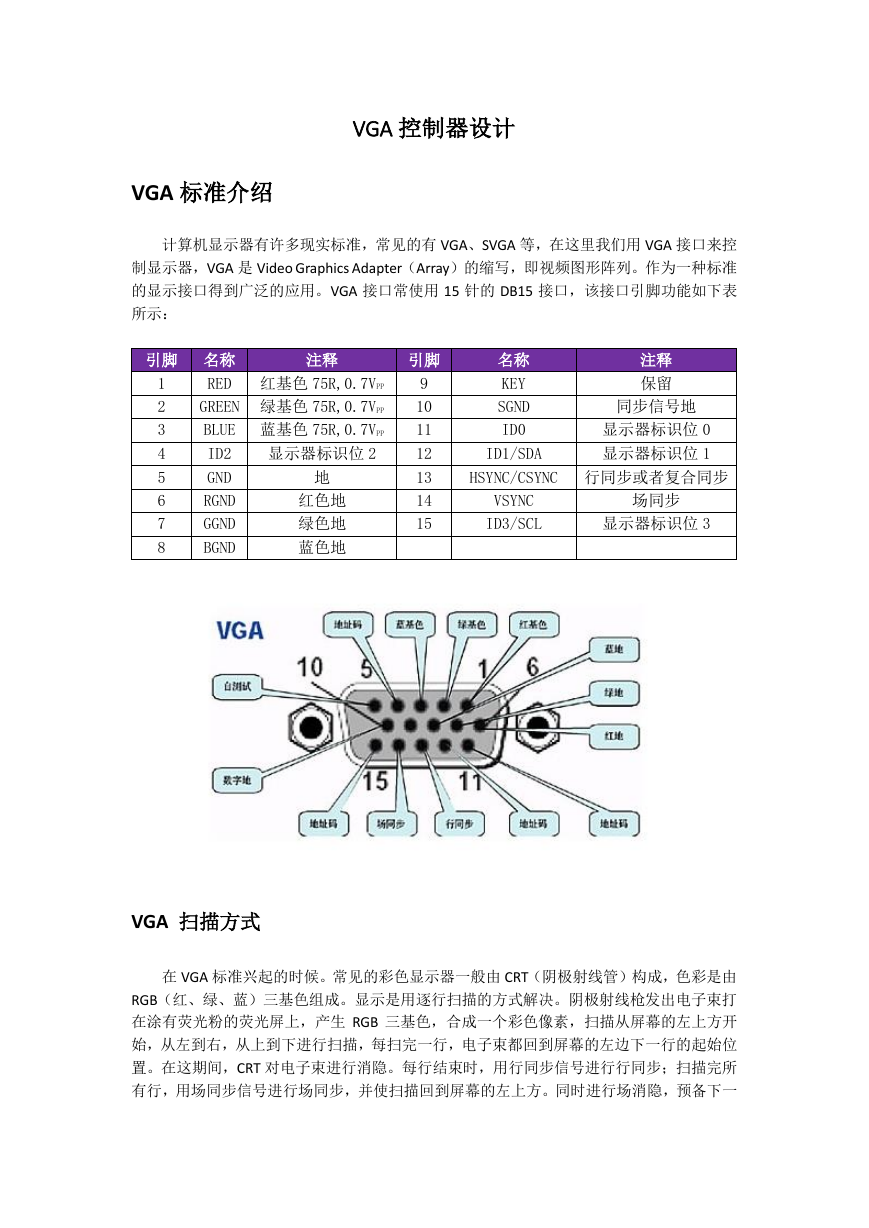

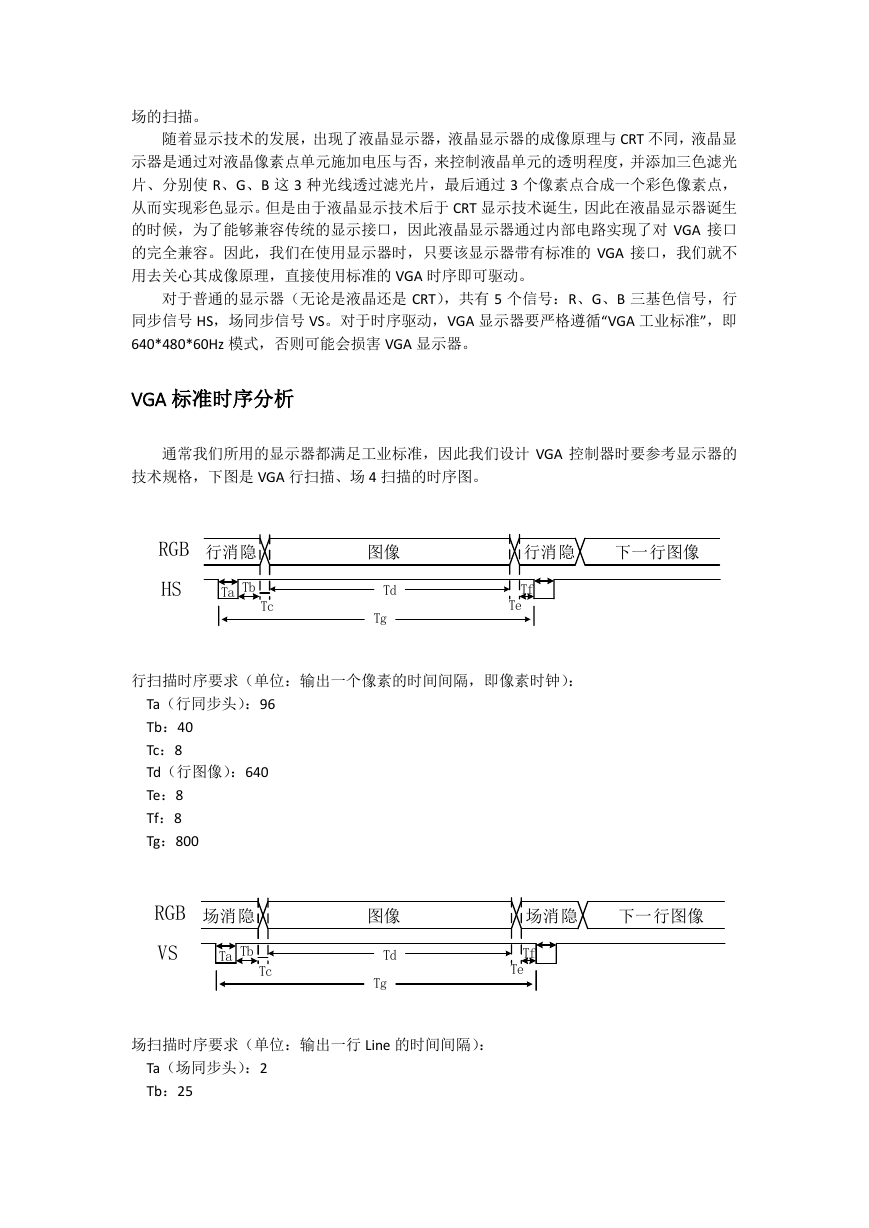

VGA 标准时序分析

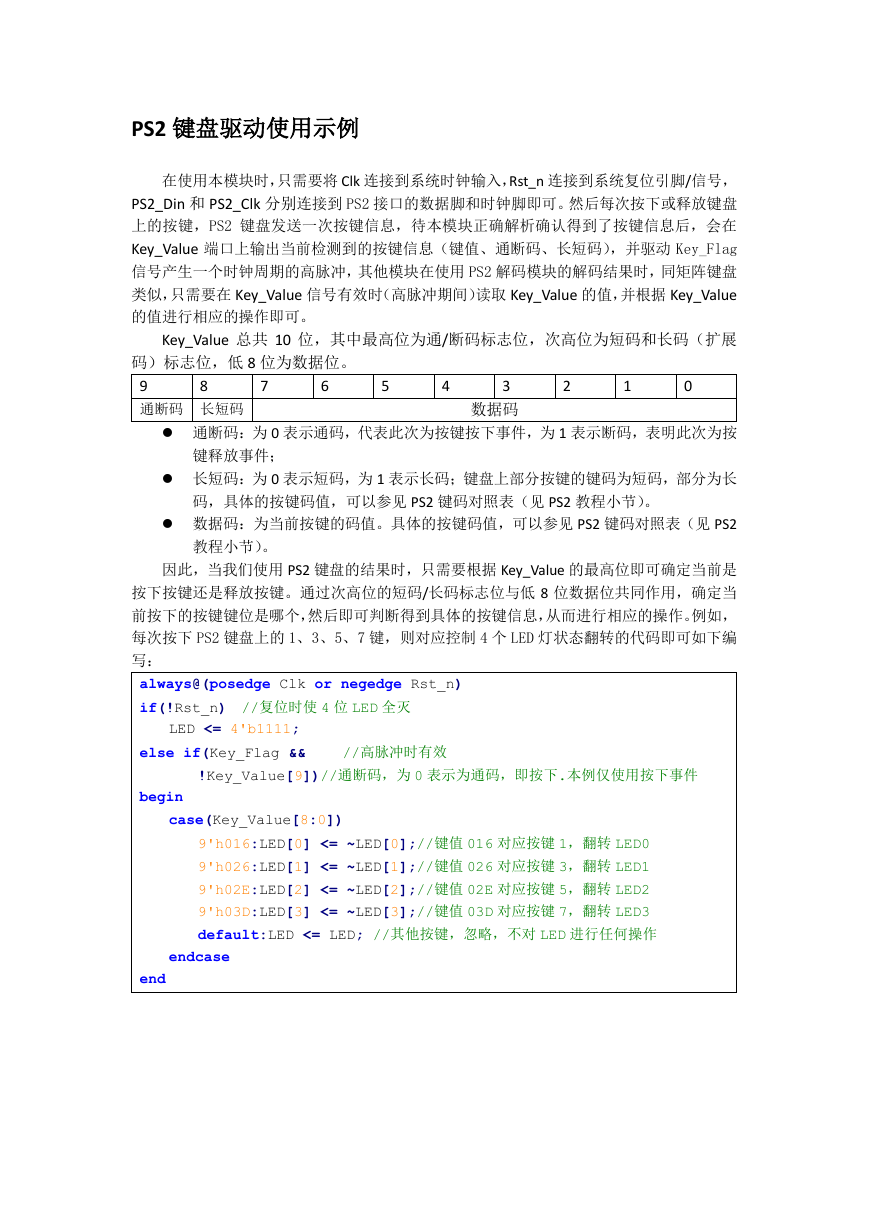

通常我们所用的显示器都满足工业标准,因此我们设计 VGA 控制器时要参考显示器的

技术规格,下图是 VGA 行扫描、场 4 扫描的时序图。

行扫描时序要求(单位:输出一个像素的时间间隔,即像素时钟):

Ta(行同步头):96

Tb:40

Tc:8

Td(行图像):640

Te:8

Tf:8

Tg:800

场扫描时序要求(单位:输出一行 Line 的时间间隔):

Ta(场同步头):2

Tb:25

行消隐行消隐图像下一行图像TaTbTcTdTgTeTfRGBHS场消隐场消隐图像下一行图像TaTbTcTdTgTeTfRGBVS�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc