2019/3/18

训练3

个人主页 / 我的课程 / 数字系统实验 / 三位数码管3(第三次课) / 训练3

题目1

完成

获得1.00分中的

1.00分

题目2

完成

获得1.00分中的

1.00分

题目3

完成

获得1.00分中的

1.00分

2019年03月18日 星期一 16:44

完成

2019年03月18日 星期一 16:51

6 分钟 37 秒

30.00/满分30.00 ﴾100%﴿

关于译码器 下列说法正确的是

选择一项或多项:

a. 译码器decoder﴿是一类多输入多输出组合逻辑电路器件,其可以分为:变量译码和显示译码两类。

b. 显示译码器用来将二进制数转换成对应的七段码,一般其可分为驱动LED和驱动LCD两类

c. 译码器的种类很多,但它们的工作原理和分析设计方法大同小异,其中二进制译码器、二‐十进制译码器和显示译

码器是三种最典型,使用十分广泛的译码电路

d. 变量译码器一般是一种较少输入变为较多输出的器件,常见的有n线‐2^n线译码和8421BCD码译码两类

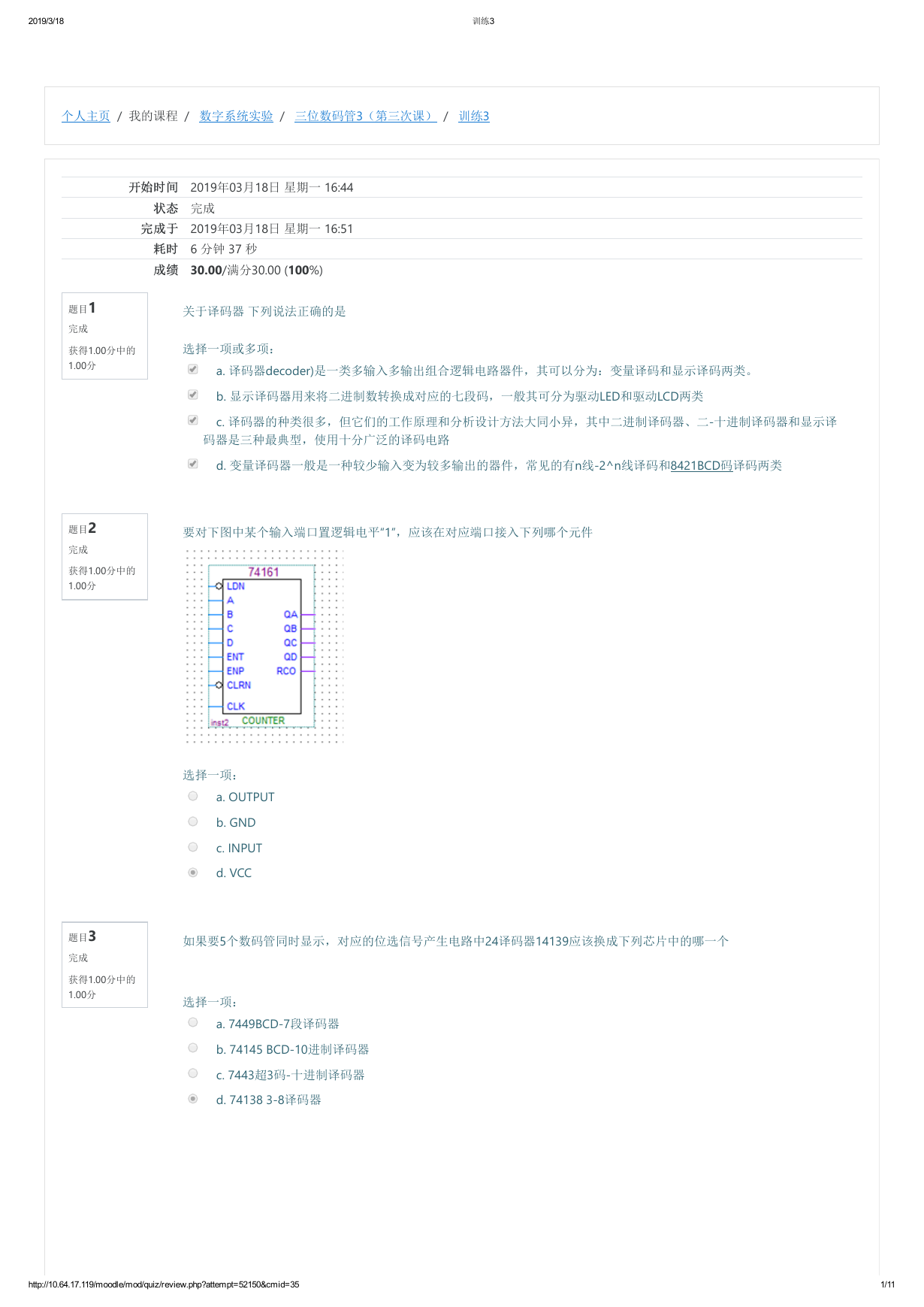

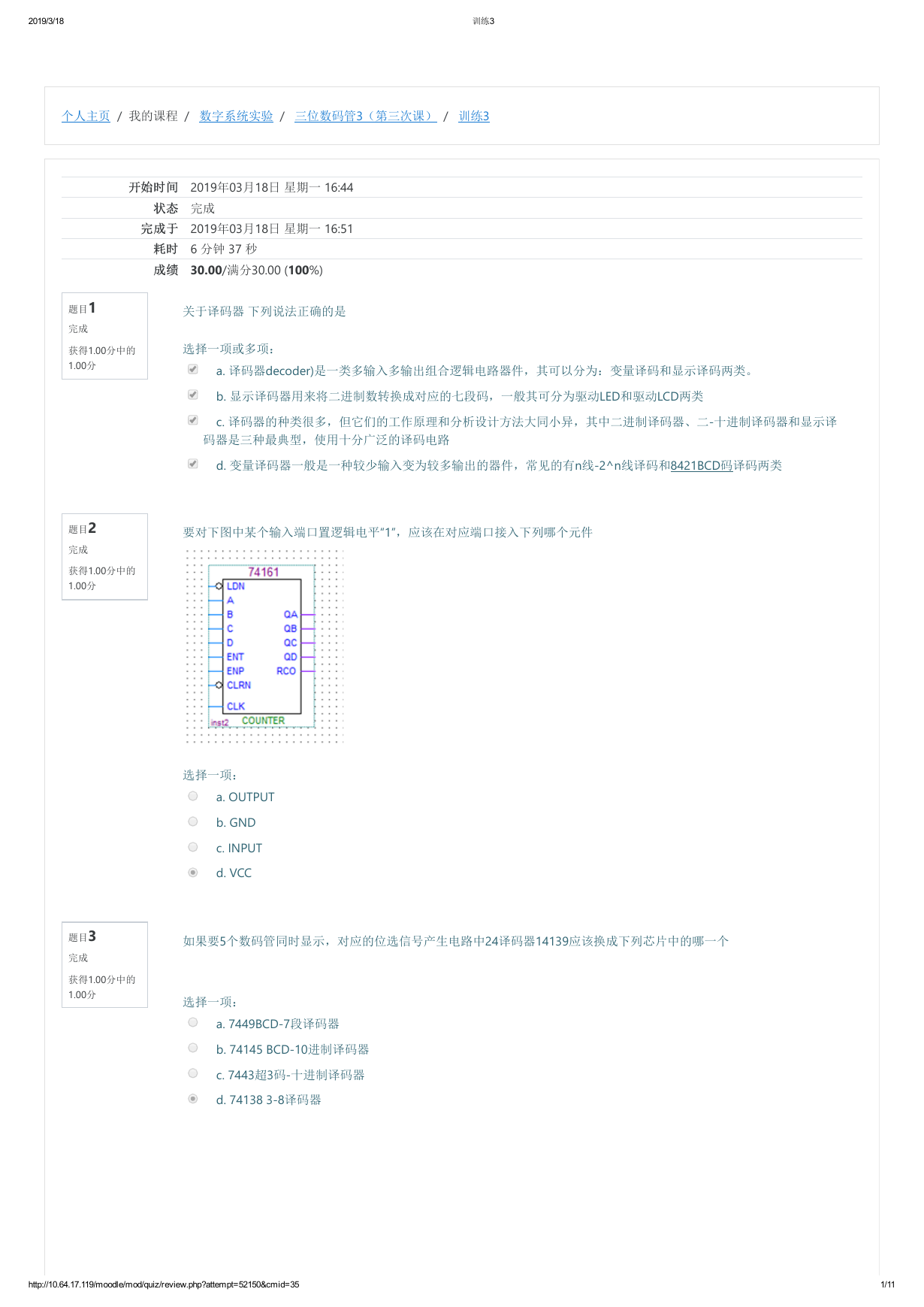

要对下图中某个输入端口置逻辑电平“1”,应该在对应端口接入下列哪个元件

选择一项:

a. OUTPUT

b. GND

c. INPUT

d. VCC

如果要5个数码管同时显示,对应的位选信号产生电路中24译码器14139应该换成下列芯片中的哪一个

选择一项:

a. 7449BCD‐7段译码器

b. 74145 BCD‐10进制译码器

c. 7443超3码‐十进制译码器

d. 74138 3‐8译码器

http://10.64.17.119/moodle/mod/quiz/review.php?attempt=52150&cmid=35

1/11

开

始

时

间

状

态

完

成

于

耗

时

成

绩

�

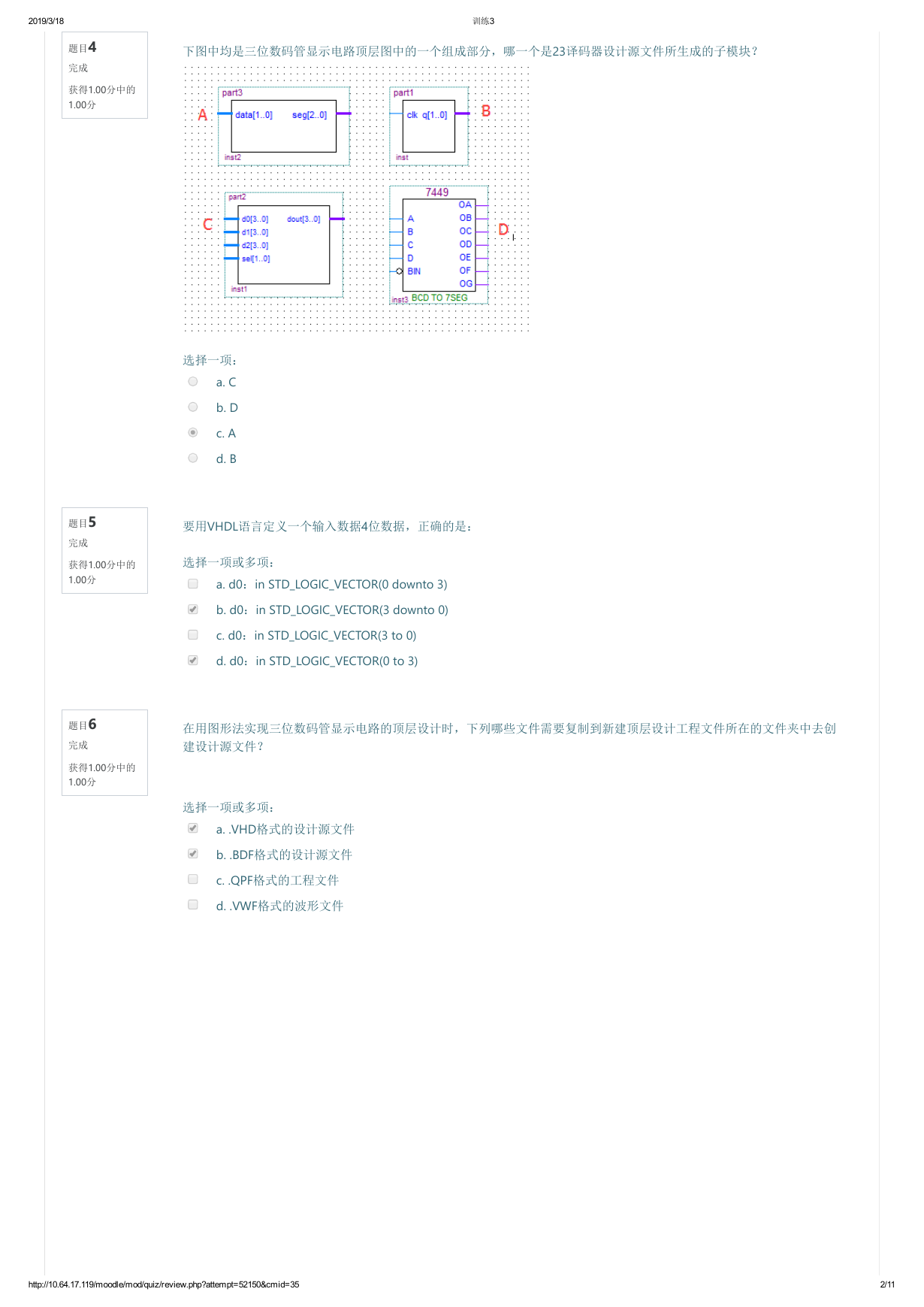

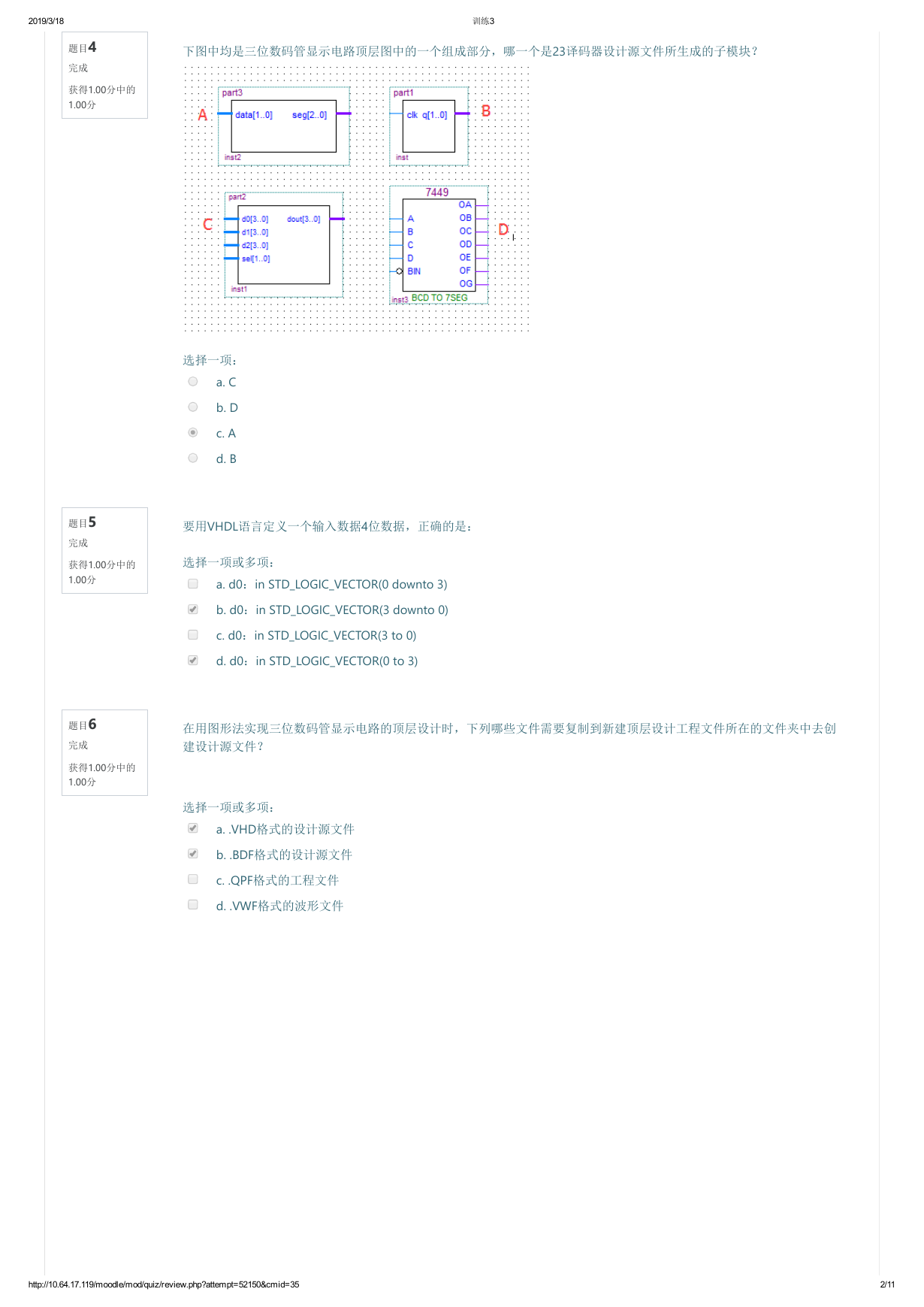

下图中均是三位数码管显示电路顶层图中的一个组成部分,哪一个是23译码器设计源文件所生成的子模块?

训练3

2019/3/18

题目4

完成

获得1.00分中的

1.00分

题目5

完成

获得1.00分中的

1.00分

题目6

完成

获得1.00分中的

1.00分

选择一项:

a. C

b. D

c. A

d. B

要用VHDL语言定义一个输入数据4位数据,正确的是:

选择一项或多项:

a. d0:in STD_LOGIC_VECTOR﴾0 downto 3﴿

b. d0:in STD_LOGIC_VECTOR﴾3 downto 0﴿

c. d0:in STD_LOGIC_VECTOR﴾3 to 0﴿

d. d0:in STD_LOGIC_VECTOR﴾0 to 3﴿

在用图形法实现三位数码管显示电路的顶层设计时,下列哪些文件需要复制到新建顶层设计工程文件所在的文件夹中去创

建设计源文件?

选择一项或多项:

a. .VHD格式的设计源文件

b. .BDF格式的设计源文件

c. .QPF格式的工程文件

d. .VWF格式的波形文件

http://10.64.17.119/moodle/mod/quiz/review.php?attempt=52150&cmid=35

2/11

�

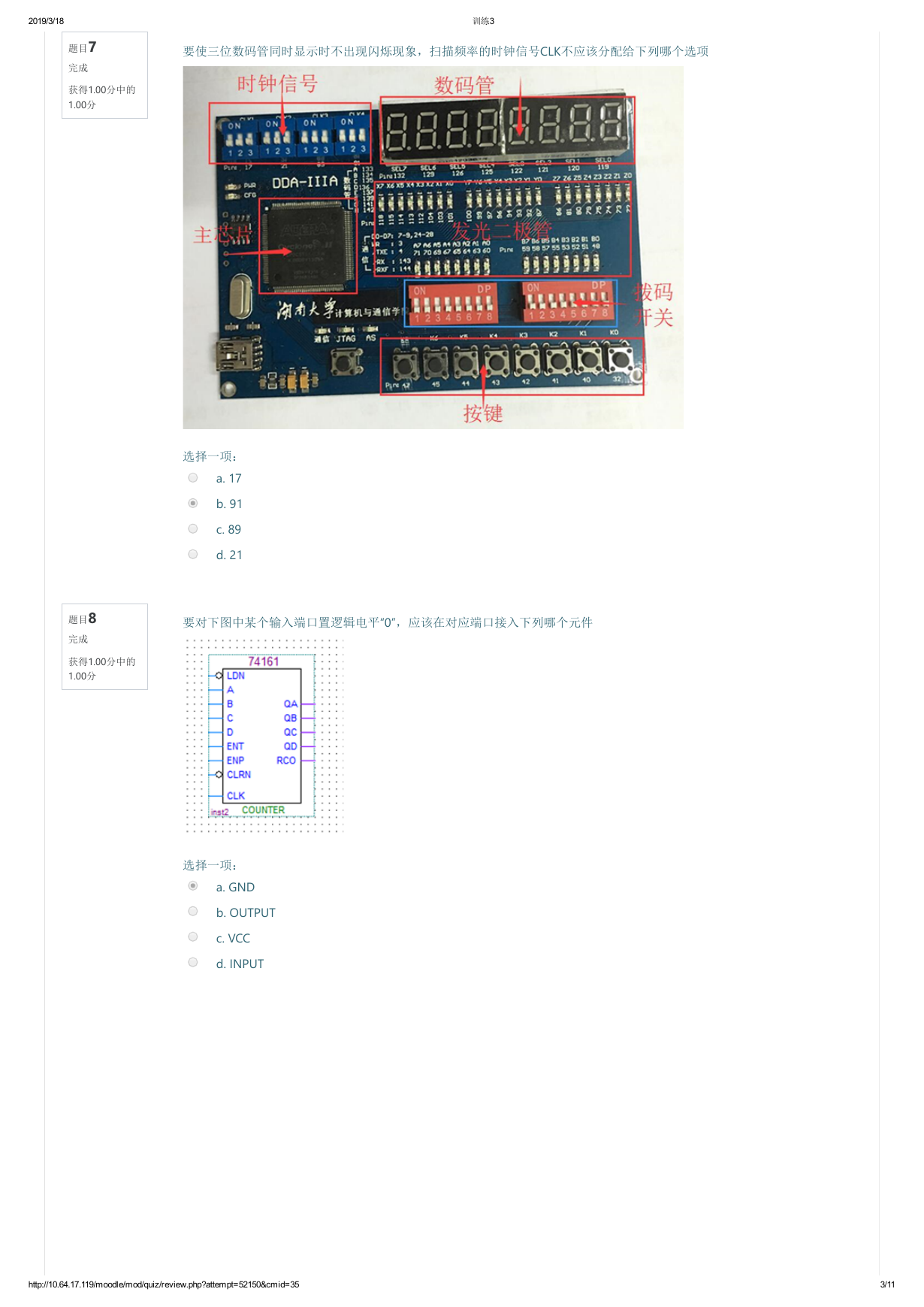

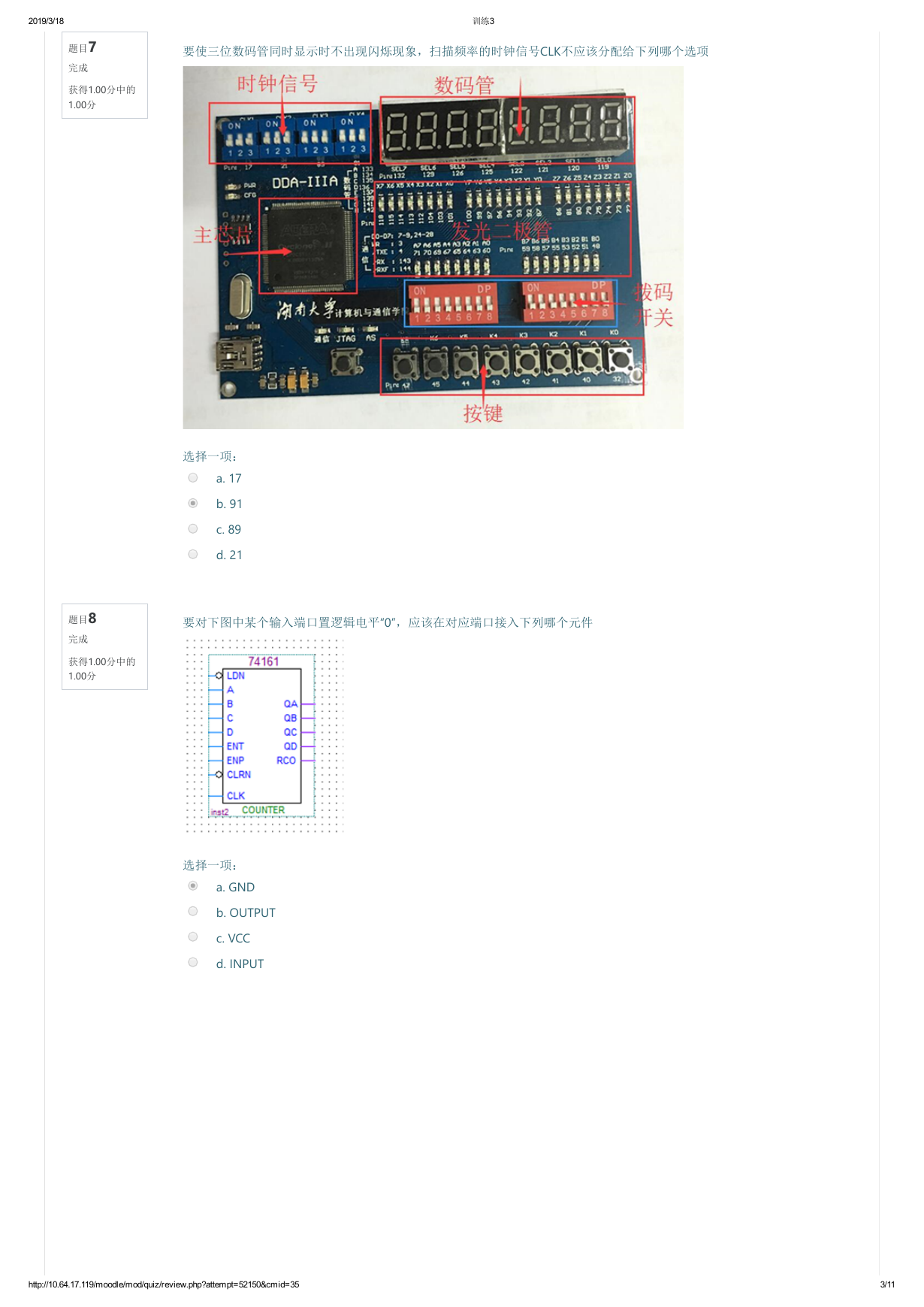

要使三位数码管同时显示时不出现闪烁现象,扫描频率的时钟信号CLK不应该分配给下列哪个选项

训练3

2019/3/18

题目7

完成

获得1.00分中的

1.00分

选择一项:

a. 17

b. 91

c. 89

d. 21

要对下图中某个输入端口置逻辑电平“0”,应该在对应端口接入下列哪个元件

题目8

完成

获得1.00分中的

1.00分

选择一项:

a. GND

b. OUTPUT

c. VCC

d. INPUT

http://10.64.17.119/moodle/mod/quiz/review.php?attempt=52150&cmid=35

3/11

�

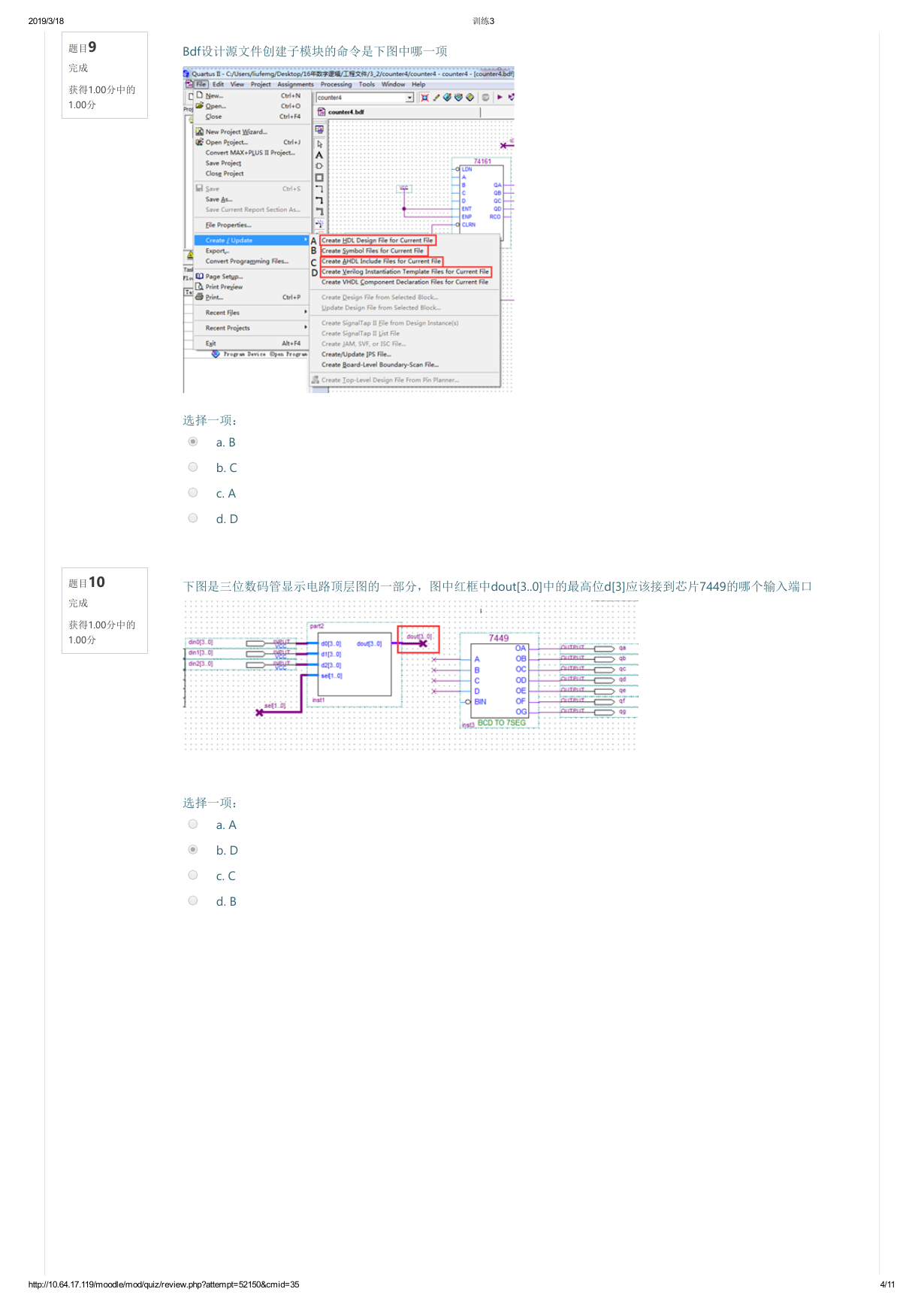

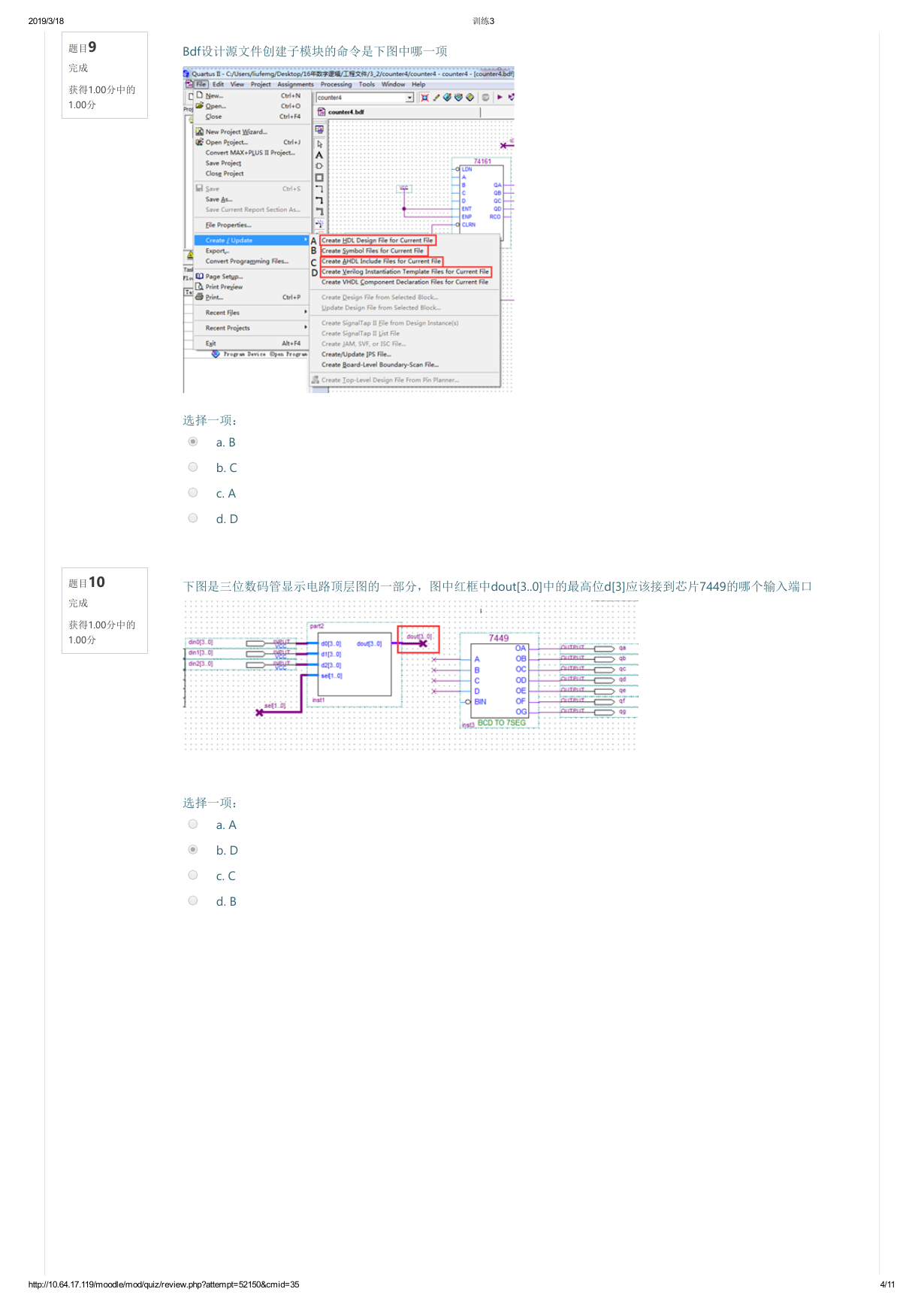

Bdf设计源文件创建子模块的命令是下图中哪一项

训练3

2019/3/18

题目9

完成

获得1.00分中的

1.00分

选择一项:

a. B

b. C

c. A

d. D

下图是三位数码管显示电路顶层图的一部分,图中红框中dout[3..0]中的最高位d[3]应该接到芯片7449的哪个输入端口

题目10

完成

获得1.00分中的

1.00分

选择一项:

a. A

b. D

c. C

d. B

http://10.64.17.119/moodle/mod/quiz/review.php?attempt=52150&cmid=35

4/11

�

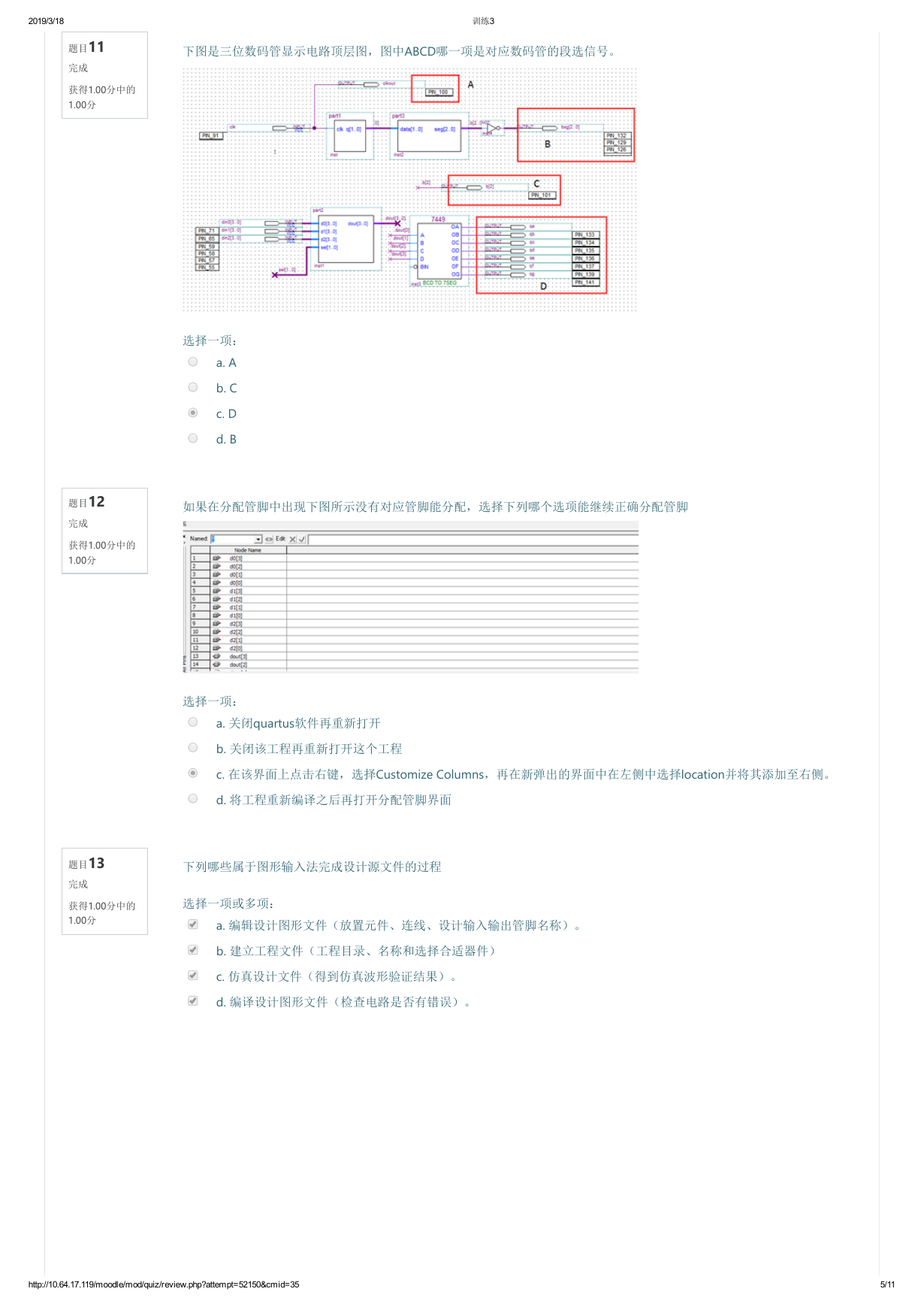

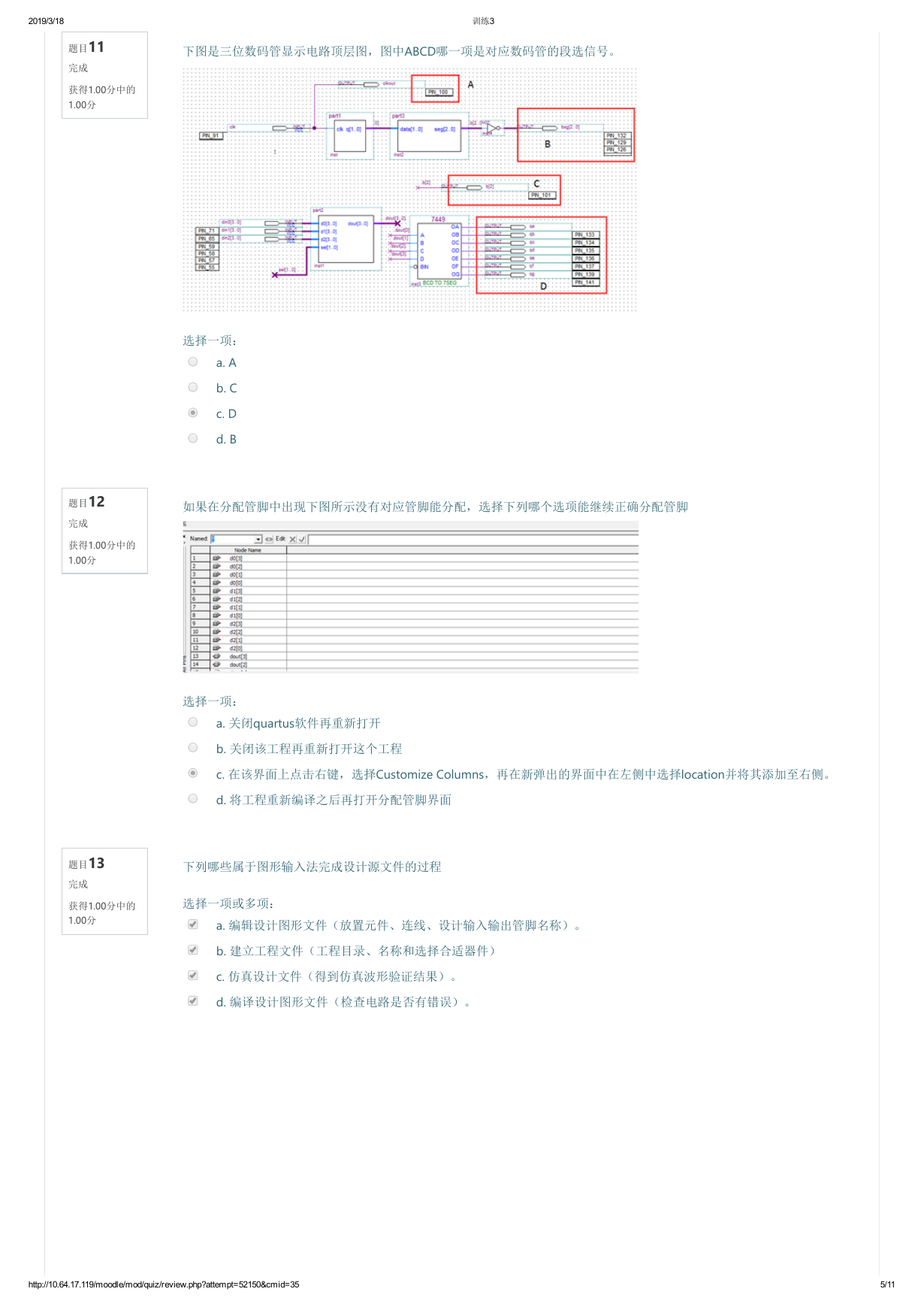

下图是三位数码管显示电路顶层图,图中ABCD哪一项是对应数码管的段选信号。

训练3

2019/3/18

题目11

完成

获得1.00分中的

1.00分

选择一项:

a. A

b. C

c. D

d. B

题目12

完成

获得1.00分中的

1.00分

如果在分配管脚中出现下图所示没有对应管脚能分配,选择下列哪个选项能继续正确分配管脚

选择一项:

a. 关闭quartus软件再重新打开

b. 关闭该工程再重新打开这个工程

c. 在该界面上点击右键,选择Customize Columns,再在新弹出的界面中在左侧中选择location并将其添加至右侧。

d. 将工程重新编译之后再打开分配管脚界面

题目13

完成

获得1.00分中的

1.00分

下列哪些属于图形输入法完成设计源文件的过程

选择一项或多项:

a. 编辑设计图形文件(放置元件、连线、设计输入输出管脚名称)。

b. 建立工程文件(工程目录、名称和选择合适器件)

c. 仿真设计文件(得到仿真波形验证结果)。

d. 编译设计图形文件(检查电路是否有错误)。

http://10.64.17.119/moodle/mod/quiz/review.php?attempt=52150&cmid=35

5/11

�

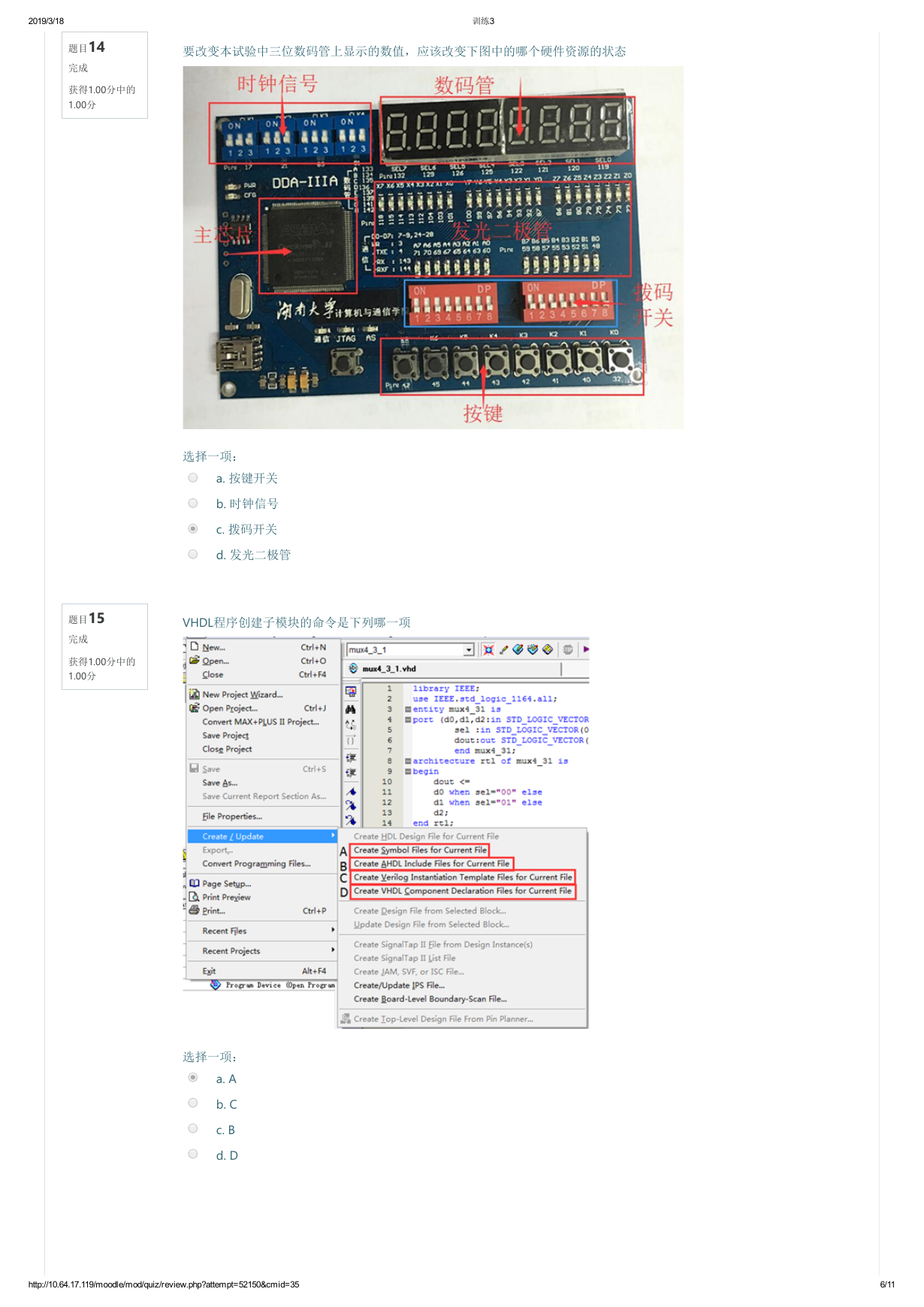

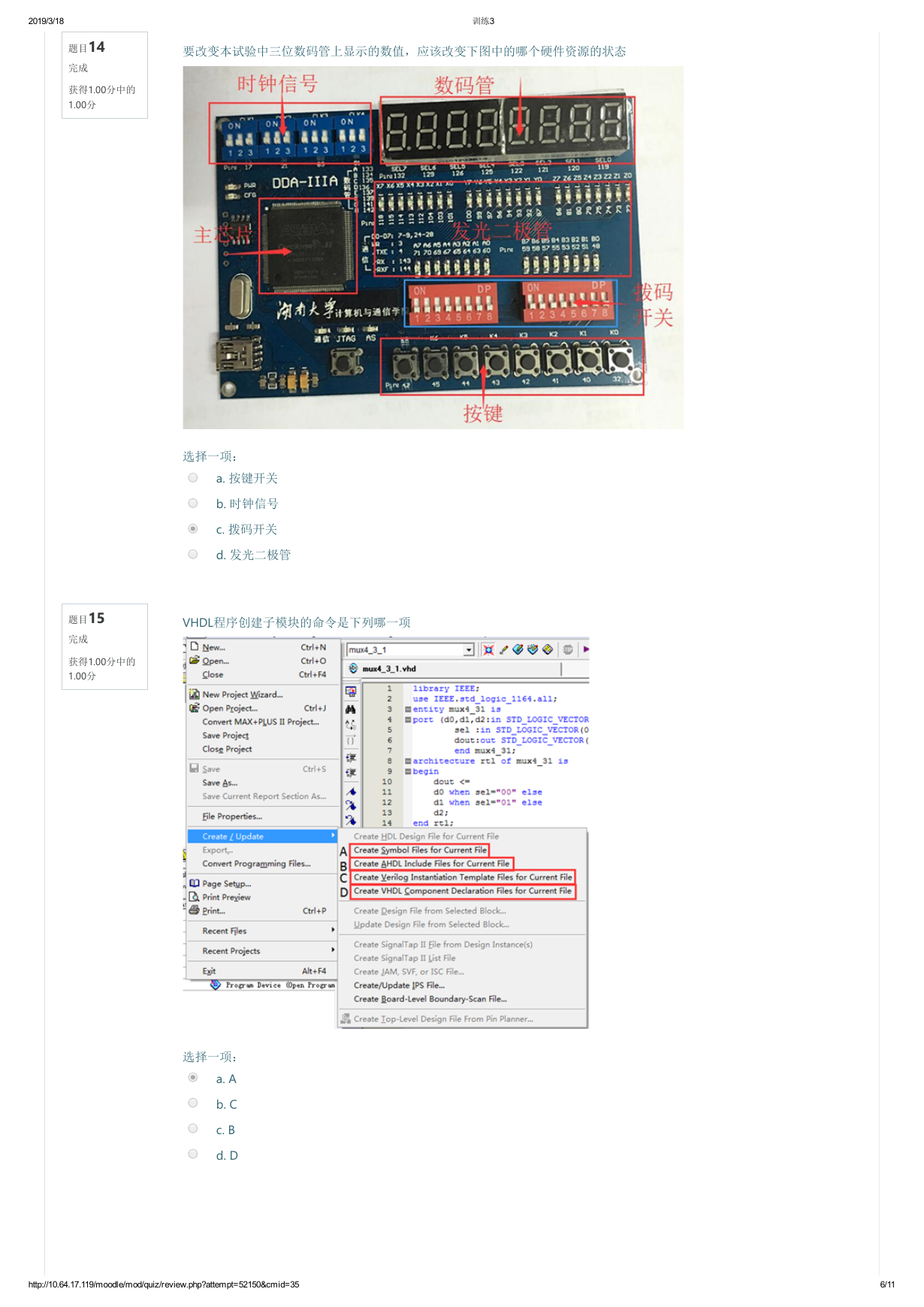

要改变本试验中三位数码管上显示的数值,应该改变下图中的哪个硬件资源的状态

训练3

2019/3/18

题目14

完成

获得1.00分中的

1.00分

选择一项:

a. 按键开关

b. 时钟信号

c. 拨码开关

d. 发光二极管

VHDL程序创建子模块的命令是下列哪一项

题目15

完成

获得1.00分中的

1.00分

选择一项:

a. A

b. C

c. B

d. D

http://10.64.17.119/moodle/mod/quiz/review.php?attempt=52150&cmid=35

6/11

�

2019/3/18

题目16

完成

获得1.00分中的

1.00分

题目17

完成

获得1.00分中的

1.00分

题目18

完成

获得1.00分中的

1.00分

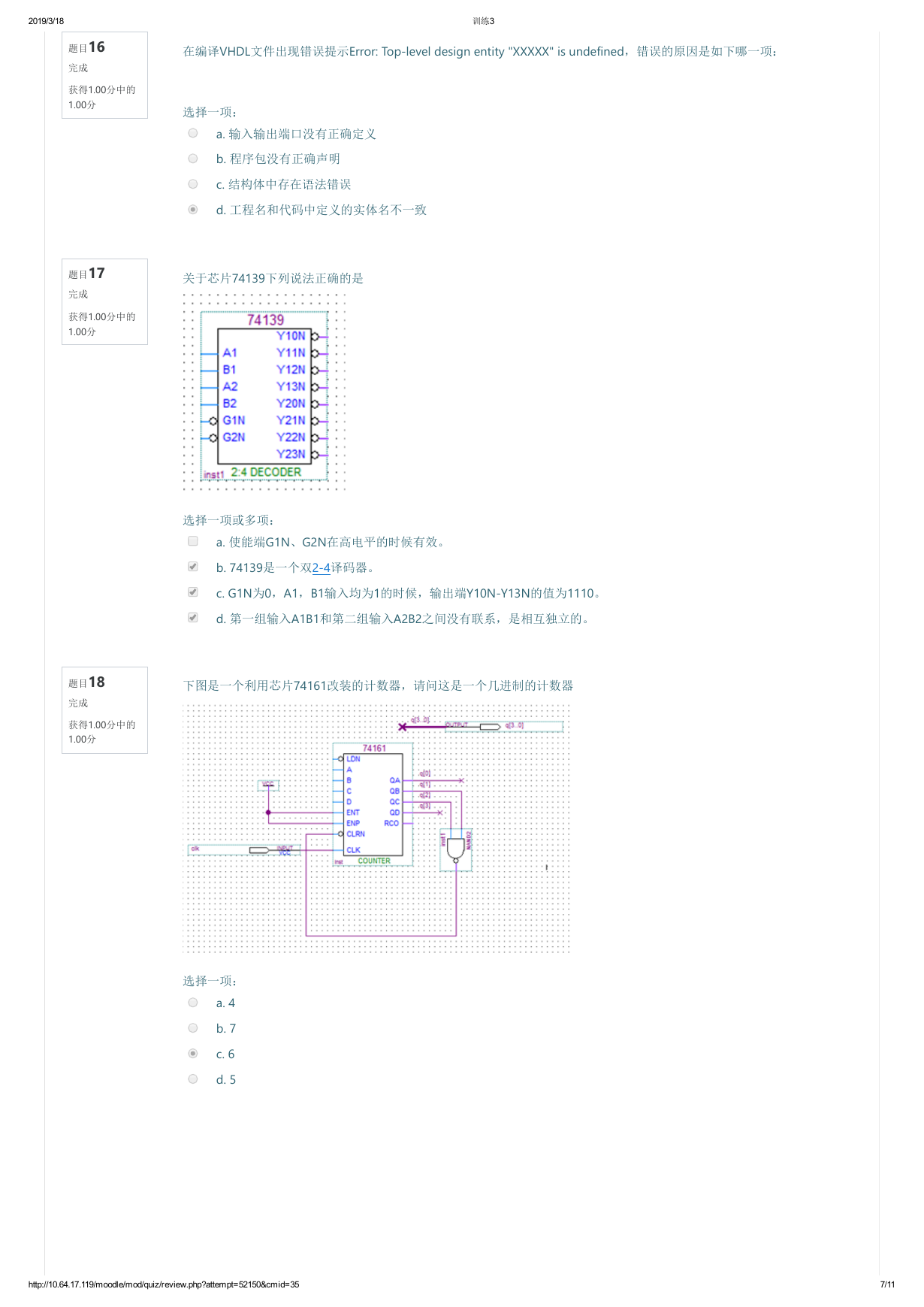

在编译VHDL文件出现错误提示Error: Top‐level design entity "XXXXX" is undefined,错误的原因是如下哪一项:

训练3

选择一项:

a. 输入输出端口没有正确定义

b. 程序包没有正确声明

c. 结构体中存在语法错误

d. 工程名和代码中定义的实体名不一致

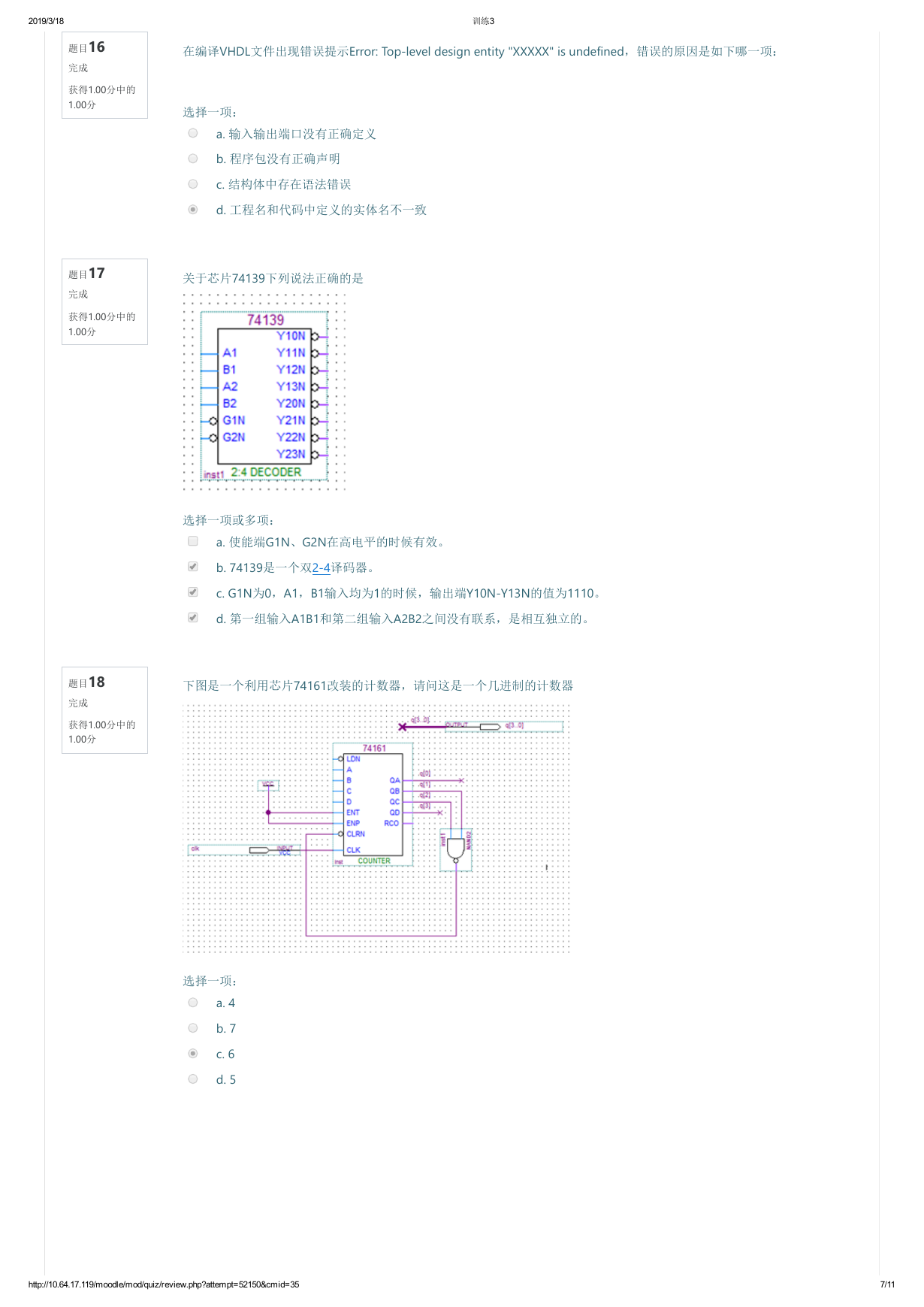

关于芯片74139下列说法正确的是

选择一项或多项:

a. 使能端G1N、G2N在高电平的时候有效。

b. 74139是一个双2‐4译码器。

c. G1N为0,A1,B1输入均为1的时候,输出端Y10N‐Y13N的值为1110。

d. 第一组输入A1B1和第二组输入A2B2之间没有联系,是相互独立的。

下图是一个利用芯片74161改装的计数器,请问这是一个几进制的计数器

选择一项:

a. 4

b. 7

c. 6

d. 5

http://10.64.17.119/moodle/mod/quiz/review.php?attempt=52150&cmid=35

7/11

�

2019/3/18

题目19

完成

获得1.00分中的

1.00分

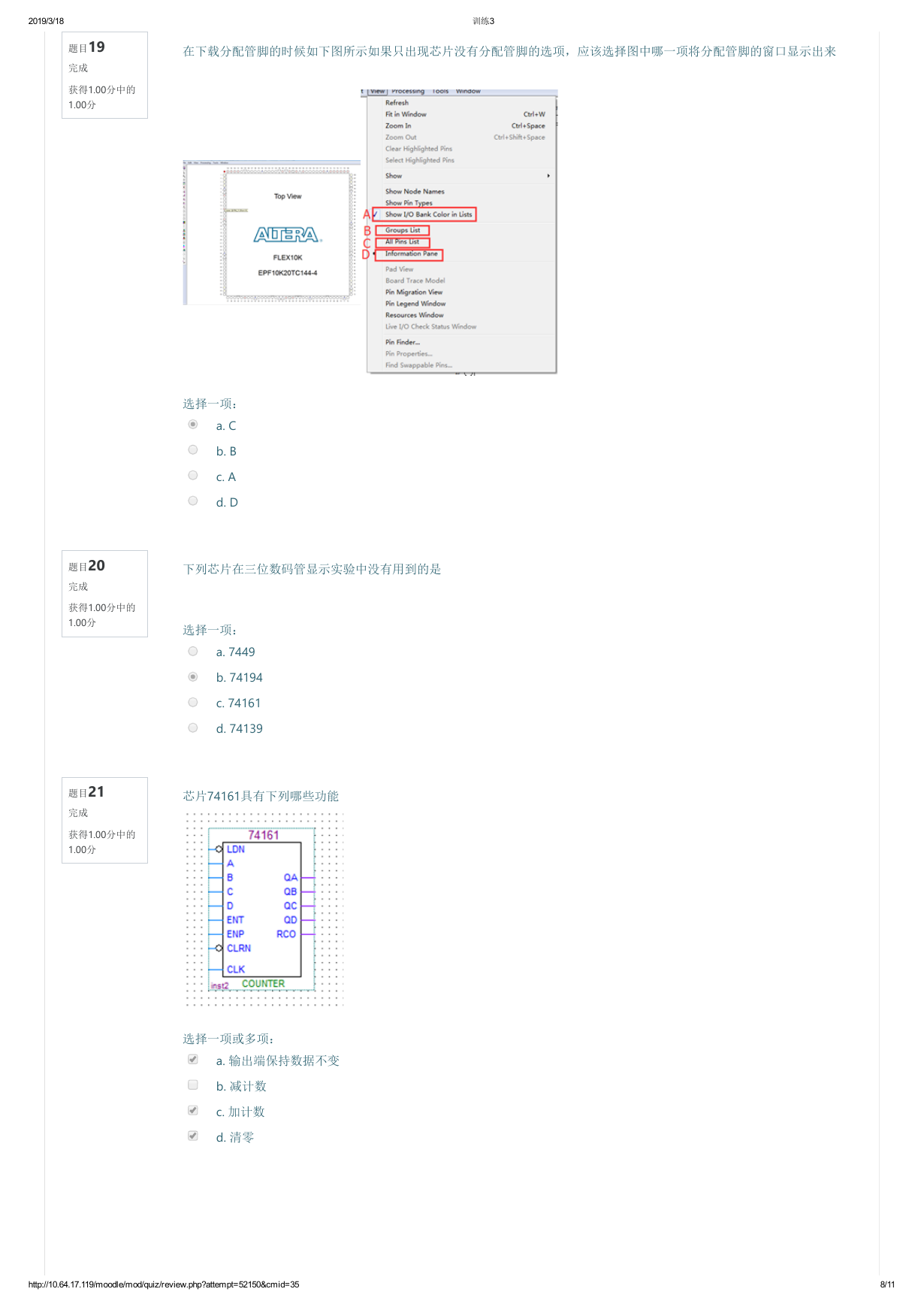

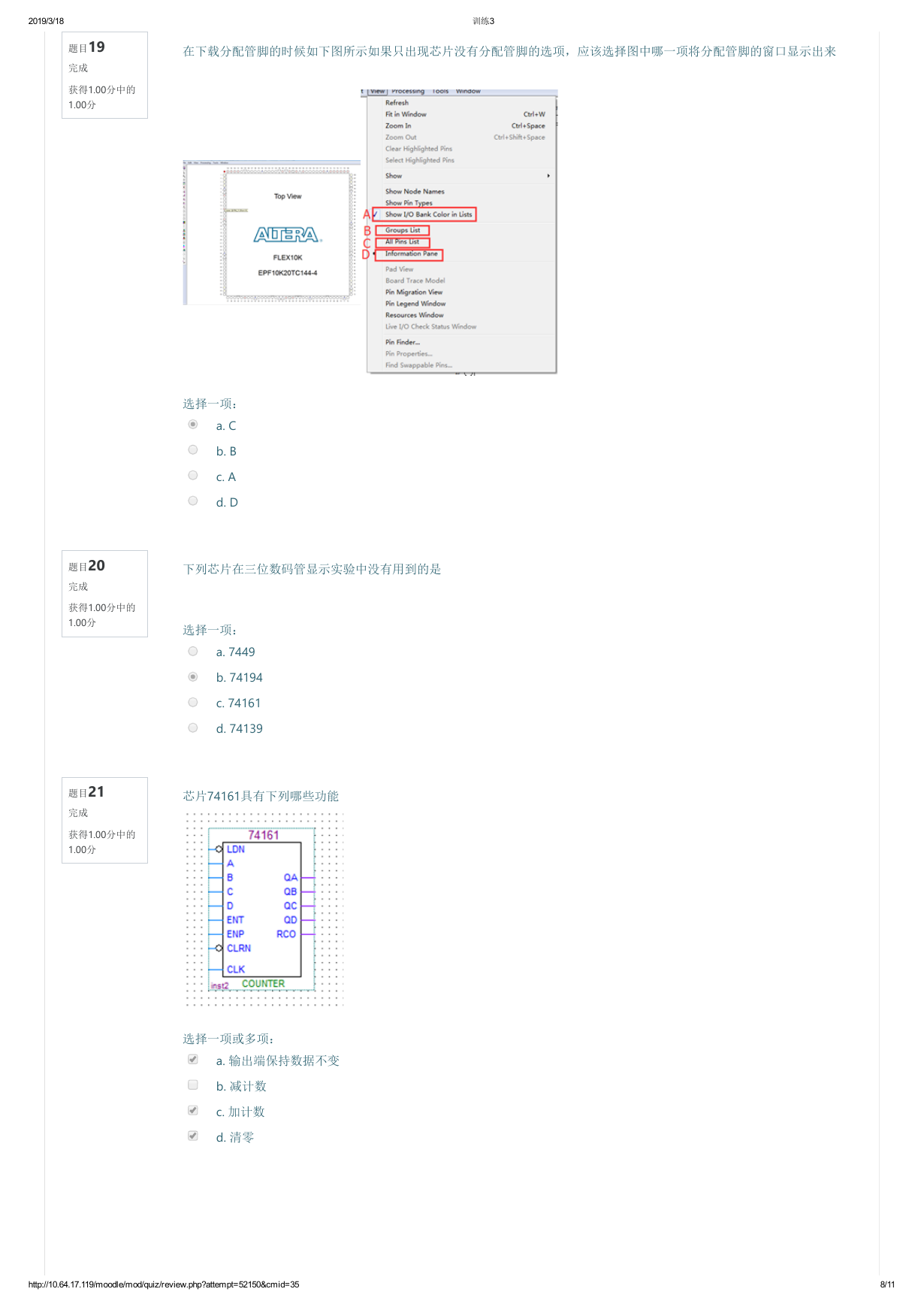

在下载分配管脚的时候如下图所示如果只出现芯片没有分配管脚的选项,应该选择图中哪一项将分配管脚的窗口显示出来

训练3

题目20

完成

获得1.00分中的

1.00分

题目21

完成

获得1.00分中的

1.00分

选择一项:

a. C

b. B

c. A

d. D

下列芯片在三位数码管显示实验中没有用到的是

选择一项:

a. 7449

b. 74194

c. 74161

d. 74139

芯片74161具有下列哪些功能

选择一项或多项:

a. 输出端保持数据不变

b. 减计数

c. 加计数

d. 清零

http://10.64.17.119/moodle/mod/quiz/review.php?attempt=52150&cmid=35

8/11

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc