有符号乘法器设计报告

——VLSI 课程设计

2010 年 12 月

复旦大学专用集成电路与国家重点实验室

�

第一章 设计要求

完成16*16有符号乘法器的设计。

具体设计方案选择要求如下:

1、 编码方式:non-booth 编码,Booth 编码,Booth2 编码(任选一种)

2、 拓扑结构:简单阵列,双阵列,二进制树,Wallace 树(任选一种)

3、 加法器:Ripple Carry Adder,Carry bypass,Carry select,Carry

look ahead(任选一种或采用混合方法)

设计报告必须包含设计方案说明及选择该方案的理由、仿真和设计结构等。

第二章 设计分析

在微控制器(MCU)、微处理器(MPU)、数字信号处理器(DSP)、滤波器

(FIR/IIR)等各种电路中都会用到乘法器,乘法器是最基本、最重要的运算模块

之一。并且乘法器往往还是处在关键路径上,所以乘法器的性能就显得更加重要。

伴随着现在工艺水平的提高,模块的面积也随着减小,在一定程度下以面积为代

价来追求性能的提升,这也是允许的。

本设计是以追求性能为设计目标的,采用全并行的乘法器电路,设计指标设

为传播延时为 5ns。

第三章 乘法器原理分析

乘法器通常有三种结构形式,全串行乘法器、串并行乘法器以及全并行乘法

器。全串行乘法器都可以是串行的,需要多个时钟周期,速度很慢;串并行乘法

器的一个输入是并行的,另一输入是串行的,乘积串行输出;全并行乘法器,输

入和输出都是并行的,电路较为复杂,但是速度极快。本设计追求的就是速度,

所以采用全并行乘法器机构。

16 位有符号乘法器可以分为三个部分:根据输入的被乘数和乘数产生部分

积、部分积压缩产生和和进位、将产生的和和进位相加。这三个部分分别对应着

编码方式、拓扑结构以及加法器。

3.1 编码方式

本设计采用 booth2 编码。

Booth 算法的提出主要是为了解决有符号数乘法运算中的复杂的符号修正的

问题,所以采用 booth2 编码对于补码表示的两数就不需要考虑符号的问题。

任何一个有符号数的补码,都可以表示为下面的形式:

Y

y

n

1

2

n

1

n

2

i

0

y

i

i

2

附加上一位 y-1=0,帮助分析 y0,以下简单推导两数的乘法运算。

�

Y

y

n

1

n

1

2

y

i

i

2

y

1

y

n

1

n

1

2

y

n

1

n

1

2

i

i

y

i

i

2

i

y

i

i

2

n

3

1

odd

3

n

i

1

odd

y

i

i

2

y

1

i

1

y

i

2

2

i

n

3

1

odd

i

1

y

i

2

y

1

2

y

(

n

2) 1

n

2

2

2

n

0

even

y

i

i

2

2

n

even

y

i

1

i

2

2

i

4

n

0

even

y

i

1

i

2

y

1

2

n

0

i

2

n

0

even

2

n

0

even

i

2

n

0

even

y

i

1

i

2

i

y

i

i

2

2

i

i

n

2

2

0

even

y

i

1

i

2

(

y

i

1

y

i

2

y

i

1

i

)2

2

n

0

even

2

n

0

even

i

i

XY

PP

i

(

y

n

2

0

i

(

y

i

even

1

y

i

2

y

i

1

)

X

y

i

2

y

i

1

) 2

X

i

i

1

i

2

n

0

even

PP

i

i

2

仔细观察推导出的结果,i 是偶数,即隔一位编码一次,每次检验 3 位,每次检验 3 位

的高位时下一次检验 3 位的低位。

Booth2 算法规则

表中有 8 种组合,但真正进行的运算只有 3 种:+0,+X,+2X,负项

通过补码运算变成加法。负数的补码可通过“取反加 1”实现。

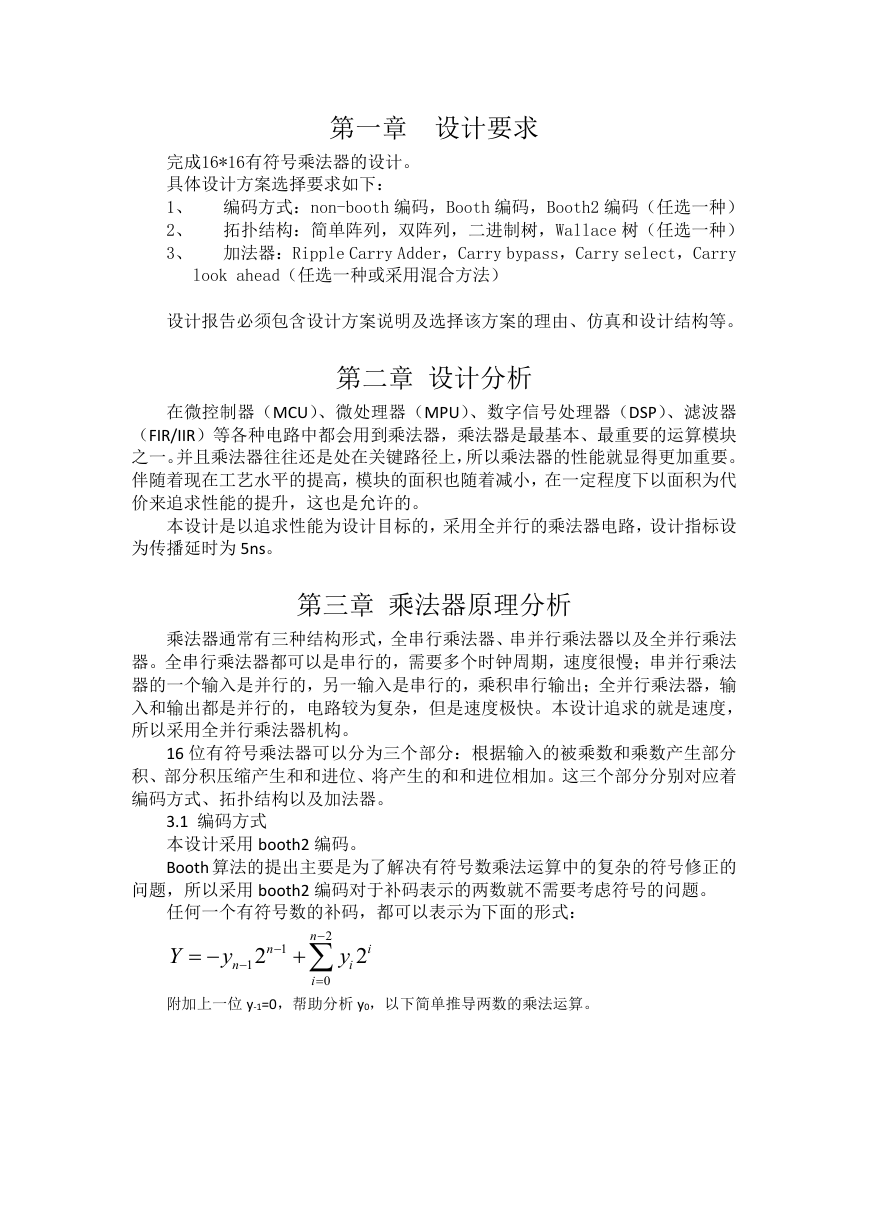

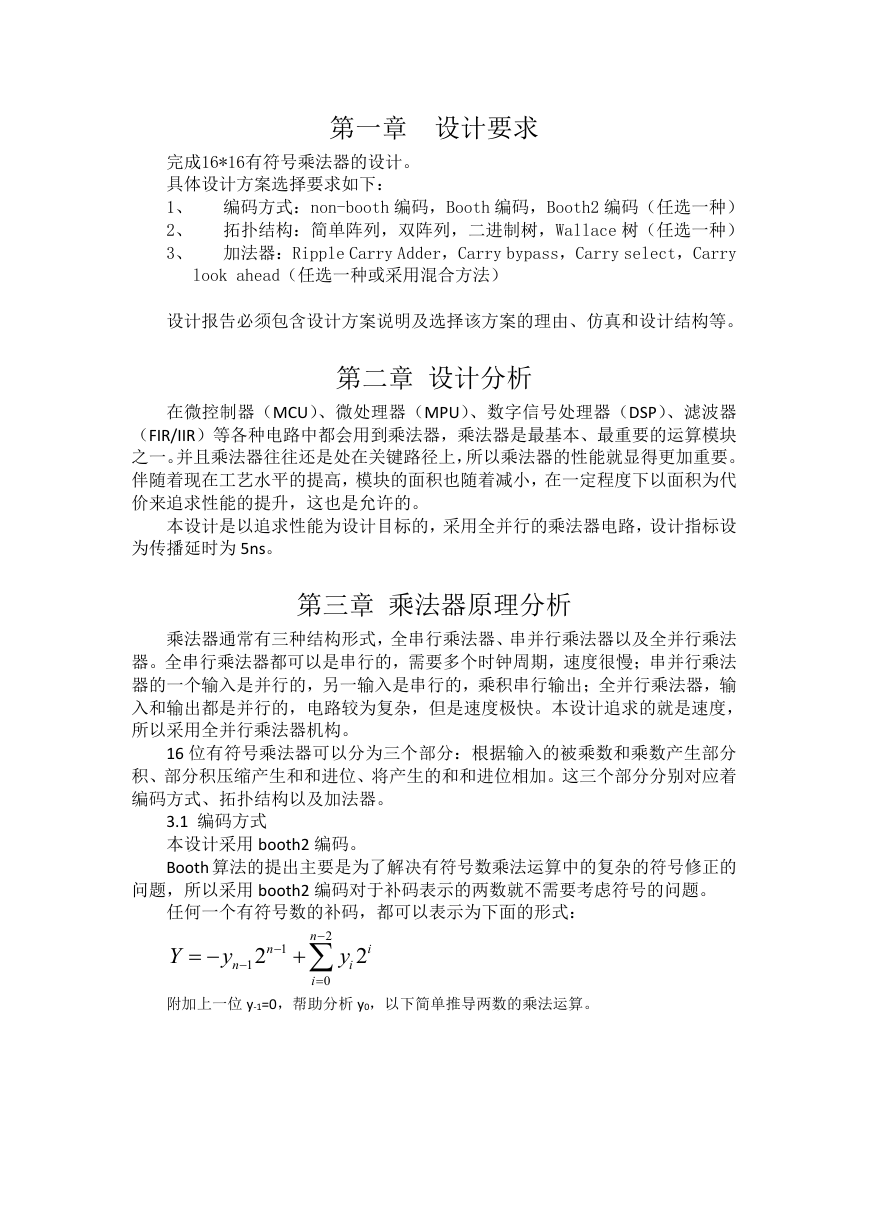

经过 booth2 编码后,产生的部分积可能是负值,需要考虑符号扩展的问题。

如果某个低位的部分积是负数,则需要扩展其符号位使其和高位数对其,无论是

正数还是负数,扩展符号位都不会引起数值额变化,所以可以对所有的部分积都

扩展符号位。但这样带来的弊处就是增加了硬件开销。可以采用以下的方法来降

低开销。

�

把符号位的高位部分都转化为 1,再通过化去高位的 1 的方法,来减少硬件

开销。部分积可以转化为下图所示:

部分积是负数时 S=1,部分积是正数时 S=0;

当部分积是+0 时,E=1,部分积是-0 时,E=0,其余情况 E=S 取反。

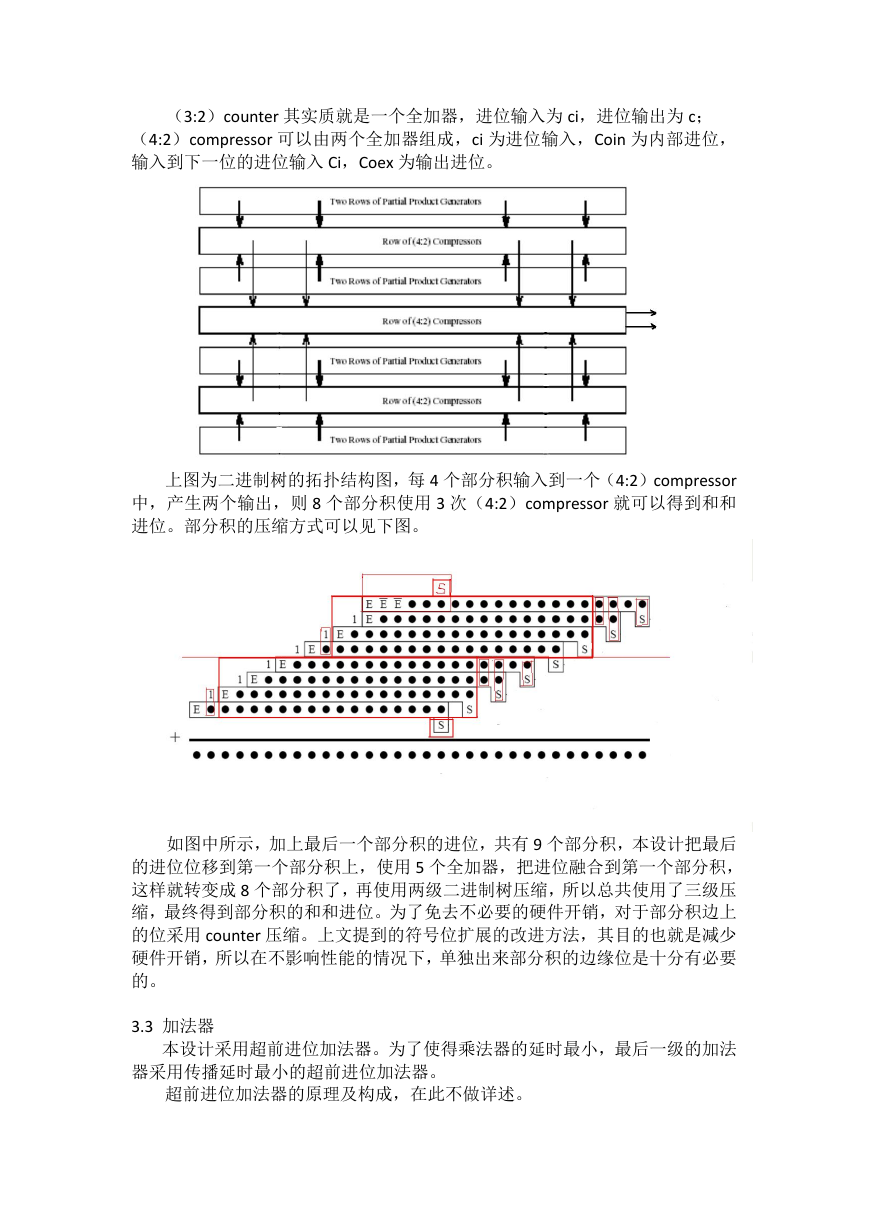

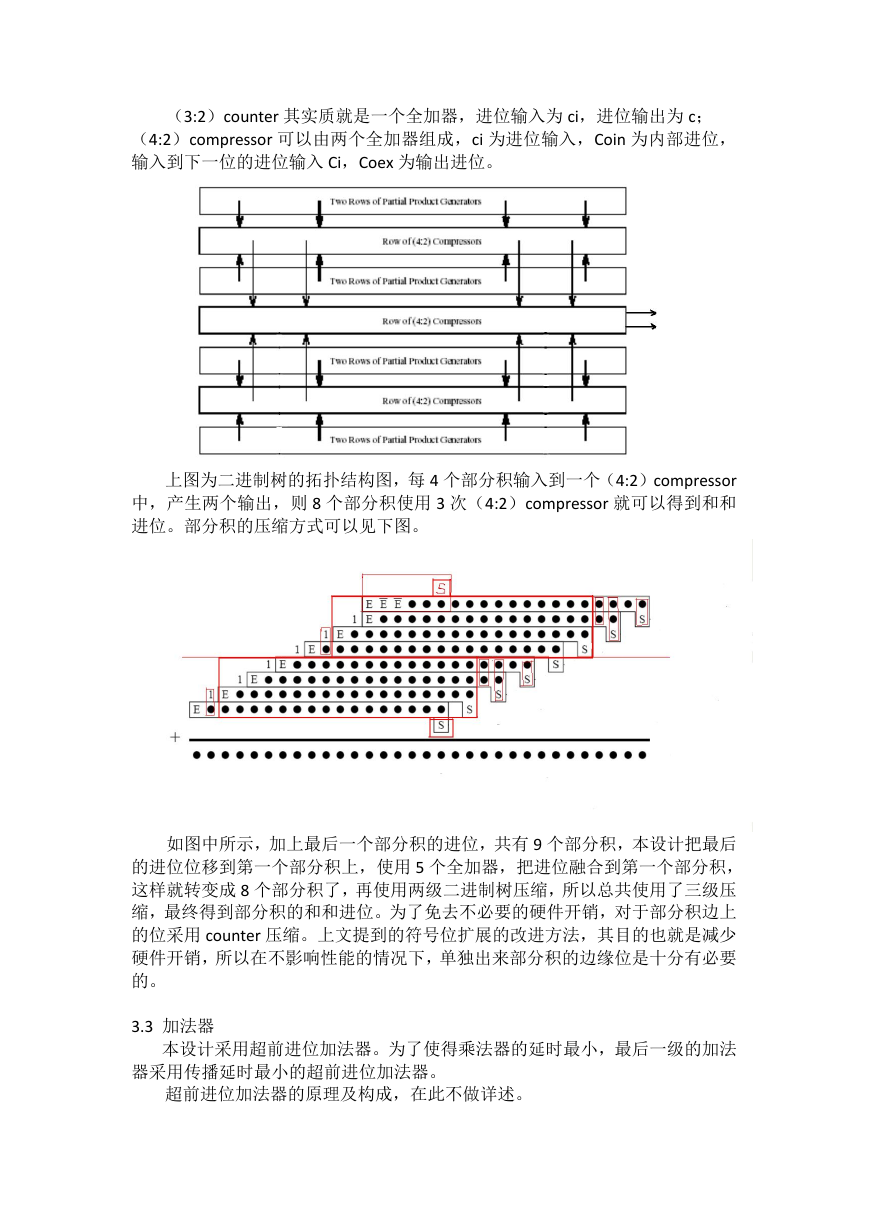

3.2 拓扑结构

本设计采用二进制树的拓扑结构。二进制树拓扑结构排列的较为规整,且部

分积压缩的速度也非常快。

部分积压缩的目的是为了减小进位传播的延时,采用进位保留加法器,根据

当前位信息产生下一位的进位,仅仅产生而没有进位行波传播,这样就可以把当

前的多位压缩到较少的位数。经过几次压后,把部分积压缩成和以及进位。

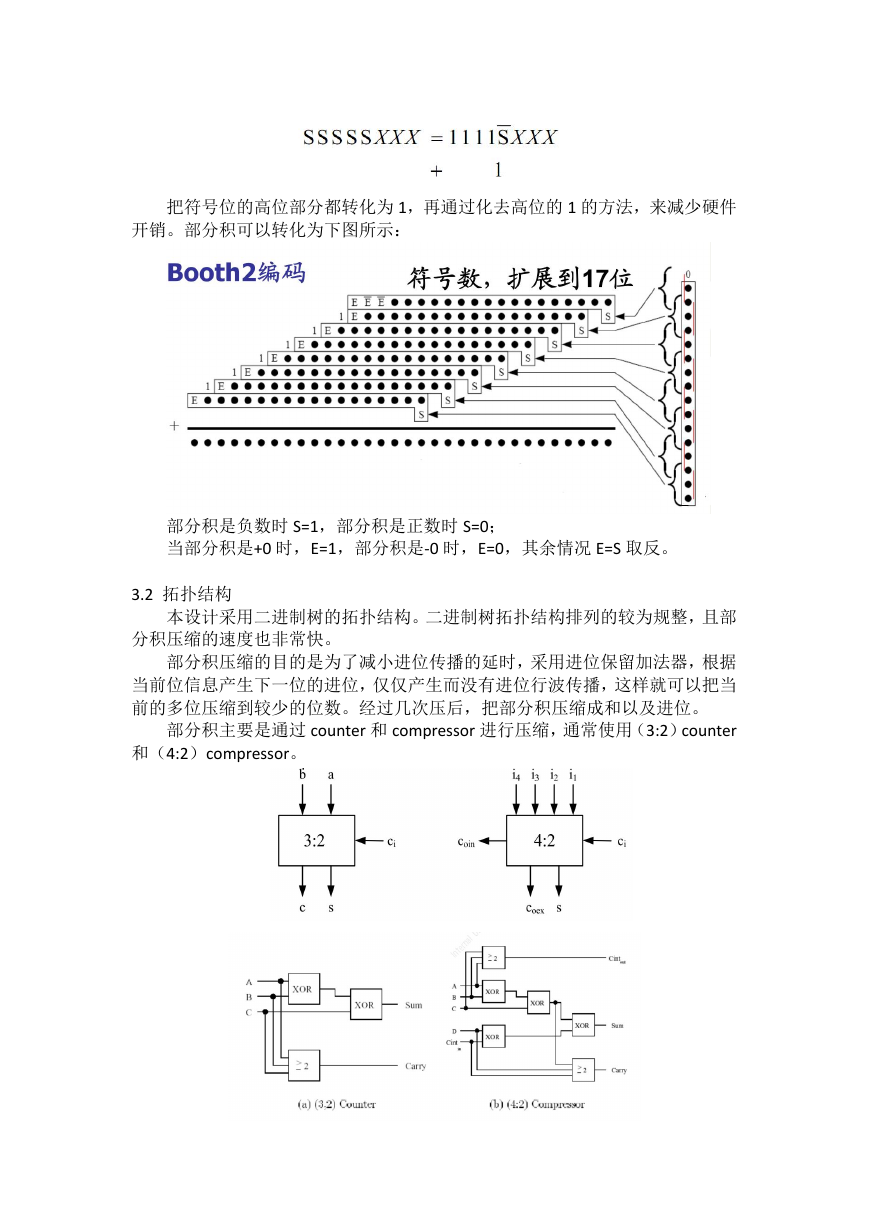

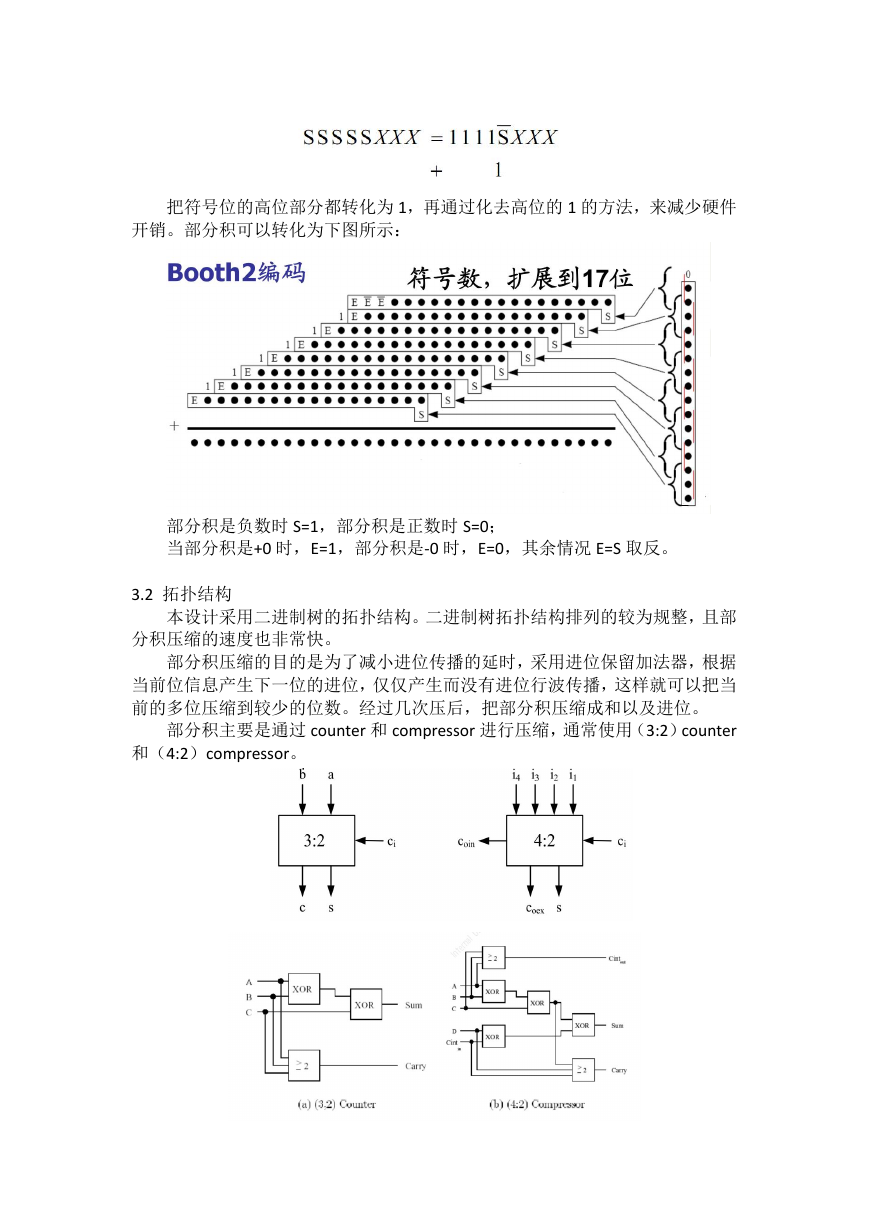

部分积主要是通过 counter 和 compressor 进行压缩,通常使用(3:2)counter

和(4:2)compressor。

�

(3:2)counter 其实质就是一个全加器,进位输入为 ci,进位输出为 c;

(4:2)compressor 可以由两个全加器组成,ci 为进位输入,Coin 为内部进位,

输入到下一位的进位输入 Ci,Coex 为输出进位。

上图为二进制树的拓扑结构图,每 4 个部分积输入到一个(4:2)compressor

中,产生两个输出,则 8 个部分积使用 3 次(4:2)compressor 就可以得到和和

进位。部分积的压缩方式可以见下图。

如图中所示,加上最后一个部分积的进位,共有 9 个部分积,本设计把最后

的进位位移到第一个部分积上,使用 5 个全加器,把进位融合到第一个部分积,

这样就转变成 8 个部分积了,再使用两级二进制树压缩,所以总共使用了三级压

缩,最终得到部分积的和和进位。为了免去不必要的硬件开销,对于部分积边上

的位采用 counter 压缩。上文提到的符号位扩展的改进方法,其目的也就是减少

硬件开销,所以在不影响性能的情况下,单独出来部分积的边缘位是十分有必要

的。

3.3 加法器

本设计采用超前进位加法器。为了使得乘法器的延时最小,最后一级的加法

器采用传播延时最小的超前进位加法器。

超前进位加法器的原理及构成,在此不做详述。

�

第四章 仿真验证

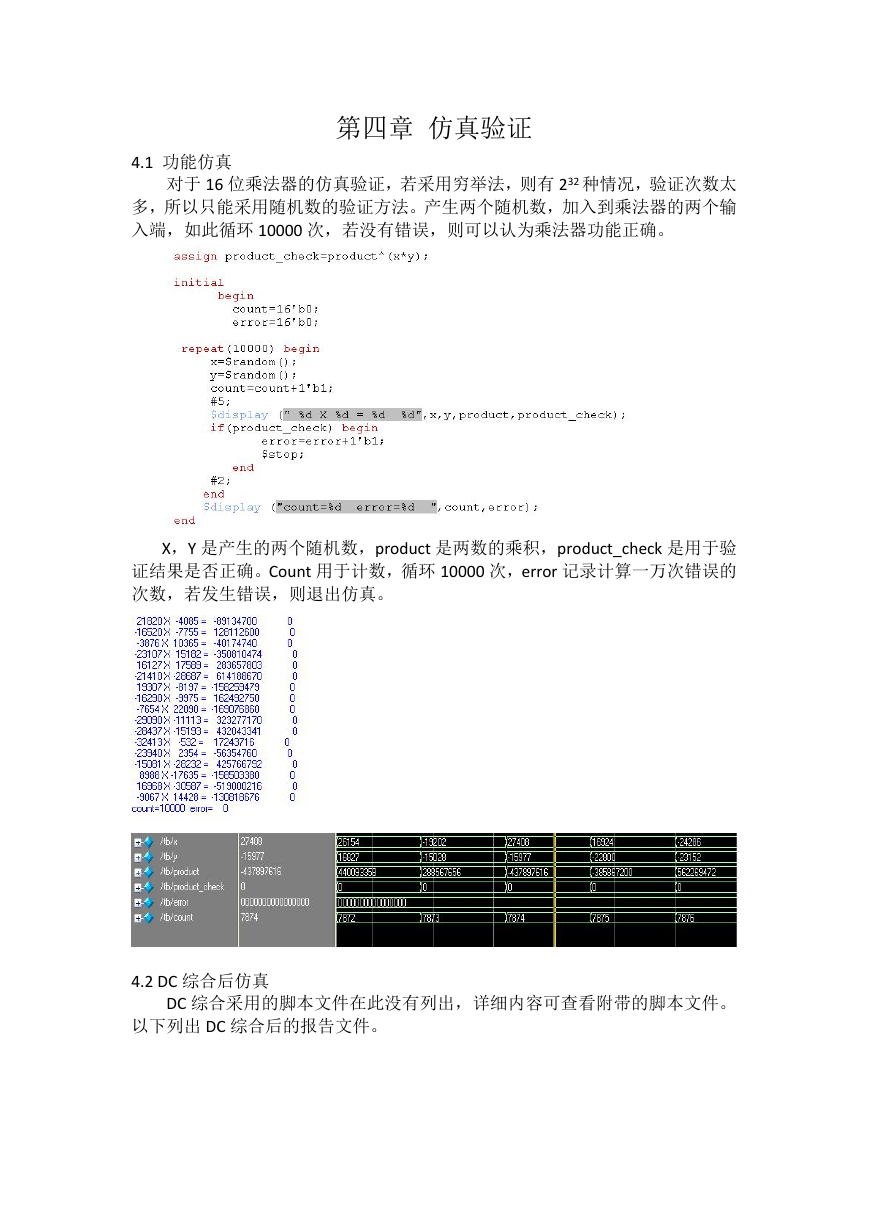

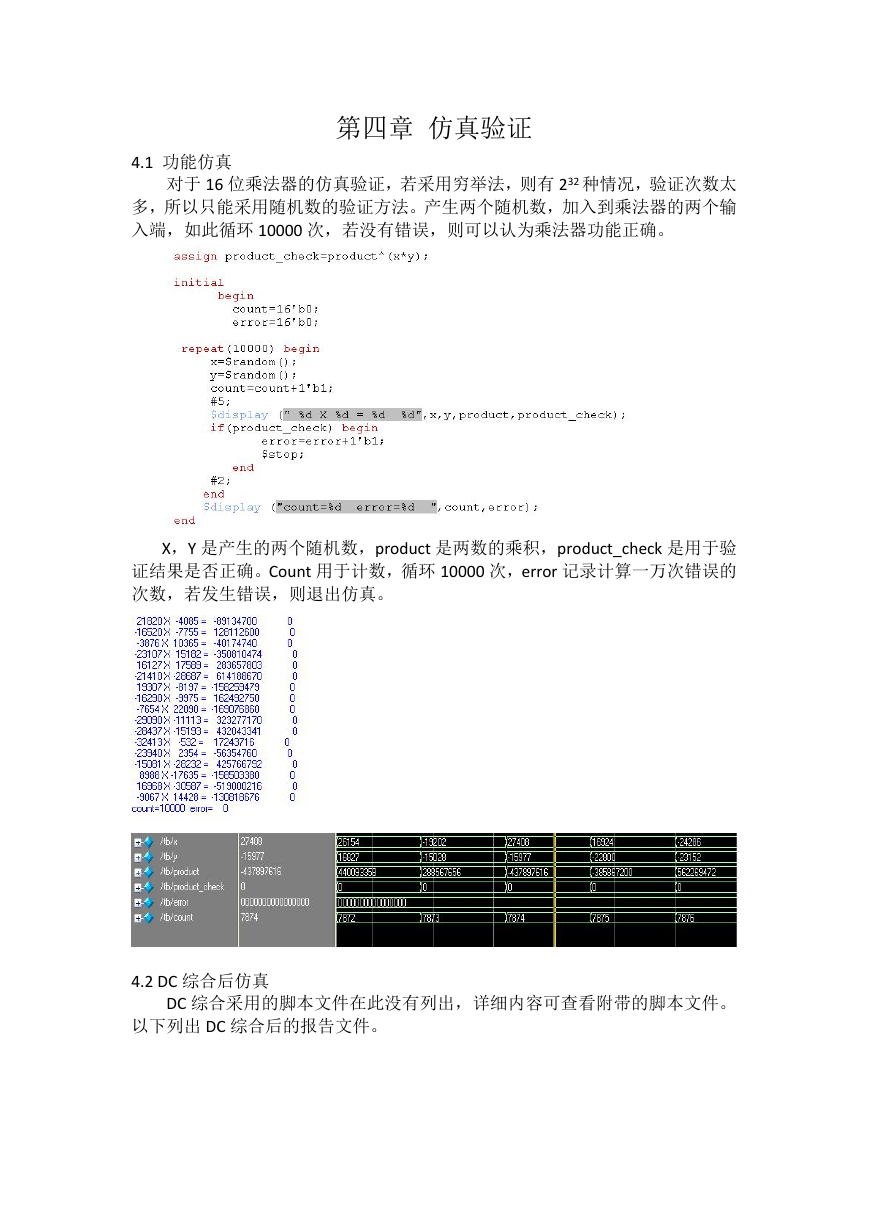

4.1 功能仿真

对于 16 位乘法器的仿真验证,若采用穷举法,则有 232 种情况,验证次数太

多,所以只能采用随机数的验证方法。产生两个随机数,加入到乘法器的两个输

入端,如此循环 10000 次,若没有错误,则可以认为乘法器功能正确。

X,Y 是产生的两个随机数,product 是两数的乘积,product_check 是用于验

证结果是否正确。Count 用于计数,循环 10000 次,error 记录计算一万次错误的

次数,若发生错误,则退出仿真。

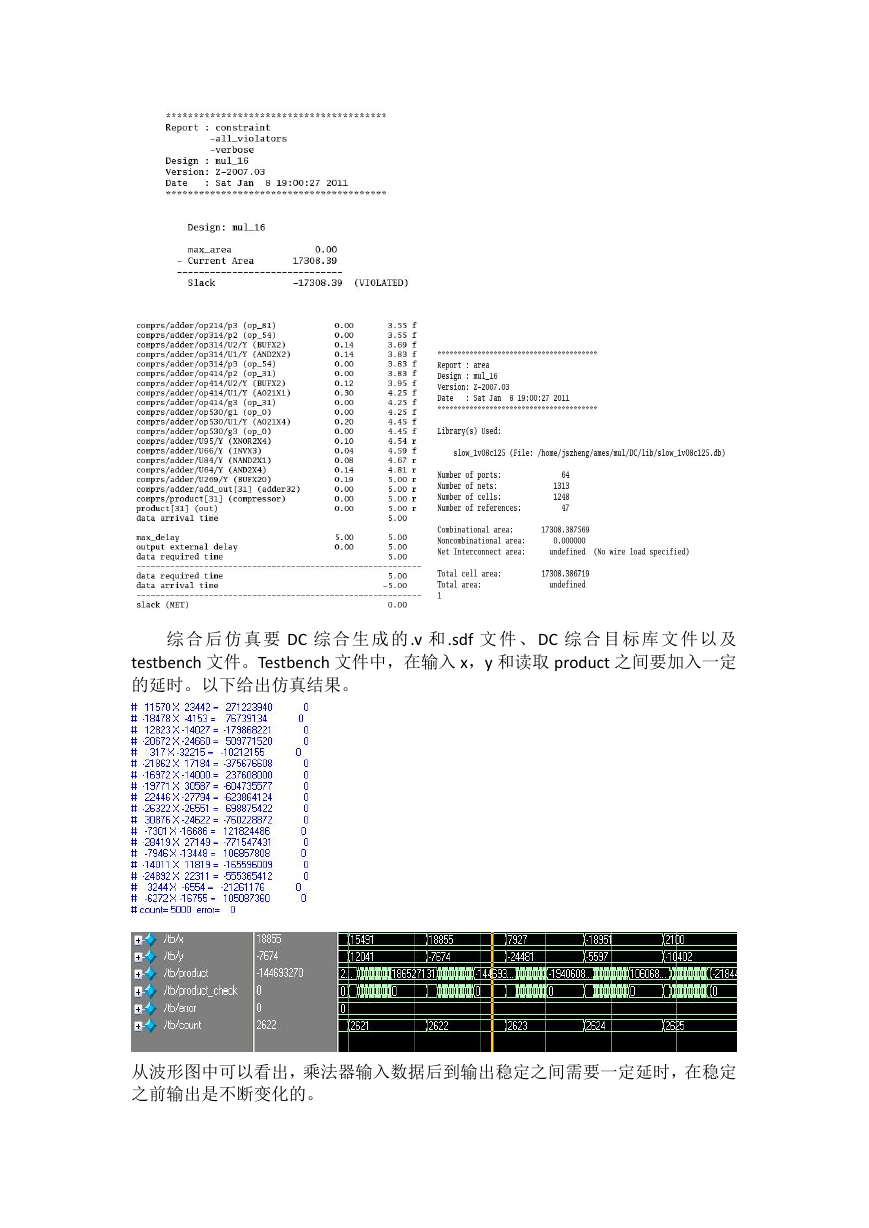

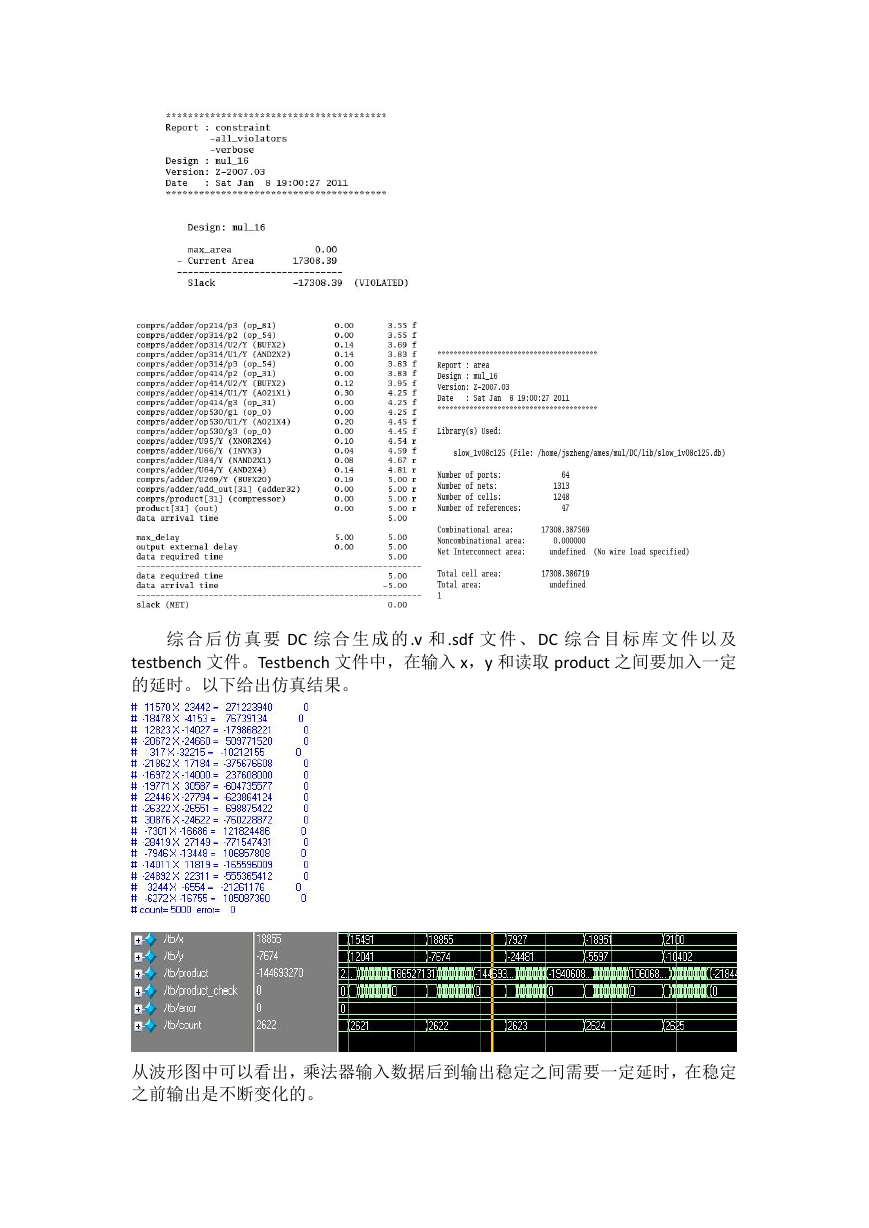

4.2 DC 综合后仿真

以下列出 DC 综合后的报告文件。

DC 综合采用的脚本文件在此没有列出,详细内容可查看附带的脚本文件。

�

综 合 后仿 真 要 DC 综 合 生成 的.v 和.sdf 文 件 、DC 综 合 目标 库 文 件 以 及

testbench 文件。Testbench 文件中,在输入 x,y 和读取 product 之间要加入一定

的延时。以下给出仿真结果。

从波形图中可以看出,乘法器输入数据后到输出稳定之间需要一定延时,在稳定

之前输出是不断变化的。

�

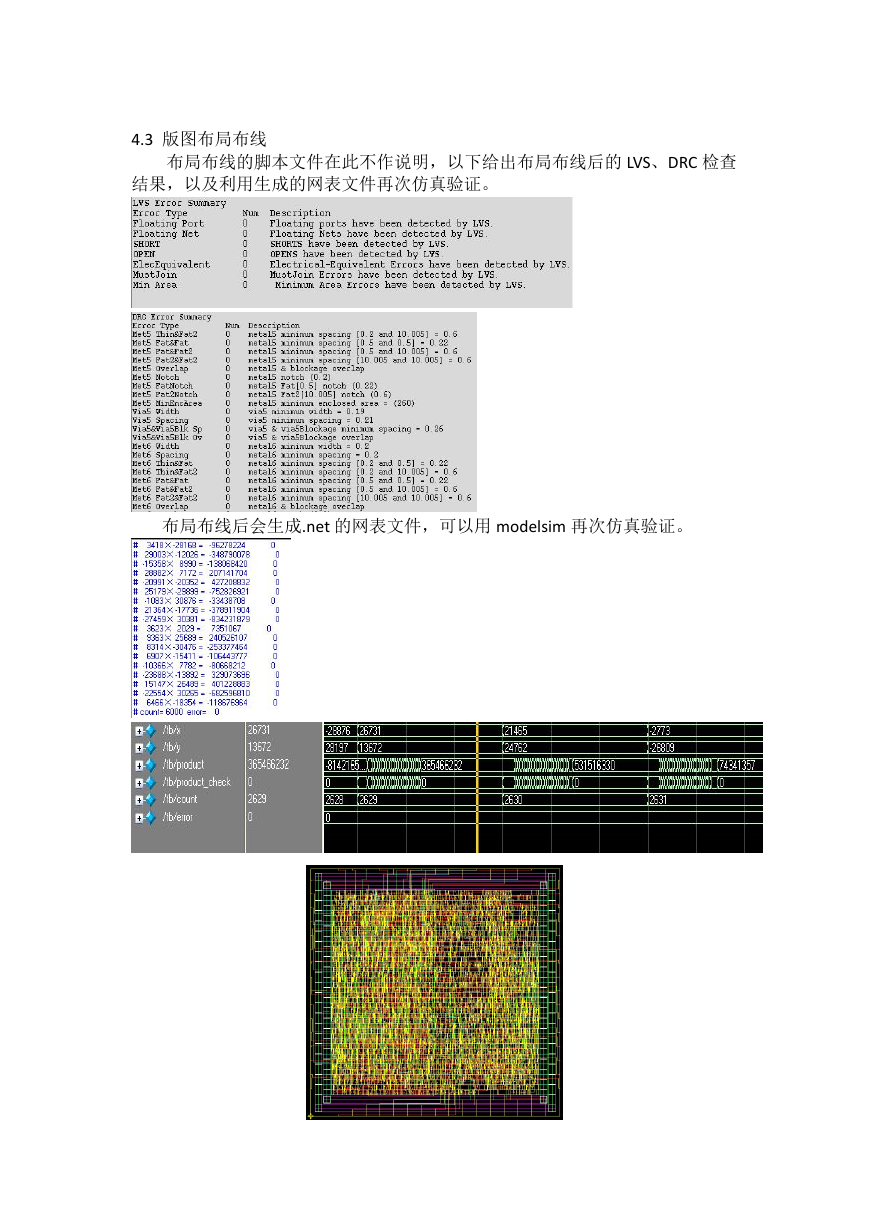

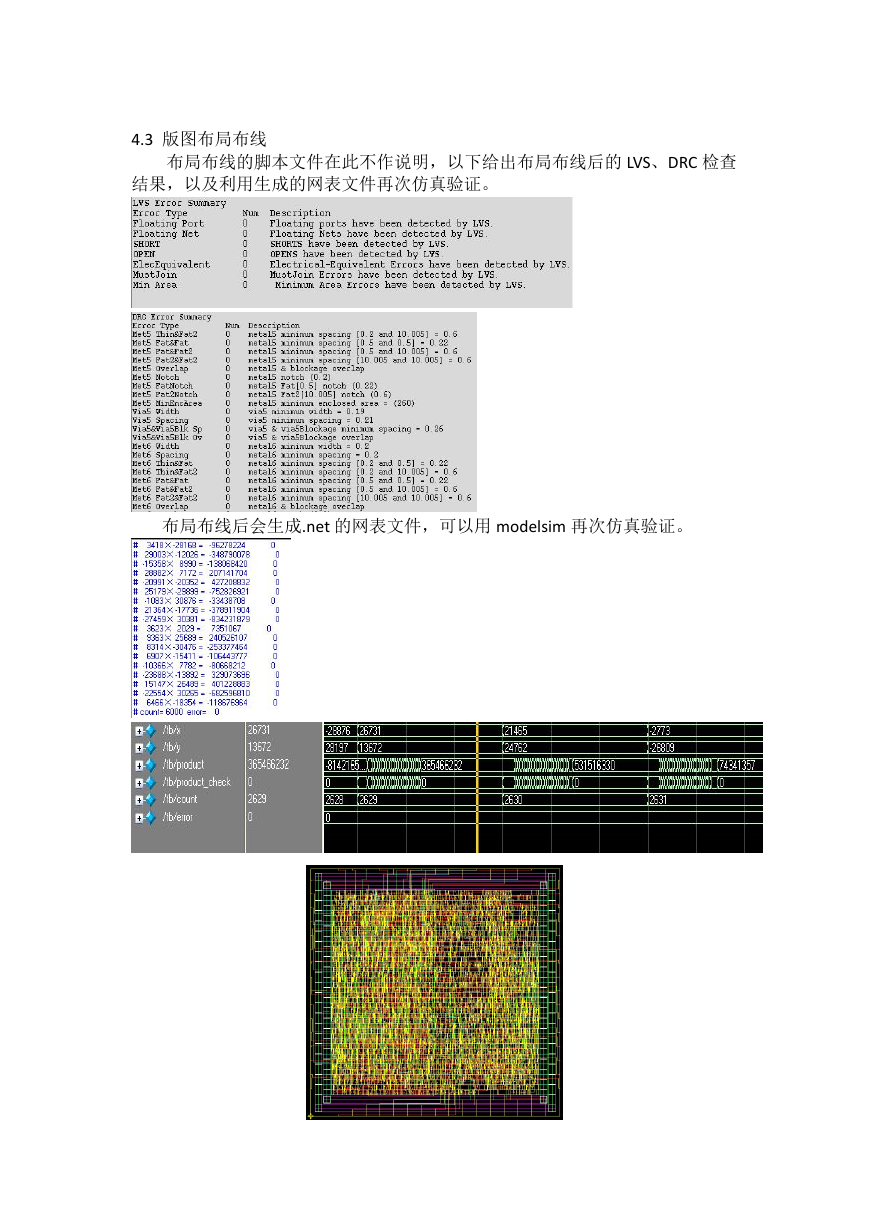

4.3 版图布局布线

布局布线的脚本文件在此不作说明,以下给出布局布线后的 LVS、DRC 检查

结果,以及利用生成的网表文件再次仿真验证。

布局布线后会生成.net 的网表文件,可以用 modelsim 再次仿真验证。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc