SMPTE SD/HD/3G-SDI 3.0

Product Guide

PG071 October 2, 2013

�

Table of Contents

IP Facts

Chapter 1: Overview

SMPTE Interface Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Licensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 2: Product Specification

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Core Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Chapter 4: Customizing and Generating the Core

Vivado Integrated Design Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Output Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Chapter 5: Constraining the Core

Required Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

SMPTE SD/HD/3G-SDI 3.0

PG071 October 2, 2013

www.xilinx.com

2

Send Feedback�

Chapter 6: Simulation

Chapter 7: Synthesis and Implementation

Chapter 8: Detailed Example Design

Chapter 9: Test Bench

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Appendix A: Verification, Compliance, and Interoperability

Hardware Testing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Appendix B: Migrating and Upgrading

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Upgrading in Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Appendix C: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Simulation Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Appendix D: Additional Resources

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Notice of Disclaimer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

SMPTE SD/HD/3G-SDI 3.0

PG071 October 2, 2013

www.xilinx.com

3

Send Feedback�

IP Facts

Supported

Device Family(1)

Resources

Documentation

Design Files

Example Design

Test Bench

Constraints File

Simulation

Models

Supported

Software Drivers

Design Entry

Tools

Simulation

Synthesis Tools

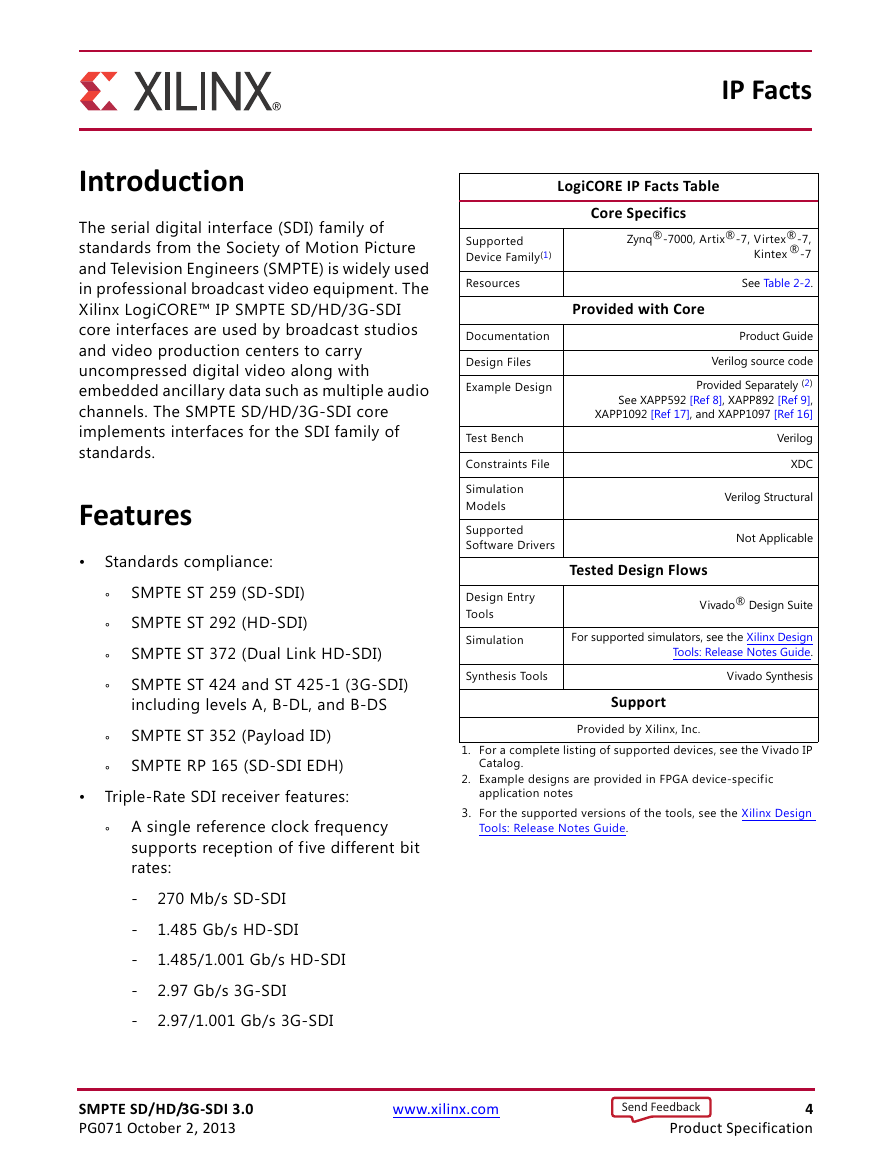

LogiCORE IP Facts Table

Core Specifics

Zynq®-7000, Artix®-7, Virtex®-7,

Kintex ®-7

Provided with Core

See Table 2-2.

Product Guide

Verilog source code

Provided Separately (2)

See XAPP592 [Ref 8], XAPP892 [Ref 9],

XAPP1092 [Ref 17], and XAPP1097 [Ref 16]

Verilog

XDC

Verilog Structural

Not Applicable

Tested Design Flows

Vivado® Design Suite

For supported simulators, see the Xilinx Design

Tools: Release Notes Guide.

Vivado Synthesis

Support

Provided by Xilinx, Inc.

1. For a complete listing of supported devices, see the Vivado IP

Catalog.

2. Example designs are provided in FPGA device-specific

application notes

3. For the supported versions of the tools, see the Xilinx Design

Tools: Release Notes Guide.

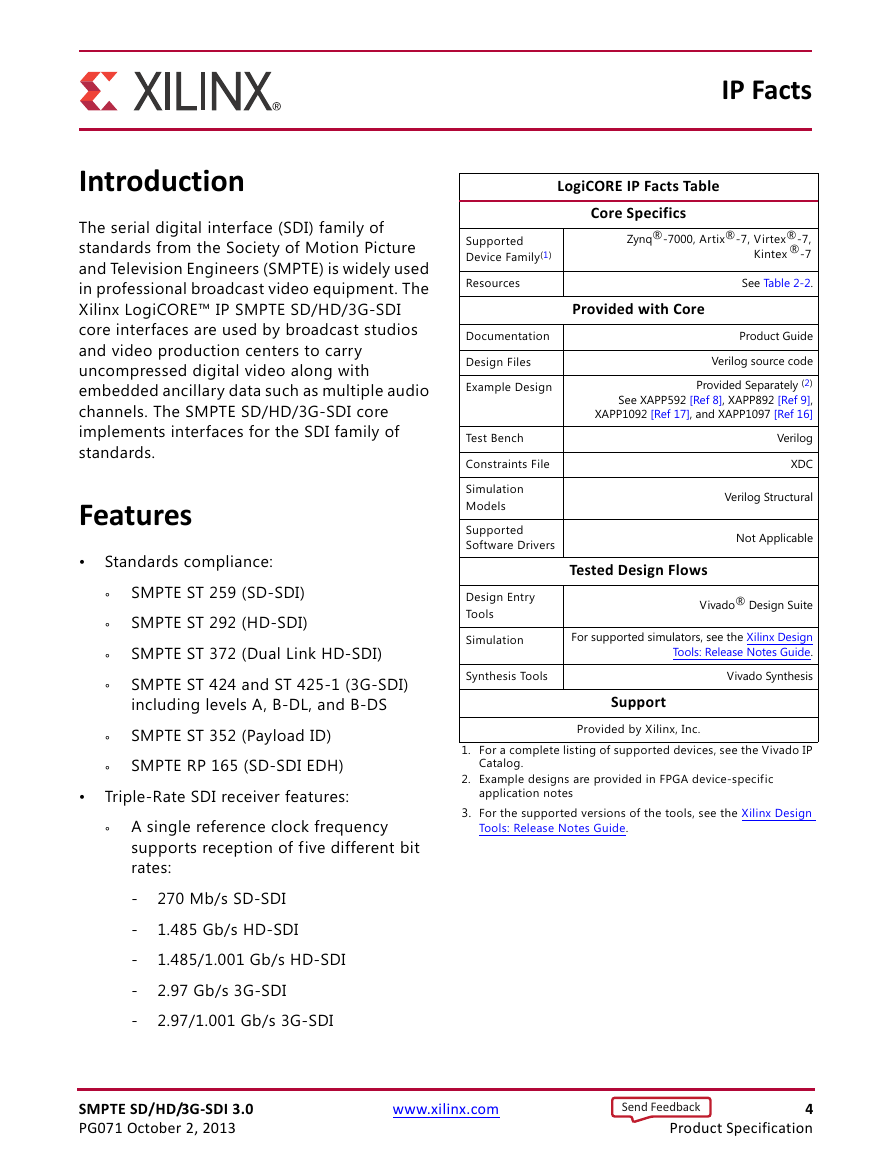

Introduction

The serial digital interface (SDI) family of

standards from the Society of Motion Picture

and Television Engineers (SMPTE) is widely used

in professional broadcast video equipment. The

Xilinx LogiCORE™ IP SMPTE SD/HD/3G-SDI

core interfaces are used by broadcast studios

and video production centers to carry

uncompressed digital video along with

embedded ancillary data such as multiple audio

channels. The SMPTE SD/HD/3G-SDI core

implements interfaces for the SDI family of

standards.

Features

•

Standards compliance:

•

°

°

°

°

°

SMPTE ST 259 (SD-SDI)

SMPTE ST 292 (HD-SDI)

SMPTE ST 372 (Dual Link HD-SDI)

SMPTE ST 424 and ST 425-1 (3G-SDI)

including levels A, B-DL, and B-DS

SMPTE ST 352 (Payload ID)

SMPTE RP 165 (SD-SDI EDH)

°

Triple-Rate SDI receiver features:

°

A single reference clock frequency

supports reception of five different bit

rates:

-

-

-

-

-

270 Mb/s SD-SDI

1.485 Gb/s HD-SDI

1.485/1.001 Gb/s HD-SDI

2.97 Gb/s 3G-SDI

2.97/1.001 Gb/s 3G-SDI

SMPTE SD/HD/3G-SDI 3.0

PG071 October 2, 2013

www.xilinx.com

4

Product Specification

Send Feedback�

°

Automatically detects incoming SDI standard and bit rate

Automatically detects incoming video transport format

°

° Detects and captures ST 352 packets

Checks for CRC errors for HD-SDI and 3G-SDI

°

° Optionally checks for EDH errors for SD-SDI

Triple-Rate SDI transmitter features:

° Only two reference clock frequencies are required to transmit five different bit rates:

•

-

-

-

-

-

270 Mb/s SD-SDI

1.485 Gb/s HD-SDI

1.485/1.001 Gb/s HD-SDI

2.97 Gb/s 3G-SDI

2.97/1.001 Gb/s 3G-SDI

° Generates and inserts CRC and line numbers for HD-SDI and 3G-SDI

° Generates and inserts EDH packets for SD-SDI

° Generates and inserts ST 352 packets for all SDI standards

SMPTE SD/HD/3G-SDI 3.0

PG071 October 2, 2013

www.xilinx.com

5

Product Specification

Send Feedback�

Chapter 1

Overview

SMPTE Interface Standards

The SMPTE SD/HD/3G-SDI core implements three main SMPTE interface standards:

SD-SDI (SMPTE ST 259): SDTV Digital Signal/Data - Serial Digital Interface

•

• HD-SDI (SMPTE ST 292-1): 1.5 Gb/s Signal/Data Serial Interface

•

3G-SDI (SMPTE ST 424): 3 Gb/s Signal/Data Serial Interface

In addition, two SMPTE SDI receivers or transmitters can be combined to implement SMPTE

ST 372 Dual Link HD-SDI interfaces.

SD-SDI

The SMPTE SD/HD/3G-SDI core is designed to support the 270 Mb/s bit rate (level C) of the

SD-SDI standard.

The SMPTE SD/HD/3G-SDI core fully supports the SMPTE RP 165 Error Detection and

Handling (EDH) standard for the receive and transmit sections.

HD-SDI

Although this standard is called a 1.5 Gb/s interface, the bit rates supported by HD-SDI are

actually 1.485 Gb/s and 1.485/1.001 Gb/s. The SMPTE SD/HD/3G-SDI core fully supports

both of these bit rates. The SMPTE SD/HD/3G-SDI core also fully supports generation

(TX-side) and checking (RX-side) of CRC values for each video line and the insertion

(TX-side) and capture (RX-side) of line number values for each line.

3G-SDI

This standard is called a 3 Gb/s interface, but the actual bit rates are 2.97 Gb/s and 2.97/

1.001 Gb/s. The SMPTE SD/HD/3G-SDI core fully supports both of these bit rates. 3G-SDI

supports several different mapping levels, described in the SMPTE ST 425-1 standard. These

levels are called A, B-DL, and B-DS. The SMPTE SD/HD/3G-SDI core supports all three of

SMPTE SD/HD/3G-SDI 3.0

PG071 October 2, 2013

www.xilinx.com

6

Send Feedback�

SMPTE Interface Standards

these levels. As with the HD-SDI standard, the SMPTE SD/HD/3G-SDI core supports CRC

generation and checking and line number insertion and capture for 3G-SDI.

Payload ID

The SMPTE SD/HD/3G-SDI core implements a SMPTE ST 352 payload ID ancillary data

packet insertion capability for the transmitter that works in all SDI modes (SD-SDI, HD-SDI,

3G-SDI, and dual link HD-SDI). The receive side also detects and captures the four data

bytes of ST 352 payload ID packets.

Ancillary Data Support

The SMPTE SD/HD/3G-SDI core allows the application to implement ancillary data packet

insertion prior to transmission. While the core doesn't provide ancillary data packet

insertion capability, except for ST 352 payload ID packets, it has the necessary data paths to

allow ancillary data packet insertion to be implemented by the application. On the receive

side, all embedded ancillary data is preserved by the SMPTE SD/HD/3G-SDI core's receiver

section and is present in the SDI data streams output from the core. Applications can

process the received SDI data streams to receive and/or modify the ancillary data as

needed.

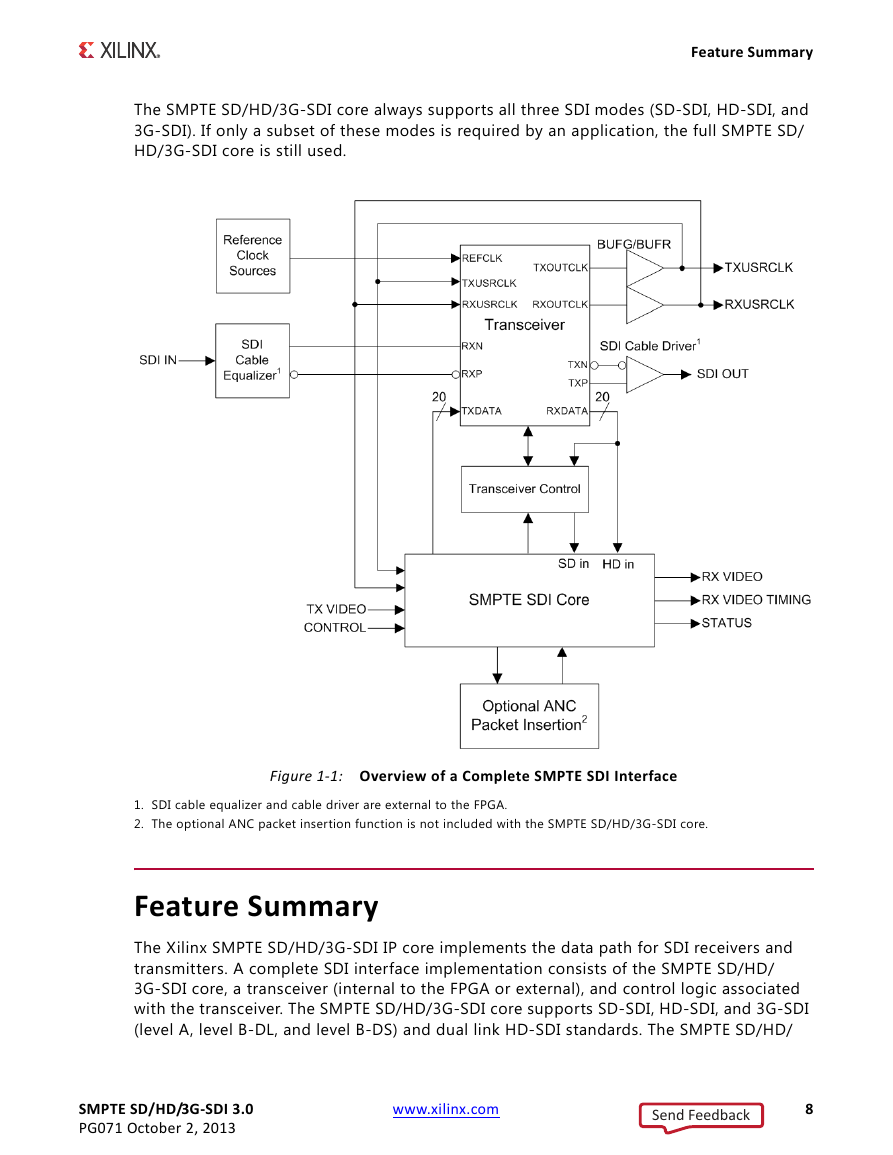

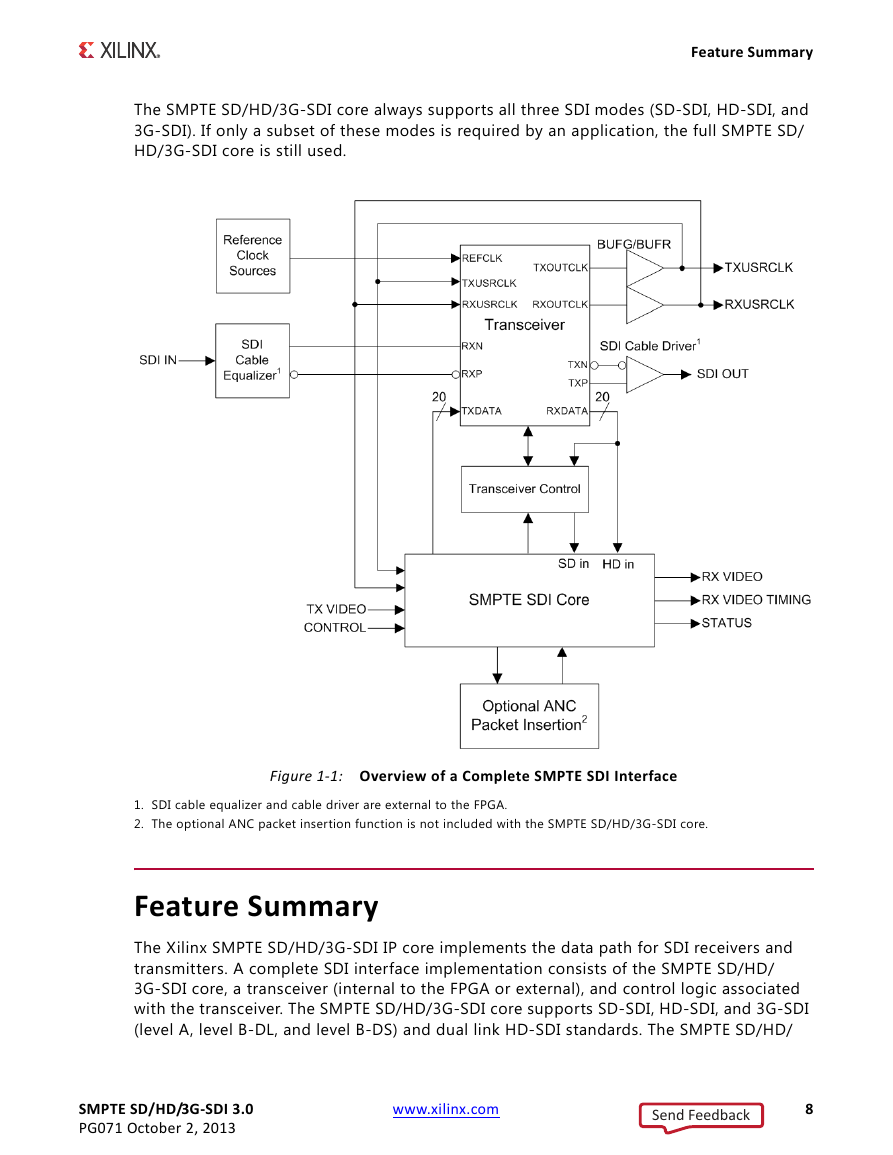

Complete SMPTE SDI Interface Solution

A complete SMPTE SDI interface is comprised of:

• A multi-rate SDI-compliant transceiver

•

The SMPTE SD/HD/3G-SDI core

• Control logic for the transceiver

•

•

Industry standard SDI cable driver (for TX) and SDI cable equalizer (for RX)

Transceiver reference clock source(s)

Figure 1-1 shows a high-level block diagram of an SDI receive/transmit interface using the

SMPTE SD/HD/3G-SDI core. In this figure, a transceiver internal to the Xilinx FPGA is used

with the SMPTE SD/HD/3G-SDI core.

The SMPTE SD/HD/3G-SDI core implements one SDI receiver and one SDI transmitter. If

only a receiver or only a transmitter is needed by the application, the input ports for the

unused half of the core can be tied to ground and the output ports left unconnected. The

synthesis tool will optimize the unused portion of the core out of the application.

When both the receiver and transmitter sections of the SMPTE SD/HD/3G-SDI core are

used, the receiver and transmitter are completely independent. They can be operating in

different SDI modes and bit rates (receiving 3G-SDI at 2.97/1.001 Gb/s while transmitting

SD-SDI at 270 Mb/s or HD-SDI at either bit rate, for example).

SMPTE SD/HD/3G-SDI 3.0

PG071 October 2, 2013

www.xilinx.com

7

Send Feedback�

The SMPTE SD/HD/3G-SDI core always supports all three SDI modes (SD-SDI, HD-SDI, and

3G-SDI). If only a subset of these modes is required by an application, the full SMPTE SD/

HD/3G-SDI core is still used.

X-Ref Target - Figure 1-1

Feature Summary

Figure 1-1: Overview of a Complete SMPTE SDI Interface

1. SDI cable equalizer and cable driver are external to the FPGA.

2. The optional ANC packet insertion function is not included with the SMPTE SD/HD/3G-SDI core.

Feature Summary

The Xilinx SMPTE SD/HD/3G-SDI IP core implements the data path for SDI receivers and

transmitters. A complete SDI interface implementation consists of the SMPTE SD/HD/

3G-SDI core, a transceiver (internal to the FPGA or external), and control logic associated

with the transceiver. The SMPTE SD/HD/3G-SDI core supports SD-SDI, HD-SDI, and 3G-SDI

(level A, level B-DL, and level B-DS) and dual link HD-SDI standards. The SMPTE SD/HD/

SMPTE SD/HD/3G-SDI 3.0

PG071 October 2, 2013

www.xilinx.com

8

Send Feedback�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc