1

2

3

4

5

6

A

P2

VCC

VCC

D1

D3

D5

D7

1

2

3

4

5

6

7

8

9

1K

D2

D4

D6

D8

20

10

19

18

17

16

15

14

13

12

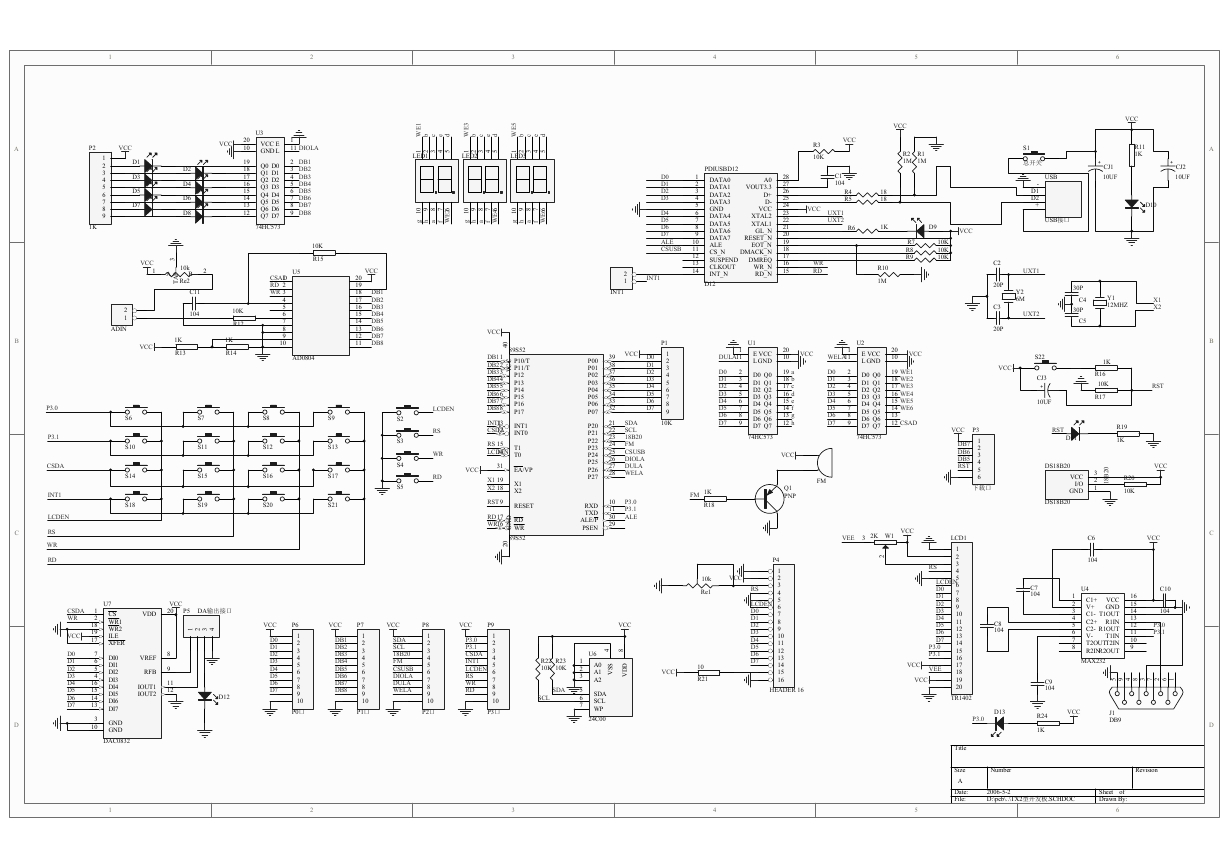

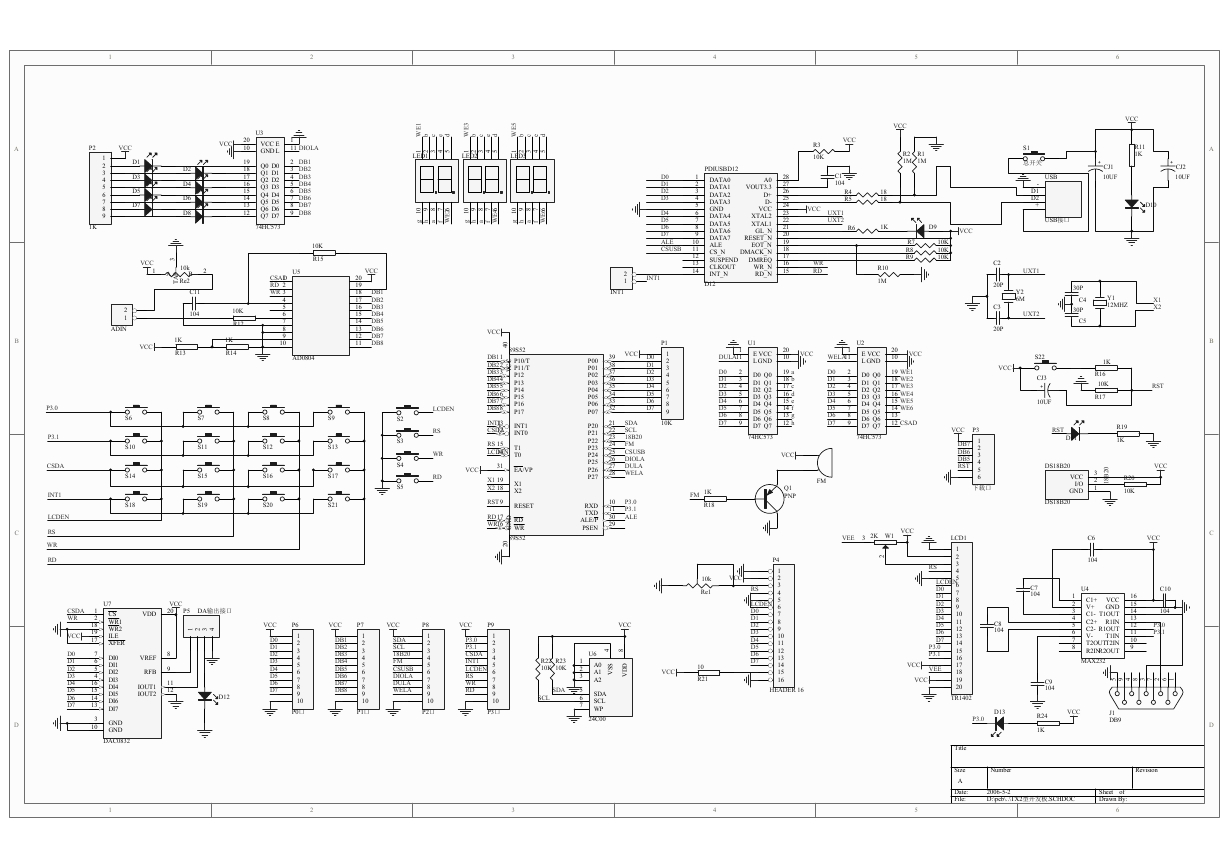

U3

VCC

GND

E

L

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

D0

D1

D2

D3

D4

D5

D6

D7

74HC573

VCC

1

3

10k

B

Re2

A

P

A

T

2

C11

104

VCC

1K

R13

2

1

ADIN

10K

R12

1K

R14

CSAD

1

2

RD

WR

3

4

5

6

7

8

9

10

1

E

W

b

c

e

d

3

E

W

b

c

e

d

5

E

W

b

c

e

d

12345

LED1

12345

LED2

12345

LED3

0

1

g

6789

6

E

W

h

a

f

0

1

g

6789

2

E

W

h

a

f

0

1

g

6789

4

E

W

h

a

f

VCC

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

20

19

18

17

16

15

14

13

12

11

VCC

0

4

1

11

DIOLA

2

3

4

5

6

7

8

9

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

10K

R15

U5

AD0804

D0

D1

D2

D3

D4

D5

D6

D7

ALE

CSUSB

1

2

3

4

5

6

7

8

9

10

11

12

13

14

PDIUSBD12

DATA0

DATA1

DATA2

DATA3

GND

DATA4

DATA5

DATA6

DATA7

ALE

CS_N

SUSPEND

CLKOUT

INT_N

A0

VOUT3.3

D+

D-

VCC

XTAL2

XTAL1

GL_N

RESET_N

EOT_N

DMACK_N

DMREQ

WR_N

RD_N

D12

28

27

26

25

24

23

22

21

20

19

18

17

16

15

2

1

INT1

INT1

VCC

R2

1M

R1

1M

D9

VCC

R7

R8

R9

10K

10K

10K

VCC

R3

10K

C1

104

R4

R5

UXT1

UXT2

R6

VCC

WR

RD

18

18

1K

R10

1M

S6

S10

S14

S18

S7

S11

S15

S19

S8

S12

S16

S20

S9

S13

S17

S21

LCDEN

RS

WR

RD

S2

S3

S4

S5

P3.0

P3.1

CSDA

INT1

LCDEN

RS

WR

RD

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

1

2

3

4

5

6

7

8

INT1

13

CSDA

12

RS

LCDEN

15

14

C

C

V

89S52

P10/T

P11/T

P12

P13

P14

P15

P16

P17

INT1

INT0

T1

T0

EA/VP

X1

X2

RESET

VCC

31

X1

X2

19

18

RST

9

RD

WR

17

16

D

N

G

RD

WR

89S52

0

2

D0

D1

D2

D3

D4

D5

D6

D7

P1

1

2

3

4

5

6

7

8

9

10K

VCC

SDA

SCL

18B20

FM

CSUSB

DIOLA

DULA

WELA

P3.0

P3.1

ALE

39

38

37

36

35

34

33

32

21

22

23

24

25

26

27

28

10

11

30

29

P00

P01

P02

P03

P04

P05

P06

P07

P20

P21

P22

P23

P24

P25

P26

P27

RXD

TXD

ALE/P

PSEN

1

11

DULA

D0

D1

D2

D3

D4

D5

D6

D7

2

3

4

5

6

7

8

9

U1

E

L

VCC

GND

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

74HC573

VCC

1

11

WELA

D0

D1

D2

D3

D4

D5

D6

D7

2

3

4

5

6

7

8

9

U2

E

L

VCC

GND

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

74HC573

20

10

19

18

17

16

15

14

13

12

VCC

WE1

WE2

WE3

WE4

WE5

WE6

CSAD

FM

20

10

19

18

17

16

15

14

13

12

a

b

c

d

e

f

g

h

VCC

Q1

PNP

VCC

DB7

DB6

DB5

RST

P3

1

2

3

4

5

6

下载口

VEE

3

2K

W1

VCC

1

LCD1

FM

1K

R18

VCC

10k

Re1

A

B

VCC

R11

1K

+ CJ1

10UF

+ CJ2

10UF

D10

S1

总开关

-

D1

D2

+

USB

USB接口

C2

20P

C3

20P

VCC

UXT1

Y2

6M

UXT2

30P

C4

30P

C5

Y1

12MHZ

X1

X2

S22

CJ3

+

10UF

1K

R16

10K

R17

RST

D11

DS18B20

VCC

I/O

GND

DS18B20

R19

1K

0

2

B

8

1

3

2

1

R20

10K

RST

VCC

B

C

D

VCC

20

P5 DA输出接口

VDD

1234

VREF

RFB

IOUT1

IOUT2

8

9

11

12

D12

CSDA

WR

VCC

D0

D1

D2

D3

D4

D5

D6

D7

1

2

18

19

17

7

6

5

4

16

15

14

13

3

10

U7

CS

WR1

WR2

ILE

XFER

DI0

DI1

DI2

DI3

DI4

DI5

DI6

DI7

GND

GND

DAC0832

VCC

D0

D1

D2

D3

D4

D5

D6

D7

P6

1

2

3

4

5

6

7

8

9

10

P0口

VCC

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

P7

1

2

3

4

5

6

7

8

9

10

P1口

VCC

SDA

SCL

18B20

FM

CSUSB

DIOLA

DULA

WELA

P8

1

2

3

4

5

6

7

8

9

10

P2口

VCC

P3.0

P3.1

CSDA

INT1

LCDEN

RS

WR

RD

P9

1

2

3

4

5

6

7

8

9

10

P3口

VCC

4

8

U6

A0

A1

A2

S

S

V

D

D

V

SDA

SCL

WP

24C00

R22

10K

R23

10K

SDA

SCL

1

2

3

5

6

7

VCC

10

R21

1

2

3

4

5

P4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

RS

LCDEN

D0

D1

D2

D3

D4

D5

D6

D7

HEADER 16

2

VCC

VCC

RS

1

2

3

4

5

LCDEN

6

D0

7

D1

8

D2

9

D3

10

D4

11

D5

12

D6

13

D7

14

P3.0

15

P3.1

16

17

18

19

20

VEE

C7

104

C8

104

TR1402

D13

P3.0

C9

104

R24

1K

VCC

C

C6

104

C10

104

P3.0

P3.1

1

2

3

4

5

6

7

8

U4

C1+

V+

C1-

C2+

C2-

V-

T2OUT

R2IN

VCC

GND

T1OUT

R1IN

R1OUT

T1IN

T2IN

R2OUT

MAX232

16

15

14

13

12

11

10

9

162738495

VCC

J1

DB9

D

Title

Size

A

Date:

File:

Number

Revision

2006-5-2

D:\pcb\..\TX2型开发板.SCHDOC

Sheet of

Drawn By:

6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc