Preliminary DataThis is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.July 2007 Rev 21/671STM32F103x6STM32F103x8 STM32F103xBPerformance line, ARM-based 32-bit MCU with Flash, USB, CAN,seven 16-bit timers, two ADCs and nine communication interfacesFeatures■Core: ARM 32-bit Cortex™-M3 CPU–72 MHz, 90 DMIPS with 1.25 DMIPS/MHz–Single-cycle multiplication and hardware division–Nested interrupt controller with 43 maskable interrupt channels–Interrupt processing (down to 6 CPU cycles) with tail chaining■Memories–32-to-128 Kbytes of Flash memory–6-to-20 Kbytes of SRAM■Clock, reset and supply management–2.0 to 3.6V application supply and I/Os –POR, PDR, and programmable voltage detector (PVD)–4-to-16 MHz quartz oscillator –Internal 8 MHz factory-trimmed RC–Internal 32 kHz RC–PLL for CPU clock–Dedicated 32 kHz oscillator for RTC with calibration■Low power–Sleep, Stop and Standby modes–VBAT supply for RTC and backup registers■2 x 12-bit, 1 µs A/D converters (16-channel)–Conversion range: 0 to 3.6 V–Dual-sample and hold capability–Synchronizable with advanced control timer–Temperature sensor■DMA–7-channel DMA controller –Peripherals supported: timers, ADC, SPIs, I2Cs and USARTs■Debug mode–Serial wire debug (SWD) & JTAG interfaces■Up to 80 fast I/O ports–32/49/80 5V-tolerant I/Os–All mappable on 16 external interrupt vectors–Atomic read/modify/write operations■Up to 7 timers–Up to three 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter–16-bit, 6-channel advanced control timer:up to 6 channels for PWM outputDead time generation and emergency stop–2 x 16-bit watchdog timers (Independent and Window)–SysTick timer: a 24-bit downcounter■Up to 9 communication interfaces–Up to 2 x I2C interfaces (SMBus/PMBus)–Up to 3 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)–Up to 2 SPIs (18 Mbit/s)–CAN interface (2.0B Active)–USB 2.0 full speed interface Table 1.Device summaryReferenceRoot part numberSTM32F103x6STM32F103C6, STM32F103R6STM32F103x8STM32F103C8, STM32F103R8 STM32F103V8STM32F103xBSTM32F103RB STM32F103VBLQFP6410 x 10 mmLQFP10014 x 14 mmLQFP487 x 7 mmBGA10010 x 10 mmwww.st.com�

ContentsSTM32F103xx2/67 Contents1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.1Device overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.2Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154Memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.1Test conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.1.1Minimum and maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.1.2Typical values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.1.3Typical curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.1.4Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.1.5Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.1.6Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245.1.7Current consumption measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 255.2Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265.3Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275.3.1General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275.3.2Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . . 275.3.3Embedded reset and power control block characteristics . . . . . . . . . . . 285.3.4Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285.3.5Supply current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295.3.6External clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 335.3.7Internal clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 375.3.8PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385.3.9Memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395.3.10EMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 405.3.11Absolute maximum ratings (electrical sensitivity) . . . . . . . . . . . . . . . . . 425.3.12I/O port pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 435.3.13NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47�

STM32F103xxContents 3/675.3.14TIM timer characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485.3.15Communications interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495.3.16CAN (controller area network) interface . . . . . . . . . . . . . . . . . . . . . . . . . 545.3.1712-bit ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 545.3.18Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 586Package characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 596.1Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 647Order codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 657.1Future family enhancements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 658Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66�

List of tablesSTM32F103xx4/67 List of tablesTable 1.Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1Table 2.Device features and peripheral counts (STM32F103xx performance line). . . . . . . . . . . . . . 7Table 3.Pin definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18Table 4.Voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Table 5.Current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Table 6.Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27Table 7.General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27Table 8.Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27Table 9.Embedded reset and power control block characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . 28Table 10.Embedded internal reference voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28Table 11.Maximum current consumption in Run and Sleep modes . . . . . . . . . . . . . . . . . . . . . . . . . 29Table 12.Maximum current consumption in Stop and Standby modes . . . . . . . . . . . . . . . . . . . . . . . 30Table 13.Typical current consumption in Run and Sleep modes . . . . . . . . . . . . . . . . . . . . . . . . . . . 31Table 14.Typical current consumption in Stop and Standby modes . . . . . . . . . . . . . . . . . . . . . . . . . 32Table 15.High-speed external (HSE) user clock characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33Table 16.Low-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33Table 17.HSE 4-16 MHz oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35Table 18.LSE oscillator characteristics (fLSE = 32.768 kHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36Table 19.HSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37Table 20.LSI oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37Table 21.Low-power mode wakeup timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38Table 22.PLL characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38Table 23.Flash memory characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39Table 24.Flash memory endurance and data retention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39Table 25.EMS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40Table 26.EMI characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41Table 27.ESD absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Table 28.Electrical sensitivities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Table 29.I/O static characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43Table 30.Output voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45Table 31.I/O AC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46Table 32.NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47Table 33.TIMx characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48Table 34.I2C characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49Table 35.SCL frequency (fPCLK1= 36 MHz.,VDD = 3.3 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50Table 36.SPI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51Table 37.USB DC electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53Table 38.USB: Full speed electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Table 39.ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Table 40.ADC accuracy (fPCLK2 = 14 MHz, fADC = 14 MHz, RAIN <10 kΩ, VDDA = 3.3V). . . . . . . . . 55Table 41.TS characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58Table 42.LFBGA100 - low profile fine pitch ball grid array package mechanical data. . . . . . . . . . . . 59Table 43.LQFP100 – 100-pin low-profile quad flat package mechanical data . . . . . . . . . . . . . . . . . 61Table 44.LQFP64 – 64 pin low-profile quad flat package mechanical data. . . . . . . . . . . . . . . . . . . . 62Table 45.LQFP48 – 48 pin low-profile quad flat package mechanical data. . . . . . . . . . . . . . . . . . . . 63Table 46.Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64Table 47.Order codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65�

STM32F103xxList of figures 5/67List of figuresFigure 1.STM32F103xx performance line block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14Figure 2.STM32F103xx performance line LQFP100 pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15Figure 3.STM32F103xx performance line LQFP64 pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16Figure 4.STM32F103xx performance line LQFP48 pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16Figure 5.STM32F103xx performance line BGA100 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17Figure 6.Memory map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22Figure 7.Pin loading conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24Figure 8.Pin input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24Figure 9.Power supply scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24Figure 10.Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25Figure 11.High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34Figure 12.Low-speed external clock source AC timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34Figure 13.Typical application with a 8-MHz crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35Figure 14.Typical application with a 32.768 kHz crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36Figure 15.Unused I/O pin connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44Figure 16.I/O AC characteristics definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47Figure 17.Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48Figure 18.I2C bus AC waveforms and measurement circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50Figure 19.SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52Figure 20.SPI timing diagram - slave mode and CPHA = 11). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52Figure 21.SPI timing diagram - master mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53Figure 22.USB timings: definition of data signal rise and fall time . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Figure 23.ADC accuracy characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56Figure 24.Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56Figure 25.Power supply and reference decoupling (VREF+ not connected to VDDA). . . . . . . . . . . . . . 57Figure 26.Power supply and reference decoupling (VREF+ connected to VDDA). . . . . . . . . . . . . . . . . 57Figure 27.LFBGA100 - low profile fine pitch ball grid array package outline . . . . . . . . . . . . . . . . . . . 59Figure 28.Recommended PCB design rules (0.80/0.75 mm pitch BGA) . . . . . . . . . . . . . . . . . . . . . . 60Figure 29.LQFP100 – 100-pin low-profile quad flat package outline . . . . . . . . . . . . . . . . . . . . . . . . . 61Figure 30.LQFP64 – 64 pin low-profile quad flat package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . 62Figure 31.LQFP48 – 48 pin low-profile quad flat package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . 63�

IntroductionSTM32F103xx6/67 1 IntroductionThis datasheet provides the STM32F103xx performance line ordering information and mechanical device characteristics.For information on programming, erasing and protection of the internal Flash memory please refer to the STM32F10xxx Flash programming reference manual, pm0042, available from www.st.com.For information on the Cortex-M3 core please refer to the Cortex-M3 Technical Reference Manual.2 DescriptionThe STM32F103xx performance line family incorporates the high-performance ARM Cortex-M3 32-bit RISC core operating at a 72 MHz frequency, high-speed embedded memories (Flash memory up to 128Kbytes and SRAM up to 20 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, three general purpose 16-bit timers plus one PWM timer, as well as standard and advanced communication interfaces: up to two I2Cs and SPIs, three USARTs, an USB and a CAN. The STM32F103xx performance line family operates in the −40 to +105 °C temperature range, from a 2.0 to 3.6V power supply. A comprehensive set of power-saving mode allows to design low-power applications.The complete STM32F103xx performance line family includes devices in 4 different package types: from 48 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.These features make the STM32F103xx performance line microcontroller family suitable for a wide range of applications:●Motor drive and application control●Medical and handheld equipment●PC peripherals gaming and GPS platforms●Industrial applications: PLC, inverters, printers, and scanners●Alarm systems, Video intercom, and HVACFigure1 shows the general block diagram of the device family. �

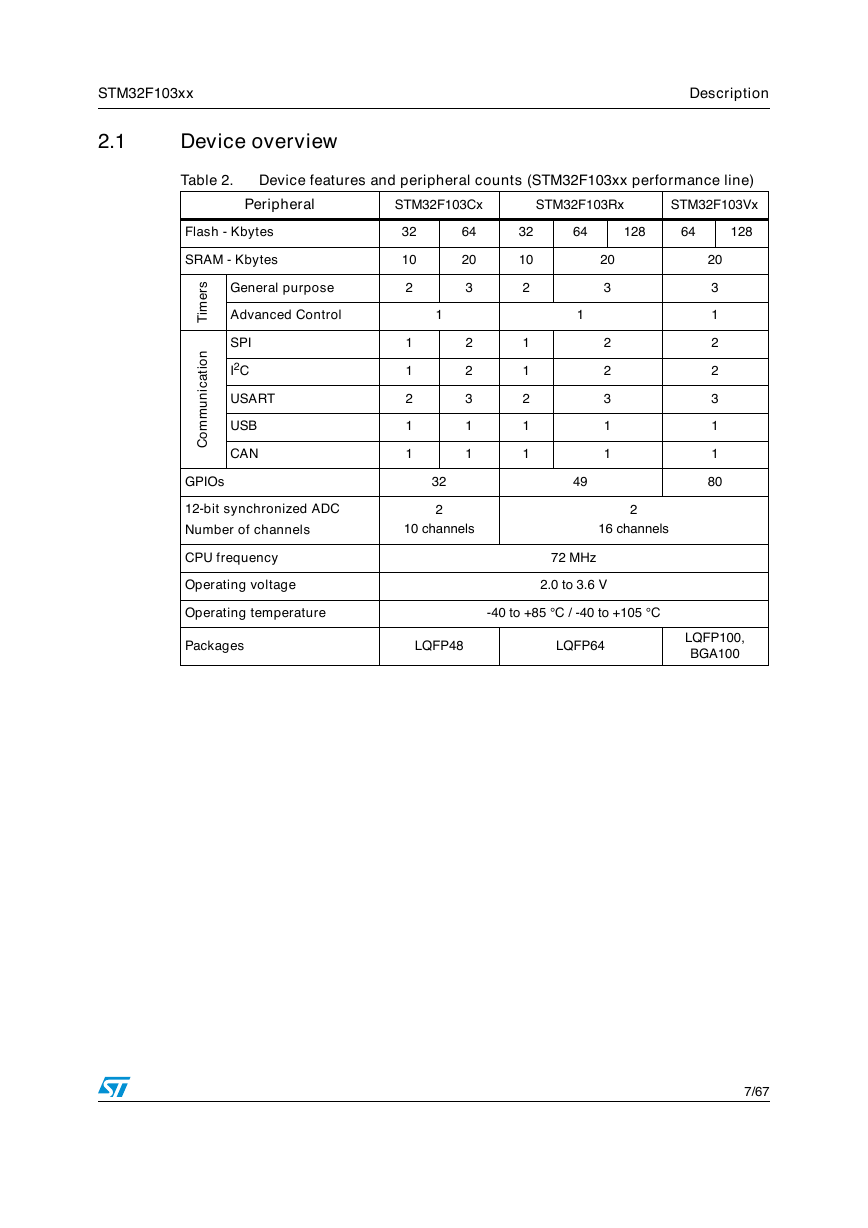

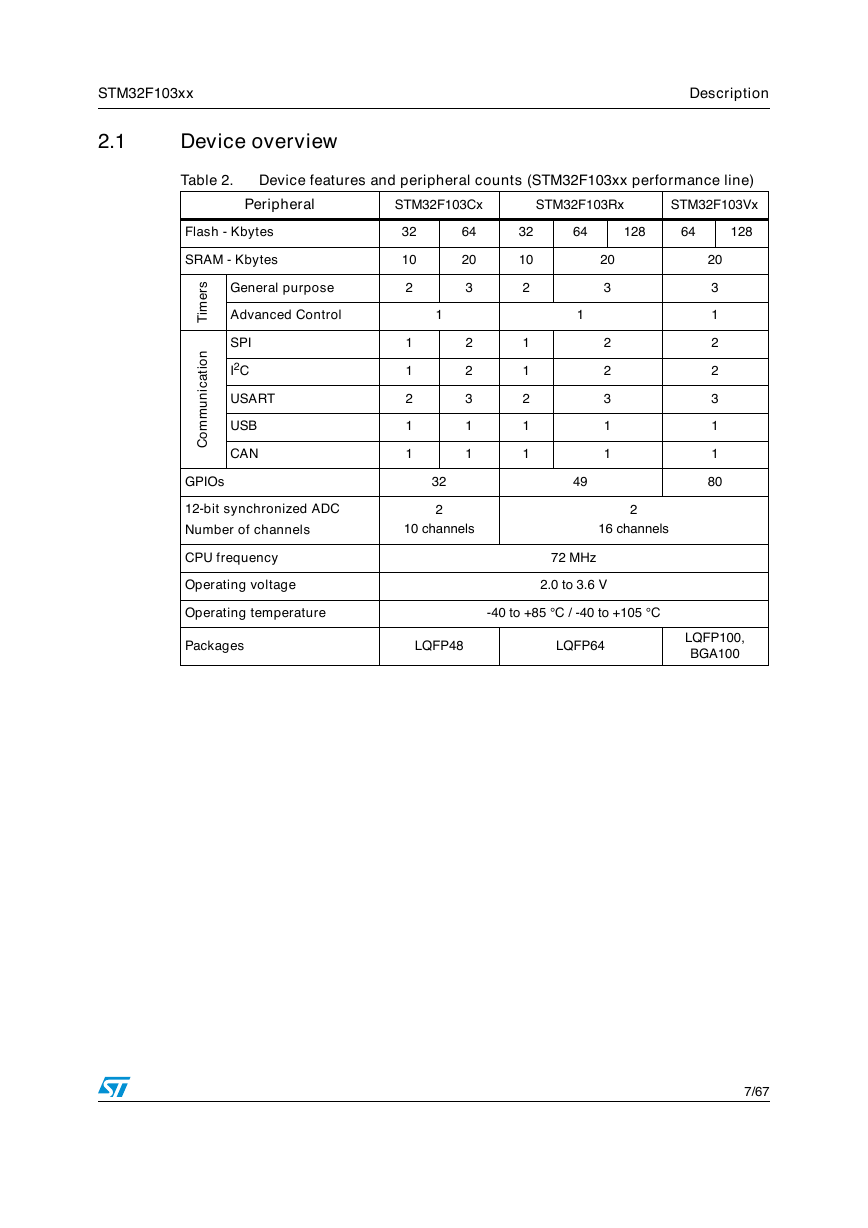

STM32F103xxDescription 7/672.1 Device overview Table 2.Device features and peripheral counts (STM32F103xx performance line)PeripheralSTM32F103CxSTM32F103RxSTM32F103VxFlash - Kbytes3264326412864128SRAM - Kbytes1020102020TimersGeneral purpose23233Advanced Control111CommunicationSPI12122I2C12122USART23233USB11111CAN1 1111GPIOs32498012-bit synchronized ADCNumber of channels210 channels216 channelsCPU frequency72 MHzOperating voltage2.0 to 3.6 VOperating temperature-40 to +85 °C / -40 to +105 °CPackagesLQFP48LQFP64LQFP100, BGA100�

DescriptionSTM32F103xx8/67 2.2 OverviewARM® CortexTM-M3 core with embedded Flash and SRAMThe ARM Cortex-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.The ARM Cortex-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.The STM32F103xx performance line family having an embedded ARM core, is therefore compatible with all ARM tools and software.Figure1 shows the general block diagram of the device family.Embedded Flash memory●Up to 128 Kbytes of embedded Flash is available for storing programs and data. Embedded SRAMUp to 20 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.Nested vectored interrupt controller (NVIC)The STM32F103xx performance line embeds a Nested Vectored Interrupt Controller able to handle up to 43 maskable interrupt channels (not including the 16 interrupt lines of Cortex-M3) and 16 priority levels. ●Closely coupled NVIC gives low latency interrupt processing●Interrupt entry vector table address passed directly to the core●Closely coupled NVIC core interface●Allows early processing of interrupts●Processing of late arriving higher priority interrupts●Support for tail-chaining●Processor state automatically saved●Interrupt entry restored on interrupt exit with no instruction overheadThis hardware block provides flexible interrupt management features with minimal interrupt latency.External interrupt/event controller (EXTI)The external interrupt/event controller consists of 19 edge detectors lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect external line with pulse width lower than the Internal APB2 clock period. Up to 80 GPIOs are connected to the 16 external interrupt lines.�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc