山东英才职业技术学院

毕业设计

院(系):计算机电子信息工程学院

专 业 :

班 级 :

姓 名 :

指导教师:王甲琛

200 年 4 月

1

�

8路抢答器控制系统设计任务与要求

设计任务书

设计任务:

利用 EDA 工具,基于硬件描述语言,借助 CPLD 器件,设计 8 路抢

答器控制系统。

具体要求:

1、8路抢答器控制系统是娱乐活动中经常使用的重要基础设备之

一,根据抢答要求,系统所需实现的功能如下:

(1)主持人按键清零,数码显示0,蜂鸣器不叫,进入抢答状态。

(2)主持人发出开始命令,8人开始抢答。其中一人先按下抢答

键,蜂鸣器发出鸣叫,数码显示该人号码,其他人再按键,系统不再

响应,直至主持人按键清零,下一次抢答开始。

2、设计构思系统原理结构框图

3、基于VHDL的设计(使用MAXPLUSII软件)

(1)源代码程序设计

(2)编译、管脚设置

(3)下载实验验证

4、PCB(印刷电路板)生成制作(使用PROTELL软件)

(1)原理图及元件封装设计

(2)网络表生成

(3)电路板制作

2

�

目 录

摘 要 ...................................................

Abstract ..................................................

引言 ......................................................

第一章 8 路抢答器功能与系统原理结构框图 ...................

第二章 基于 VHDL 的设计 ...................................

第三章 PCB(印刷电路板)生成制作 .........................

结束语 ....................................................

参考文献 ..................................................

3

�

摘 要

EDA技术的应用引起了电子产品系统开发的革命性变革。利用先进的EDA工具,

基于硬件描述语言,借助CPLD器件,可以进行系统级数字逻辑电路的设计。本文

以8路抢答器为例,介绍了在Max+plus II、PROTEL开发软件下,利用VHDL硬件描

述语言设计数字逻辑电路、PCB制作的过程和方法。

关键词:可编程逻辑器件 VHDL

EDA

8路抢答器控制系统。

Abstract

The EDA technology application has caused the electronic products system

development revolutionary transformation.Uses the advanced EDA tool, based on the

hardware description language, with the aid of the CPLD component, may carry on the

system-level numeral logic circuit the design.This article vies to answer first take 8

groups as an example, introduced in Max plus II, under the PROTEL development

software, uses the VHDL hardware description language design numeral logic circuit,

the PCB manufacture process and the method

Keywords : Programmable logical component VHDL the EDA 8 groups vie to

answer first the control system.

1

�

引言

随着电子技术的发展,可编程逻辑器件的出现,使得电子系统的设计者利用

EDA(电子设计自动化)软件,在实验室里就可以设计自己的专用集成电路ASIC器

件。

可编程逻辑器件是一种半导体集成器件的半成品。在可编程逻辑器件的芯片

中按一定方式(阵列形式或单元阵列形式)制作了大量的门、触发器等基本逻辑

器件,如对这些基本器件适当地连接(此连接的过程称为编程或配置),就可以

完成基个电路或系统的功能。

可编程逻辑器件大致可分为FPGA(现场可编程门阵列)、CPLD(复杂的可编

程逻辑器件)SPLD(简单的可编程逻辑器件)3类,它们的规模和结构有较大的区

别,但使用方法是基本一致的,其中应用最广泛的是FPGA和CPLD。

这种可编程ASIC不仅使设计的产品达到小型化、集成化和高可靠性,而且器

件具有用户可编程特性,大大缩短设计周期,减少了设计费用,降低了设计风险。

目前数字系统的设计可以直接面向用户需求,根据系统的行为功能要求,自上至

下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成器件,实现电子

设计自动化。

本文详细论述了使用EDA技术设计8路抢答器控制系统的过程。

2

�

第一章 8 路抢答器功能与系统原理结构框图

一、8 路抢答器控制系统的功能

8路抢答器控制系统是娱乐活动中经常使用的重要基础设备之一,根据抢答要

求,系统所需实现的功能如下:

(1)主持人按键清零,数码显示0,蜂鸣器不叫,进入抢答状态。

(2)主持人发出开始命令,8人开始抢答。其中一人先按下抢答键,蜂鸣器发

出鸣叫,数码显示该人号码,其他人再按键,系统不再响应,直至主持人按键清

零,下一次抢答开始。

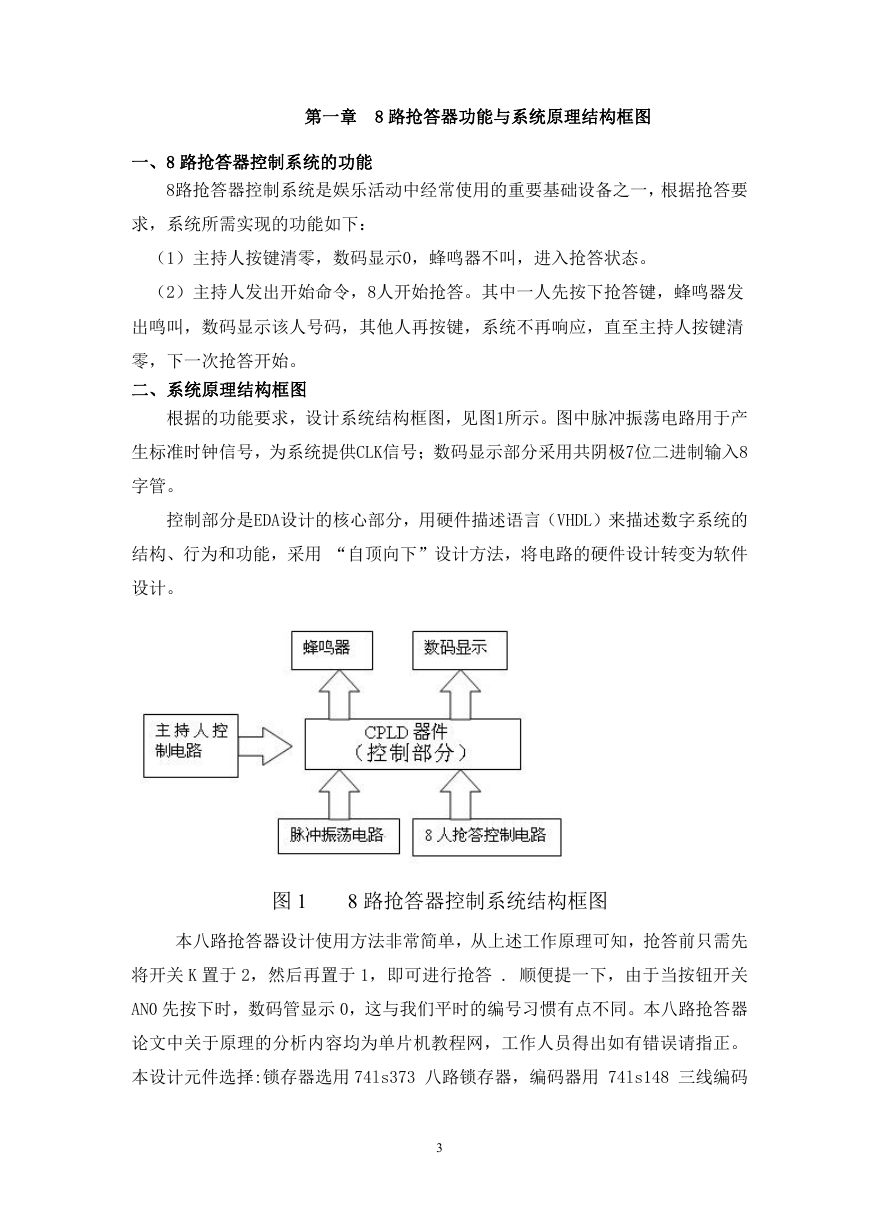

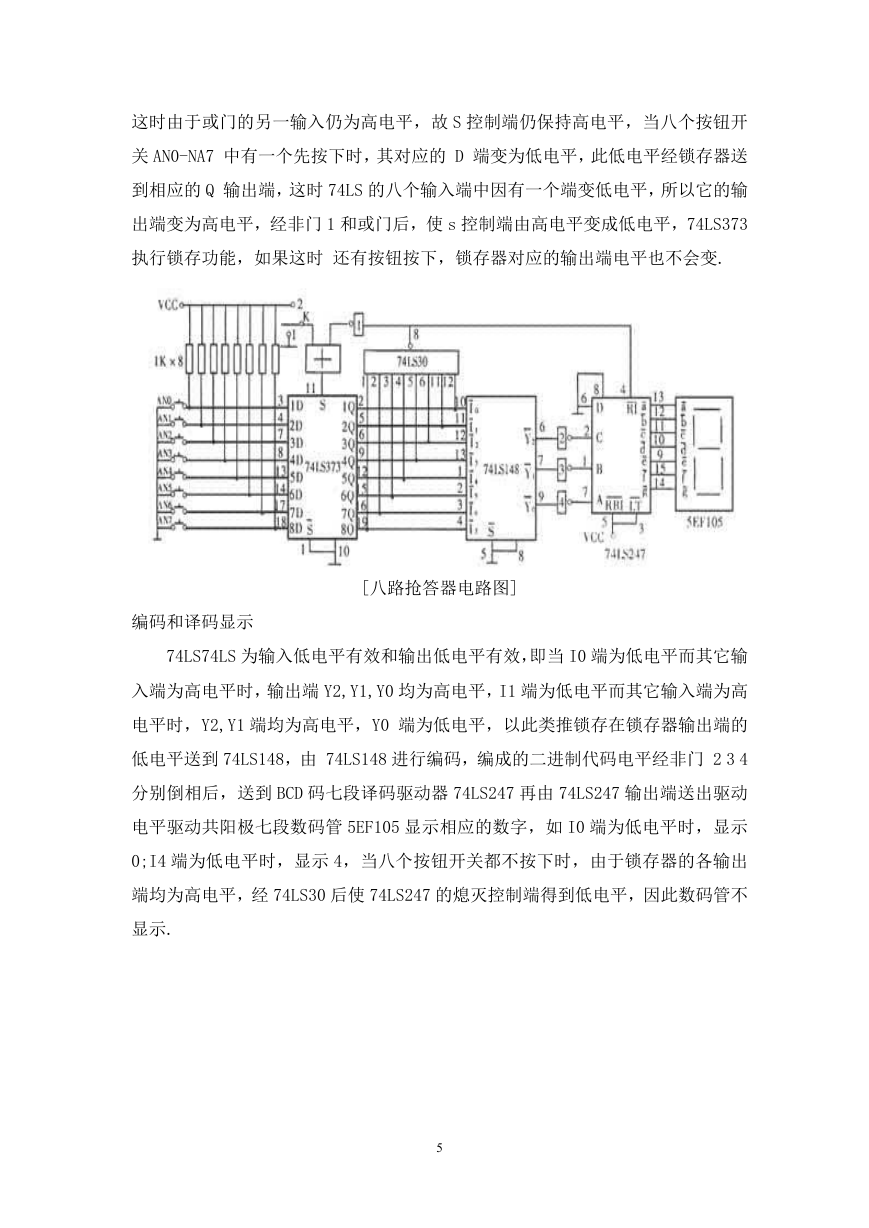

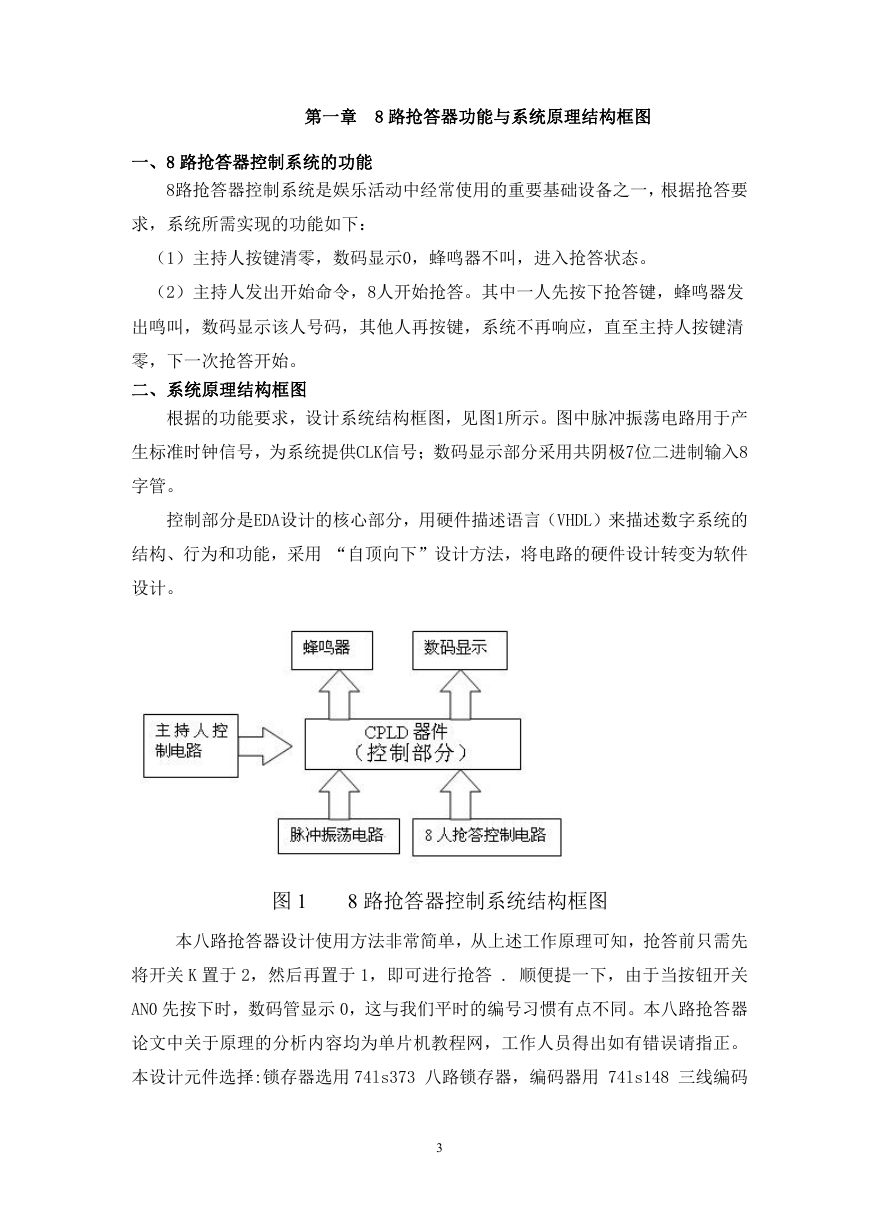

二、系统原理结构框图

根据的功能要求,设计系统结构框图,见图1所示。图中脉冲振荡电路用于产

生标准时钟信号,为系统提供CLK信号;数码显示部分采用共阴极7位二进制输入8

字管。

控制部分是EDA设计的核心部分,用硬件描述语言(VHDL)来描述数字系统的

结构、行为和功能,采用 “自顶向下”设计方法,将电路的硬件设计转变为软件

设计。

图 1

8 路抢答器控制系统结构框图

本八路抢答器设计使用方法非常简单,从上述工作原理可知,抢答前只需先

将开关 K 置于 2,然后再置于 1,即可进行抢答 . 顺便提一下,由于当按钮开关

AN0 先按下时,数码管显示 0,这与我们平时的编号习惯有点不同。本八路抢答器

论文中关于原理的分析内容均为单片机教程网,工作人员得出如有错误请指正。

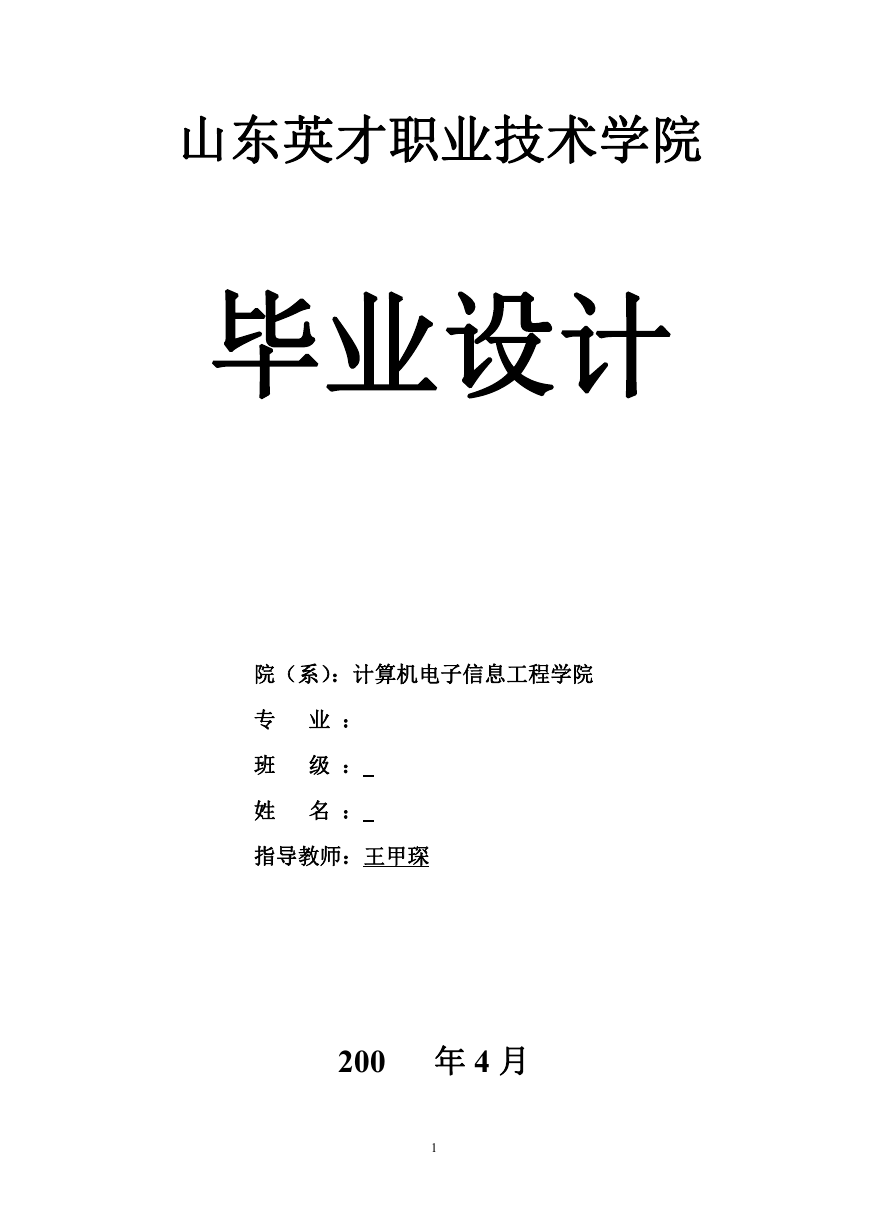

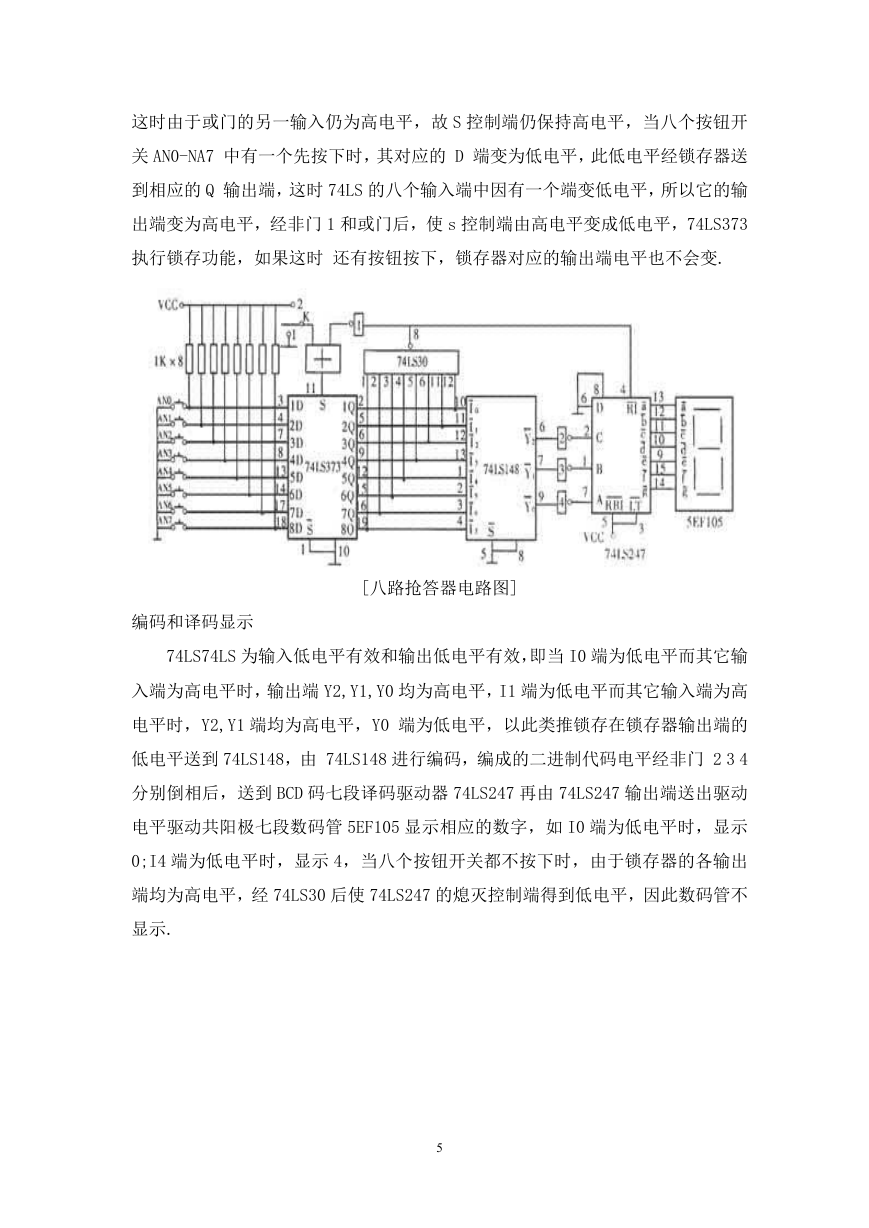

本设计元件选择:锁存器选用 74ls373 八路锁存器,编码器用 74ls148 三线编码

3

�

器,数码显示驱动器用 bcd 码七段译码器 74ls247 与共阳极七段数码管搭配,控

制电路由八输入与非门 74ls30 和一个或门、一个非门构成,或门用 74ls32 二输

入四或门,非门 74ls04 六反相器。

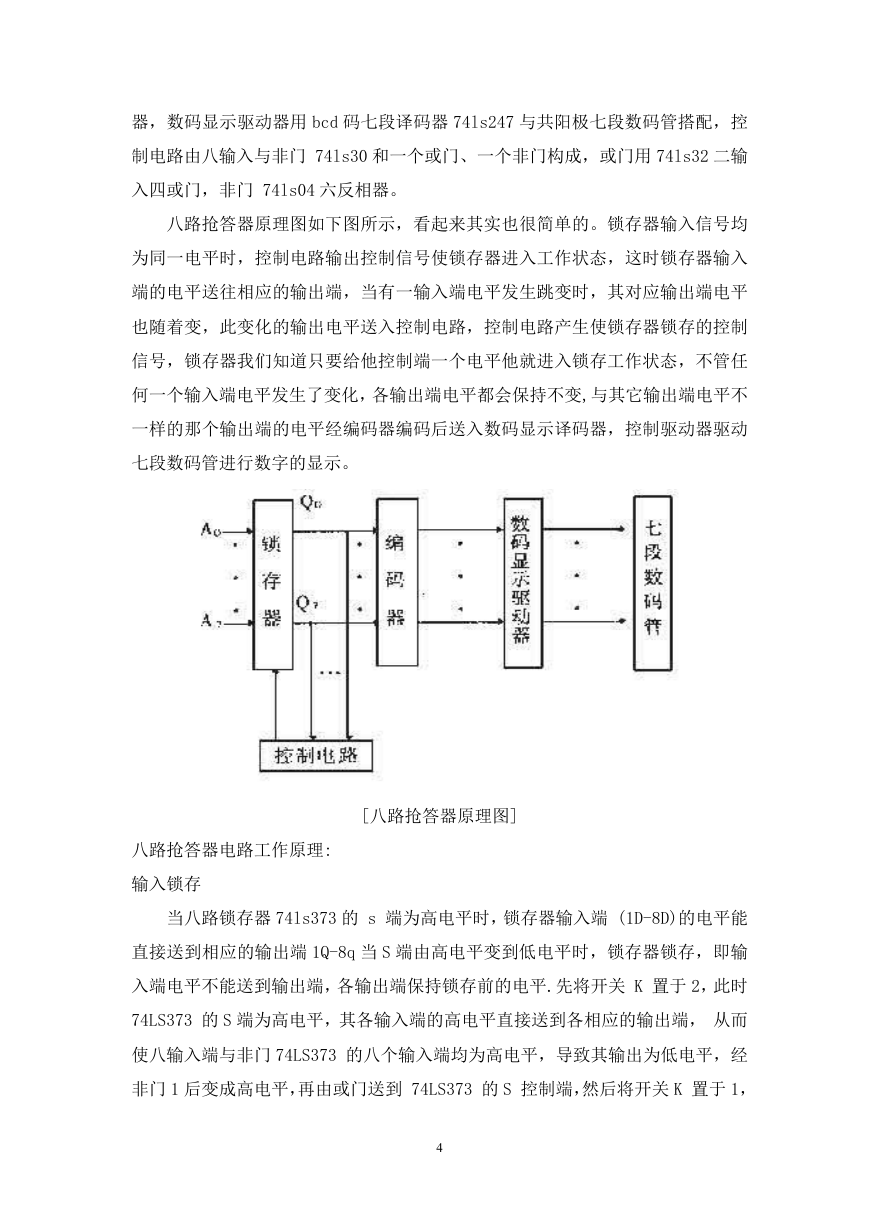

八路抢答器原理图如下图所示,看起来其实也很简单的。锁存器输入信号均

为同一电平时,控制电路输出控制信号使锁存器进入工作状态,这时锁存器输入

端的电平送往相应的输出端,当有一输入端电平发生跳变时,其对应输出端电平

也随着变,此变化的输出电平送入控制电路,控制电路产生使锁存器锁存的控制

信号,锁存器我们知道只要给他控制端一个电平他就进入锁存工作状态,不管任

何一个输入端电平发生了变化,各输出端电平都会保持不变,与其它输出端电平不

一样的那个输出端的电平经编码器编码后送入数码显示译码器,控制驱动器驱动

七段数码管进行数字的显示。

[八路抢答器原理图]

八路抢答器电路工作原理:

输入锁存

当八路锁存器 74ls373 的 s 端为高电平时,锁存器输入端 (1D-8D)的电平能

直接送到相应的输出端 1Q-8q 当 S 端由高电平变到低电平时,锁存器锁存,即输

入端电平不能送到输出端,各输出端保持锁存前的电平.先将开关 K 置于 2,此时

74LS373 的 S 端为高电平,其各输入端的高电平直接送到各相应的输出端, 从而

使八输入端与非门 74LS373 的八个输入端均为高电平,导致其输出为低电平,经

非门 1 后变成高电平,再由或门送到 74LS373 的 S 控制端,然后将开关 K 置于 1,

4

�

这时由于或门的另一输入仍为高电平,故 S 控制端仍保持高电平,当八个按钮开

关 AN0-NA7 中有一个先按下时,其对应的 D 端变为低电平,此低电平经锁存器送

到相应的 Q 输出端,这时 74LS 的八个输入端中因有一个端变低电平,所以它的输

出端变为高电平,经非门 1 和或门后,使 s 控制端由高电平变成低电平,74LS373

执行锁存功能,如果这时 还有按钮按下,锁存器对应的输出端电平也不会变.

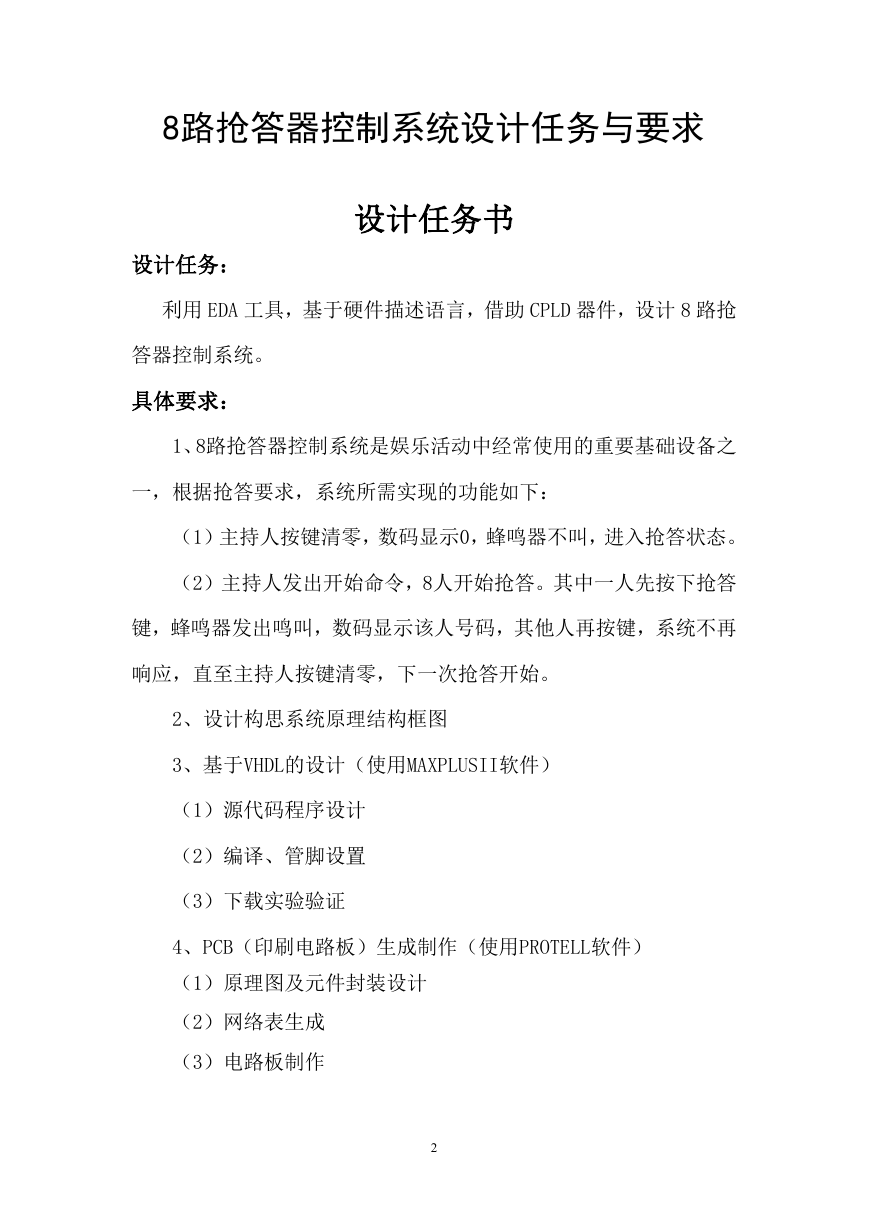

编码和译码显示

[八路抢答器电路图]

74LS74LS 为输入低电平有效和输出低电平有效,即当 I0 端为低电平而其它输

入端为高电平时,输出端 Y2,Y1,Y0 均为高电平,I1 端为低电平而其它输入端为高

电平时,Y2,Y1 端均为高电平,Y0 端为低电平,以此类推锁存在锁存器输出端的

低电平送到 74LS148,由 74LS148 进行编码,编成的二进制代码电平经非门 2 3 4

分别倒相后,送到 BCD 码七段译码驱动器 74LS247 再由 74LS247 输出端送出驱动

电平驱动共阳极七段数码管 5EF105 显示相应的数字,如 I0 端为低电平时,显示

0;I4 端为低电平时,显示 4,当八个按钮开关都不按下时,由于锁存器的各输出

端均为高电平,经 74LS30 后使 74LS247 的熄灭控制端得到低电平,因此数码管不

显示.

5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc