产品资料夹

样品与购买

技术文件

工具与软件

支持与社区

DP83848C / I / VYB / YB PHYTER™QFP单端口10/100 Mb / s以太网物理层收发器

DP83848C,DP83848I DP83848VYB,DP83848YB

SNLS266E – 2007年5月– 2015年3月修订

1 介绍

1.1 特点

• 从–40°C到105°C的多个温度范围•IEEE 802.3 ENDEC,10BASE-T收发器和

• 低功耗3.3V,0.18μmCMOS技术

• 低功耗<270 mW(典型值)

• 3.3V MAC接口

• Auto-MDIX为10/100 Mb / s

• 能量检测模式

• 25MHz时钟输出

筛选器

• IEEE 802.3 PCS,100BASE-TX收发器和滤波器

• IEEE 1149.1 JTAG

• 集成ANSI X3.263的TP-PMD物理子层,具有自适应均衡和基线漂移补偿

SNI接口(可配置)

•

RMII版本1.2接口(可配置)

•

• MII串行管理接口(MDC和MDIO)

•可编程LED支持链接,10/100 Mb / s

检测

•长达150米的无错误操作

模式,活动,双工和冲突

IEEE 802.3 MII

•

IEEE 802.3自动协商和并行

•

•用于完整PHY状态的单寄存器访问

•10/100 Mb / s数据包BIST(内置自检)检测

1.2 应用领域

• 汽车/运输•通用嵌入式应用

• 工业控制与工厂自动化

1.3 描述

需要以太网连接的应用程序数量继续增加,从而使支持以太网的设备进入更恶劣的环境。

DP83848C / I / VYB / YB旨在通过超出典型工业温度范围的扩展温度性能来应对这些新应用的挑战。DP83848C / I / VYB / YB是一款高度可靠,功能丰富,坚固耐

用的设备,在从商业温度到极端温度的多个温度范围内均符合IEEE 802.3标准。该设备非常适合恶劣环境,例如无线远程基站,汽车/运输和工业控制应用。

它提供增强的ESD保护,并提供MII或RMII接口的选择,从而在选择MPU时具有最大的灵活性。全部采用48引脚封装。

DP83848VYB在较宽的工作温度范围内扩展了PHYTER™系列设备的领导地位。TI的PHYTER收发器产品线建立在数十年的以太网专业知识基础上,可提供高性能

和灵活性,使最终用户可以轻松地量身定制满足这些应用需求的设备。

零件号

DP83848VYB / YB

DP83848I / C

(1)有关更多信息,请参见第9节,

包

HLQFP(48)

品质保证计划(48)

。

(1)

设备信息

身体尺码(NOM)

7.00毫米×7.00毫米

本数据表末尾的重要声明涉及可用性,保修,更改,在安全关键型应用中使用,知识产权问题和其他重要的免责声明。生产数据。

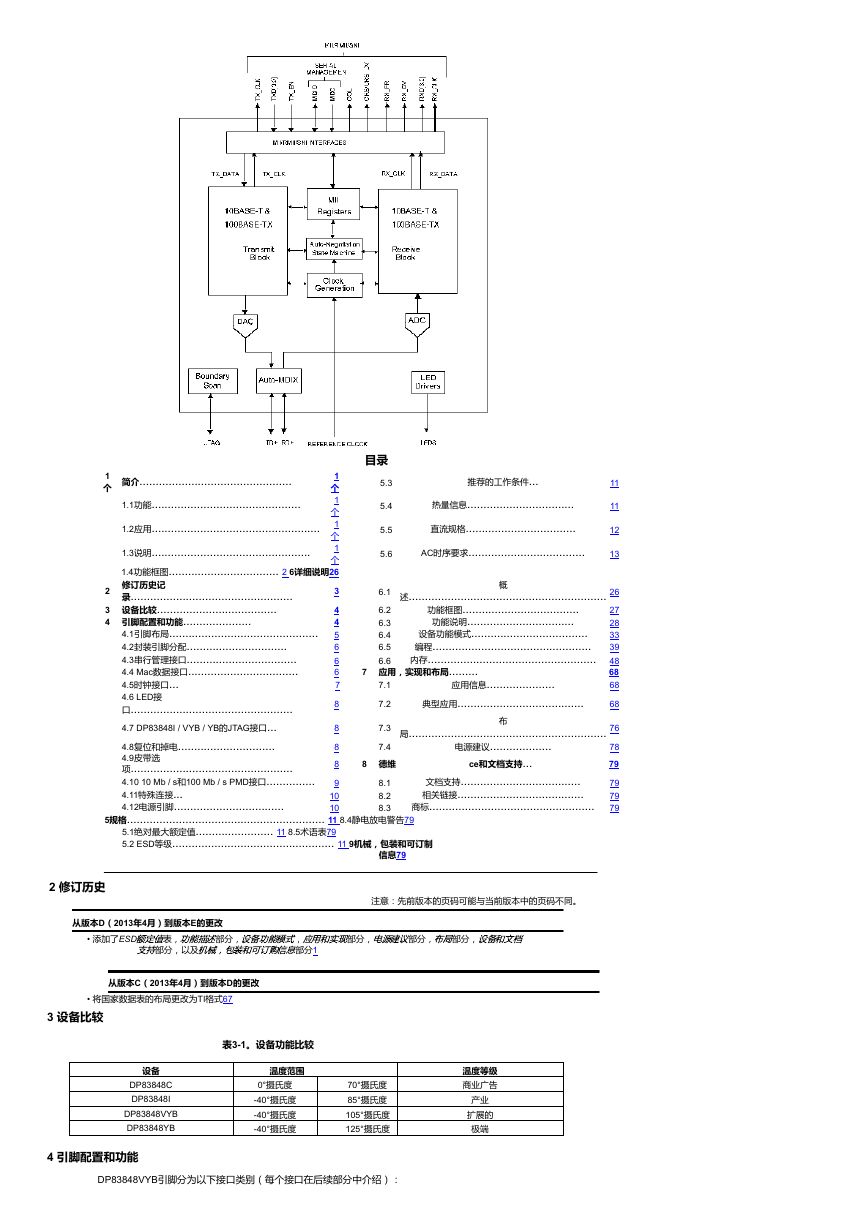

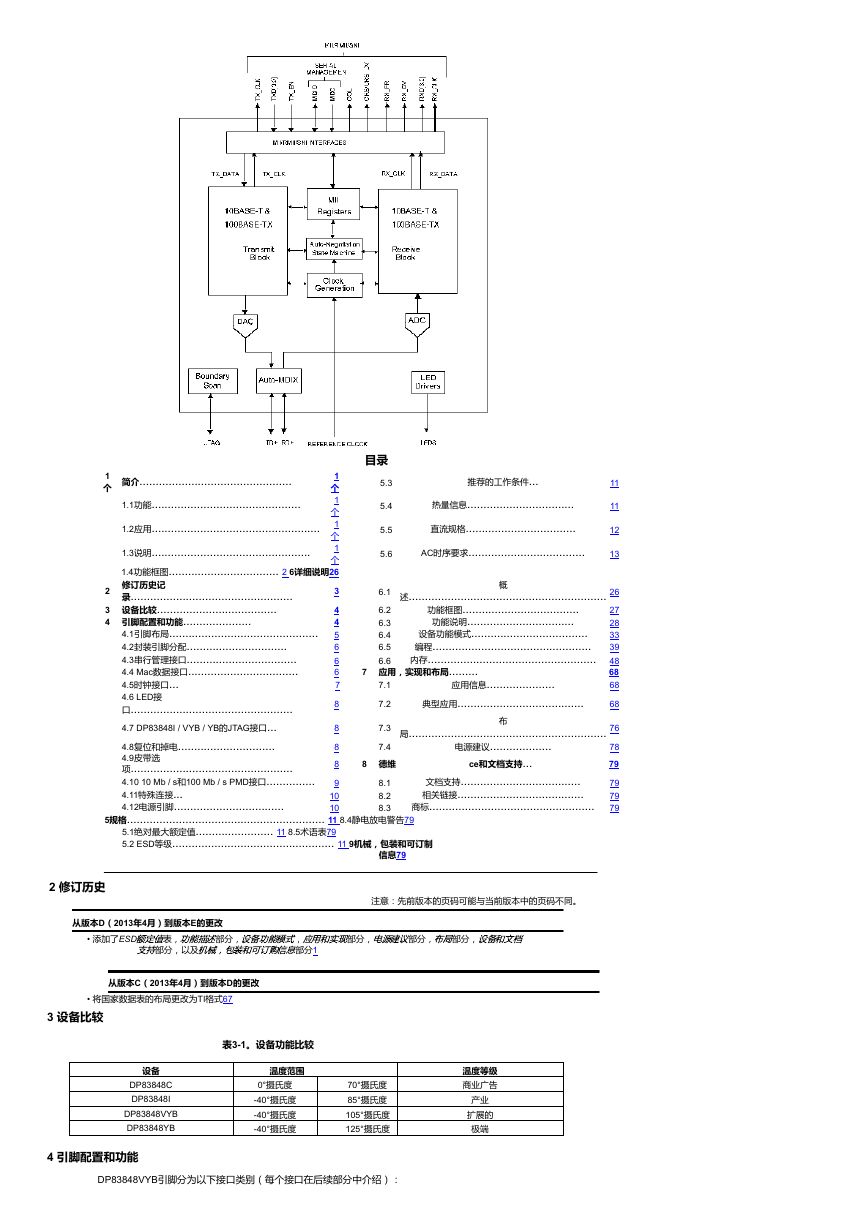

1.4 功能框图

机

械

,

包

装

和

订

购

信

息

�

目录

5.3

5.4

5.5

5.6

6.1

1

个

1

简介...............................................

个

1

1.1功能..............................................

个

1

1.2应用....................................................

个

1

1.3说明.................................................

个

1.4功能框图.................................. 2 6详细说明26

修订历史记

3

录..................................................

4

4

5

6

6

6

7

2

3 设备比较.....................................

4 引脚配置和功能.....................

4.1引脚布局..............................................

4.2封装引脚分配...............................

4.3串行管理接口..................................

4.4 Mac数据接口..................................

4.5时钟接口...

4.6 LED接

口..................................................

4.7 DP83848I / VYB / YB的JTAG接口...

4.8复位和掉电..............................

4.9皮带选

项..................................................

4.10 10 Mb / s和100 Mb / s PMD接口...............

9

4.11特殊连接...

10

4.12电源引脚..................................

10

5.1绝对最大额定值........................ 11 8.5术语表79

5.2 ESD等级.................................................. 11 9机械,包装和可订制

5规格............................................................. 11 8.4静电放电警告79

7.4

8 德维

6.2

6.3

6.4

6.5

6.6

8.1

8.2

8.3

8

8

8

8

7.1

7.2

7.3

信息79

功能框图....................................

功能说明.................................

述............................................................. 26

27

28

33

39

48

68

68

设备功能模式....................................

编程.................................................

内存....................................................

应用信息.....................

典型应用.......................................

7 应用,实现和布局.........

概

布

推荐的工作条件...

热量信息.................................

直流规格..................................

AC时序要求....................................

11

11

12

13

局............................................................. 76

78

79

电源建议...................

ce和文档支持...

文档支持.....................................

相关链接.......................................

商标...................................................

68

79

79

79

2 修订历史

从版本D(2013年4月)到版本E的更改

• 添加了ESD

表,

部分,以及

部分,

,

部分1

部分,

部分,

部分,

注意:先前版本的页码可能与当前版本中的页码不同。

从版本C(2013年4月)到版本D的更改

• 将国家数据表的布局更改为TI格式67

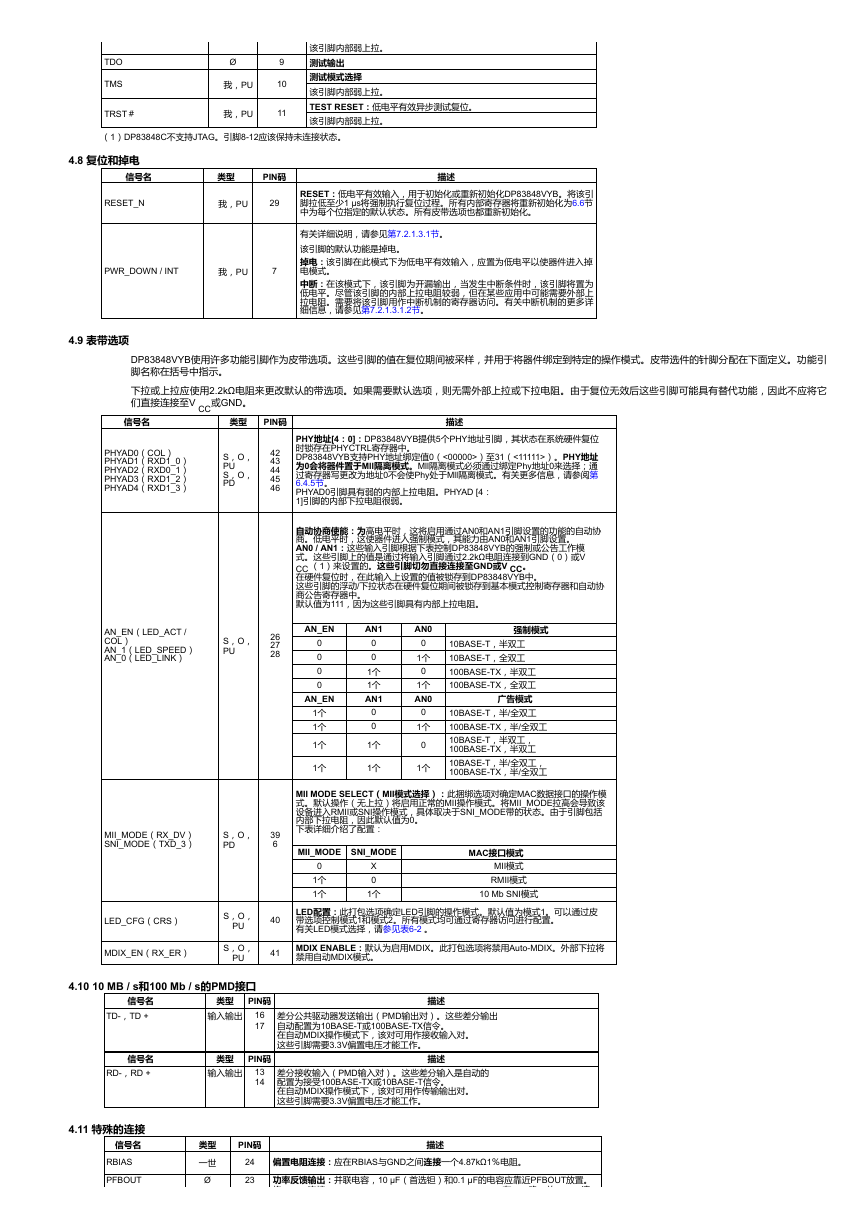

3 设备比较

表3-1。设备功能比较

设备

DP83848C

DP83848I

DP83848VYB

DP83848YB

温度范围

0°摄氏度

-40°摄氏度

-40°摄氏度

-40°摄氏度

70°摄氏度

85°摄氏度

105°摄氏度

125°摄氏度

温度等级

商业广告

产业

扩展的

极端

4 引脚配置和功能

DP83848VYB引脚分为以下接口类别(每个接口在后续部分中介绍):

额

定

值

功

能

描

述

设

备

功

能

模

式

应

用

和

实

现

电

源

建

议

布

局

设

备

和

文

档

支

持

机

械

,

包

装

和

可

订

购

信

息

�

• 串行管理界面

• MAC数据接口

• 时钟接口

• LED接口

• JTAG接口

• 重置并掉电

• 表带选项

• 10/100 Mb / s PMD接口

• 特殊连接销

• 电源和接地引脚

捆扎针选项。有关皮带的定义,请参见第4.9节。

注意

无论特定用途如何,所有DP83848VYB信号引脚均为I / O单元。以下定义定义了每个引脚的I / O单元的功能。

类型:I输入

类型:O 输出类型:I / O输入/输出类型:OD开漏

类型:PD,PU内部下拉/上拉

类型:S 捆绑引脚(所有捆绑带引脚的内部上拉或下拉电阻都很弱。如果要更改默认捆绑带值,则应使用外部2.2kΩ电阻。有关详细信息,请参见4.9节。)

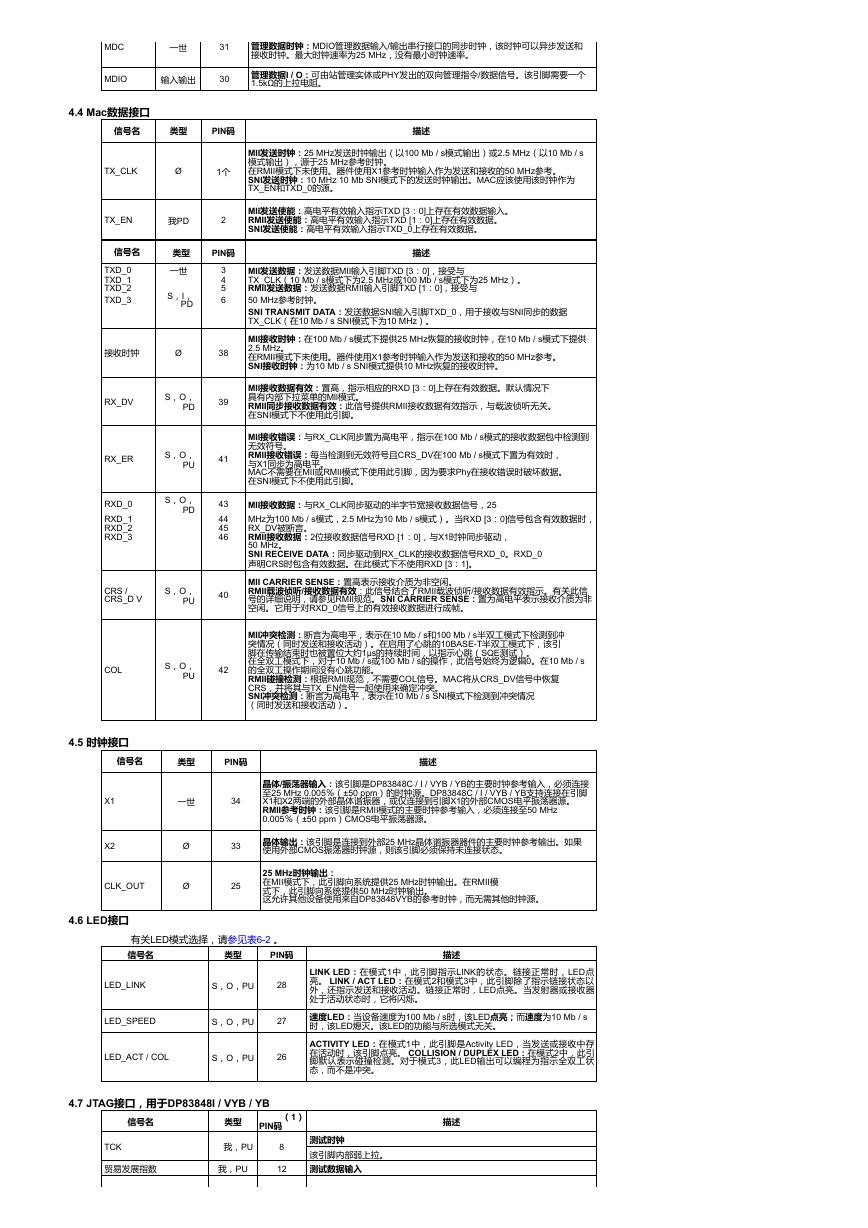

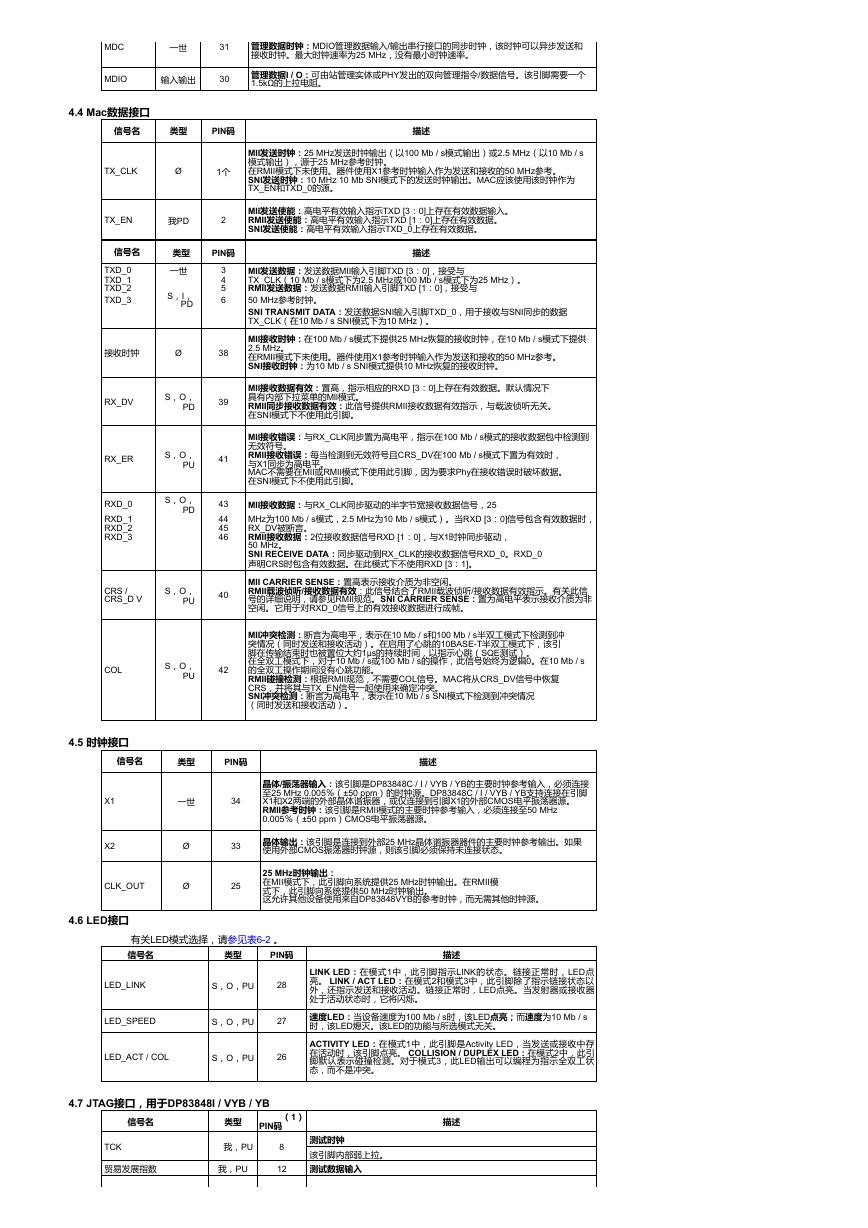

4.1 引脚布局

PTB封装48引脚HLQFP

顶视图

4.2 封装引脚分配

VBH48A PIN#

密码名称

VBH48A PIN#

密码名称

1个

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18岁

19

20

21

22

23

24

25

TX_CLK

TX_EN

TXD_0

TXD_1

TXD_2

TXD_3 / SNI_MODE

PWR_DOWN / INT

TCK

TDO

TMS

TRST#

贸易发展指数

RD-

RD +

地线

TD-

TD +

PFBIN1

地线

已预留

已预留

AVDD33

PFBOUT

RBIAS

CLK_OUT

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

LED_ACT / COL / AN_EN

LED_SPEED / AN1

LED_LINK / AN0

RESET_N

MDIO

MDC

IOVDD33

X2

X1

IOGND

地线

PFBIN2

接收时钟

RX_DV / MII_MODE

CRS / CRS_DV / LED_CFG

RX_ER / MDIX_EN

COL / PHYAD0

RXD_0 / PHYAD1

RXD_1 / PHYAD2

RXD_2 / PHYAD3

RXD_3 / PHYAD4

IOGND

IOVDD33

地垫

4.3 串行管理接口

信号名

类型

PIN码

管 数

钟

管

描述

行接

钟 该 钟

发

�

MDC

一世

MDIO

输入输出

31

30

管理数据时钟:MDIO管理数据输入/输出串行接口的同步时钟,该时钟可以异步发送和

接收时钟。最大时钟速率为25 MHz,没有最小时钟速率。

管理数据I / O:可由站管理实体或PHY发出的双向管理指令/数据信号。该引脚需要一个

1.5kΩ的上拉电阻。

4.4 Mac数据接口

信号名

类型

PIN码

描述

TX_CLK

Ø

1个

MII发送时钟:25 MHz发送时钟输出(以100 Mb / s模式输出)或2.5 MHz(以10 Mb / s

模式输出),源于25 MHz参考时钟。

在RMII模式下未使用。器件使用X1参考时钟输入作为发送和接收的50 MHz参考。

SNI发送时钟:10 MHz 10 Mb SNI模式下的发送时钟输出。MAC应该使用该时钟作为

TX_EN和TXD_0的源。

TX_EN

我PD

2

MII发送使能:高电平有效输入指示TXD [3:0]上存在有效数据输入。

RMII发送使能:高电平有效输入指示TXD [1:0]上存在有效数据。

SNI发送使能:高电平有效输入指示TXD_0上存在有效数据。

信号名

TXD_0

TXD_1

TXD_2

TXD_3

类型

一世

S,I,

PD

接收时钟

Ø

RX_DV

S,O,

PD

S,O,

PU

S,O,

PD

RX_ER

RXD_0

RXD_1

RXD_2

RXD_3

CRS /

CRS_D V

S,O,

PU

COL

S,O,

PU

PIN码

描述

3

4

5

6

38

39

41

43

44

45

46

40

42

MII发送数据:发送数据MII输入引脚TXD [3:0],接受与

TX_CLK(10 Mb / s模式下为2.5 MHz或100 Mb / s模式下为25 MHz)。

RMII发送数据:发送数据RMII输入引脚TXD [1:0],接受与

50 MHz参考时钟。

SNI TRANSMIT DATA:发送数据SNI输入引脚TXD_0,用于接收与SNI同步的数据

TX_CLK(在10 Mb / s SNI模式下为10 MHz)。

MII接收时钟:在100 Mb / s模式下提供25 MHz恢复的接收时钟,在10 Mb / s模式下提供

2.5 MHz。

在RMII模式下未使用。器件使用X1参考时钟输入作为发送和接收的50 MHz参考。

SNI接收时钟:为10 Mb / s SNI模式提供10 MHz恢复的接收时钟。

MII接收数据有效:置高,指示相应的RXD [3:0]上存在有效数据。默认情况下

具有内部下拉菜单的Mll模式。

RMII同步接收数据有效:此信号提供RMII接收数据有效指示,与载波侦听无关。

在SNI模式下不使用此引脚。

MII接收错误:与RX_CLK同步置为高电平,指示在100 Mb / s模式的接收数据包中检测到

无效符号。

RMII接收错误:每当检测到无效符号且CRS_DV在100 Mb / s模式下置为有效时,

与X1同步为高电平。

MAC不需要在MII或RMII模式下使用此引脚,因为要求Phy在接收错误时破坏数据。

在SNI模式下不使用此引脚。

MII接收数据:与RX_CLK同步驱动的半字节宽接收数据信号,25

MHz为100 Mb / s模式,2.5 MHz为10 Mb / s模式)。当RXD [3:0]信号包含有效数据时,

RX_DV被断言。

RMII接收数据:2位接收数据信号RXD [1:0],与X1时钟同步驱动,

50 MHz。

SNI RECEIVE DATA:同步驱动到RX_CLK的接收数据信号RXD_0。RXD_0

声明CRS时包含有效数据。在此模式下不使用RXD [3:1]。

MII CARRIER SENSE:置高表示接收介质为非空闲。

RMII载波侦听/接收数据有效:此信号结合了RMII载波侦听/接收数据有效指示。有关此信

号的详细说明,请参见RMII规范。SNI CARRIER SENSE:置为高电平表示接收介质为非

空闲。它用于对RXD_0信号上的有效接收数据进行成帧。

MII冲突检测:断言为高电平,表示在10 Mb / s和100 Mb / s半双工模式下检测到冲

突情况(同时发送和接收活动)。在启用了心跳的10BASE-T半双工模式下,该引

脚在传输结束时也被置位大约1µs的持续时间,以指示心跳(SQE测试)。

在全双工模式下,对于10 Mb / s或100 Mb / s的操作,此信号始终为逻辑0。在10 Mb / s

的全双工操作期间没有心跳功能。

RMII碰撞检测:根据RMII规范,不需要COL信号。MAC将从CRS_DV信号中恢复

CRS,并将其与TX_EN信号一起使用来确定冲突。

SNI冲突检测:断言为高电平,表示在10 Mb / s SNI模式下检测到冲突情况

(同时发送和接收活动)。

4.5 时钟接口

信号名

类型

PIN码

描述

一世

Ø

Ø

34

33

25

晶体/振荡器输入:该引脚是DP83848C / I / VYB / YB的主要时钟参考输入,必须连接

至25 MHz 0.005%(±50 ppm)的时钟源。DP83848C / I / VYB / YB支持连接在引脚

X1和X2两端的外部晶体谐振器,或仅连接到引脚X1的外部CMOS电平振荡器源。

RMII参考时钟:该引脚是RMII模式的主要时钟参考输入,必须连接至50 MHz

0.005%(±50 ppm)CMOS电平振荡器源。

晶体输出:该引脚是连接到外部25 MHz晶体谐振器器件的主要时钟参考输出。如果

使用外部CMOS振荡器时钟源,则该引脚必须保持未连接状态。

25 MHz时钟输出:

在MII模式下,此引脚向系统提供25 MHz时钟输出。在RMII模

式下,此引脚向系统提供50 MHz时钟输出。

这允许其他设备使用来自DP83848VYB的参考时钟,而无需其他时钟源。

X1

X2

CLK_OUT

4.6 LED接口

有关LED模式选择,请参见表6-2 。

信号名

类型

PIN码

描述

LED_LINK

S,O,PU

LED_SPEED

S,O,PU

LED_ACT / COL

S,O,PU

28

27

26

LINK LED:在模式1中,此引脚指示LINK的状态。链接正常时,LED点

亮。 LINK / ACT LED:在模式2和模式3中,此引脚除了指示链接状态以

外,还指示发送和接收活动。链接正常时,LED点亮。当发射器或接收器

处于活动状态时,它将闪烁。

速度LED:当设备速度为100 Mb / s时,该LED点亮;而速度为10 Mb / s

时,该LED熄灭。该LED的功能与所选模式无关。

ACTIVITY LED:在模式1中,此引脚是Activity LED,当发送或接收中存

在活动时,该引脚点亮。 COLLISION / DUPLEX LED:在模式2中,此引

脚默认表示碰撞检测。对于模式3,此LED输出可以编程为指示全双工状

态,而不是冲突。

4.7 JTAG接口,用于DP83848I / VYB / YB

信号名

TCK

贸易发展指数

类型 PIN码

(1)

我,PU

我,PU

8

12

测试时钟

该引脚内部弱上拉。

测试数据输入

描述

�

TDO

TMS

TRST#

Ø

我,PU

我,PU

9

10

11

该引脚内部弱上拉。

测试输出

测试模式选择

该引脚内部弱上拉。

TEST RESET:低电平有效异步测试复位。

该引脚内部弱上拉。

(1)DP83848C不支持JTAG。引脚8-12应该保持未连接状态。

4.8 复位和掉电

信号名

类型

PIN码

描述

RESET_N

我,PU

29

PWR_DOWN / INT

我,PU

7

RESET:低电平有效输入,用于初始化或重新初始化DP83848VYB。将该引

脚拉低至少1 µs将强制执行复位过程。所有内部寄存器将重新初始化为6.6节

中为每个位指定的默认状态。所有皮带选项也都重新初始化。

有关详细说明,请参见第7.2.1.3.1节。

该引脚的默认功能是掉电。

掉电:该引脚在此模式下为低电平有效输入,应置为低电平以使器件进入掉

电模式。

中断:在该模式下,该引脚为开漏输出,当发生中断条件时,该引脚将置为

低电平。尽管该引脚的内部上拉电阻较弱,但在某些应用中可能需要外部上

拉电阻。需要将该引脚用作中断机制的寄存器访问。有关中断机制的更多详

细信息,请参见第7.2.1.3.1.2节。

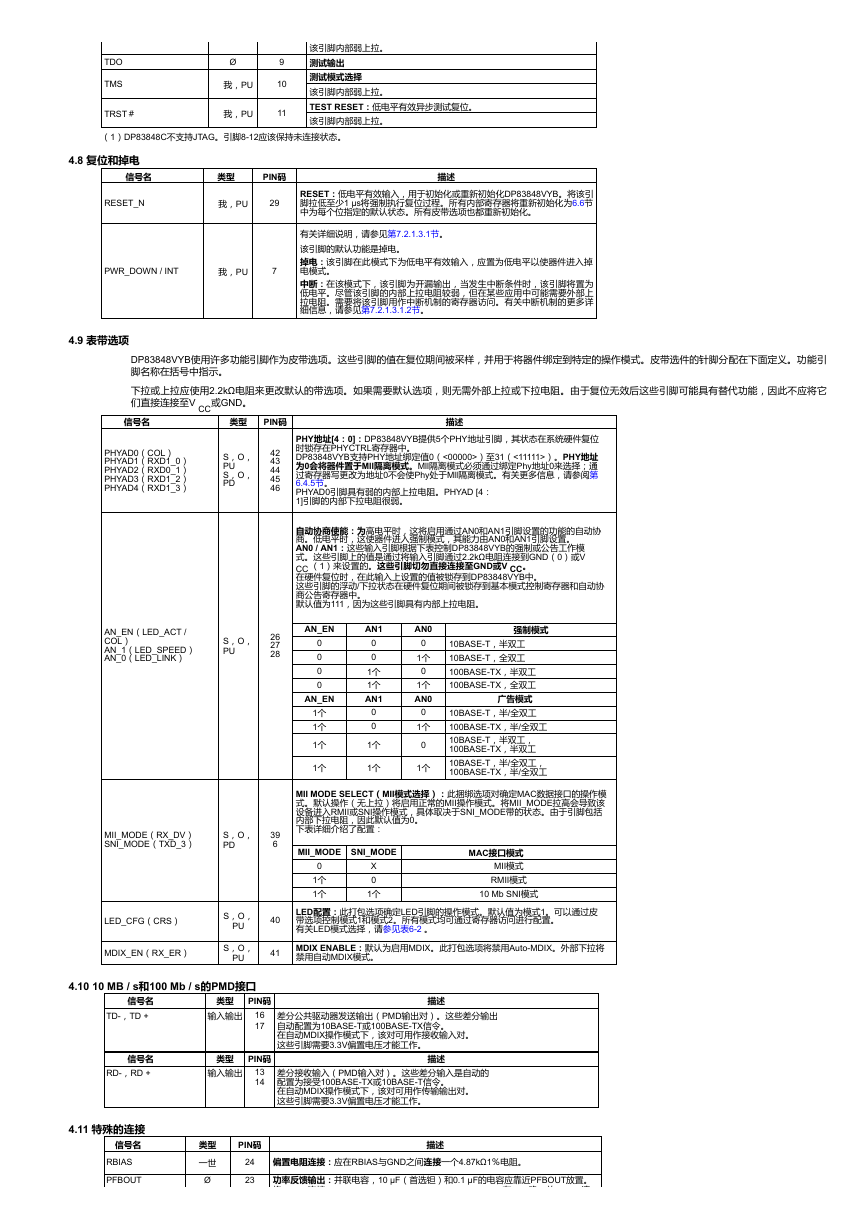

4.9 表带选项

DP83848VYB使用许多功能引脚作为皮带选项。这些引脚的值在复位期间被采样,并用于将器件绑定到特定的操作模式。皮带选件的针脚分配在下面定义。功能引

脚名称在括号中指示。

下拉或上拉应使用2.2kΩ电阻来更改默认的带选项。如果需要默认选项,则无需外部上拉或下拉电阻。由于复位无效后这些引脚可能具有替代功能,因此不应将它

们直接连接至V

或GND。

CC

信号名

类型 PIN码

描述

PHYAD0(COL)

PHYAD1(RXD1_0)

PHYAD2(RXD0_1)

PHYAD3(RXD1_2)

PHYAD4(RXD1_3)

S,O,

PU

S,O,

PD

42

43

44

45

46

PHY地址[4:0]:DP83848VYB提供5个PHY地址引脚,其状态在系统硬件复位

时锁存在PHYCTRL寄存器中。

DP83848VYB支持PHY地址绑定值0(<00000>)至31(<11111>)。PHY地址

为0会将器件置于Mll隔离模式。Mll隔离模式必须通过绑定Phy地址0来选择;通

过寄存器写更改为地址0不会使Phy处于Mll隔离模式。有关更多信息,请参阅第

6.4.5节。

PHYAD0引脚具有弱的内部上拉电阻。PHYAD [4:

1]引脚的内部下拉电阻很弱。

AN_EN(LED_ACT /

COL)

AN_1(LED_SPEED)

AN_0(LED_LINK)

S,O,

PU

26

27

28

MII_MODE(RX_DV)

SNI_MODE(TXD_3)

S,O,

PD

39

6

自动协商使能:为高电平时,这将启用通过AN0和AN1引脚设置的功能的自动协

商。低电平时,这使器件进入强制模式,其能力由AN0和AN1引脚设置。

AN0 / AN1:这些输入引脚根据下表控制DP83848VYB的强制或公告工作模

式。这些引脚上的值是通过将输入引脚通过2.2kΩ电阻连接到GND(0)或V

CC (1)来设置的。这些引脚切勿直接连接至GND或V CC。

在硬件复位时,在此输入上设置的值被锁存到DP83848VYB中。

这些引脚的浮动/下拉状态在硬件复位期间被锁存到基本模式控制寄存器和自动协

商公告寄存器中。

默认值为111,因为这些引脚具有内部上拉电阻。

AN_EN

0

0

0

0

AN_EN

1个

1个

1个

1个

AN1

0

0

1个

1个

AN1

0

0

1个

1个

AN0

0

1个

0

1个

AN0

0

1个

0

1个

强制模式

10BASE-T,半双工

10BASE-T,全双工

100BASE-TX,半双工

100BASE-TX,全双工

广告模式

10BASE-T,半/全双工

100BASE-TX,半/全双工

10BASE-T,半双工,

100BASE-TX,半双工

10BASE-T,半/全双工,

100BASE-TX,半/全双工

MII MODE SELECT(MII模式选择):此捆绑选项对确定MAC数据接口的操作模

式。默认操作(无上拉)将启用正常的MII操作模式。将MII_MODE拉高会导致该

设备进入RMII或SNI操作模式,具体取决于SNI_MODE带的状态。由于引脚包括

内部下拉电阻,因此默认值为0。

下表详细介绍了配置:

MII_MODE SNI_MODE

0

1个

1个

X

0

1个

MAC接口模式

MII模式

RMII模式

10 Mb SNI模式

LED_CFG(CRS)

MDIX_EN(RX_ER)

S,O,

PU

S,O,

PU

40

41

LED配置:此打包选项确定LED引脚的操作模式。默认值为模式1。可以通过皮

带选项控制模式1和模式2。所有模式均可通过寄存器访问进行配置。

有关LED模式选择,请参见表6-2 。

MDIX ENABLE:默认为启用MDIX。此打包选项将禁用Auto-MDIX。外部下拉将

禁用自动MDIX模式。

4.10 10 MB / s和100 Mb / s的PMD接口

信号名

TD-,TD +

信号名

RD-,RD +

类型 PIN码

描述

输入输出 16 差分公共驱动器发送输出(PMD输出对)。这些差分输出

17 自动配置为10BASE-T或100BASE-TX信令。

在自动MDIX操作模式下,该对可用作接收输入对。

这些引脚需要3.3V偏置电压才能工作。

类型 PIN码

描述

输入输出 13 差分接收输入(PMD输入对)。这些差分输入是自动的

14 配置为接受100BASE-TX或10BASE-T信令。

在自动MDIX操作模式下,该对可用作传输输出对。

这些引脚需要3.3V偏置电压才能工作。

4.11 特殊的连接

信号名

RBIAS

PFBOUT

类型

一世

Ø

PIN码

24

23

描述

偏置电阻连接:应在RBIAS与GND之间连接一个4.87kΩ1%电阻。

功率反馈输出:并联电容,10 µF(首选钽)和0.1 µF的电容应靠近PFBOUT放置。

将

请

确 放

连接

有

�

PFBIN1

PFBIN2

一世

18岁

37

将此引脚连接到PFBIN1(引脚18)和PFBIN2(引脚37)。有关正确的放置销,请

参见第7.2.1.3节。

电源反馈输入:这些引脚由PFBOUT引脚供电。每个引脚附近应连接一个0.1 µF的小

电容。

(1)

已预留

(1)注:除通过PFBOUT供电外,请勿为这些引脚供电。

输入输出 20、21 保留:这些引脚必须通过2.2kΩ电阻上拉至AVDD33电源。

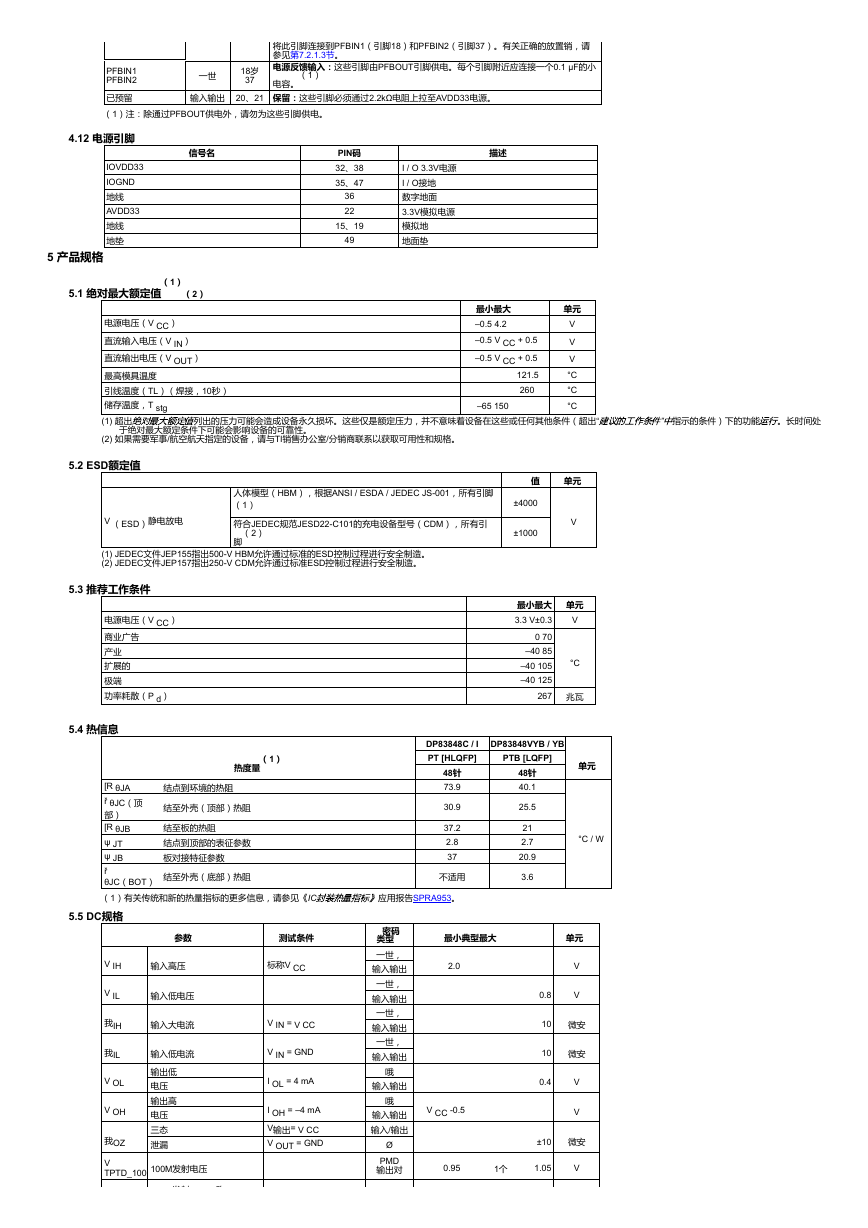

4.12 电源引脚

信号名

IOVDD33

IOGND

地线

AVDD33

地线

地垫

5 产品规格

描述

PIN码

32、38

35、47

36

22

15、19

49

I / O 3.3V电源

I / O接地

数字地面

3.3V模拟电源

模拟地

地面垫

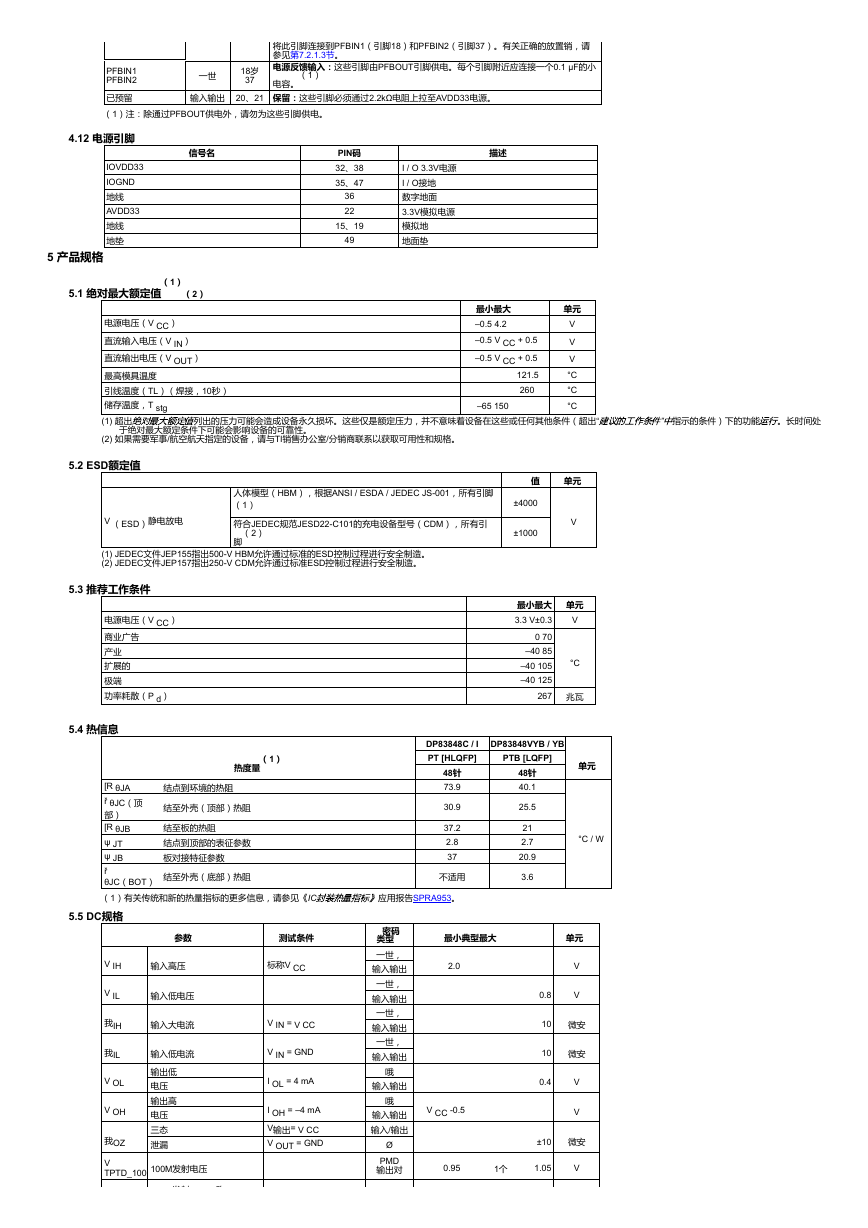

5.1 绝对最大额定值

(2)

(1)

电源电压(V CC)

直流输入电压(V IN)

直流输出电压(V OUT)

最高模具温度

引线温度(TL)(焊接,10秒)

储存温度,T stg

(1) 超出

(2) 如果需要军事/航空航天指定的设备,请与TI销售办公室/分销商联系以获取可用性和规格。

于绝对最大额定条件下可能会影响设备的可靠性。

最小最大

–0.5 4.2

–0.5 V CC + 0.5

–0.5 V CC + 0.5

121.5

260

–65 150

单元

V

V

V

°C

°C

°C

列出的压力可能会造成设备永久损坏。这些仅是额定压力,并不意味着设备在这些或任何其他条件(超出“

”

指示的条件)下的功能

。长时间处

5.2 ESD额定值

V (ESD)静电放电

人体模型(HBM),根据ANSI / ESDA / JEDEC JS-001,所有引脚

(1)

符合JEDEC规范JESD22-C101的充电设备型号(CDM),所有引

脚

(2)

(1) JEDEC文件JEP 155指出500-V HBM允许通过标准的ESD控制过程进行安全制造。

(2) JEDEC文件JEP 157指出250-V CDM允许通过标准ESD控制过程进行安全制造。

值

单元

±4000

±1000

V

最小最大 单元

3.3 V±0.3

V

0 70

–40 85

–40 105

–40 125

°C

267 兆瓦

DP83848C / I DP83848VYB / YB

PT [HLQFP]

PTB [LQFP]

48针

73.9

30.9

37.2

2.8

37

不适用

48针

40.1

25.5

21

2.7

20.9

3.6

单元

°C / W

应用报告SPRA953。

密码

类型

一世,

输入输出

一世,

输入输出

一世,

输入输出

一世,

输入输出

哦

输入输出

哦

输入输出

输入/输出

Ø

PMD

输出对

最小典型最大

2.0

V CC -0.5

单元

V

V

0.8

10 微安

10 微安

0.4

V

V

±10 微安

0.95

1个

1.05

V

5.3 推荐工作条件

电源电压(V CC)

商业广告

产业

扩展的

极端

功率耗散(P d)

5.4 热信息

(1)

热度量

结点到环境的热阻

结至外壳(顶部)热阻

[R θJA

ř θJC(顶

部)

[R θJB

ψ JT

ψ JB

ř

θJC(BOT) 结至外壳(底部)热阻

(1)有关传统和新的热量指标的更多信息,请参见《IC

结至板的热阻

结点到顶部的表征参数

板对接特征参数

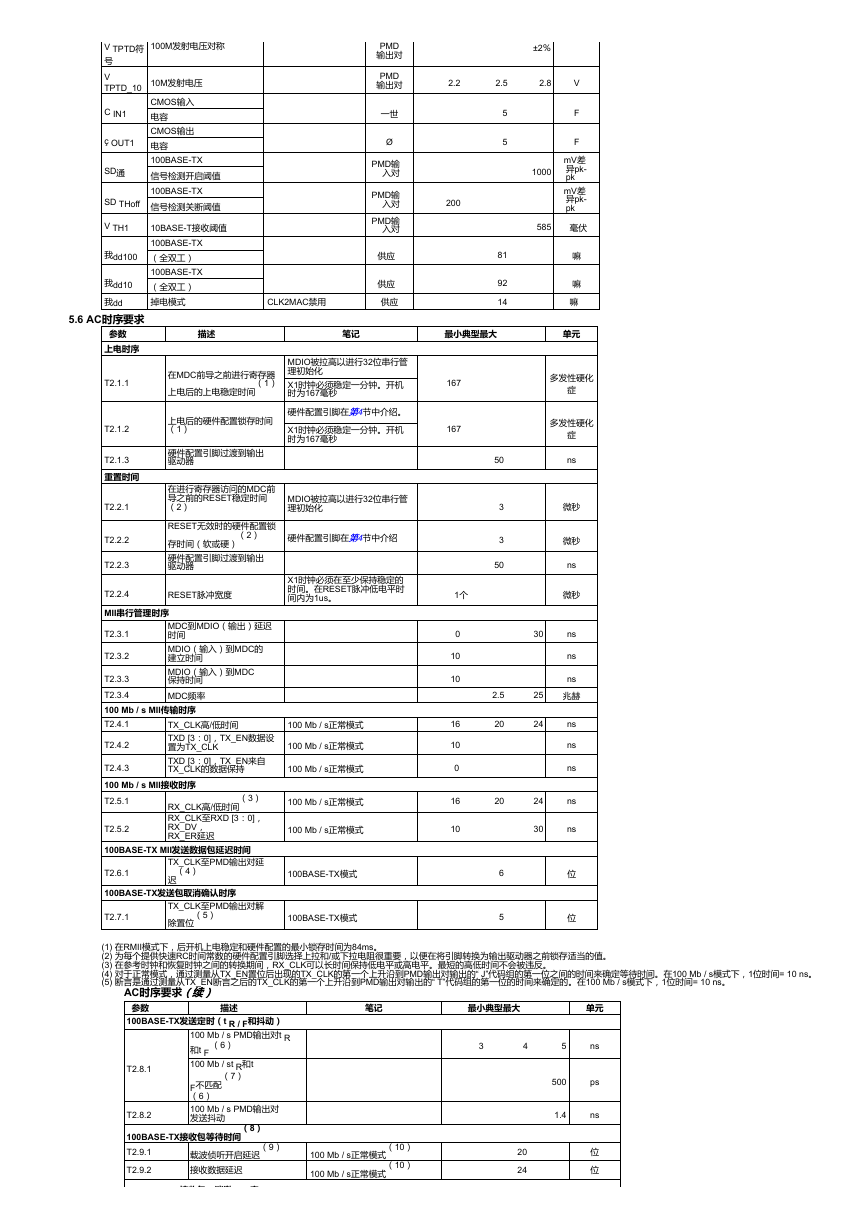

5.5 DC规格

参数

输入高压

输入低电压

输入大电流

输入低电流

输出低

电压

输出高

电压

三态

泄漏

V IH

V IL

我IH

我IL

V OL

V OH

我OZ

V

TPTD_100 100M发射电压

发射

称

测试条件

标称V CC

V IN = V CC

V IN = GND

I OL = 4 mA

I OH = –4 mA

V输出= V CC

V OUT = GND

绝

对

最

大

额

定

值

建

议

的

工

作

条

件

中

运

行

封

装

热

量

指

标

》

�

100M发射电压对称

V TPTD符

号

V

TPTD_10 10M发射电压

C IN1

ç OUT1

SD通

SD THoff

V TH1

我dd100

我dd10

我dd

CMOS输入

电容

CMOS输出

电容

100BASE-TX

信号检测开启阈值

100BASE-TX

信号检测关断阈值

10BASE-T接收阈值

100BASE-TX

(全双工)

100BASE-TX

(全双工)

掉电模式

5.6 AC时序要求

PMD

输出对

PMD

输出对

一世

Ø

PMD输

入对

PMD输

入对

PMD输

入对

供应

供应

供应

CLK2MAC禁用

±2%

2.2

2.5

2.8

V

F

F

mV差

异pk-

pk

mV差

异pk-

pk

1000

585

毫伏

嘛

嘛

嘛

200

5

5

81

92

14

描述

笔记

最小典型最大

单元

多发性硬化

症

多发性硬化

症

ns

微秒

微秒

ns

微秒

ns

ns

ns

兆赫

ns

ns

ns

ns

ns

位

位

30

25

24

24

30

50

3

3

50

2.5

20

20

6

5

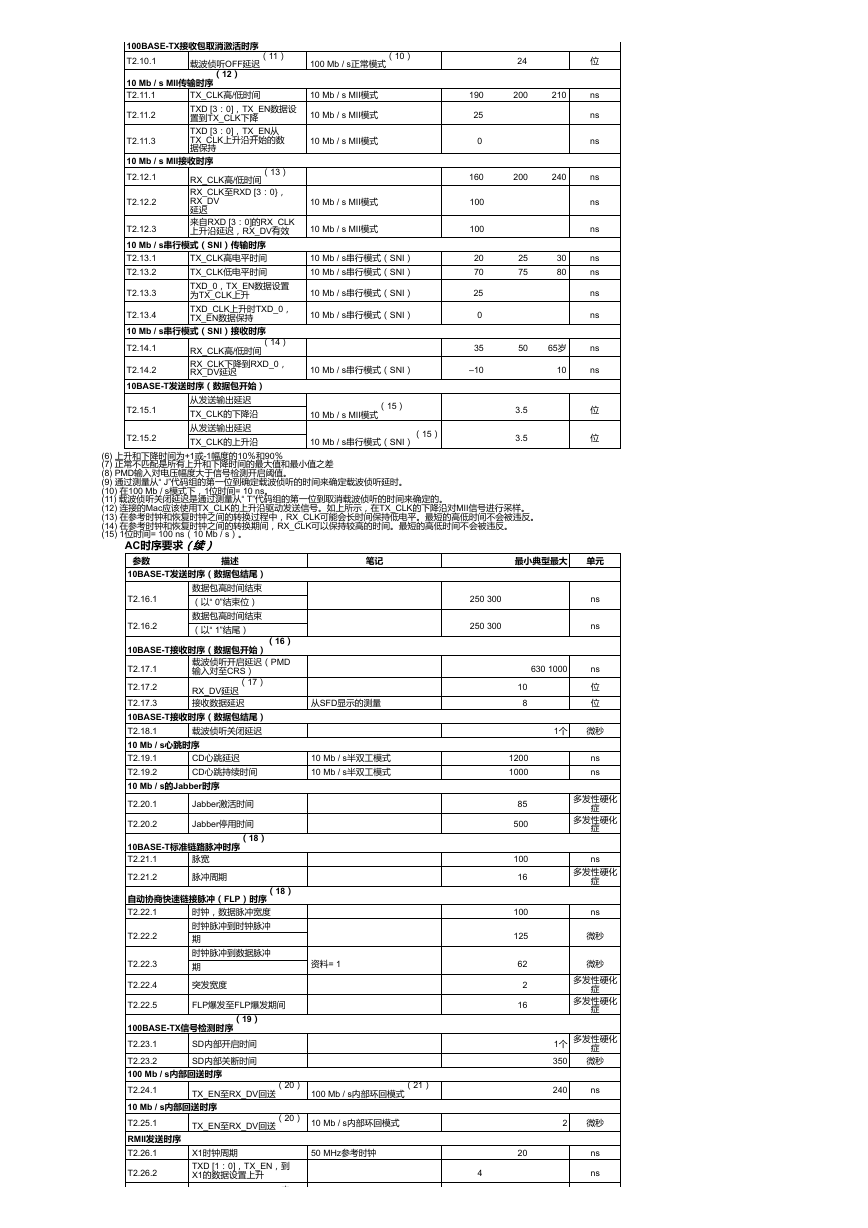

参数

上电时序

T2.1.1

T2.1.2

T2.1.3

重置时间

T2.2.1

T2.2.2

T2.2.3

T2.2.4

T2.3.1

T2.3.2

在MDC前导之前进行寄存器

(1)

上电后的上电稳定时间

上电后的硬件配置锁存时间

(1)

硬件配置引脚过渡到输出

驱动器

在进行寄存器访问的MDC前

导之前的RESET稳定时间

(2)

RESET无效时的硬件配置锁

存时间(软或硬)

硬件配置引脚过渡到输出

驱动器

(2)

RESET脉冲宽度

MDIO被拉高以进行32位串行管

理初始化

X1时钟必须稳定一分钟。开机

时为167毫秒

硬件配置引脚在

4节中介绍。

X1时钟必须稳定一分钟。开机

时为167毫秒

167

167

MDIO被拉高以进行32位串行管

理初始化

硬件配置引脚在

4节中介绍

X1时钟必须在至少保持稳定的

时间。在RESET脉冲低电平时

间内为1us。

1个

MII串行管理时序

MDC到MDIO(输出)延迟

时间

MDIO(输入)到MDC的

建立时间

MDIO(输入)到MDC

保持时间

MDC频率

TX_CLK高/低时间

TXD [3:0],TX_EN数据设

置为TX_CLK

TXD [3:0],TX_EN来自

TX_CLK的数据保持

(3)

RX_CLK高/低时间

RX_CLK至RXD [3:0],

RX_DV,

RX_ER延迟

T2.3.3

T2.3.4

100 Mb / s MII传输时序

T2.4.1

T2.4.2

T2.4.3

100 Mb / s MII接收时序

T2.5.1

T2.5.2

100BASE-TX MII发送数据包延迟时间

T2.6.1

TX_CLK至PMD输出对延

迟

(4)

100BASE-TX发送包取消确认时序

T2.7.1

TX_CLK至PMD输出对解

除置位

(5)

0

10

10

16

10

0

16

10

100 Mb / s正常模式

100 Mb / s正常模式

100 Mb / s正常模式

100 Mb / s正常模式

100 Mb / s正常模式

100BASE-TX模式

100BASE-TX模式

(1) 在RMII模式下,后开机上电稳定和硬件配置的最小锁存时间为84ms。

(2) 为每个提供快速RC时间常数的硬件配置引脚选择上拉和/或下拉电阻很重要,以便在将引脚转换为输出驱动器之前锁存适当的值。

(3) 在参考时钟和恢复时钟之间的转换期间,RX_CLK可以长时间保持低电平或高电平。最短的高低时间不会被违反。

(4) 对于正常模式,通过测量从TX_EN置位后出现的TX_CLK的第一个上升沿到PMD输出对输出的“ J”代码组的第一位之间的时间来确定等待时间。在100 Mb / s模式下,1位时间= 10 ns。

(5) 断言是通过测量从TX_EN断言之后的TX_CLK的第一个上升沿到PMD输出对输出的“ T”代码组的第一位的时间来确定的。在100 Mb / s模式下,1位时间= 10 ns。

笔记

最小典型最大

单元

描述

AC时序要求

参数

100BASE-TX发送定时(t R / F和抖动)

100 Mb / s PMD输出对t R

和t F

100 Mb / st R和t

F不匹配

(6)

100 Mb / s PMD输出对

发送抖动

T2.8.1

T2.8.2

(7)

(6)

100BASE-TX接收包等待时间

T2.9.1

(8)

T2.9.2

载波侦听开启延迟

接收数据延迟

(9)

100 Mb / s正常模式

100 Mb / s正常模式

(10)

(10)

接收包 消激

序

3

4

5

500

1.4

20

24

ns

ps

ns

位

位

第

第

(

续

)

�

T2.12.2

100BASE-TX接收包取消激活时序

T2.10.1

载波侦听OFF延迟

(11)

(12)

10 Mb / s MII传输时序

T2.11.1

T2.11.2

TX_CLK高/低时间

TXD [3:0],TX_EN数据设

置到TX_CLK下降

TXD [3:0],TX_EN从

TX_CLK上升沿开始的数

据保持

10 Mb / s MII接收时序

T2.12.1

T2.11.3

(13)

RX_CLK高/低时间

RX_CLK至RXD [3:0},

RX_DV

延迟

来自RXD [3:0]的RX_CLK

上升沿延迟,RX_DV有效

T2.12.3

10 Mb / s串行模式(SNI)传输时序

TX_CLK高电平时间

T2.13.1

T2.13.2

TX_CLK低电平时间

TXD_0,TX_EN数据设置

为TX_CLK上升

TXD_CLK上升时TXD_0,

TX_EN数据保持

T2.13.4

10 Mb / s串行模式(SNI)接收时序

T2.14.1

T2.13.3

(14)

RX_CLK高/低时间

RX_CLK下降到RXD_0,

RX_DV延迟

T2.14.2

10BASE-T发送时序(数据包开始)

T2.15.1

T2.15.2

从发送输出延迟

TX_CLK的下降沿

从发送输出延迟

TX_CLK的上升沿

100 Mb / s正常模式

(10)

10 Mb / s MII模式

10 Mb / s MII模式

10 Mb / s MII模式

10 Mb / s MII模式

10 Mb / s MII模式

10 Mb / s串行模式(SNI)

10 Mb / s串行模式(SNI)

10 Mb / s串行模式(SNI)

10 Mb / s串行模式(SNI)

10 Mb / s串行模式(SNI)

10 Mb / s MII模式

(15)

10 Mb / s串行模式(SNI)

(15)

190

25

0

160

100

100

20

70

25

0

35

–10

24

200

210

200

240

25

75

30

80

50

65岁

10

3.5

3.5

位

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

位

位

(6) 上升和下降时间为+1或-1幅度的10%和90%

(7) 正常不匹配是所有上升和下降时间的最大值和最小值之差

(8) PMD输入对电压幅度大于信号检测开启阈值。

(9) 通过测量从“ J”代码组的第一位到确定载波侦听的时间来确定载波侦听延时。

(10) 在100 Mb / s模式下,1位时间= 10 ns。

(11) 载波侦听关闭延迟是通过测量从“ T”代码组的第一位到取消载波侦听的时间来确定的。

(12) 连接的Mac应该使用TX_CLK的上升沿驱动发送信号。如上所示,在TX_CLK的下降沿对MII信号进行采样。

(13) 在参考时钟和恢复时钟之间的转换过程中,RX_CLK可能会长时间保持低电平。最短的高低时间不会被违反。

(14) 在参考时钟和恢复时钟之间的转换期间,RX_CLK可以保持较高的时间。最短的高低时间不会被违反。

(15) 1位时间= 100 ns(10 Mb / s)。

笔记

最小典型最大

单元

250 300

250 300

630 1000

ns

ns

ns

位

位

10

8

1200

1000

85

500

100

16

100

125

62

2

16

从SFD显示的测量

10 Mb / s半双工模式

10 Mb / s半双工模式

资料= 1

100 Mb / s内部环回模式

(21)

1个

微秒

ns

ns

多发性硬化

症

多发性硬化

症

ns

多发性硬化

症

ns

微秒

微秒

多发性硬化

症

多发性硬化

症

1个 多发性硬化

350

症

微秒

240

ns

2

微秒

描述

AC时序要求

参数

10BASE-T发送时序(数据包结尾)

数据包高时间结束

(以“ 0”结束位)

数据包高时间结束

(以“ 1”结尾)

T2.16.1

T2.16.2

10BASE-T接收时序(数据包开始)

(16)

T2.17.1

载波侦听开启延迟(PMD

输入对至CRS)

(17)

RX_DV延迟

接收数据延迟

T2.17.2

T2.17.3

10BASE-T接收时序(数据包结尾)

T2.18.1

载波侦听关闭延迟

10 Mb / s心跳时序

T2.19.1

T2.19.2

10 Mb / s的Jabber时序

T2.20.1

CD心跳延迟

CD心跳持续时间

Jabber激活时间

T2.20.2

Jabber停用时间

(18)

10BASE-T标准链路脉冲时序

T2.21.1

T2.21.2

脉冲周期

脉宽

(18)

自动协商快速链接脉冲(FLP)时序

T2.22.1

时钟,数据脉冲宽度

时钟脉冲到时钟脉冲

期

时钟脉冲到数据脉冲

期

T2.22.2

T2.22.3

T2.22.4

T2.22.5

突发宽度

FLP爆发至FLP爆发期间

(19)

TX_EN至RX_DV回送

(20)

SD内部开启时间

SD内部关断时间

100BASE-TX信号检测时序

T2.23.1

T2.23.2

100 Mb / s内部回送时序

T2.24.1

10 Mb / s内部回送时序

T2.25.1

RMII发送时序

T2.26.1

T2.26.2

X1时钟周期

TXD [1:0],TX_EN,到

X1的数据设置上升

来

TX_EN至RX_DV回送

(20) 10 Mb / s内部环回模式

50 MHz参考时钟

20

4

ns

ns

(

续

)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc