1

2

3

4

5

6

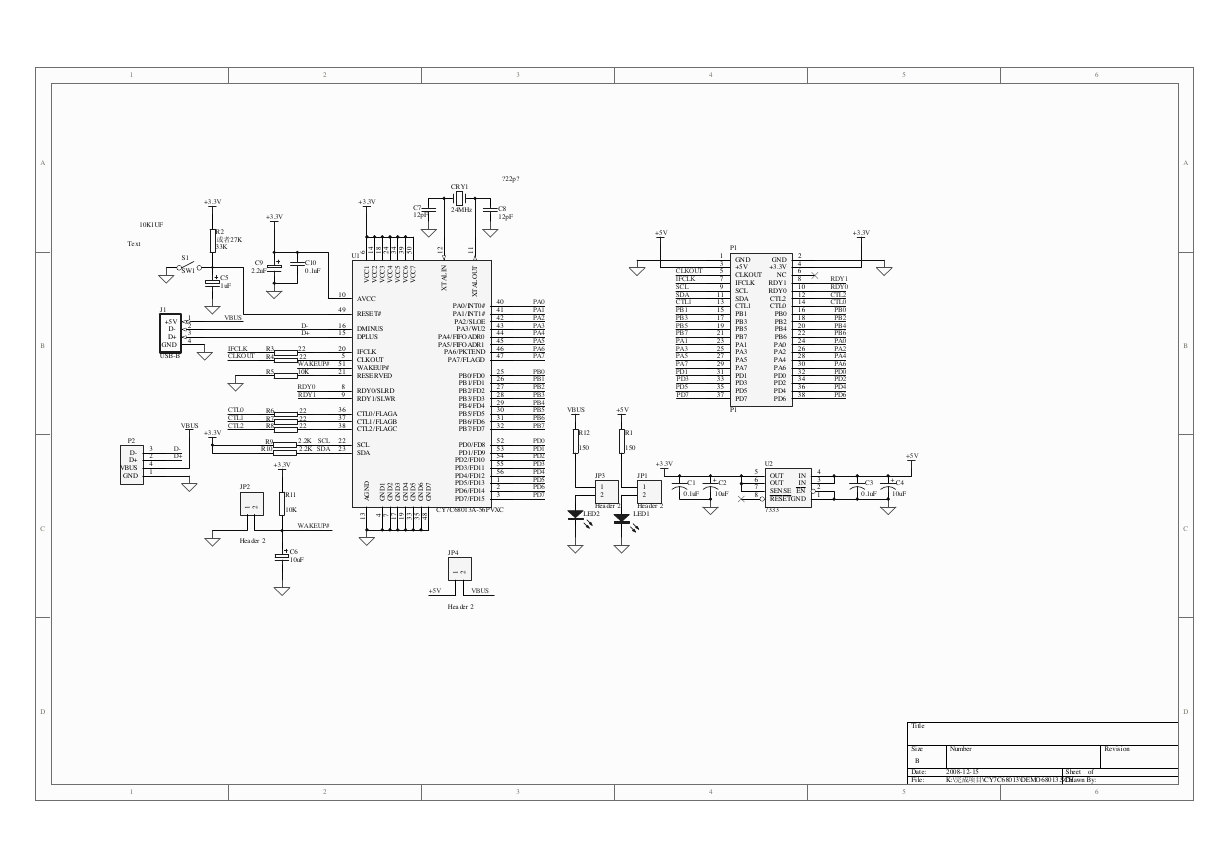

+3.3V

+3.3V

+3.3V

C7

12pF

CRY1

24MHz

?22p?

C8

12pF

10K1UF

Text

S1

SW1

J1

+5V

D-

D+

GND

USB-B

1

2

3

4

R2

或者27K

33K

C5

1uF

VBUS

IFCLK

CLKOUT

CTL0

CTL1

CTL2

VBUS

+3.3V

D-

D+

P2

D-

D+

VBUS

GND

3

2

4

1

C9

2.2uF

C10

0.1uF

10

49

16

15

20

5

51

21

8

9

36

37

38

22

23

D-

D+

22

22

WAKEUP#

10K

RDY0

RDY1

22

22

22

2.2K

2.2K

SCL

SDA

R3

R4

R5

R6

R7

R8

R9

R10

JP2

12

Header 2

+3.3V

R11

10K

WAKEUP#

C6

10uF

4

1

8

1

4

2

4

3

9

3

0

5

6

U1

1

C

C

V

2

C

C

V

3

C

C

V

4

C

C

V

5

C

C

V

6

C

C

V

7

C

C

V

AVCC

RESET#

DMINUS

DPLUS

IFCLK

CLKOUT

WAKEUP#

RESERVED

RDY0/SLRD

RDY1/SLWR

CTL0/FLAGA

CTL1/FLAGB

CTL2/FLAGC

SCL

SDA

D

N

G

A

3

1

1

D

N

G

2

D

N

G

3

D

N

G

4

D

N

G

5

D

N

G

6

D

N

G

7

D

N

G

4

7

7

1

9

1

3

3

5

3

8

4

2

1

1

1

N

I

L

A

T

X

T

U

O

L

A

T

X

PA0/INT0#

PA1/INT1#

PA2/SLOE

PA3/WU2

PA4/FIFOADR0

PA5/FIFOADR1

PA6/PKTEND

PA7/FLAGD

PB0/FD0

PB1/FD1

PB2/FD2

PB3/FD3

PB4/FD4

PB5/FD5

PB6/FD6

PB7/FD7

PD0/FD8

PD1/FD9

PD2/FD10

PD3/FD11

PD4/FD12

PD5/FD13

PD6/FD14

PD7/FD15

40

41

42

43

44

45

46

47

25

26

27

28

29

30

31

32

52

53

54

55

56

1

2

3

CY7C68013A-56PVXC

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

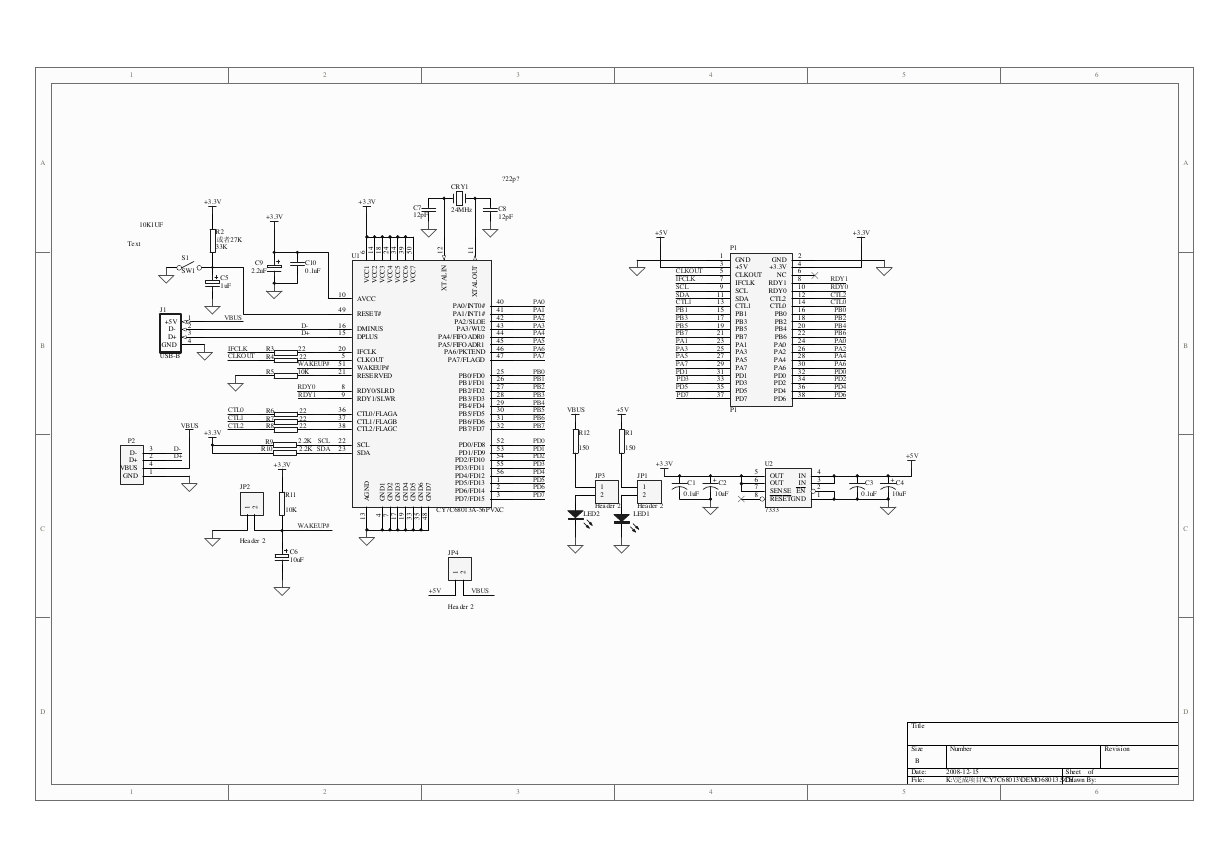

+5V

+3.3V

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

P1

GND

+5V

CLKOUT

IFCLK

SCL

SDA

CTL1

PB1

PB3

PB5

PB7

PA1

PA3

PA5

PA7

PD1

PD3

PD5

PD7

GND

+3.3V

NC

RDY1

RDY0

CTL2

CTL0

PB0

PB2

PB4

PB6

PA0

PA2

PA4

PA6

PD0

PD2

PD4

PD6

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

CLKOUT

IFCLK

SCL

SDA

CTL1

PB1

PB3

PB5

PB7

PA1

PA3

PA5

PA7

PD1

PD3

PD5

PD7

RDY1

RDY0

CTL2

CTL0

PB0

PB2

PB4

PB6

PA0

PA2

PA4

PA6

PD0

PD2

PD4

PD6

VBUS

+5V

P1

R12

150

R1

150

+3.3V

JP3

1

2

JP1

1

2

Header 2

LED2

Header 2

LED1

C1

0.1uF

+ C2

10uF

5

6

7

8

U2

OUT

OUT

SENSE

RESET

IN

IN

EN

GND

7333

4

3

2

1

+5V

C3

0.1uF

+ C4

10uF

JP4

12

+5V

VBUS

Header 2

A

B

C

D

1

2

3

4

Title

Size

B

Date:

File:

5

Number

Revision

2008-12-15

Sheet of

K:\完成项目\CY7C68013\DEMO68013.SCHDrawn By:

6

A

B

C

D

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc