计算机组成与体系结

构

课程设计报告

计算机科学与工程学院

学

班

院:

级:

学生姓名:

学

号:

指导老师:

朱娟

提交日期:

�

采用硬联线控制器的顺序模型计算机设计与调试

总框图(数据通路图);.............................................. 2

硬联线控制器逻辑模块图;........................................ 3

指令周期流程图和控制台指令流程图;....................4

根据流程图写出的组合译码表....................................8

各控制信号的 ABEL 语言源程序;......错误!未定义书签。

老师给定的验收程序;................................................ 9

设计说明书;.............................................................. 10

调试小结。...................................................................11

1

�

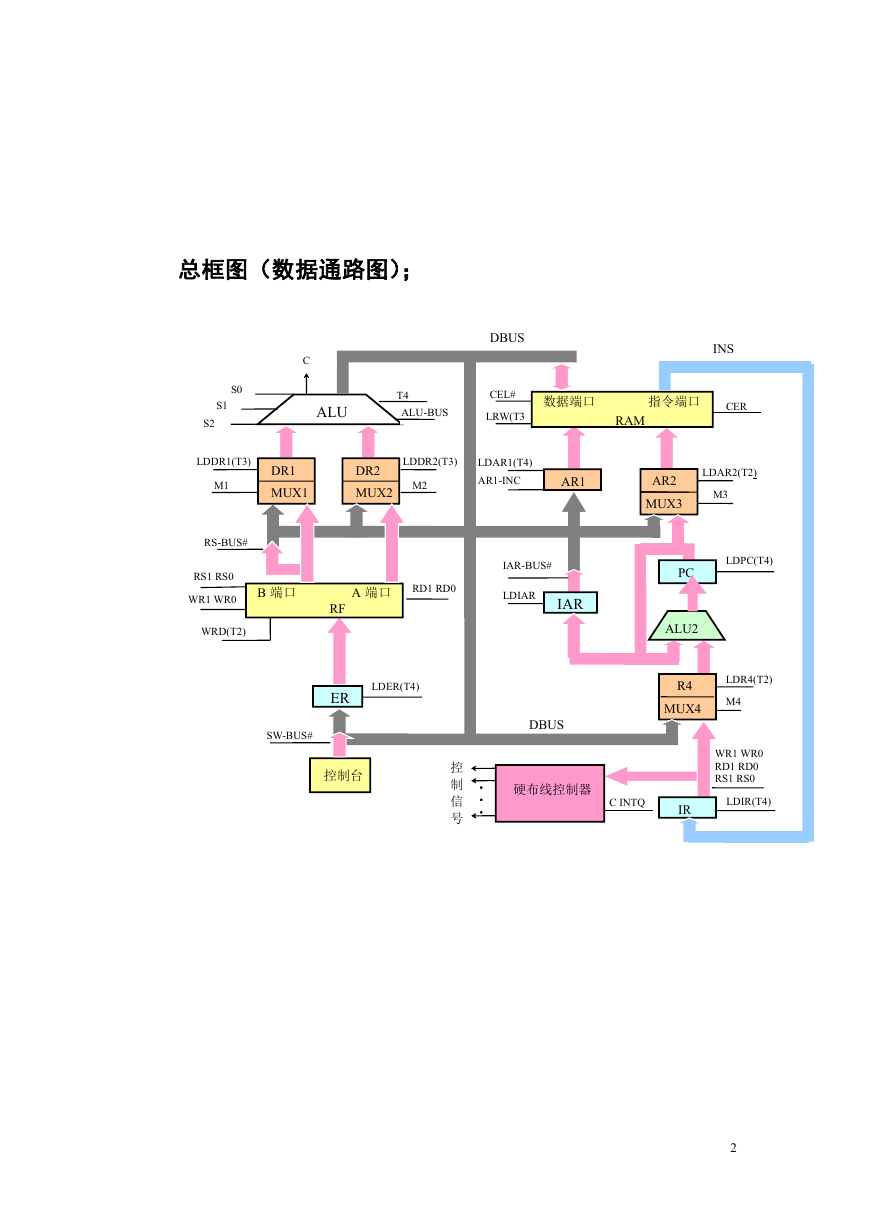

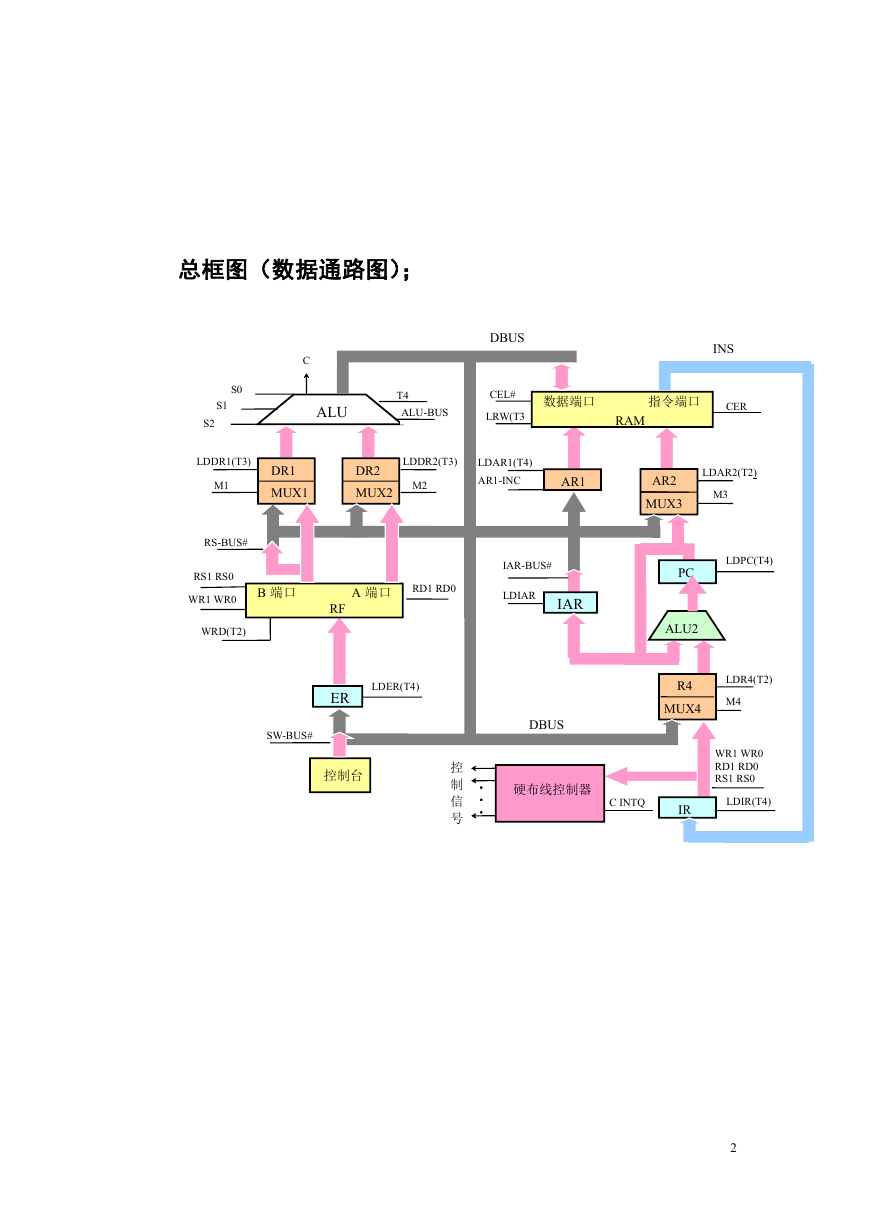

总框图(数据通路图);

C

DBUS

S0

S1

S2

ALU

T4

ALU-BUS

CEL#

LRW(T3

数据端口

指令端口

RAM

INS

CER

LDDR1(T3)

M1

DR1

MUX1

B

DR2

MUX2

A

LDDR2(T3)

M2

LDAR1(T4)

AR1-INC

AR1

RS-BUS#

RS1 RS0

WR1 WR0

WRD(T2)

B 端口

RF

A 端口

RD1 RD0

IAR-BUS#

LDIAR

IAR

LDER(T4)

ER

SW-BUS#

控制台

DBUS

控

制

信

号

·

·

·

硬布线控制器

C INTQ

IR

AR2

MUX3

LDAR2(T2)

M3

LDPC(T4)

PC

ALU2

R4

MUX4

LDR4(T2)

M4

WR1 WR0

RD1 RD0

RS1 RS0

LDIR(T4)

2

�

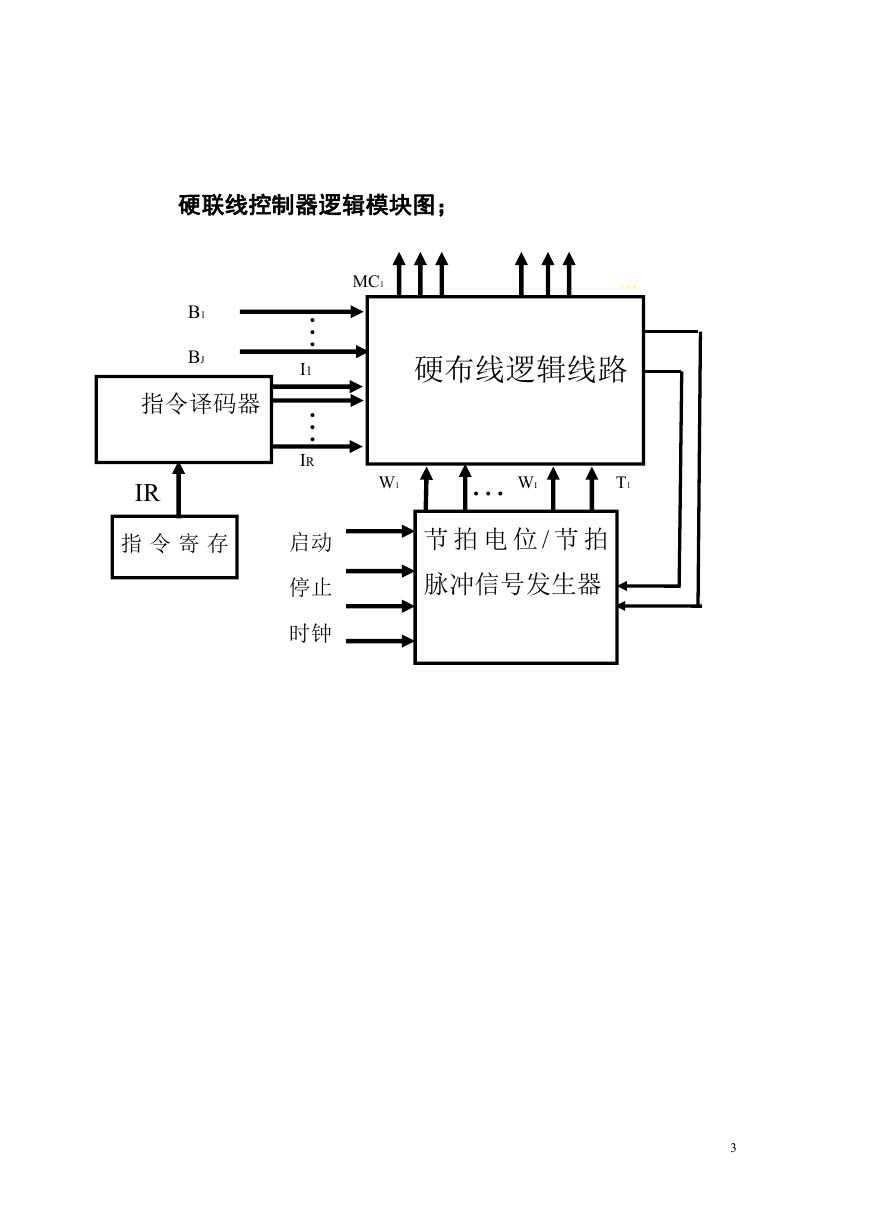

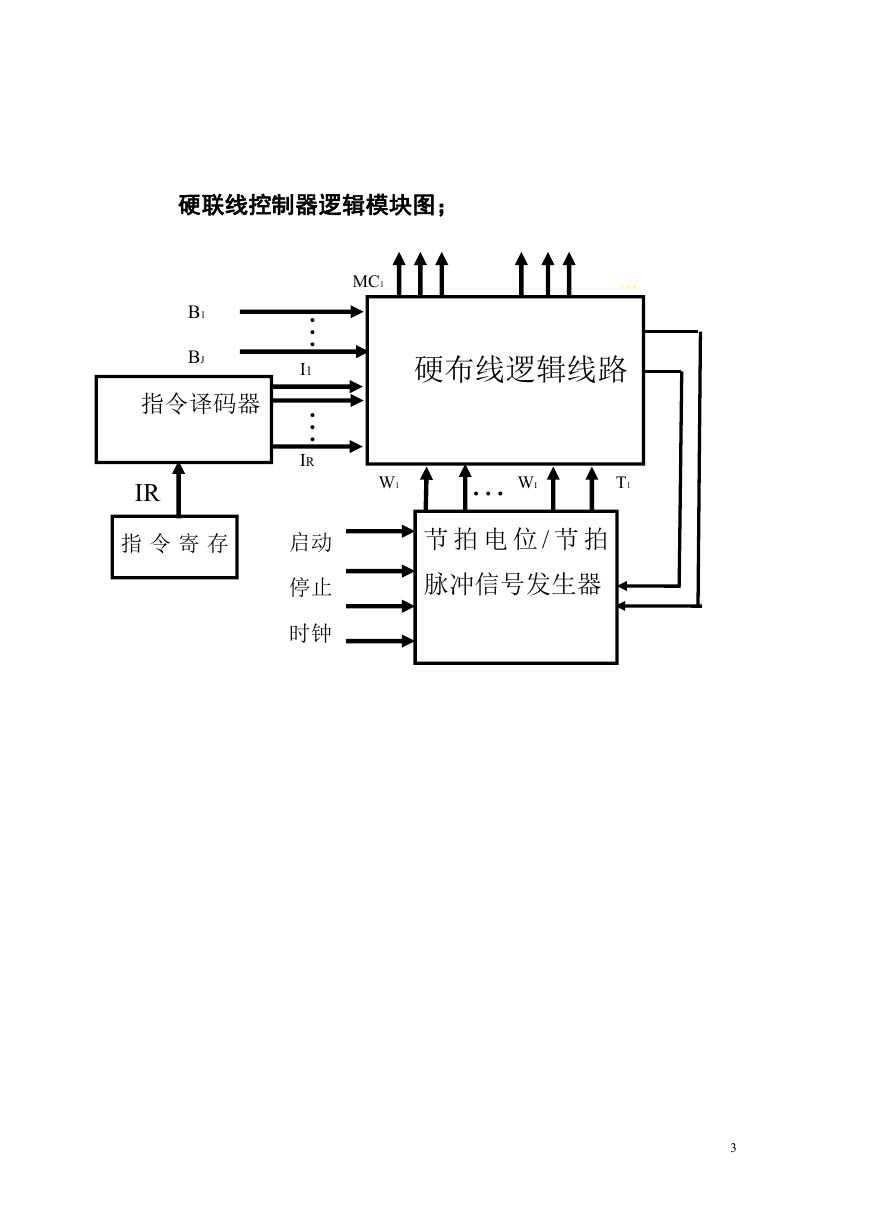

硬联线控制器逻辑模块图;

B1

BJ

指令译码器

IR

指 令 寄 存

器

MC1

MCN

W1

TK

…

I1

…

IR

启动

停止

时钟

复位

…

硬布线逻辑线路

WI

T1

…

…

节 拍 电 位 / 节 拍

脉冲信号发生器

3

�

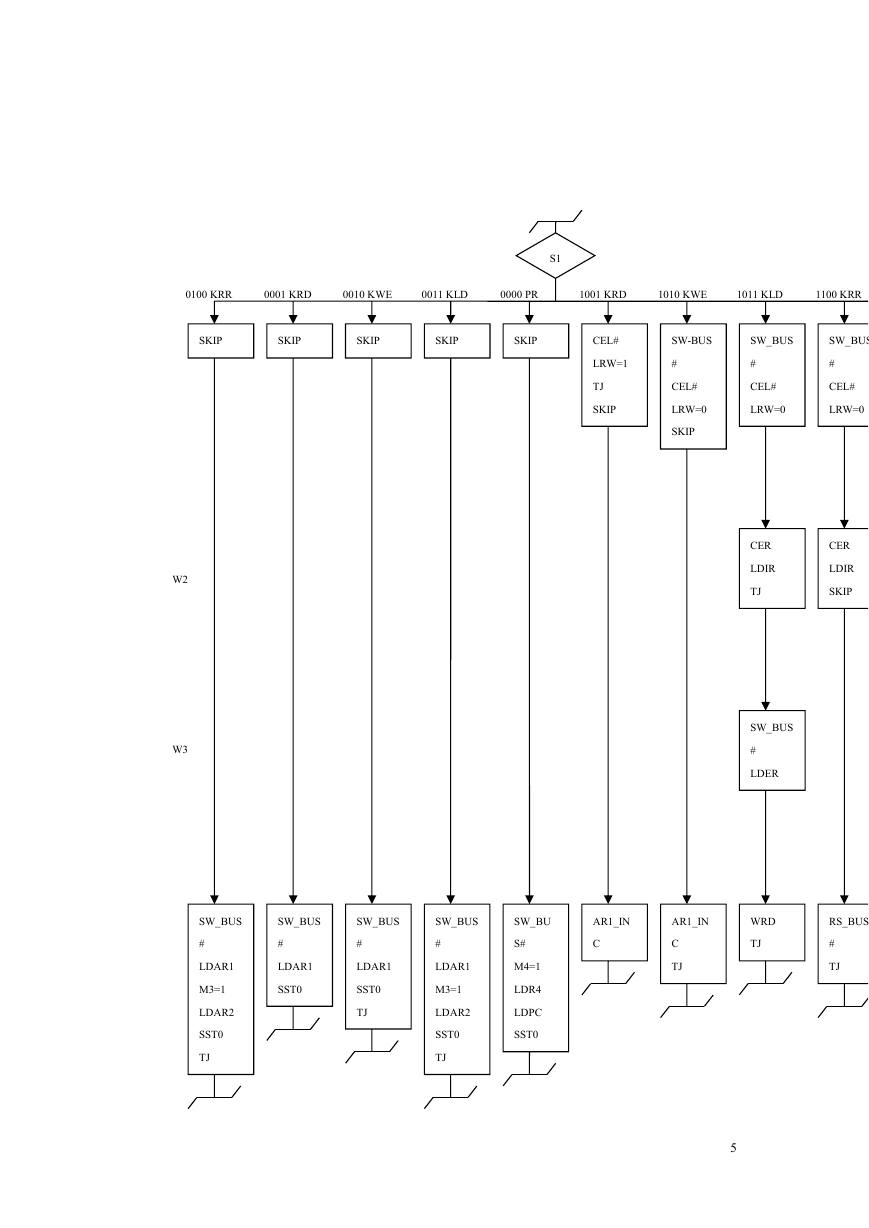

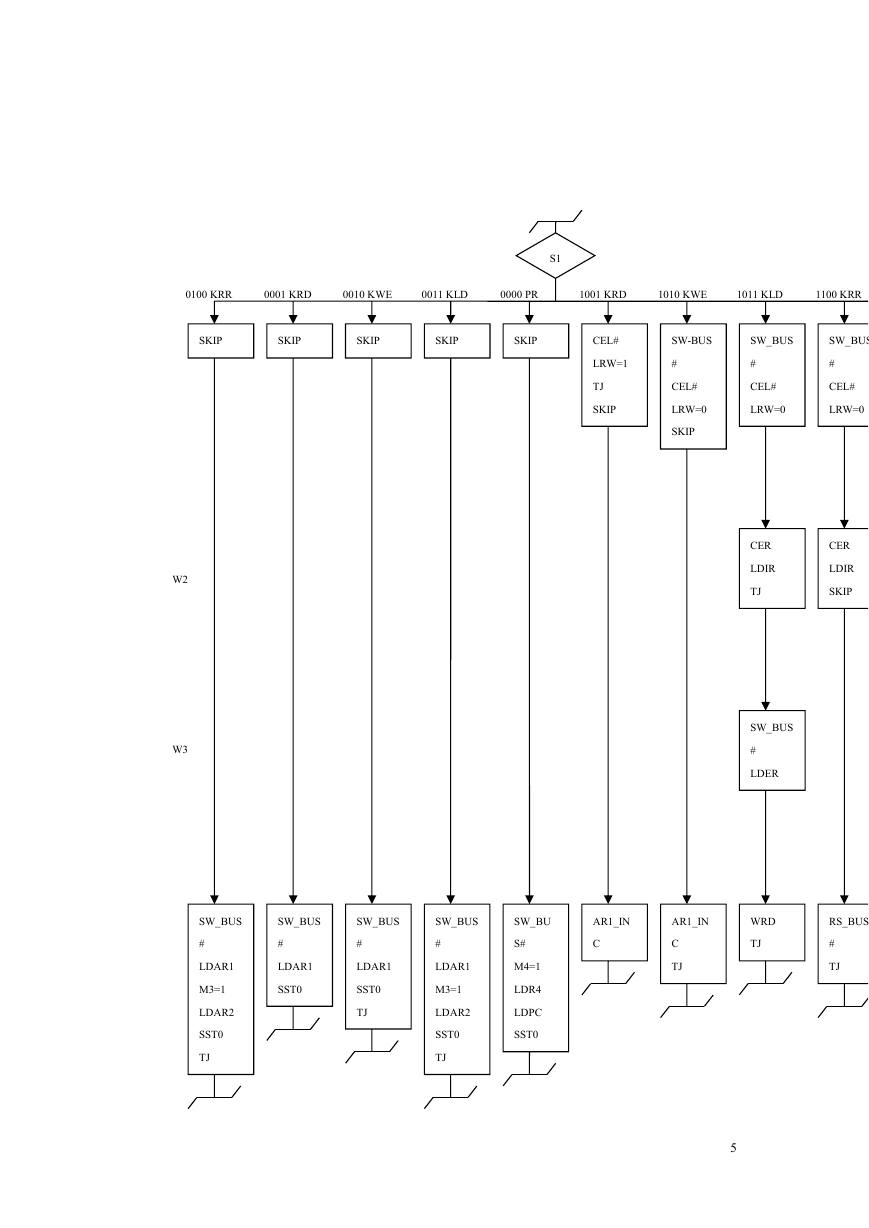

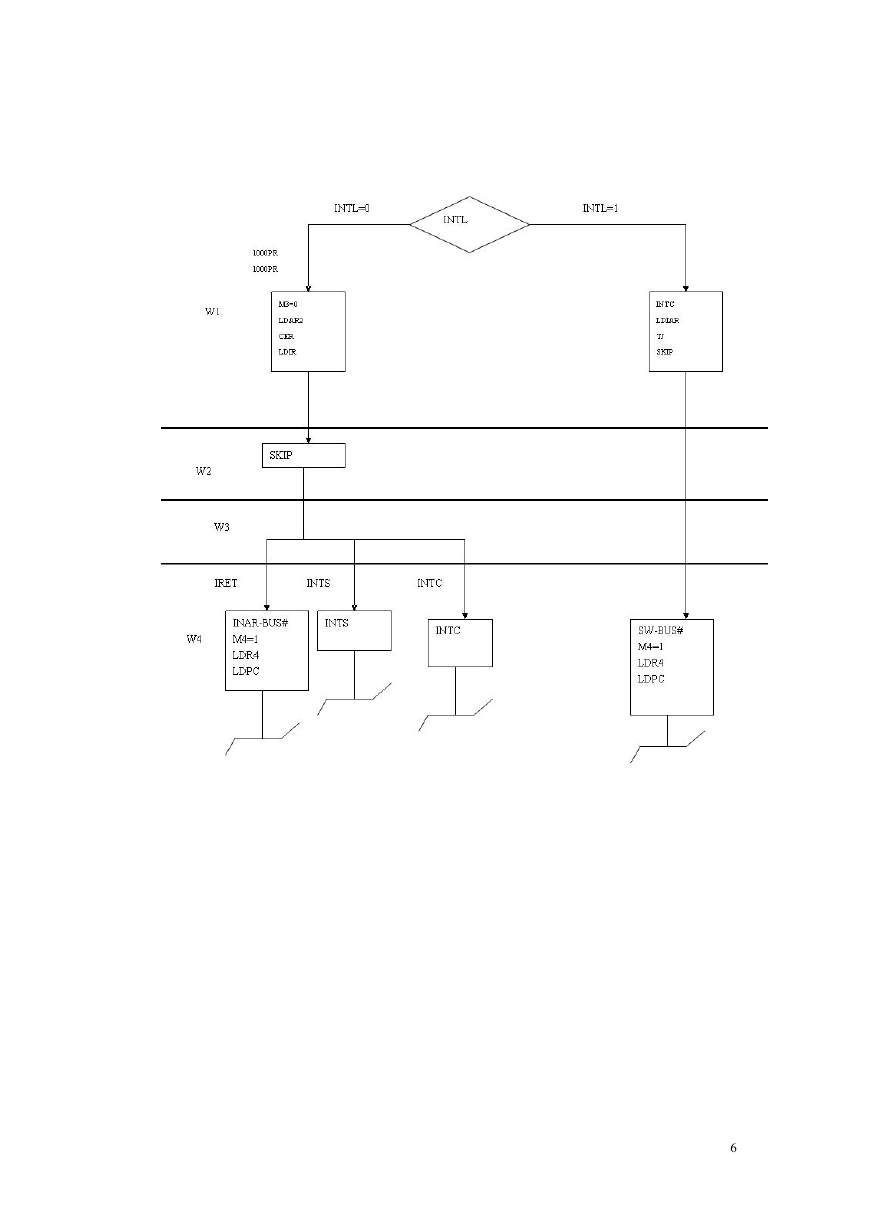

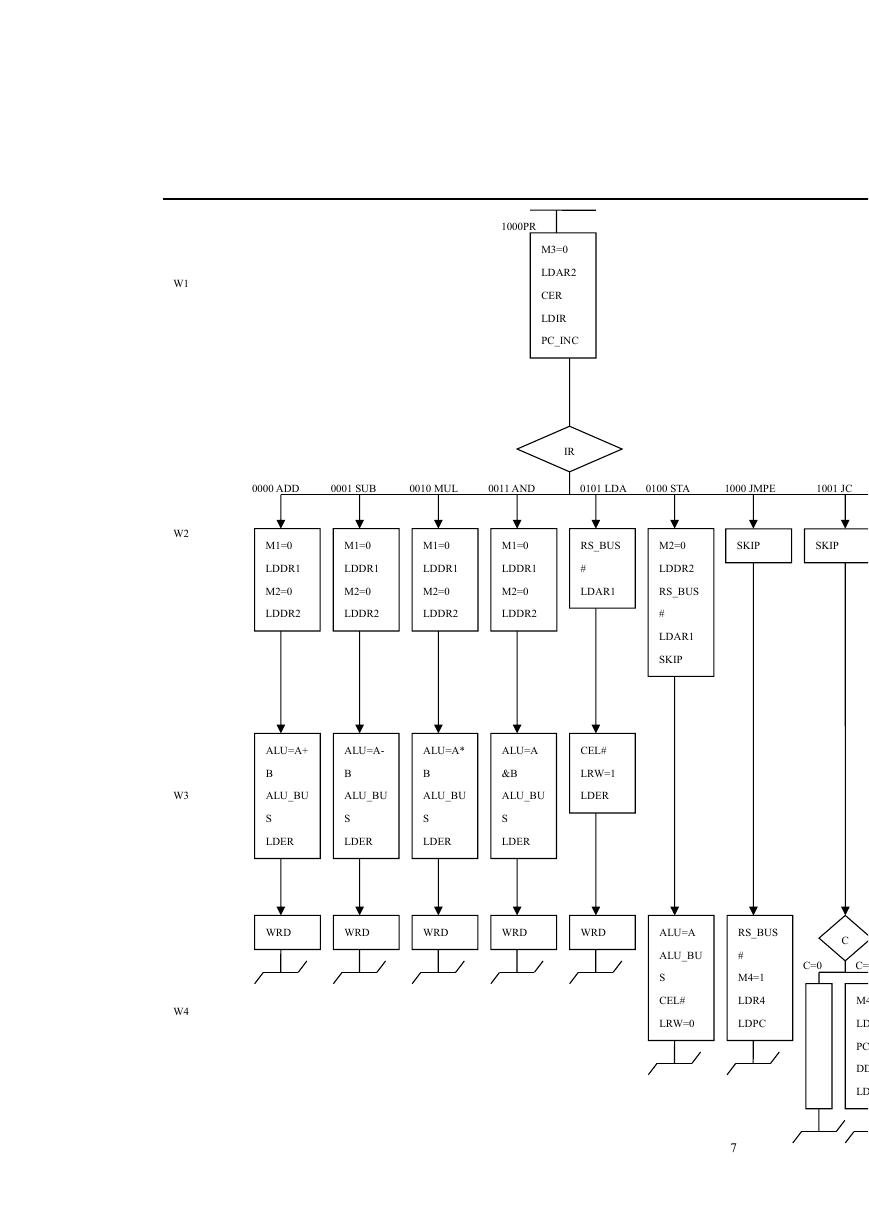

指令周期流程图和控制台指令流程图;

4

�

0100 KRR

0001 KRD

0010 KWE

0011 KLD

0000 PR

1001 KRD

1010 KWE

1011 KLD

1100 KRR

S1

SKIP

SKIP

SKIP

SKIP

SKIP

CEL#

LRW=1

TJ

SKIP

SW-BUS

SW_BUS

SW_BUS

#

CEL#

LRW=0

SKIP

#

CEL#

LRW=0

#

CEL#

LRW=0

W2

W3

CER

LDIR

TJ

CER

LDIR

SKIP

SW_BUS

#

LDER

SW_BUS

SW_BUS

SW_BUS

SW_BUS

SW_BU

AR1_IN

AR1_IN

#

LDAR1

M3=1

LDAR2

SST0

TJ

#

LDAR1

SST0

#

LDAR1

SST0

TJ

#

LDAR1

M3=1

LDAR2

SST0

TJ

S#

M4=1

LDR4

LDPC

SST0

C

C

TJ

WRD

TJ

RS_BUS

#

TJ

5

�

6

�

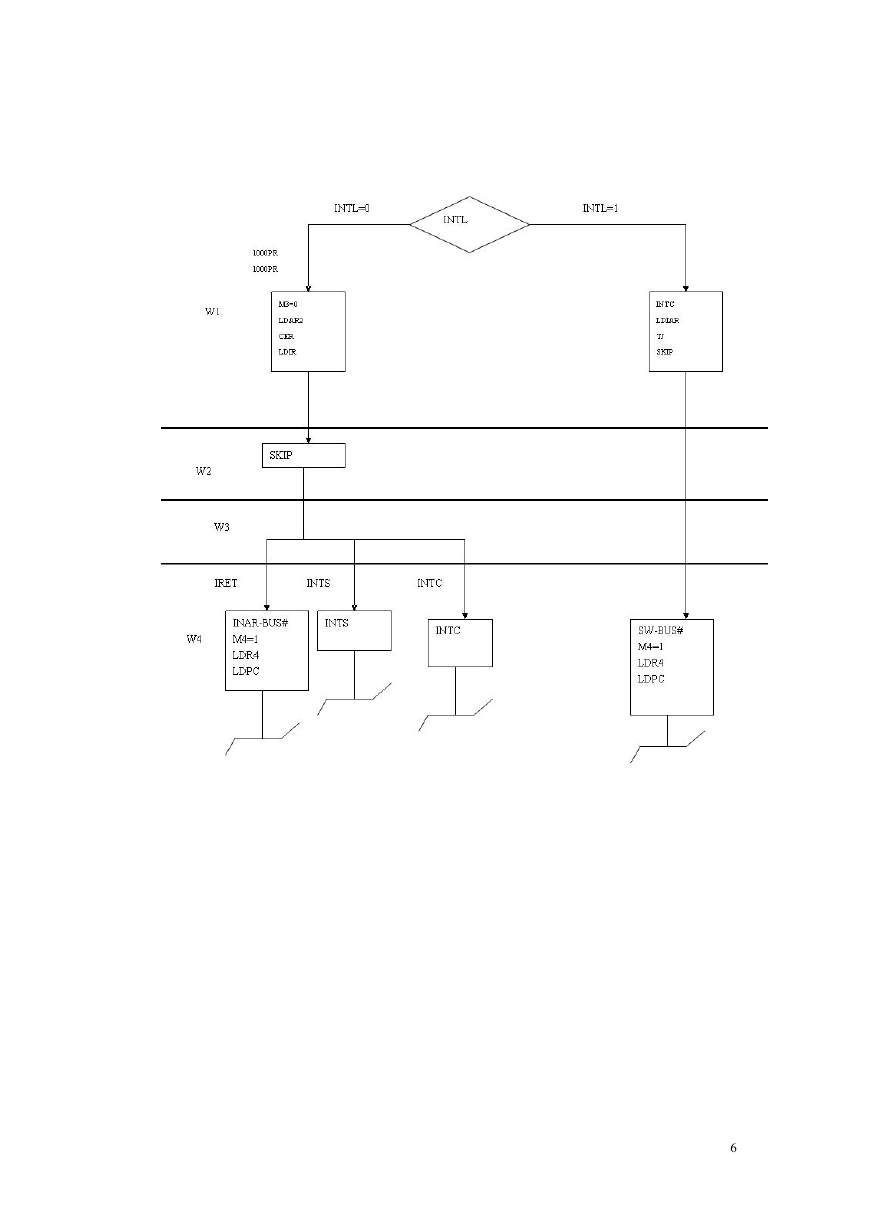

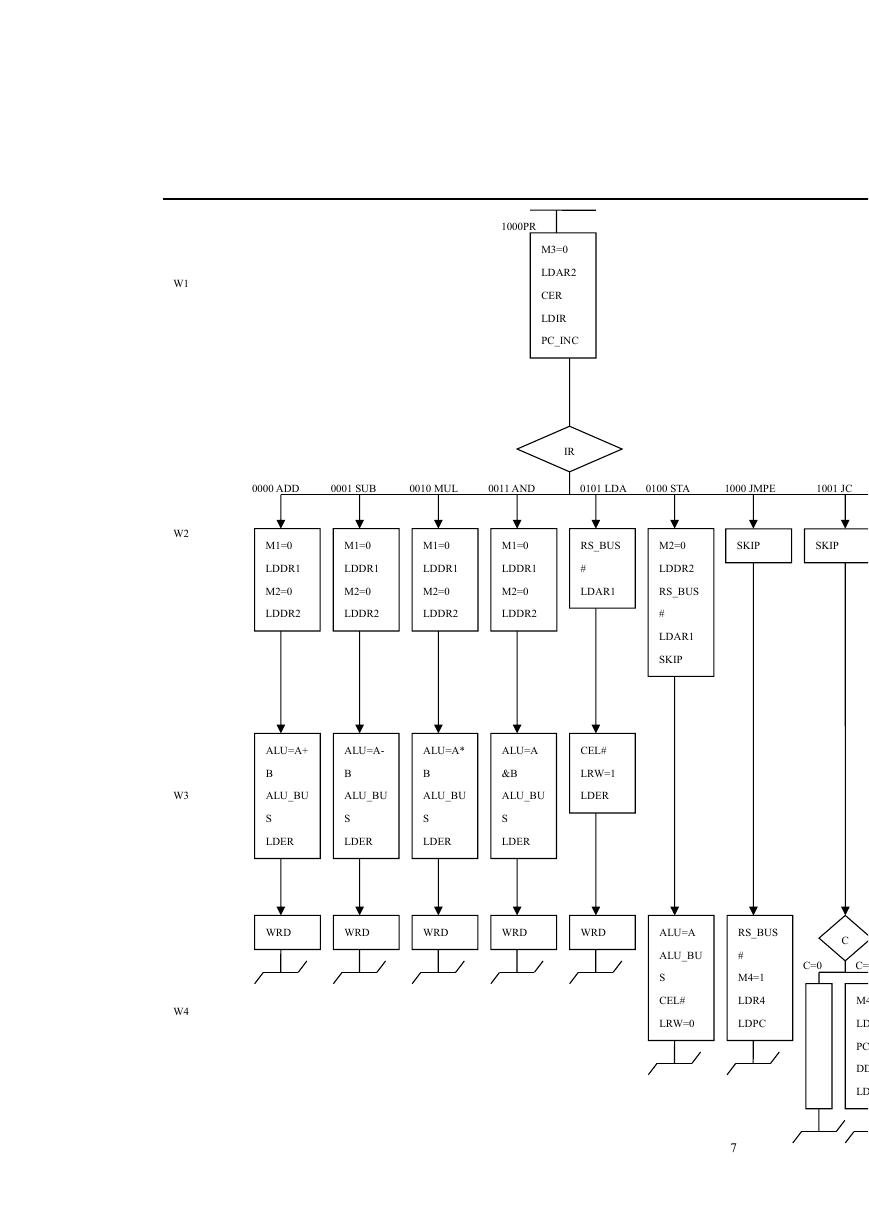

W1

W2

1000PR

M3=0

LDAR2

CER

LDIR

PC_INC

IR

0000 ADD

0001 SUB

0010 MUL

0011 AND

0101 LDA

0100 STA

1000 JMPE

1001 JC

M1=0

LDDR1

M2=0

LDDR2

M1=0

LDDR1

M2=0

LDDR2

M1=0

LDDR1

M2=0

LDDR2

M1=0

LDDR1

M2=0

LDDR2

RS_BUS

#

LDAR1

SKIP

SKIP

M2=0

LDDR2

RS_BUS

#

LDAR1

SKIP

ALU=A+

ALU=A-

ALU=A*

ALU=A

B

B

B

&B

W3

ALU_BU

ALU_BU

ALU_BU

ALU_BU

CEL#

LRW=1

LDER

S

LDER

S

LDER

S

LDER

S

LDER

WRD

WRD

WRD

WRD

WRD

W4

ALU=A

ALU_BU

S

CEL#

LRW=0

RS_BUS

#

M4=1

LDR4

LDPC

C

C=0

C=1

M4=0

LDR4

PC_A

DD

LDPC

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc