第 12 卷 第 2 期

重庆科技学院学报(自然科学版)

2010 年 4 月

基于 FPGA 的数字 PID 控制器设计

陈昭明 白向林 龚晓宏

(中国航天第四研究院 401 所,西安 710025)

摘 要:PID 控制器的可靠性及实时性是实现运动控制系统精确定位的重要环节。在分析 PID 控制算法的基础上,采

用 FPGA 对增量型 PID 控制器进行设计及仿真实验,整个程序采用 VerilogHDL 语言编写。 仿真结果表明该方法的有

效性和可行性。

关键词:控制器;FPGA;控制策略;控制算法

中图分类号:TP273

文章编号:1673-1980(2010)02-0149-03

文献标识码:A

PID 控制器结构清晰、参数可调,适用于各种控

制对象,可在现场根据实际情况调节参数而取得较

好的控制效果, 因此在动态控制系统中广泛使用。

其核心思想是针对控制对象的控制需求 ,建立描述

对象动态特性的数学模型, 通过采用调整比例、微

分、 积分参数的控制策略来达到最佳系统响应和控

制效果。 但是采用微处理器来实现时 ,不能完全避

免程序跑飞和计算机误动作对整个控制系统的破坏

性影响。 现场可编程门阵列 FPGA 的出现为 PID 控

制器的设计提供了新的实现手段。 FPGA 集成度高、

体积小、功耗低、可靠性高、设计方法灵活,不仅具有

反复编程、反复探险、反复使用等特点,更能得到实

用的系统芯片 SOC(System On Chip)。 在本设计中采

用 Xilinx 公 司 的 Virtex-Ⅱ Pro 系 列 芯 片 XC2VP30

实 现 数 字 PID 控 制 器 的 设 计 , 提 高 系 统 的 运 算 速

度、减少系统的体积、增强其可靠性。

1 PID 控制算法

完整的 PID 控制表达式为:

u(t)=kp [e(t)+ 1

Ti

t

0乙e(t)dt+Td

de(t)

dt

]

(1)

称为比例增益;Ti

为积分时间常数;Td

式中:kp

为微

分时间常数;u(t)为控制量;e(t)为偏差。 在数字控制

系统中 ,PID 控制算法的实现必须用数值逼近的方

法将模拟算法离散化。 当采样周期很短时,用求和

代 替 积 分 ,向 后 差 分 代 替 微 分 ,使 模 拟 PID 算 法 离

散化为差分方程。 经过合并,整理可得:

Δu(k)=kpΔe(k)+kie(k)+kd[Δe(k)-Δe(k-1)]

(2)

式中:Δe(k)=e(k)-e(k-1);ki=kpT/Ti,积分系数;kd=kpTd/T

为微分系数;T 为采样周期;k 为采样序号。 通常称

式(2)为增量型 PID 控制算法。 从式(2)可看出增量

型控制算法只与前三次采样值有关, 不需要大量的

数据存储和累加,因而不易引起误差累积,计算量小

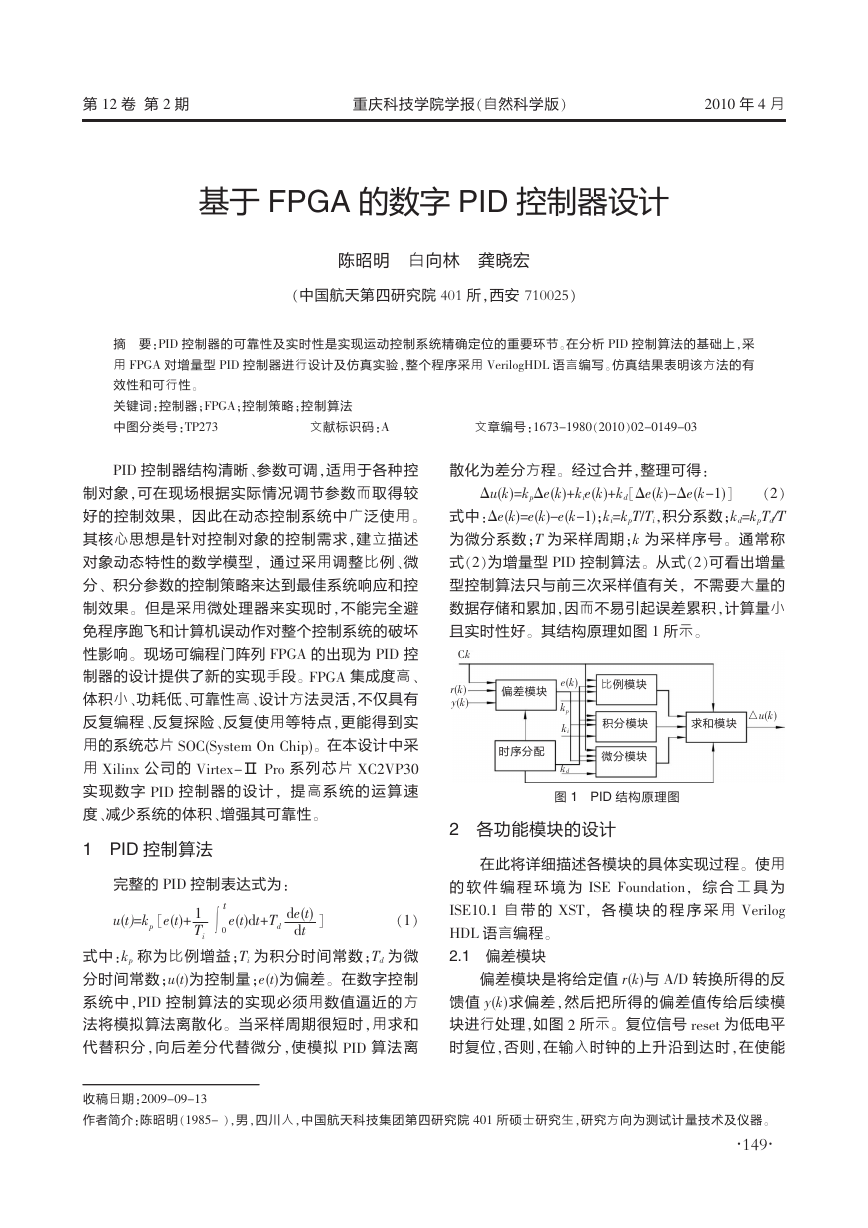

且实时性好。 其结构原理如图 1 所示。

Ck

r(k)

y(k)

偏差模块

e(k)

比例模块

时序分配

kp

ki

kd

积分模块

求和模块 △u(k)

微分模块

图 1 PID 结构原理图

2 各功能模块的设计

在此将详细描述各模块的具体实现过程。 使用

的 软 件 编 程 环 境 为 ISE Foundation, 综 合 工 具 为

ISE10.1 自 带 的 XST, 各 模 块 的 程 序 采 用 Verilog

HDL 语言编程。

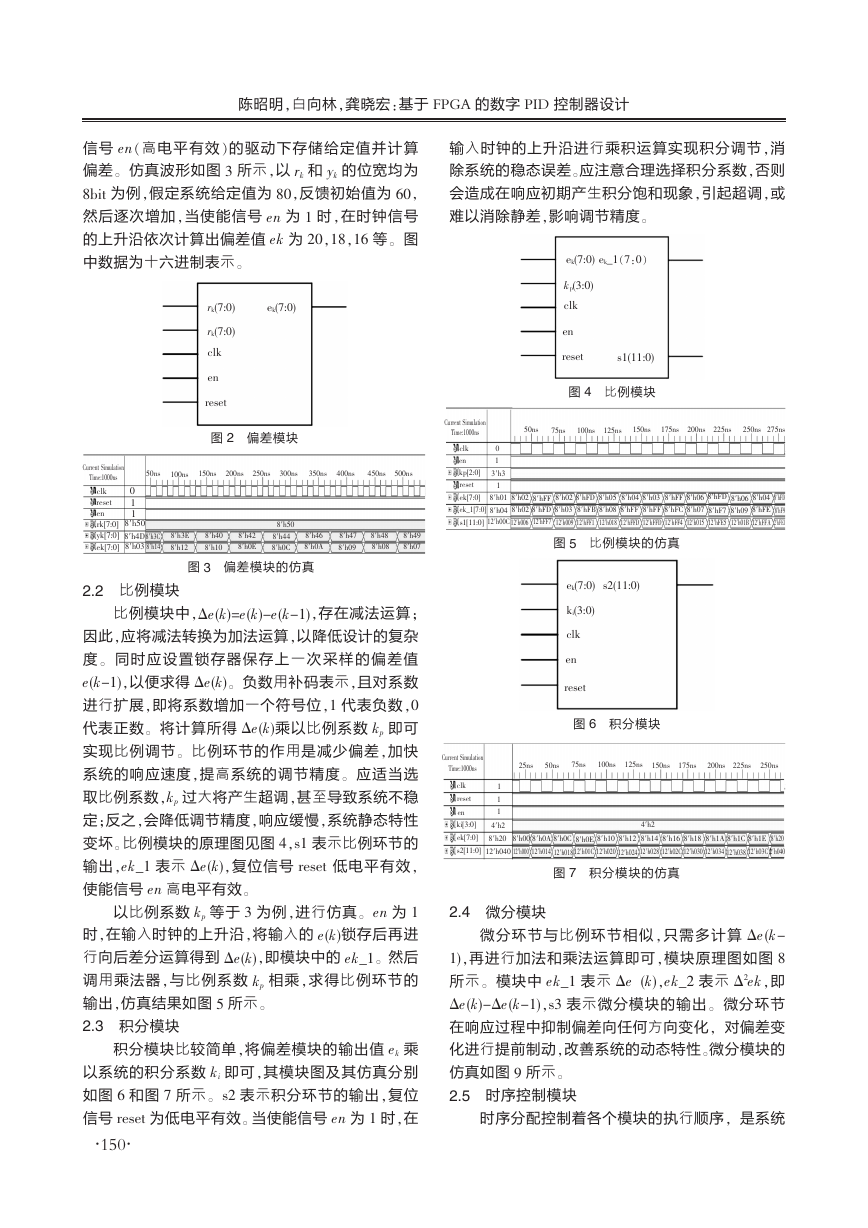

2.1 偏差模块

偏差模块是将给定值 r(k)与 A/D 转换所得的反

馈值 y(k)求偏差 ,然后把所得的偏差值传给后续模

块进行处理,如图 2 所示。 复位信号 reset 为低电平

时复位,否则,在输入时钟的上升沿到达时,在使能

收稿日期:2009-09-13

作者简介:陈昭明(1985- ),男,四川人,中国航天科技集团第四研究院 401 所硕士研究生,研究方向为测试计量技术及仪器。

149· ·

�

陈昭明,白向林,龚晓宏:基于 FPGA 的数字 PID 控制器设计

信号 en(高电平有效 )的驱动下存储给定值并 计 算

偏差。 仿真波形如图 3 所示,以 rk

的位宽均为

8bit 为例,假定系统给定值为 80,反馈初始值为 60,

然后逐次增加,当使能信号 en 为 1 时,在时钟信号

的上升沿依次计算出偏差值 ek 为 20,18,16 等。 图

中数据为十六进制表示。

和 yk

ek(7:0)

rk(7:0)

rk(7:0)

clk

en

reset

图 2 偏差模块

Current Simulation

Time:1000ns

clk

reset

en

rk[7:0]

yk[7:0]

ek[7:0]

50ns

100ns

150ns

200ns

250ns

300ns

350ns

400ns

450ns

500ns

0

1

1

8′h50

8′h4D

8′h03

8′h3C

8′h14

8′h3E

8′h12

8′h40

8′h10

8′h42

8′h0E

8′h50

8′h44

8′h0C

8′h46

8′h0A

8′h47

8′h09

8′h48

8′h08

8′h49

8′h07

图 3 偏差模块的仿真

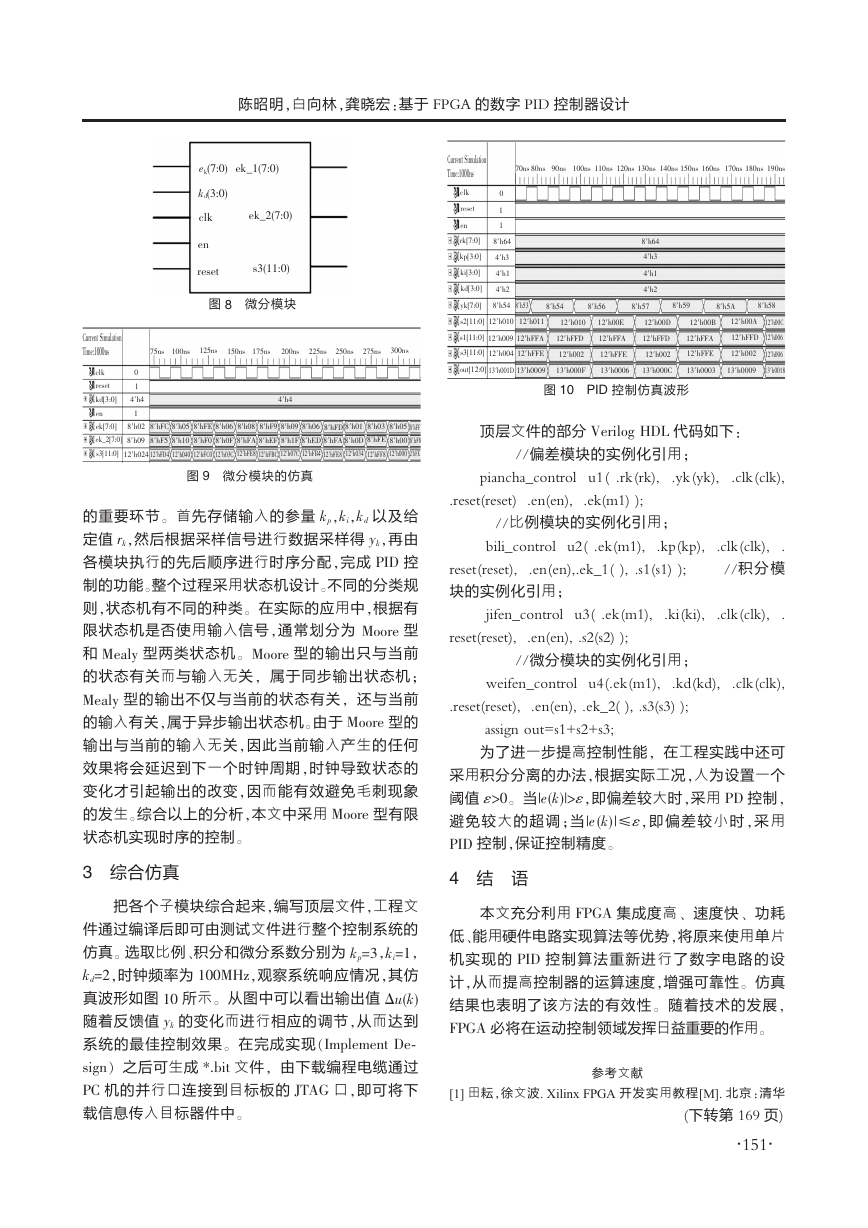

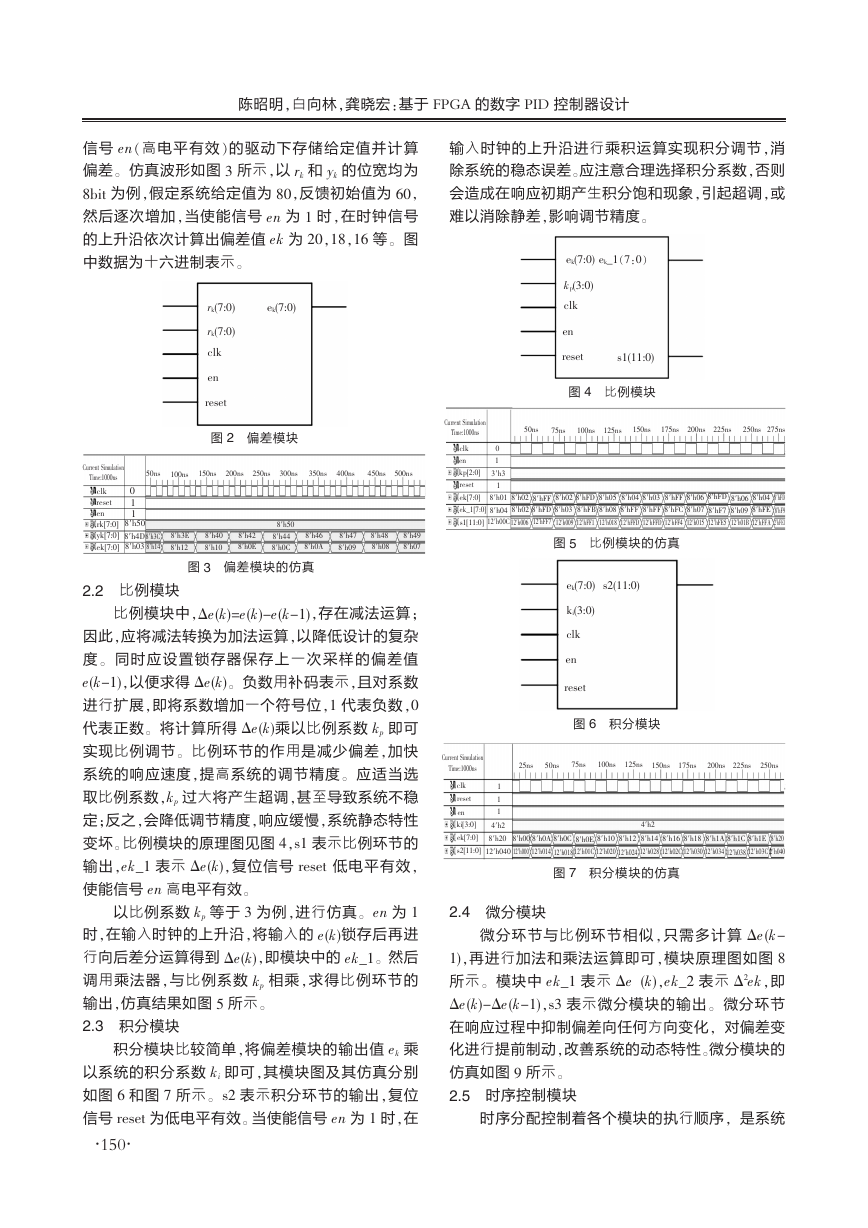

2.2 比例模块

比例模块中,Δe(k)=e(k)-e(k-1),存在减法运算;

因此,应将减法转换为加法运算,以降低设计的复杂

度 。 同 时 应 设 置 锁 存 器 保 存 上一 次 采 样 的 偏 差 值

e(k-1),以便求得 Δe(k)。 负数用补码表示,且对系数

进行扩展,即将系数增加一个符号位,1 代表负数,0

代表正数。 将计算所得 Δe(k)乘以比例系数 kp

即可

实现比例调节。 比例环节的作用是减少偏差,加快

系统的响应速度,提高系统的调节精度。 应适当选

取比例系数,kp

过大将产生超调,甚至导致系统不稳

定;反之,会降低调节精度,响应缓慢,系统静态特性

变坏。 比例模块的原理图见图 4,s1 表示比例环节的

输出,ek_1 表示 Δe(k),复位信号 reset 低电平有效,

使能信号 en 高电平有效。

以比例系数 kp

等于 3 为例,进行仿真。 en 为 1

时,在输入时钟的上升沿,将输入的 e(k)锁存后再进

行向后差分运算得到 Δe(k),即模块中的 ek_1。 然后

调用乘法器 ,与比例系数 kp

相乘 ,求得比例环节的

输出,仿真结果如图 5 所示。

2.3 积分模块

积分模块比较简单 ,将偏差模块的输出值 ek

乘

以系统的积分系数 ki

即可,其模块图及其仿真分别

如图 6 和图 7 所示。 s2 表示积分环节的输出,复位

信号 reset 为低电平有效。 当使能信号 en 为 1 时,在

150· ·

输入时钟的上升沿进行乘积运算实现积分调节 ,消

除系统的稳态误差。应注意合理选择积分系数,否则

会造成在响应初期产生积分饱和现象,引起超调,或

难以消除静差,影响调节精度。

ek(7:0) ek_1(7:0)

kp(3:0)

clk

en

reset

s1(11:0)

图 4 比例模块

50ns

75ns

100ns

125ns

150ns

175ns

200ns

225ns

250ns 275ns

8′h02

8′h03

8′hFF

8′h02

8′hFF 8′h02 8′hFD 8′h05 8′h04

8′hFD

8′hFD 8′h03 8′hFB 8′h08 8′hFF 8′hFF 8′hFC 8′h07 8′hF7 8′h09 8′hFE 8′hF9

12′h006 12′hFF7 12′h009 12′hFF1 12′h018 12′hFFD 12′hFFD 12′hFF4 12′h015 12′hFE5 12′h01B 12′hFFA 2′hFEI

8′h06 8′hFD 8′h06 8′h04

Current Simulation

Time:1000ns

clk

en

0

1

kp[2:0]

3′h3

reset

1

ek[7:0]

8′h01

ek_1[7:0]

s1[11:0]

8′h04

12′h00C

图 5 比例模块的仿真

ek(7:0) s2(11:0)

ki(3:0)

clk

en

reset

图 6 积分模块

Current Simulation

Time:1000ns

25ns

50ns

75ns

100ns

125ns

150ns

175ns

200ns 225ns

250ns

clk

reset

en

ki[3:0]

ek[7:0]

1

1

1

4′h2

8′h20

8′h00

s2[11:0]

12′h040

12′h000

4′h2

8′h0A 8′h0C 8′h0E 8′h10 8′h12 8′h14 8′h16 8′h18 8′h1A 8′h1C 8′h1E 8′h20

12′h014 12′h018 12′h01C 12′h020 12′h024 12′h028 12′h02C 12′h030 12′h034 12′h038 12′h03C

2′h040

图 7 积分模块的仿真

2.4 微分模块

微分环节与比例环 节 相 似 ,只 需 多 计 算 Δe(k-

1),再进行加法和乘法运算即可,模块原理图如图 8

所示。 模块中 ek_1 表示 Δe (k),ek_2 表示 Δ2ek,即

Δe(k)-Δe(k-1),s3 表示微分模块的输出。 微分环节

在响应过程中抑制偏差向任何方向变化, 对偏差变

化进行提前制动,改善系统的动态特性。微分模块的

仿真如图 9 所示。

2.5 时序控制模块

时序分配控制着各个模块的执行顺序, 是系统

�

陈昭明,白向林,龚晓宏:基于 FPGA 的数字 PID 控制器设计

ek(7:0) ek_1(7:0)

kd(3:0)

clk

en

reset

ek_2(7:0)

s3(11:0)

图 8 微分模块

Current Simulation

Time:1000ns

clk

reset

0

1

kd[3:0]

4′h4

en

1

75ns

100ns

125ns

150ns 175ns

200ns

225ns

250ns

275ns

300ns

4′h4

Current Simulation

Time:1000ns

clk

reset

en

0

1

1

rk[7:0]

8′h64

kp[3:0]

ki[3:0]

kd[3:0]

4′h3

4′h1

4′h2

70ns 80ns 90ns 100ns 110ns 120ns 130ns 140ns 150ns 160ns 170ns 180ns 190ns

8′h64

4′h3

4′h1

4′h2

yk[7:0]

8′h54

8′h53

8′h54

8′h56

8′h57

8′h59

8′h5A

8′h58

s2[11:0]

12′h010

12′h011

12′h010

12′h00E

12′h00D

12′h00B

12′h00A 12′h00C

s1[11:0]

12′h009

12′hFFA

12′hFFD

12′hFFA

12′hFFD

12′hFFA

12′hFFD

12′h006

s3[11:0]

12′h004

12′hFFE

12′h002

12′hFFE

12′h002

12′hFFE

12′h002

12′h006

out[12:0]

13′h001D

13′h0009

13′h000F

13′h0006

13′h000C

13′h0003

13′h0009

13′h0018

图 10 PID 控制仿真波形

ek[7:0]

8′h02

8′hFC

8′h05 8′hFE 8′h06 8′h08 8′hF9 8′h09 8′h06 8′hFD 8′h01 8′h03 8′h05 8′hFF

ek_2[7:0]

8′h09

8′hF5

8′h10 8′hF0 8′h0F 8′hFA 8′hEF

8′h1F

8′hED

8′hFA 8′h0D 8′hFE 8′h00 8′hF8

s3[11:0]

12′h024

12′hFD4 12′h040 12′hFC0 12′h03C 12′hFE8 12′hFBC 12′h07C 12′hFB4 12′hFE8 12′h034 12′hFF8 12′h000 2′hFE

图 9 微分模块的仿真

顶层文件的部分 Verilog HDL 代码如下:

//偏差模块的实例化引用;

piancha_control u1( .rk (rk),

.yk (yk),

.clk (clk),

的重要环节。 首先存储输入的参量 kp,ki,kd

以及给

定值 rk,然后根据采样信号进行数据采样得 yk,再由

各模块执行的先后顺序进行时序分配 ,完成 PID 控

制的功能。整个过程采用状态机设计。不同的分类规

则,状态机有不同的种类。 在实际的应用中,根据有

限状态机是否使用输入信号 ,通常划分为 Moore 型

和 Mealy 型两类状态机。 Moore 型的输出只与当前

的状态有关而与输入无关, 属于同步输出状态机;

Mealy 型的输出不仅与当前的状态有关, 还与当前

的输入有关,属于异步输出状态机。由于 Moore 型的

输出与当前的输入无关,因此当前输入产生的任何

效果将会延迟到下一个时钟周期 ,时钟导致状态的

变化才引起输出的改变,因而能有效避免毛刺现象

的发生。综合以上的分析,本文中采用 Moore 型有限

状态机实现时序的控制。

.reset(reset)

.en(en),

.ek(m1) );

//比例模块的实例化引用;

bili_control u2( .ek(m1),

.kp(kp),

reset(reset),

块的实例化引用;

.en(en),.ek_1( ), .s1(s1) );

.

.clk(clk),

//积 分 模

jifen_control u3( .ek(m1),

.ki(ki),

.clk(clk),

.

reset(reset),

.en(en), .s2(s2) );

//微分模块的实例化引用;

weifen_control u4(.ek(m1),

.kd(kd),

.clk(clk),

.reset(reset),

.en(en), .ek_2( ), .s3(s3) );

assign out=s1+s2+s3;

为了进一步提高控制性能, 在工程实践中还可

采用积分分离的办法,根据实际工况,人为设置一个

阈值 ε>0。 当|e(k)|>ε,即偏差较大时,采用 PD 控制,

避 免 较 大 的 超 调 ;当|e(k)|≤ε,即 偏 差 较 小 时 ,采 用

PID 控制,保证控制精度。

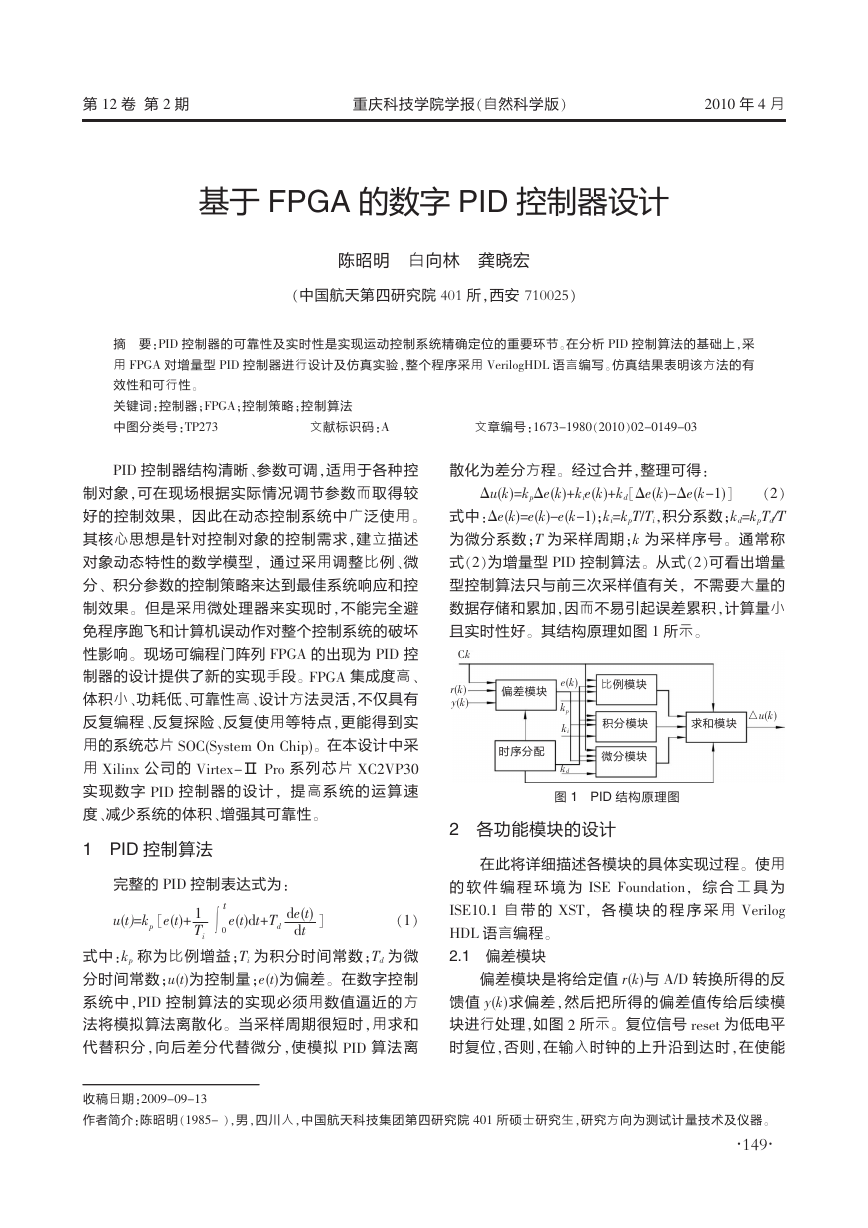

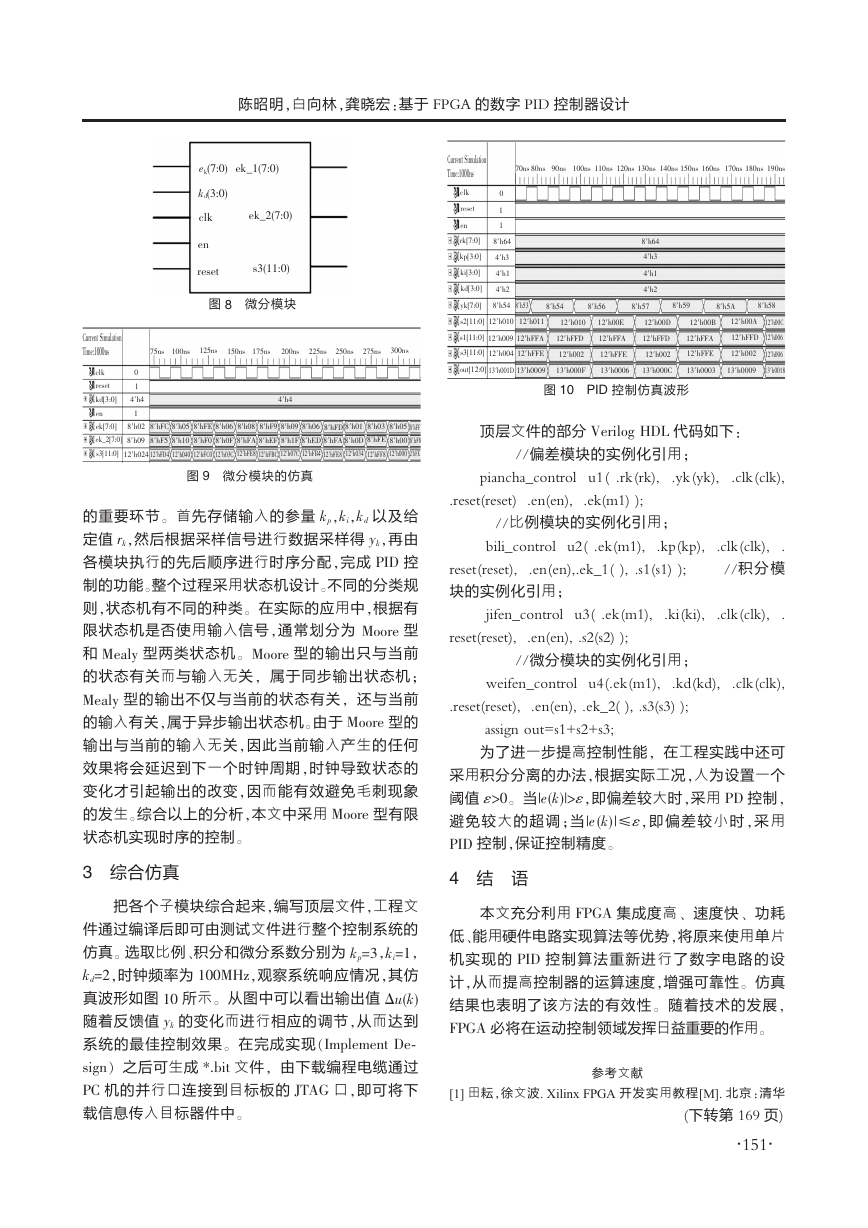

3 综合仿真

4 结 语

把各个子模块综合起来,编写顶层文件,工程文

件通过编译后即可由测试文件进行整个控制系统的

仿真。 选取比例、积分和微分系数分别为 kp=3,ki=1,

kd=2,时钟频率为 100MHz,观察系统响应情况,其仿

真波形如图 10 所示。 从图中可以看出输出值 Δu(k)

随着反馈值 yk

的变化而进行相应的调节,从而达到

系统的最佳控制效果。 在完成实现(Implement De-

sign) 之后可生成 *.bit 文件, 由下载编程电缆通过

PC 机的并行口连接到目标板的 JTAG 口,即可将下

载信息传入目标器件中。

本文充分利用 FPGA 集成度高、 速度快、 功耗

低、能用硬件电路实现算法等优势 ,将原来使用单片

机 实 现 的 PID 控 制 算 法 重 新进 行 了 数 字 电 路 的 设

计,从而提高控制器的运算速度,增强可靠性。 仿真

结果也表明了该方法的有效性 。 随着技术的发展,

FPGA 必将在运动控制领域发挥日益重要的作用。

参考文献

[1] 田耘,徐文波. Xilinx FPGA 开 发 实 用 教 程[M]. 北 京 :清 华

(下转第 169 页)

151· ·

�

唐银敏:基于相对密度的聚类算法研究

的时间复杂度为 O(n2);对 点 的 密 度 按 大 小 进 行 排

序 , 利 用 快 速 排 序 的 时 间 复 杂 度 为 O (nlgn); 聚 类

时,每次都是根据已排序的数据集从高密度往外扩

展进行聚类,所以时间复杂度为 O(n)。 所以整个算

法的时间复杂度为 O(n2)。

在基于密度的算法中,其时间主要消耗在计算

数据点的 ε 邻域,因此基于密度的聚类算法所消耗

的 时 间 应 该 与 算 法 中 计 算 ε 邻 域 的 数 据 点 数 成 正

比。 如果某一算法中参加计算 ε 邻域的数据点数越

多,则其消耗的时间也越多 ;反之 ,如果参加计算 ε

邻域的数据点数越少,则其消耗的时间也越少。 整

DBSCAN 聚类算法的时间复杂度为 O (n2), 其中 n

为数据集的规模。

5 结 语

本 文 主 要 介 绍 Red 算 法 的 基 本 思 想 及 具 体 实

现方法, 通过大量实验验证了 Red 算法的正确性。

根据 Red 算法的实验结果,对算法的时间复杂度进

行 了 分 析 , 先 通 过 4 个 均 匀 分 布 的 综 合 数 据 集 对

Red 算法进行测试, 然后在 5 个多密度的综合数据

集上进行实验,并给出了实验结果。对于大部分的数

据集,聚类结果显示出了较高的精度。

Clustering Algorithm Research Based on Relative Density

TANG Yin-min

(Nanyang Agriculture College,Nanyang 473000)

Abstract:In this paper, it introduces the clustering algorithm, and how to use the algorithm in details. The

principle of it is to get density of each point according to radius parameter, and arrange the point clustered by data

from large to small. Each time, it starts to cluster with the point with the largest density, and finds every points

which shall connect with the point as one class. In the residual points, find one point with the largest density,

followed by the above method, to cluster. At last, it finds each class, and puts the points not belong to every class

as outlier.

Key words:clustering analysis;relative density;clustering

(上接第 151 页)

大学出版社,2008.

[4] 夏宇闻. verilog 数字系统设计 教 程[M]. 北 京 :北 京 航 空 航

[2] 褚振勇,翁同木. FPGA 设计与应用[M]. 西安:西安电子科

天大学出版社,2005.

技大学出版社,2002.

[5] 谭晓. 数字 PID 控制器的实验研究[J]. 武汉 纺 织 工 学 院 学

[3] 袁俊泉,孙敏琪,曹瑞. Verilog HDL 数 字 系 统 设 计 及 其 应

报,1999,12(3):68-72.

用[M]. 西安:西安电子科技大学出版社,2002.

Design of Digital PID Controller Based on FPGA

CHEN Zhao-ming BAI Xiang-lin GONG Xiao-hong

(401 Institute of the Fourth Academy of CASC,Xi'an 710025)

Abstract:The reliability and real time of PID controller is very important to realize the precise orientation of a

motion control system. In the paper,based on the PID control algorithm,the increment-style PID controller is

designed and simulated by using field programmable gate array (FPGA),the whole program is written by Verilog

HDL language. The results proved that the method is available.

Key words:controller;field programmable gate array;PID;Verilog HDL

169· ·

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc