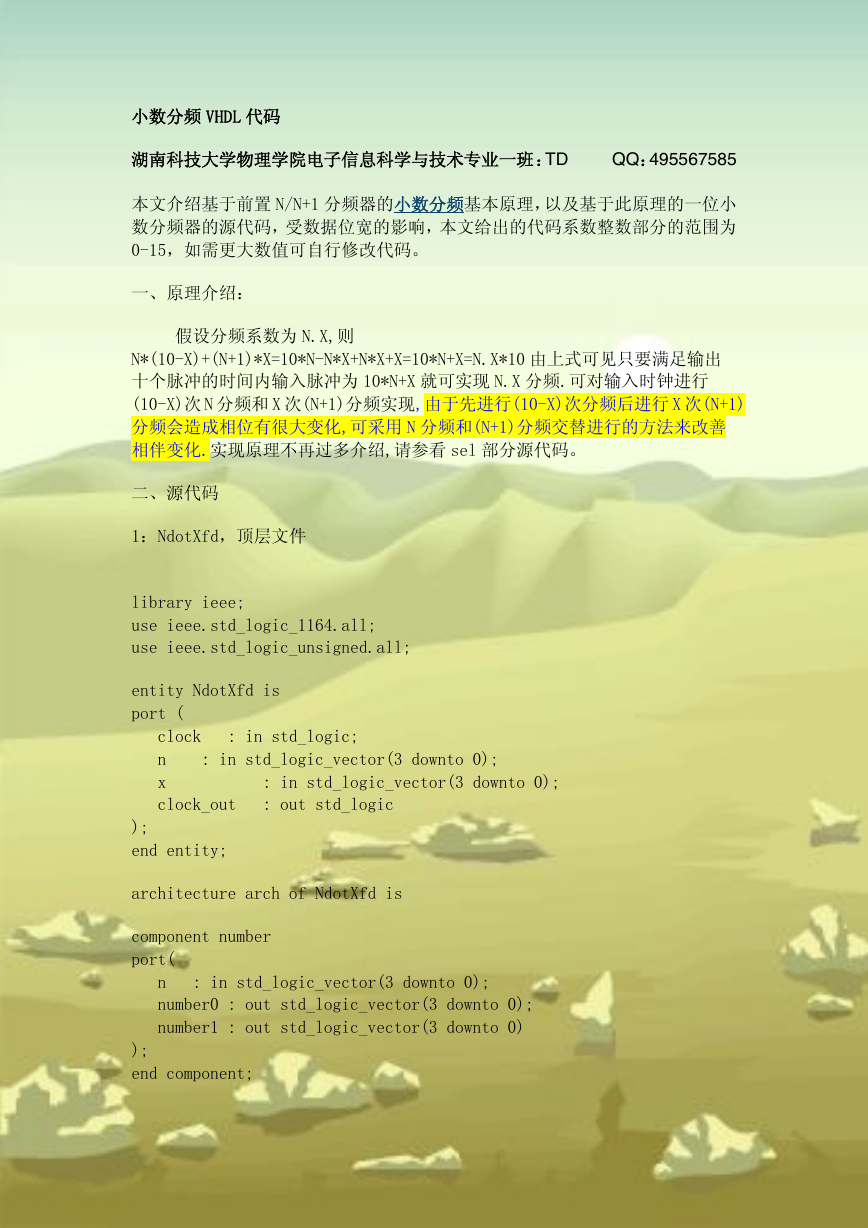

小数分频 VHDL 代码

湖南科技大学物理学院电子信息科学与技术专业一班:TD

QQ:495567585

本文介绍基于前置 N/N+1 分频器的小数分频基本原理,以及基于此原理的一位小

数分频器的源代码,受数据位宽的影响,本文给出的代码系数整数部分的范围为

0-15,如需更大数值可自行修改代码。

一、原理介绍:

假设分频系数为 N.X,则

N*(10-X)+(N+1)*X=10*N-N*X+N*X+X=10*N+X=N.X*10 由上式可见只要满足输出

十个脉冲的时间内输入脉冲为 10*N+X 就可实现 N.X 分频.可对输入时钟进行

(10-X)次 N 分频和 X 次(N+1)分频实现,由于先进行(10-X)次分频后进行 X 次(N+1)

分频会造成相位有很大变化,可采用 N 分频和(N+1)分频交替进行的方法来改善

相伴变化.实现原理不再过多介绍,请参看 sel 部分源代码。

二、源代码

1:NdotXfd,顶层文件

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity NdotXfd is

port (

: in std_logic;

: in std_logic_vector(3 downto 0);

clock

n

x

clock_out

: in std_logic_vector(3 downto 0);

: out std_logic

);

end entity;

architecture arch of NdotXfd is

component number

port(

: in std_logic_vector(3 downto 0);

n

number0 : out std_logic_vector(3 downto 0);

number1 : out std_logic_vector(3 downto 0)

);

end component;

�

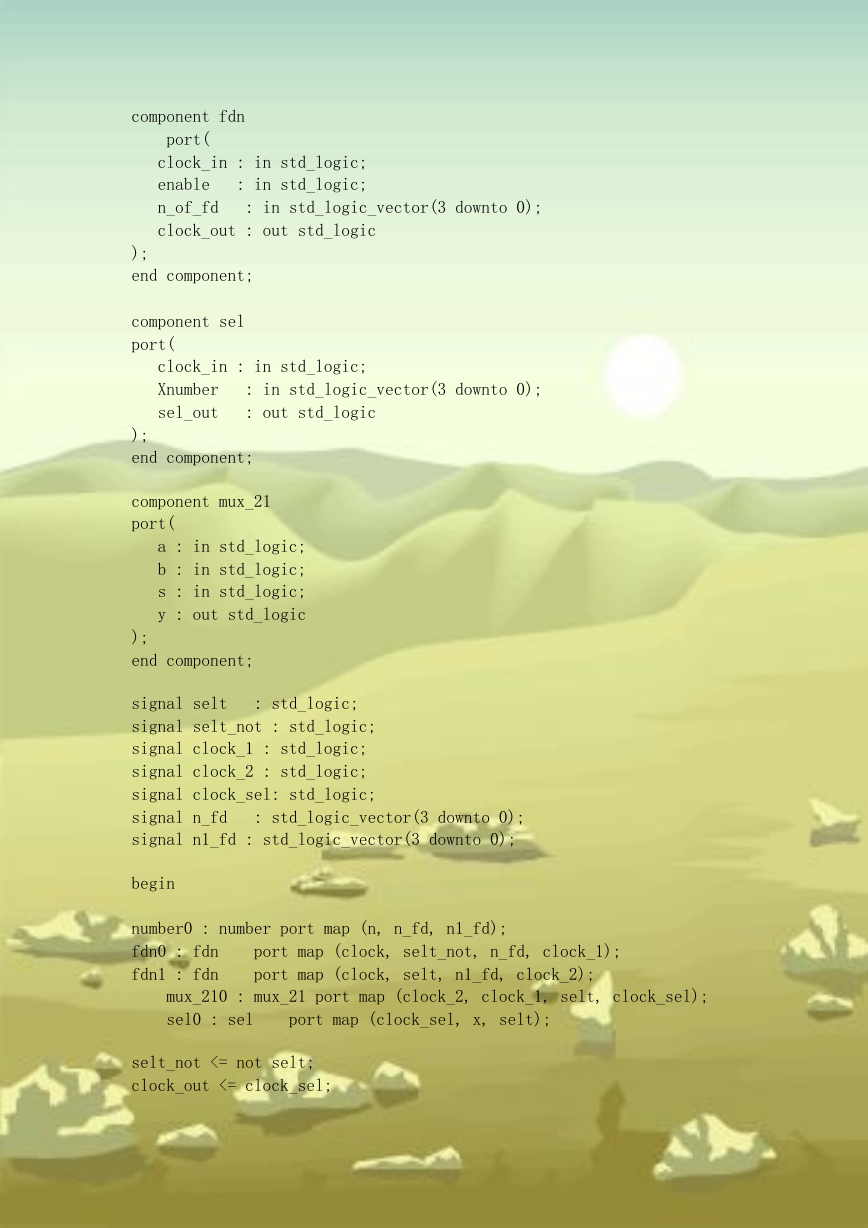

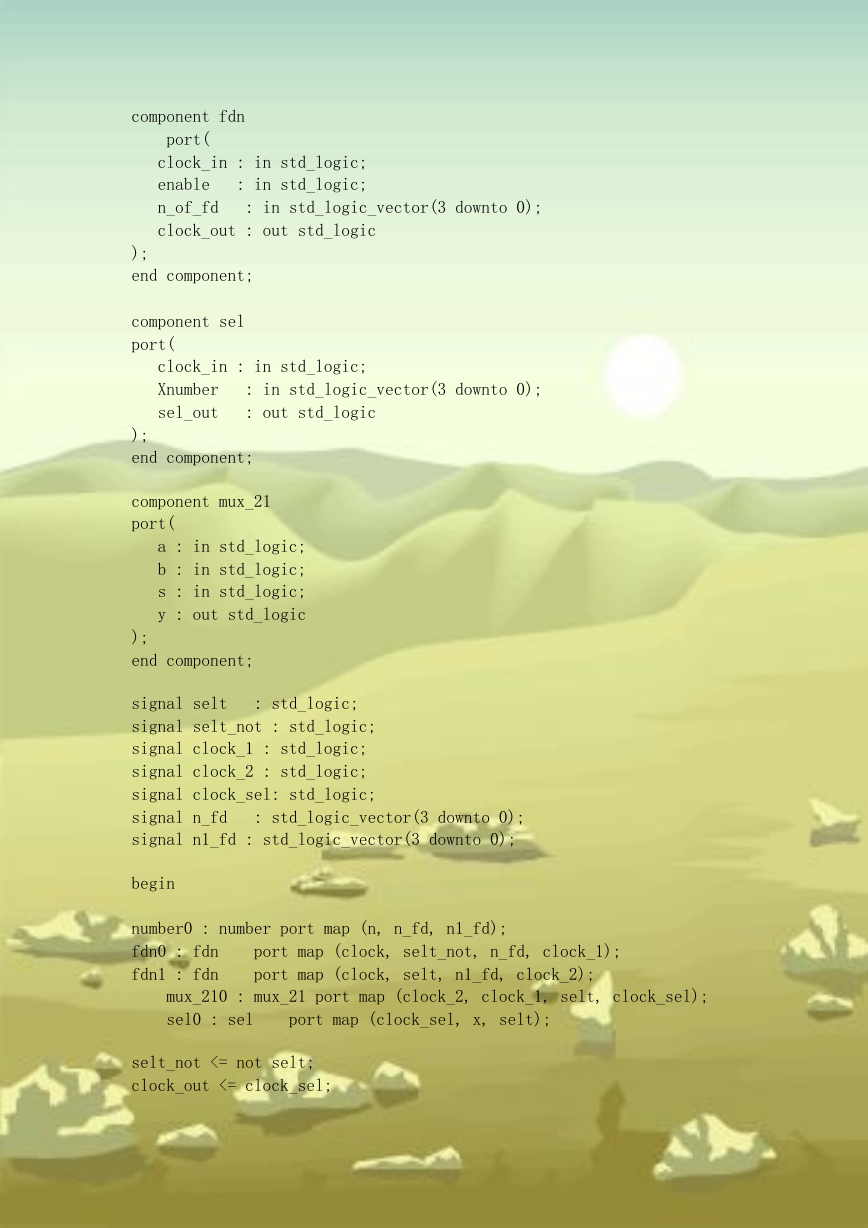

component fdn

port(

clock_in : in std_logic;

enable

: in std_logic;

n_of_fd

clock_out : out std_logic

: in std_logic_vector(3 downto 0);

);

end component;

component sel

port(

clock_in : in std_logic;

Xnumber

sel_out

: in std_logic_vector(3 downto 0);

: out std_logic

);

end component;

component mux_21

port(

a : in std_logic;

b : in std_logic;

s : in std_logic;

y : out std_logic

);

end component;

: std_logic;

signal selt

signal selt_not : std_logic;

signal clock_1 : std_logic;

signal clock_2 : std_logic;

signal clock_sel: std_logic;

signal n_fd

signal n1_fd : std_logic_vector(3 downto 0);

: std_logic_vector(3 downto 0);

begin

number0 : number port map (n, n_fd, n1_fd);

fdn0 : fdn

fdn1 : fdn

port map (clock, selt_not, n_fd, clock_1);

port map (clock, selt, n1_fd, clock_2);

mux_210 : mux_21 port map (clock_2, clock_1, selt, clock_sel);

sel0 : sel

port map (clock_sel, x, selt);

selt_not <= not selt;

clock_out <= clock_sel;

�

end arch;

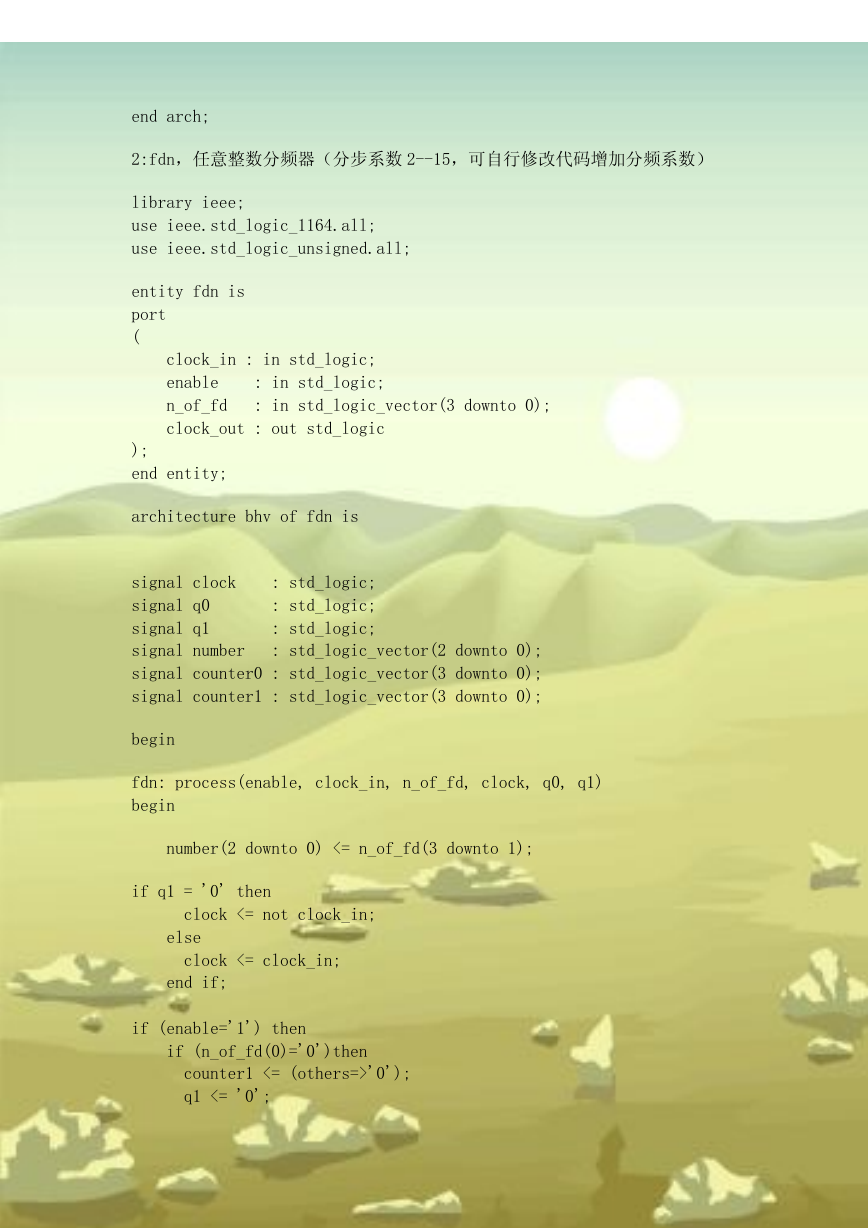

2:fdn,任意整数分频器(分步系数 2--15,可自行修改代码增加分频系数)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fdn is

port

(

clock_in : in std_logic;

enable

n_of_fd

clock_out : out std_logic

: in std_logic;

: in std_logic_vector(3 downto 0);

);

end entity;

architecture bhv of fdn is

: std_logic;

signal clock

: std_logic;

signal q0

: std_logic;

signal q1

signal number

: std_logic_vector(2 downto 0);

signal counter0 : std_logic_vector(3 downto 0);

signal counter1 : std_logic_vector(3 downto 0);

begin

fdn: process(enable, clock_in, n_of_fd, clock, q0, q1)

begin

number(2 downto 0) <= n_of_fd(3 downto 1);

if q1 = '0' then

clock <= not clock_in;

else

clock <= clock_in;

end if;

if (enable='1') then

if (n_of_fd(0)='0')then

counter1 <= (others=>'0');

q1 <= '0';

�

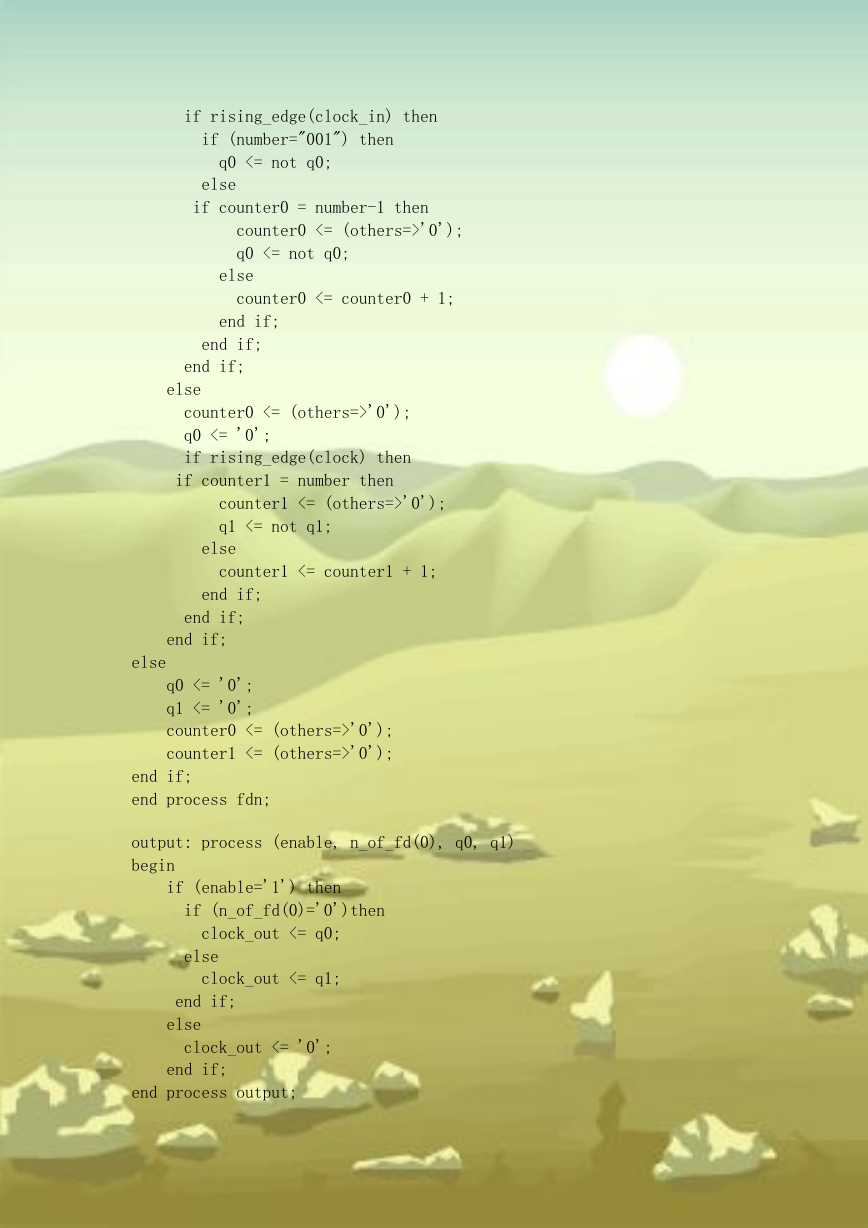

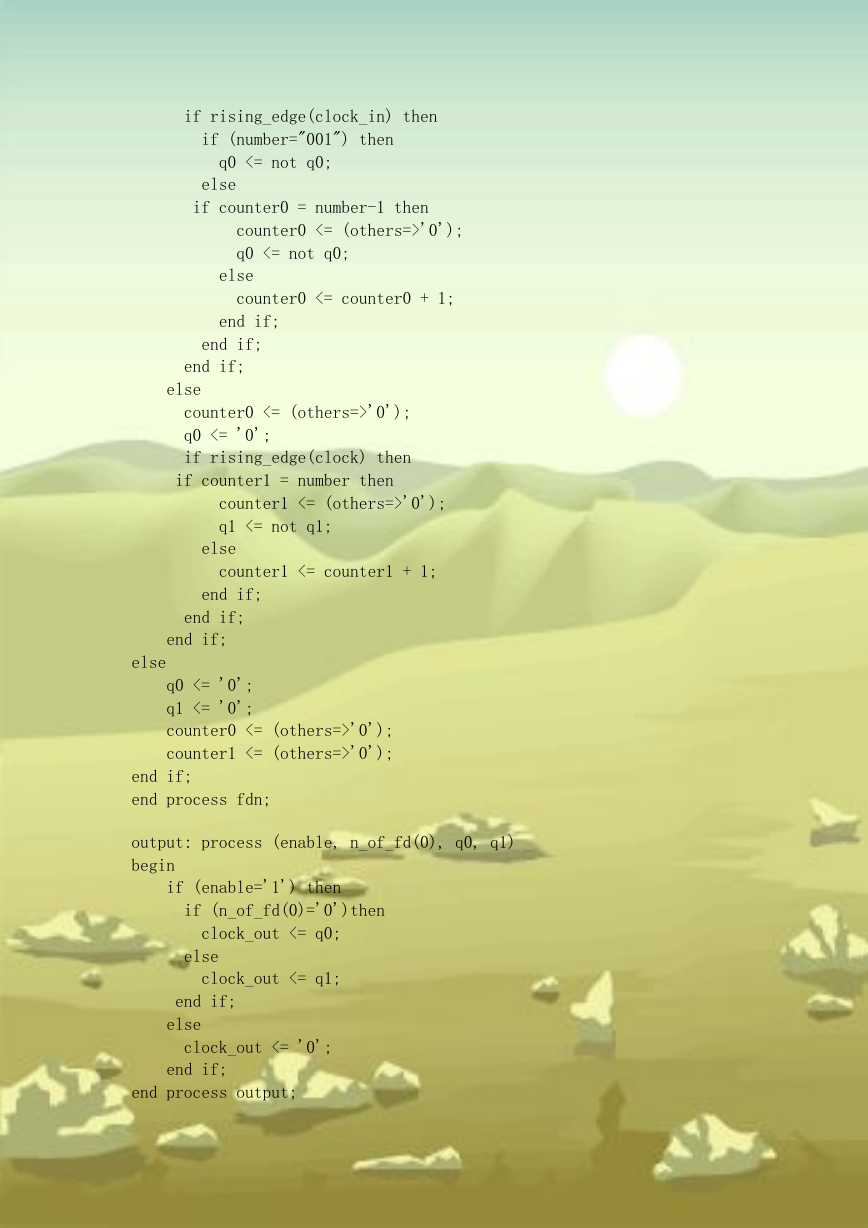

if rising_edge(clock_in) then

if (number="001") then

q0 <= not q0;

else

if counter0 = number-1 then

counter0 <= (others=>'0');

q0 <= not q0;

else

counter0 <= counter0 + 1;

end if;

end if;

end if;

else

counter0 <= (others=>'0');

q0 <= '0';

if rising_edge(clock) then

if counter1 = number then

counter1 <= (others=>'0');

q1 <= not q1;

else

counter1 <= counter1 + 1;

end if;

end if;

end if;

else

q0 <= '0';

q1 <= '0';

counter0 <= (others=>'0');

counter1 <= (others=>'0');

end if;

end process fdn;

output: process (enable, n_of_fd(0), q0, q1)

begin

if (enable='1') then

if (n_of_fd(0)='0')then

clock_out <= q0;

else

clock_out <= q1;

end if;

else

clock_out <= '0';

end if;

end process output;

�

end bhv;

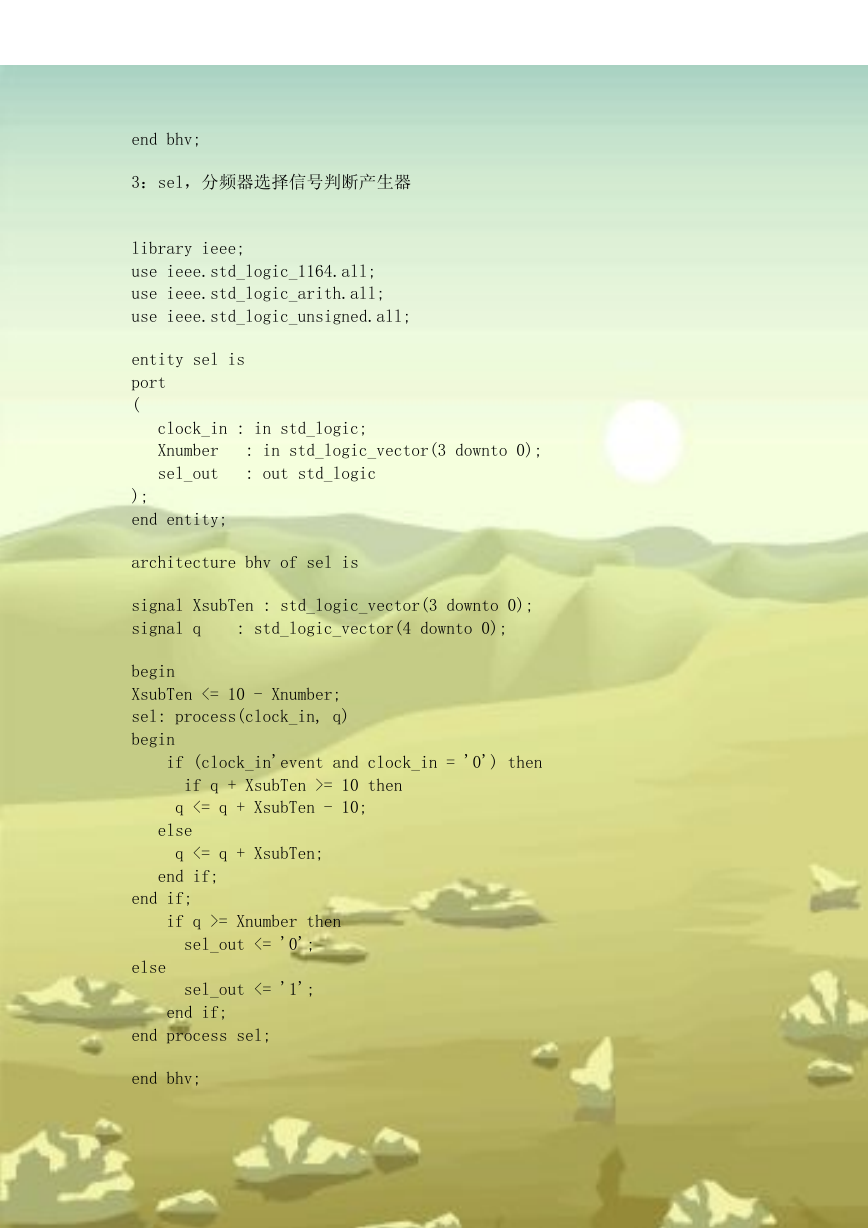

3:sel,分频器选择信号判断产生器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity sel is

port

(

clock_in : in std_logic;

Xnumber

sel_out

: in std_logic_vector(3 downto 0);

: out std_logic

);

end entity;

architecture bhv of sel is

signal XsubTen : std_logic_vector(3 downto 0);

signal q

: std_logic_vector(4 downto 0);

begin

XsubTen <= 10 - Xnumber;

sel: process(clock_in, q)

begin

if (clock_in'event and clock_in = '0') then

if q + XsubTen >= 10 then

q <= q + XsubTen - 10;

else

q <= q + XsubTen;

end if;

end if;

if q >= Xnumber then

sel_out <= '0';

else

sel_out <= '1';

end if;

end process sel;

end bhv;

�

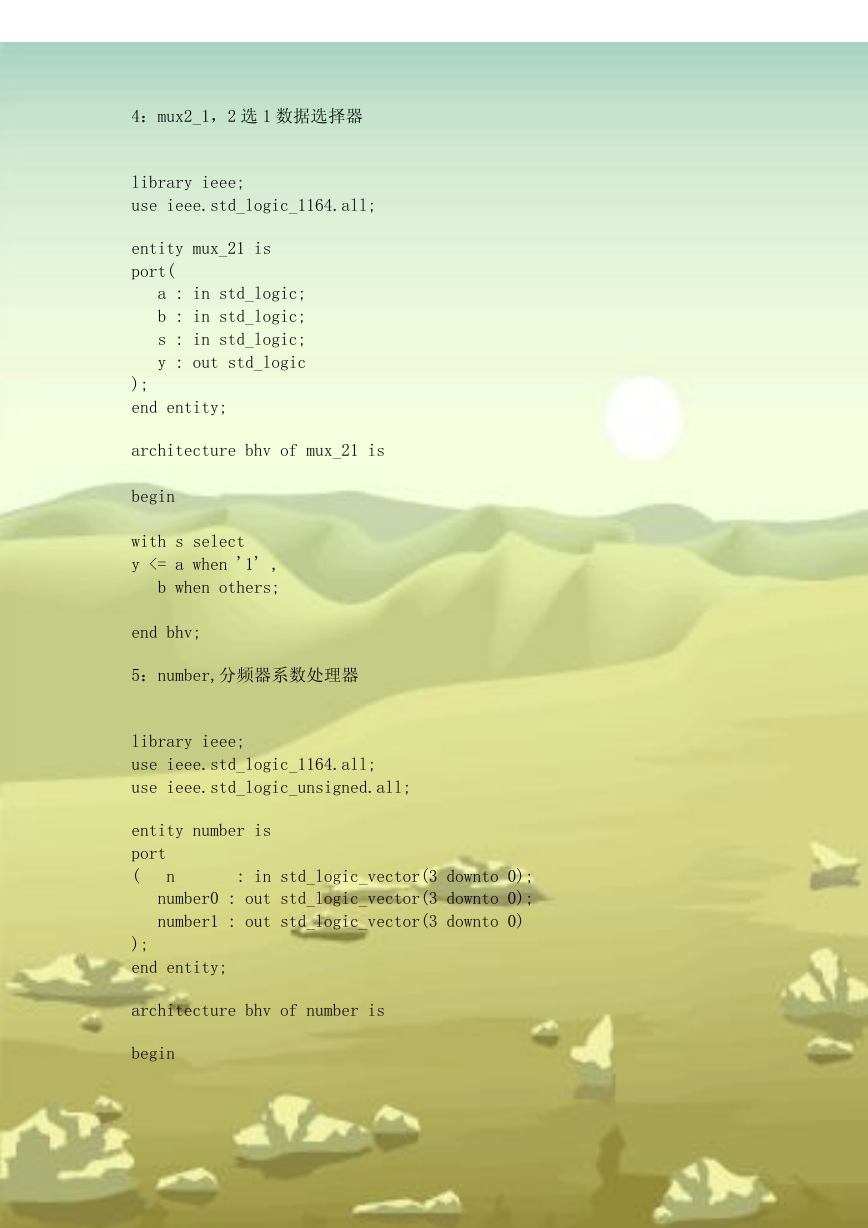

4:mux2_1,2 选 1 数据选择器

library ieee;

use ieee.std_logic_1164.all;

entity mux_21 is

port(

a : in std_logic;

b : in std_logic;

s : in std_logic;

y : out std_logic

);

end entity;

architecture bhv of mux_21 is

begin

with s select

y <= a when '1' ,

b when others;

end bhv;

5:number,分频器系数处理器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity number is

port

(

n

: in std_logic_vector(3 downto 0);

number0 : out std_logic_vector(3 downto 0);

number1 : out std_logic_vector(3 downto 0)

);

end entity;

architecture bhv of number is

begin

�

number0 <= n;

number1 <= n+1;

end bhv;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc