信 号 发 生 器

摘要

本系统由单片机控制模块、键盘模块、LCD 液晶屏模块、波形产生模块、波

形参数调整模块、幅度控制模块、输出功率放大模块、自制稳压电源组成。本系

统采用直接频率合成(DDFS)技术,由专门的 DDFS 芯片 AD9833 产生频率可预置

的正弦波,方波,三角波。采用宽带视频放大器 LT1253 对信号进行放大,较好的

拓展上限频率。由 DAC0832 内部的电阻分压网络实现幅度的步进可调。采用 OCL

功率放大器驱动 50 欧的负载。目前国际上信号发生器的生产走在前列的比如美

国泰克公司的 AWG5000 系列任意波形发生器,提供了通用的模拟和数字混合信

号发生功能,支持各种应用。而我们这个产品就目前国内水平来说,最大的优点

就在于频率稳定度高,频率的步进间隔可达 10HZ,。该系统输出的频率范围宽,

步进小,幅度和频率的精度高。

一、方案论证与比较

1、常见信号源制作方法

方案一:采用由晶体管、运放 IC 等通用器件制作,更多的则是用专门的函数

信号发生器 IC 产生。早期的函数信号发生器 IC,如 L8038、BA205、XR2207/2209

等,它们的功能较少,精度不高,频率上限只有 300kHz,无法产生更高频率的

信号,调节方式也不够灵活。而采用 MAX038 能产生多种波形,达到较高的频率,

且易于调试,但灵活性比较差,不能实现任意波形以及波形运算输出等智能化的

功能。

方案二:自行设计的基于 FPGA 芯片的解决方案,采用直接数字频率合成技术

(Direct Digital Frequency Synthesis 简称 DDS 或 DDFS)产生波形。 DDS 技

术的实现依赖于高速、高性能的数字器件。可编程逻辑器件 PLD 以其速度高、规

模大、可编程,以及有强大 EDA 软件支持等特性,十分适合实现 DDS 技术。但是

作为一个数字逻辑器件,竞争和冒险成为较为突出的问题,因此在使用时必须注

意毛刺的产生,清除及抗干扰,从而增大了电路和程序的复杂程度和可实施性。

方案三:利用专用直接数字合成(DDS)芯片 AD9833,能产生三角波、方波、

正弦波,并达到很高的频率。它以有别于其它频率合成方法的优越性能和特点成

为现代频率合成技术中的姣姣者。具体体现在相对带宽宽、频率转换时间短、频

率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程

和全数字化、控制灵活方便等方面,并具有极高的性价比。

本系统采用的核心芯片 AD9833 是 ADI 公司生产的一款低功耗、完全集成了

DDS 电路的可编程芯片,能够产生正弦波、三角波、方波。输出频率和相位都可

通过软件编程,易于调节,频率寄存器是 28 位的,主频时钟为 25MHz 时,精度

为 0.1Hz,主频时钟为 1MHz 时,精度可以达到 0.004Hz。

可以通过 3 线 SPI 接口将数据写入 AD9833,这 3 个串口的最高工作频

率 可 以 达 到 40MHz , 该 芯 片 采 用 10 引 脚 MSOP 型 表 面 贴 片 封 装 , 体 积 很

小。

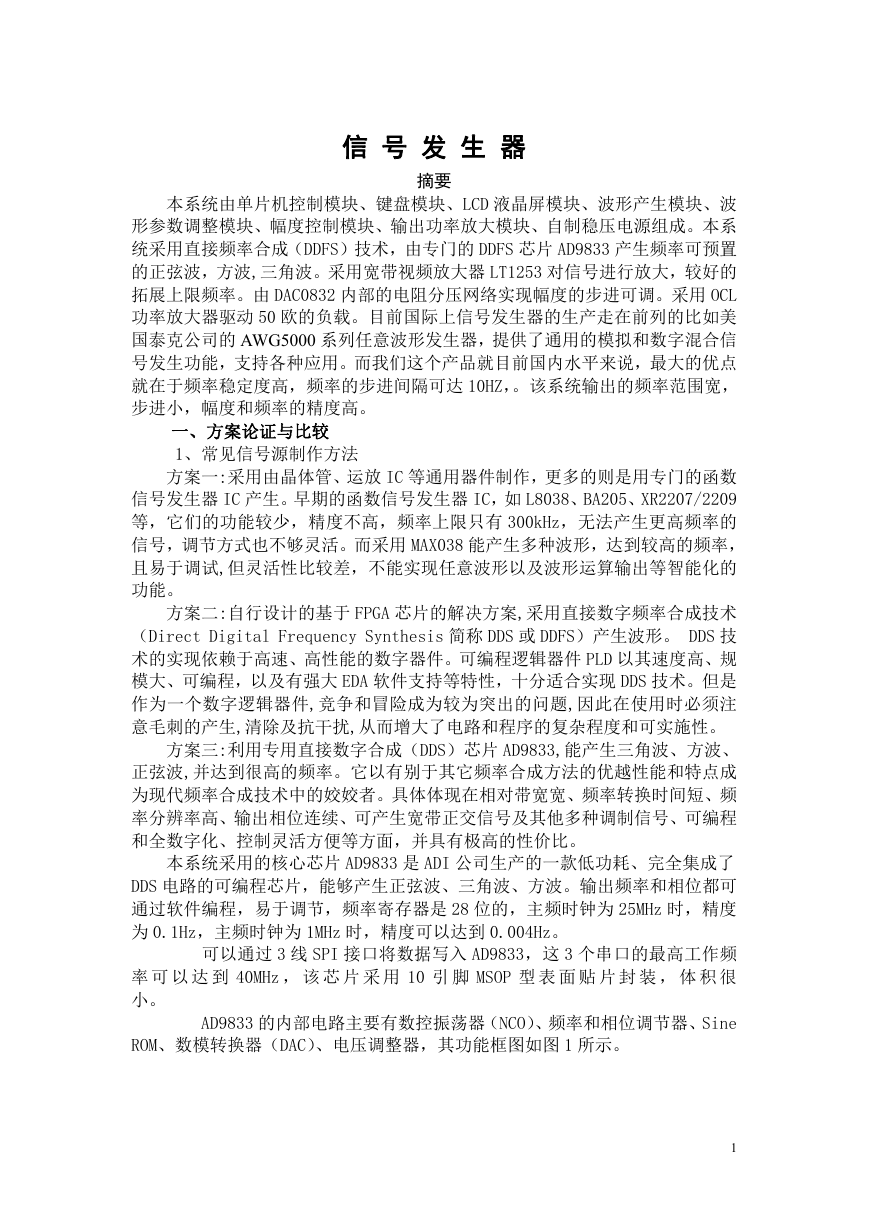

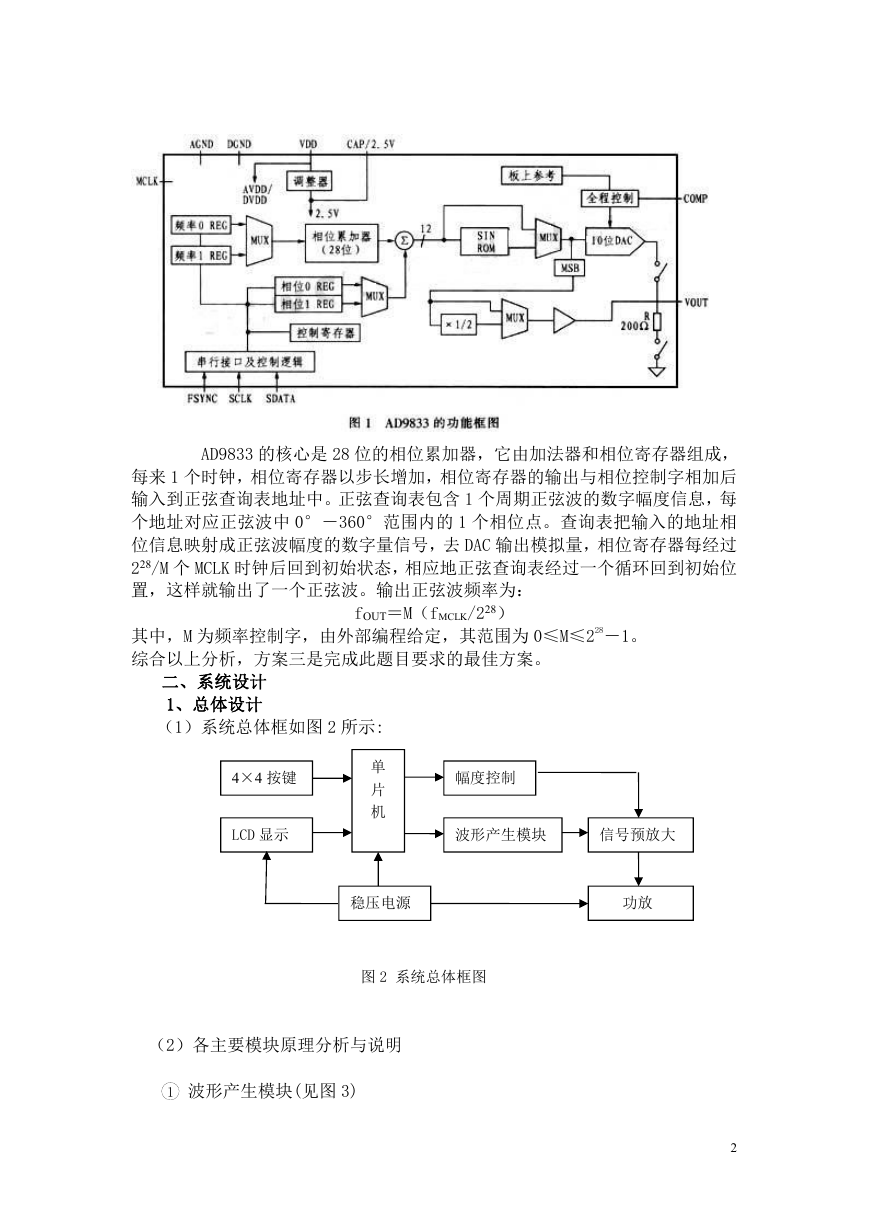

AD9833 的内部电路主要有数控振荡器(NCO)、频率和相位调节器、Sine

ROM、数模转换器(DAC)、电压调整器,其功能框图如图 1 所示。

1

�

AD9833 的核心是 28 位的相位累加器,它由加法器和相位寄存器组成,

每来 1 个时钟,相位寄存器以步长增加,相位寄存器的输出与相位控制字相加后

输入到正弦查询表地址中。正弦查询表包含 1 个周期正弦波的数字幅度信息,每

个地址对应正弦波中 0°-360°范围内的 1 个相位点。查询表把输入的地址相

位信息映射成正弦波幅度的数字量信号,去 DAC 输出模拟量,相位寄存器每经过

228/M 个 MCLK 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位

置,这样就输出了一个正弦波。输出正弦波频率为:

其中,M 为频率控制字,由外部编程给定,其范围为 0≤M≤228-1。

综合以上分析,方案三是完成此题目要求的最佳方案。

fOUT=M(fMCLK/228)

二、系统设计

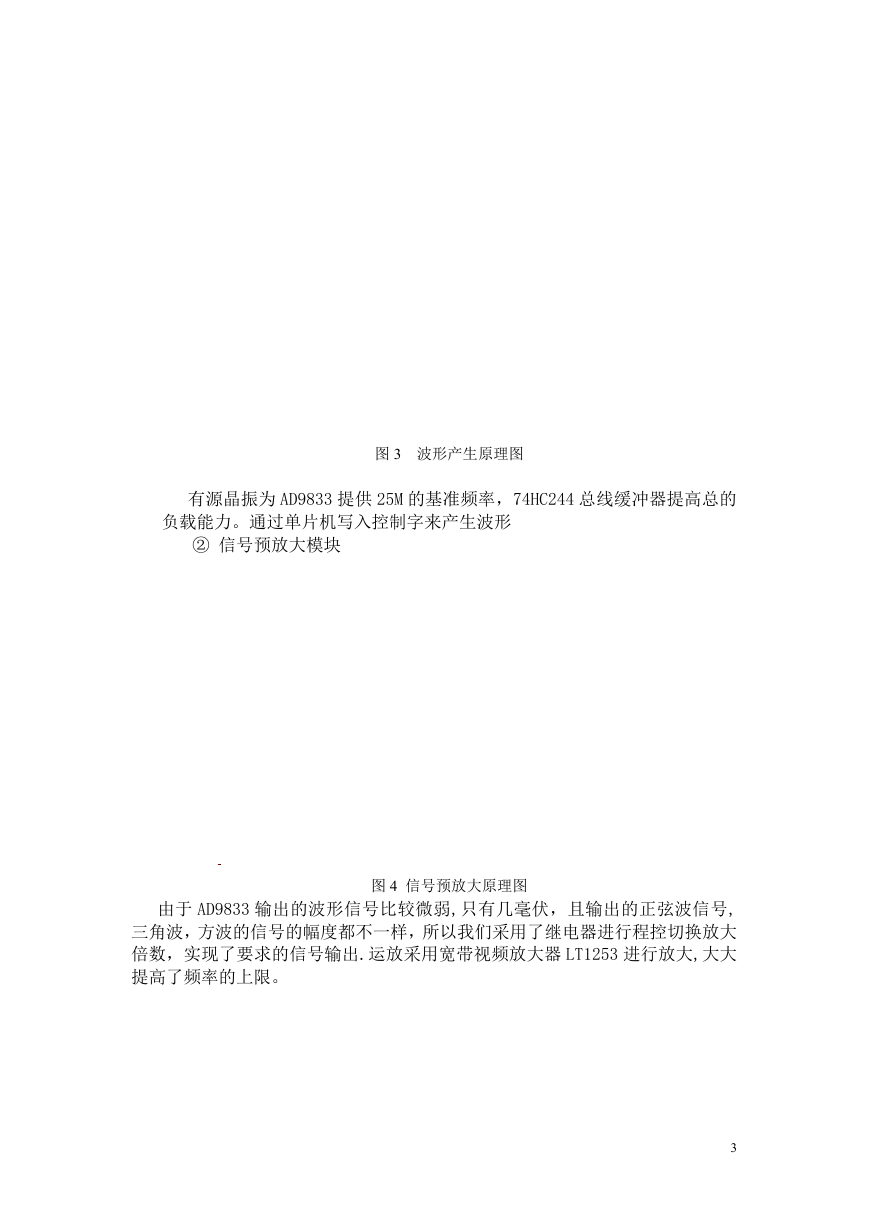

1、总体设计

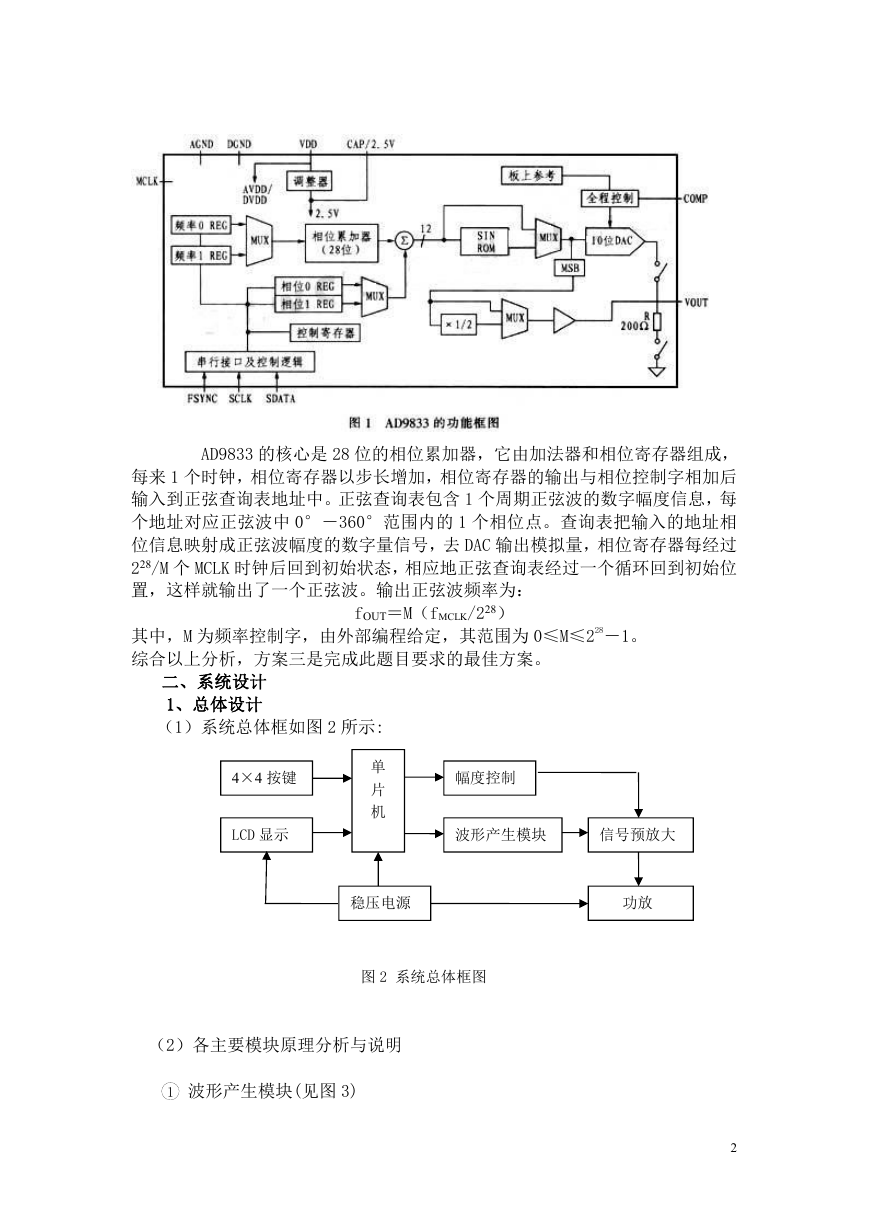

(1)系统总体框如图 2 所示:

4×4 按键

单

片

机

幅度控制

LCD 显示

波形产生模块

信号预放大

稳压电源

功放

图 2 系统总体框图

(2)各主要模块原理分析与说明

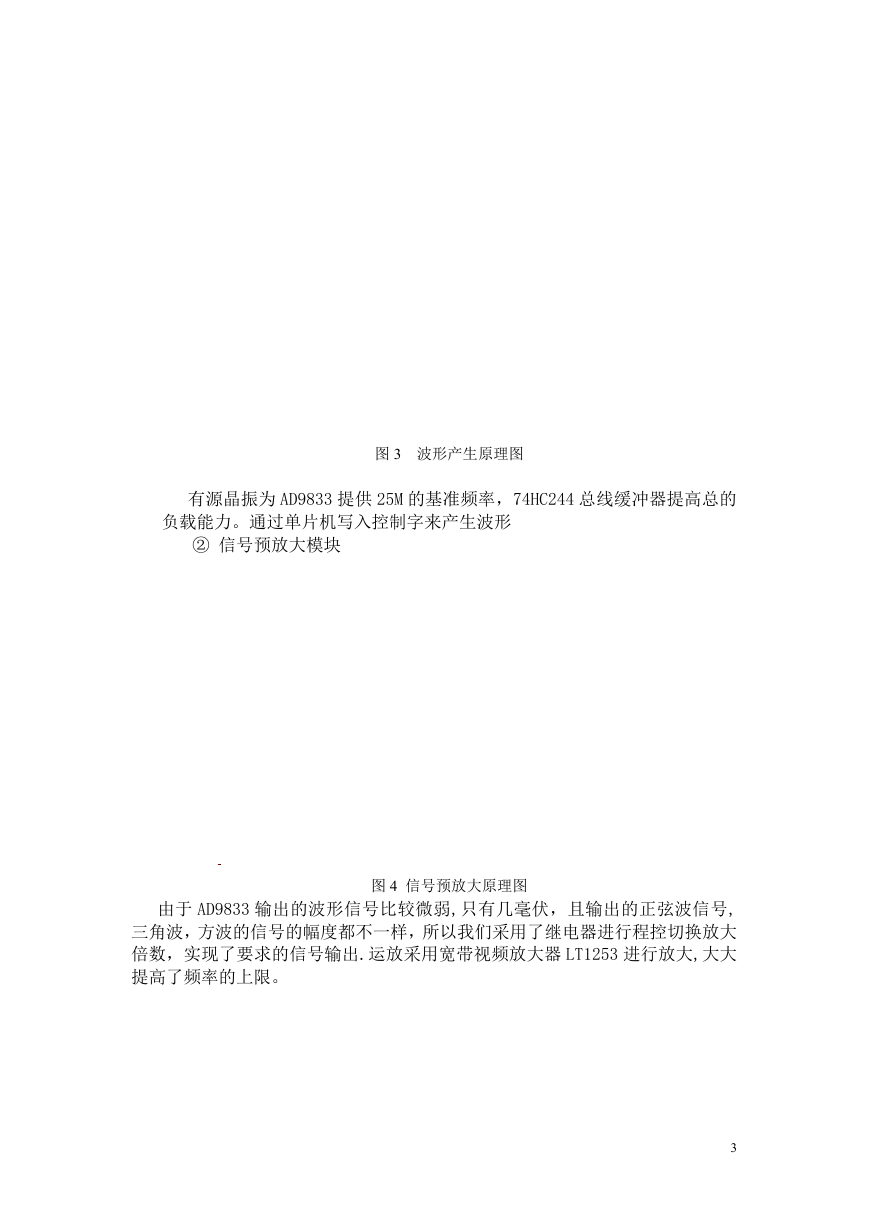

1 波形产生模块(见图 3)

2

�

DGND

图 3 波形产生原理图

有源晶振为 AD9833 提供 25M 的基准频率,74HC244 总线缓冲器提高总的

负载能力。通过单片机写入控制字来产生波形

3

5

② 信号预放大模块

7

9

12

14

16

18

2Y4

2Y3

2Y2

2Y1

1Y4

1Y3

1Y2

1Y1

SN74LS244N

10

19

1

17

15

13

11

8

6

4

2

GND

2OE

1OE

2A4

2A3

2A2

2A1

1A4

1A3

1A2

1A1

U3

Header 3

1

2

3

JP1

VCC

20

+5

DGND

DGND

5

4

3

2

1

0.1UF

C3

AD9833_BIG

MCLK

DGND

CAP

VDD

COMP

SDATA

SCLK

FSYNC

AGND

VOUT

U2

DGND

6

7

8

9

10

SIN

C2

0.1UF

10uF

C6

0.1UF

C4

DGND

+5

有源晶振

GND

CLK

NC

VCC

U1

2

1

3

4

0.1UF

C1

图 4 信号预放大原理图

由于 AD9833 输出的波形信号比较微弱,只有几毫伏,且输出的正弦波信号,

三角波,方波的信号的幅度都不一样,所以我们采用了继电器进行程控切换放大

倍数,实现了要求的信号输出.运放采用宽带视频放大器 LT1253 进行放大,大大

提高了频率的上限。

SIN

N

P

10K

N

1

R6

LT1253

U6

N

10K

P

R5

N

2

9012

Q1

9012

Q2

P

P1

3 4

1

2

-12

5

6

8

1K

1K

R4

1

3

7

4

2

3

2

1

R4

7

8

6

5

LT1253

U4

RP1

4.7K-2W

+12

1N4148

D1

5

6

1

2

DC5V-SHG

4

3

K1

NPN1

5K

R2

20P

C5

12

JP2

Header 2

+5

1N4148

D2

DC5V-SHG

2

4

3

5

NPN2

R3

6

R1

1

K2

100K

100K

3

�

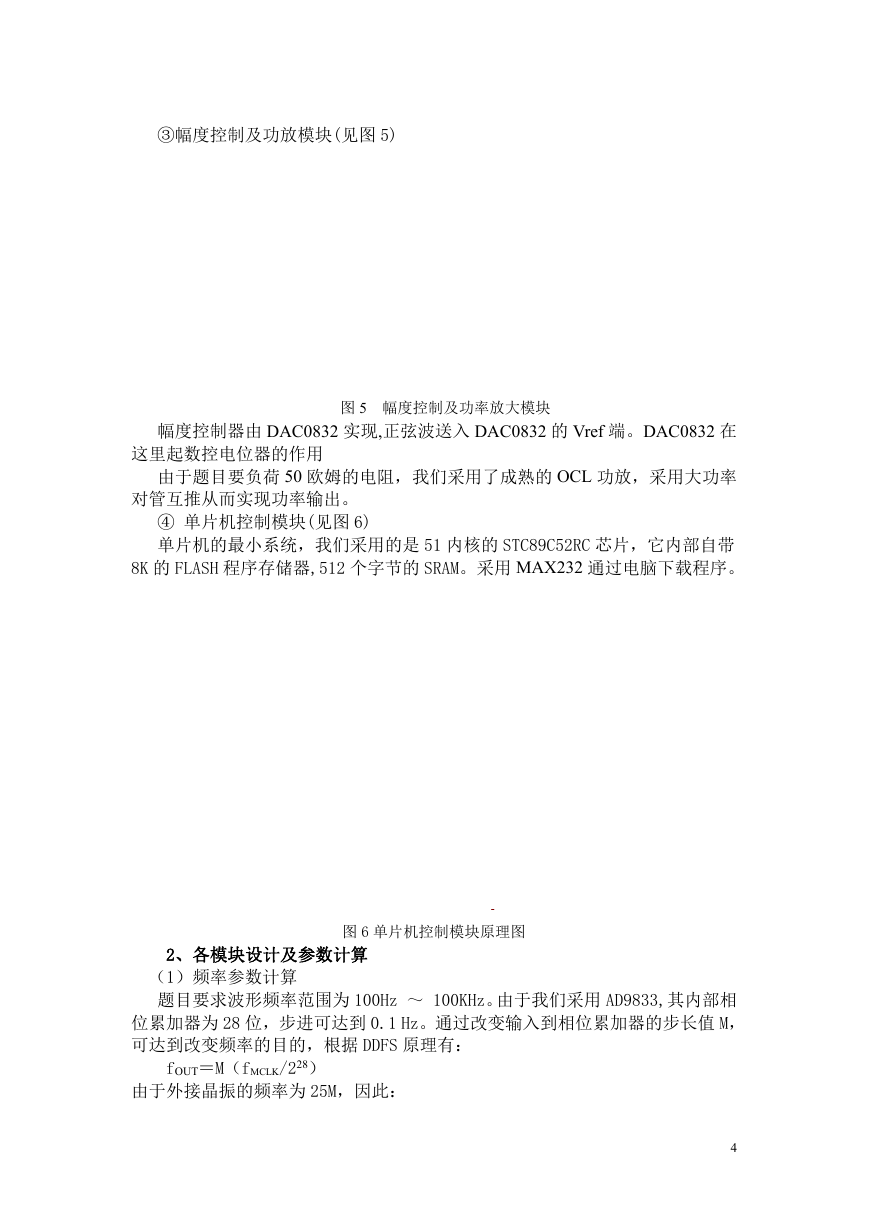

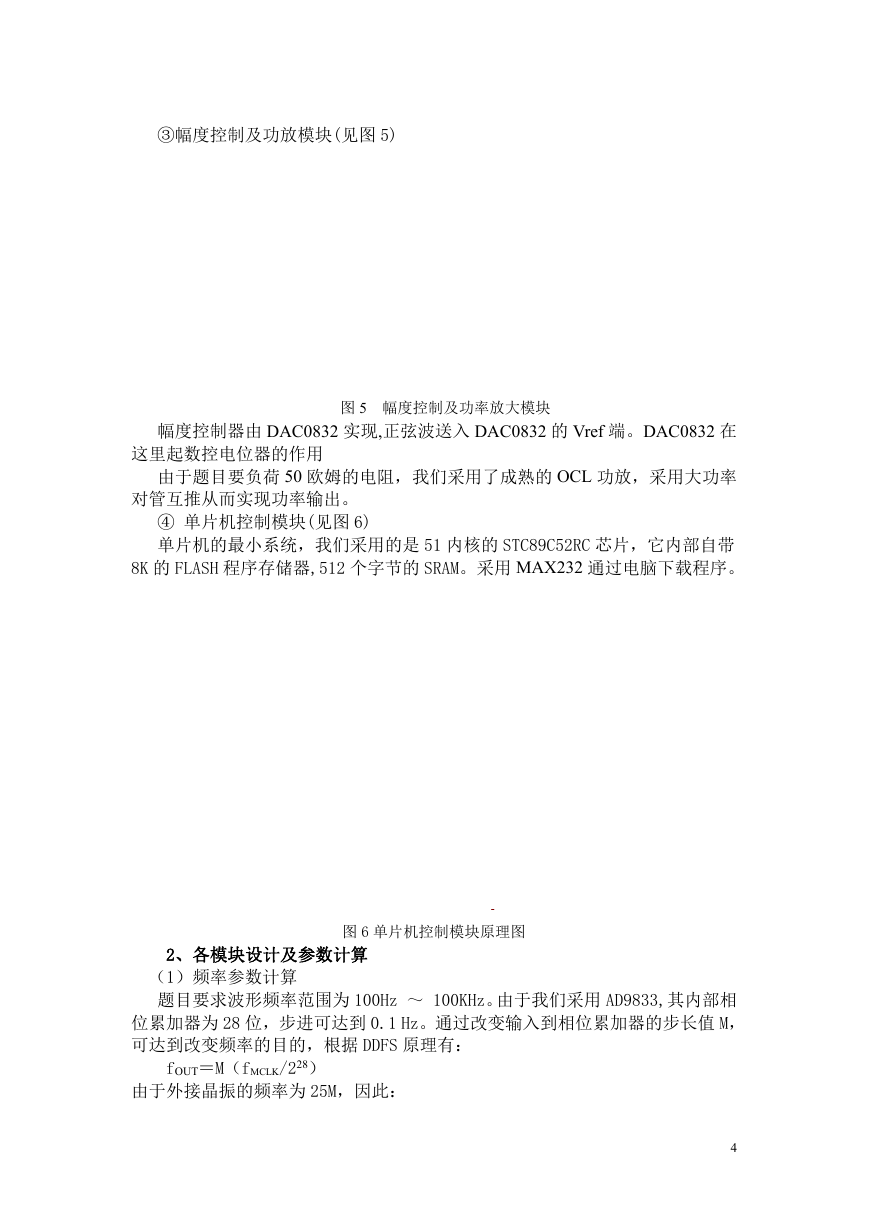

③幅度控制及功放模块(见图 5)

SINGEL

DAC0832LCJ

图 5 幅度控制及功率放大模块

-12

幅度控制器由 DAC0832 实现,正弦波送入 DAC0832 的 Vref 端。DAC0832 在

4

8

这里起数控电位器的作用

由于题目要负荷 50 欧姆的电阻,我们采用了成熟的 OCL 功放,采用大功率

12

4

3

1

7

A1360

U4

50

R4

-12

10K

R2

U3B

100K

R3

11

对管互推从而实现功率输出。

2

8

2

6

5

1

TL082

U3A

JP3

④ 单片机控制模块(见图 6)

单片机的最小系统,我们采用的是 51 内核的 STC89C52RC 芯片,它内部自带

8K 的 FLASH 程序存储器,512 个字节的 SRAM。采用 MAX232 通过电脑下载程序。

1N4148

D2

1N4148

D1

TL082

0.1uF

RFB

+12

9

C3432

U2

DI7

DI6

DI5

DI4

DI3

DI2

DI1

DI0

13

14

15

16

4

5

6

7

GND

10

GND

3

XFER

17 WR2

18

WR1

2

CS

1

VREF

8

U1

IOUT2

IOUT1

ILE

VDD

1

2

3

4

5

6

7

8

P

P1

19

20

C1

+5

10K

R1

+12

图 6 单片机控制模块原理图

2、各模块设计及参数计算

(1)频率参数计算

题目要求波形频率范围为 100Hz ~ 100KHz。由于我们采用 AD9833,其内部相

C7

MAX232CPE

位累加器为 28 位,步进可达到 0.1 Hz。通过改变输入到相位累加器的步长值 M,

可达到改变频率的目的,根据 DDFS 原理有:

R2OUT

T2IN

10uF

C5

9

10

RST

16

9

+5

VCC

V1+

V-

STC89C512RC

GND

XTAL2

XTAL1

20P

C8

20P

20

18

6M

Y1

19

+5

10uF

C6

S18

10K

R4

12

11

13

14

8

7

D1

D2

D3

D4

C8

C7

C6

C5

C4

C3

C2

C1

(RXD)P3.0

(TXD)P3.1

P3.2(INT0)

P3.3(INT1)

P1.7(SCK)

P1.6(MISO)

P1.5(MOSI)

P1.4

P1.3

P1.2

P1.1

P1.0

10

11

12

13

8

7

6

5

4

3

2

1

(A15)P2.7

(A14)P2.6

(A13)P2.5

(A12)P2.4

(A11)P2.3

(A10)P2.2

(A9)P2.1

(A8)P2.0

PSEN

ALE/PROG

P3.7(RD)

P3.6(WR)

P3.5(T1)

P3.4(T0)

(AD7)P0.7

(AD6)P0.6

(AD5)P0.5

(AD4)P0.4

(AD3)P0.3

(AD2)P0.2

(AD1)P0.1

(AD0)P0.0

EA/VPP

VCC

28

27

26

25

24

23

22

21

29

30

17

16

15

14

32

33

34

35

36

37

38

39

31

40

A1

A2

A3

A4

A5

A6

A7

A8

D8

D7

D6

D5

B8

B7

B6

4

B5

B4

B3

B2

B1

10uF

C4

2

6

fOUT=M(fMCLK/228)

D Connector 9

15

5

R1OUT

T1IN

由于外接晶振的频率为 25M,因此:

R1IN

T1OUT

R2IN

T2OUT

GND

C2-

10uF

C2

10uF

C3

C2+

C1-

C1+

11

4

3

1

U4

1

6

2

7

3

8

4

9

5

10

J3

�

M = (228 × fOUT)/ 25×106 ≈ 10.73 fOUT

根据要输出的频率可以算出 M 值

(2)幅度步进计算

幅度控制器由 DAC0832 控制,利用其内部的电阻分压网络,将其作为数控电

位器使用。将 AD9833 的输出波形作为 DAC0832 的基准电压源输入,其输出波形

将为 V=(N/256)×Vin 其中 N 为单片机的输入幅度控制字。我们采用此方法,

通过一个简单的电阻分压网络调整运放输出峰-峰值,再送入 DAC0832 由单片机

控制其幅度实现步进 0.1V 峰-峰值调整

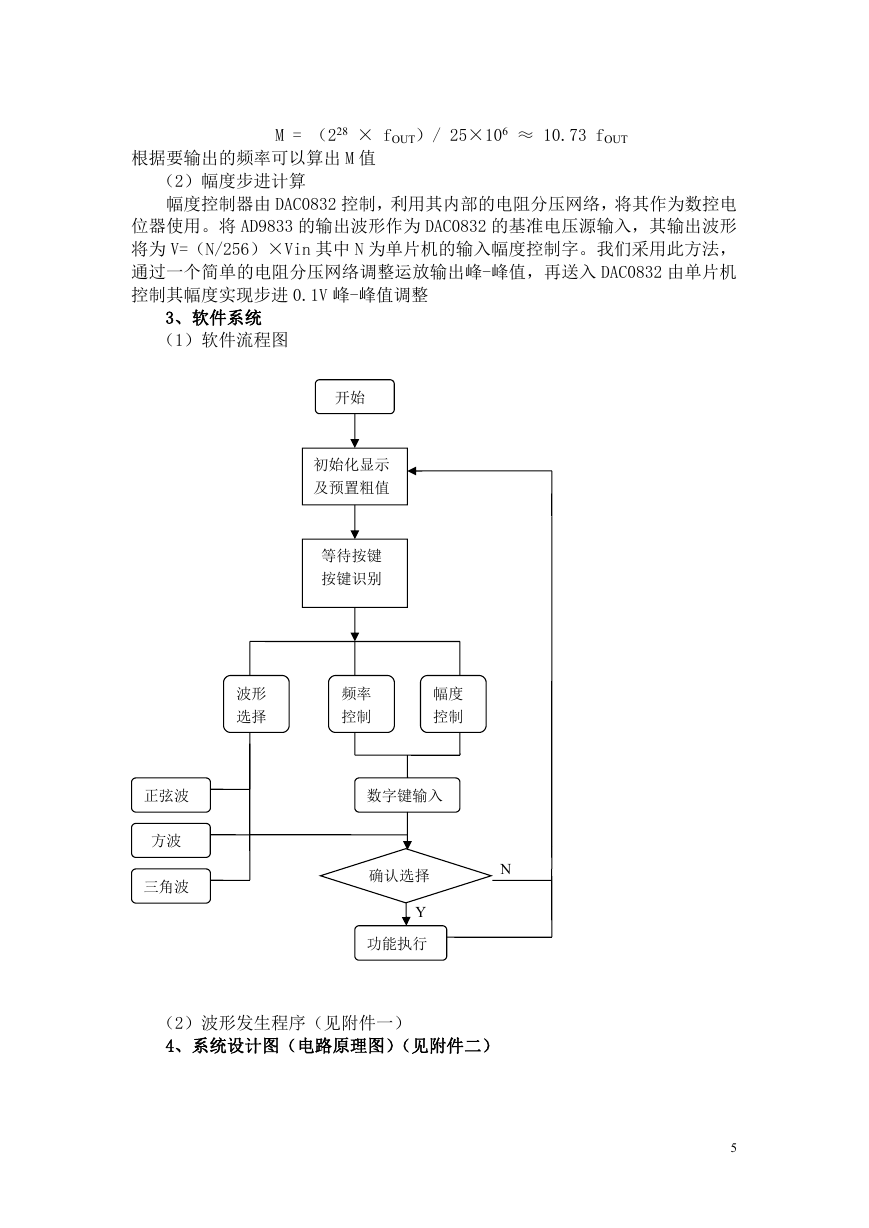

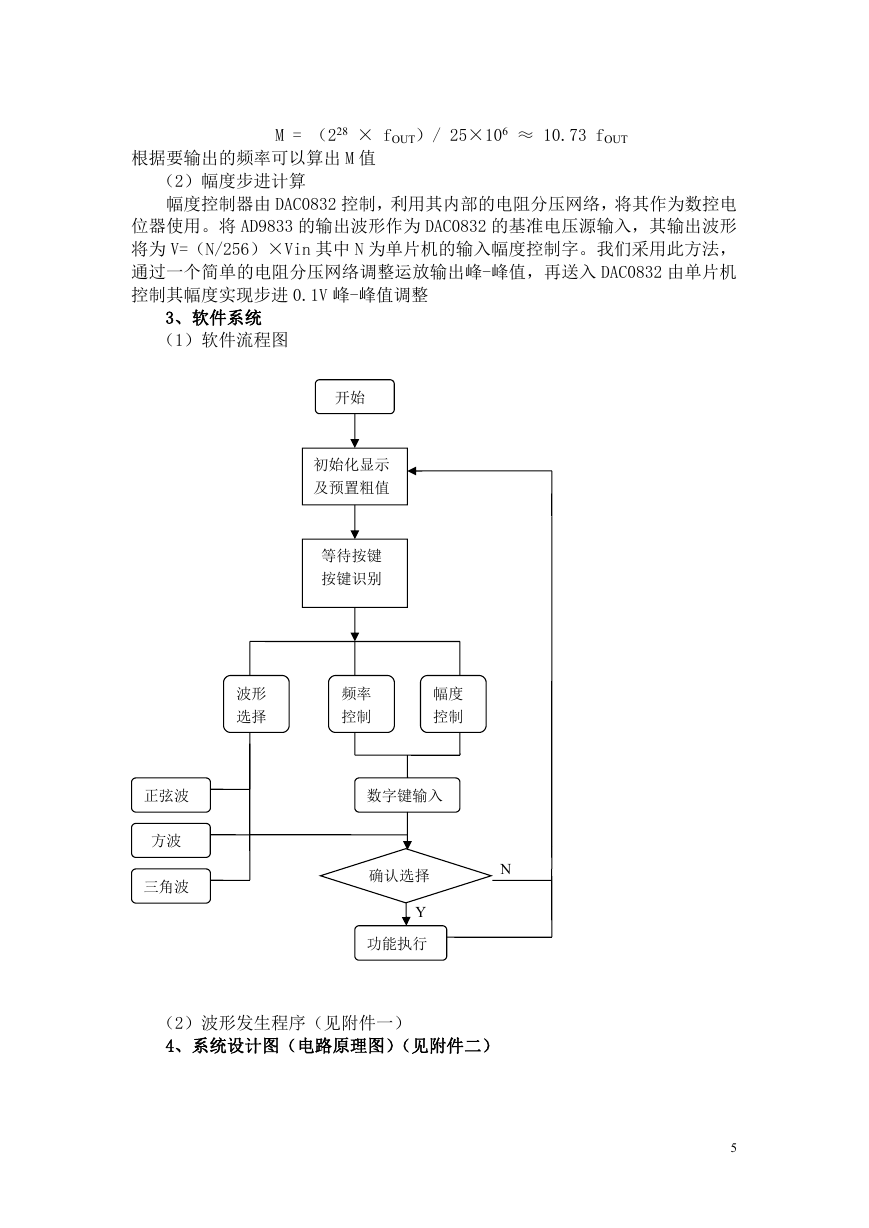

3、软件系统

(1)软件流程图

开始

初始化显示

及预置粗值

等待按键

按键识别

波形

选择

频率

控制

幅度

控制

正弦波

方波

三角波

数字键输入

确认选择

Y

功能执行

N

(2)波形发生程序(见附件一)

4、系统设计图(电路原理图)(见附件二)

5

�

三、指标测试

1、测试仪器

模拟示波器:PNG9060

函数发生/记数器:PNG1640-02

万用表:CEM DT-991L

存储示波器:CALTEK CA1102

交流有效值测试表:HP34401

2、指标测试

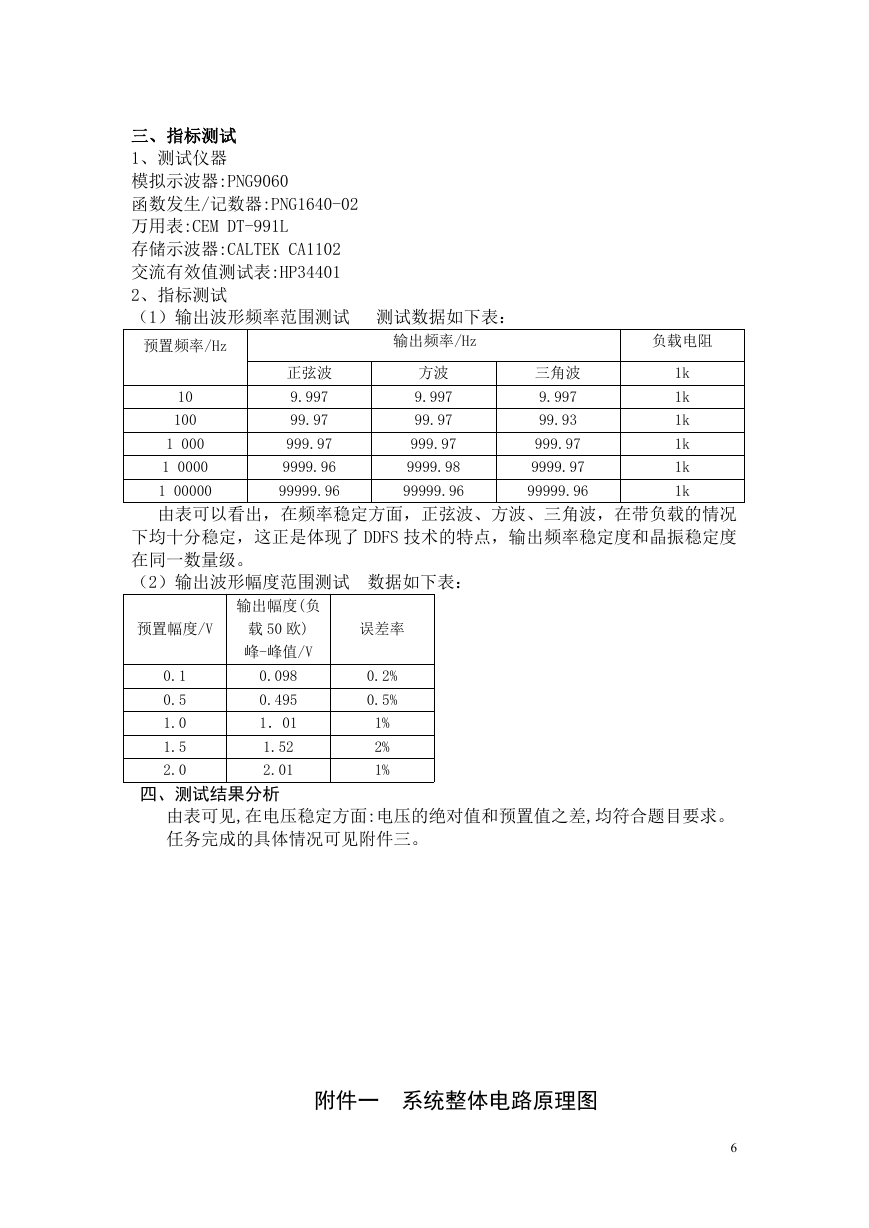

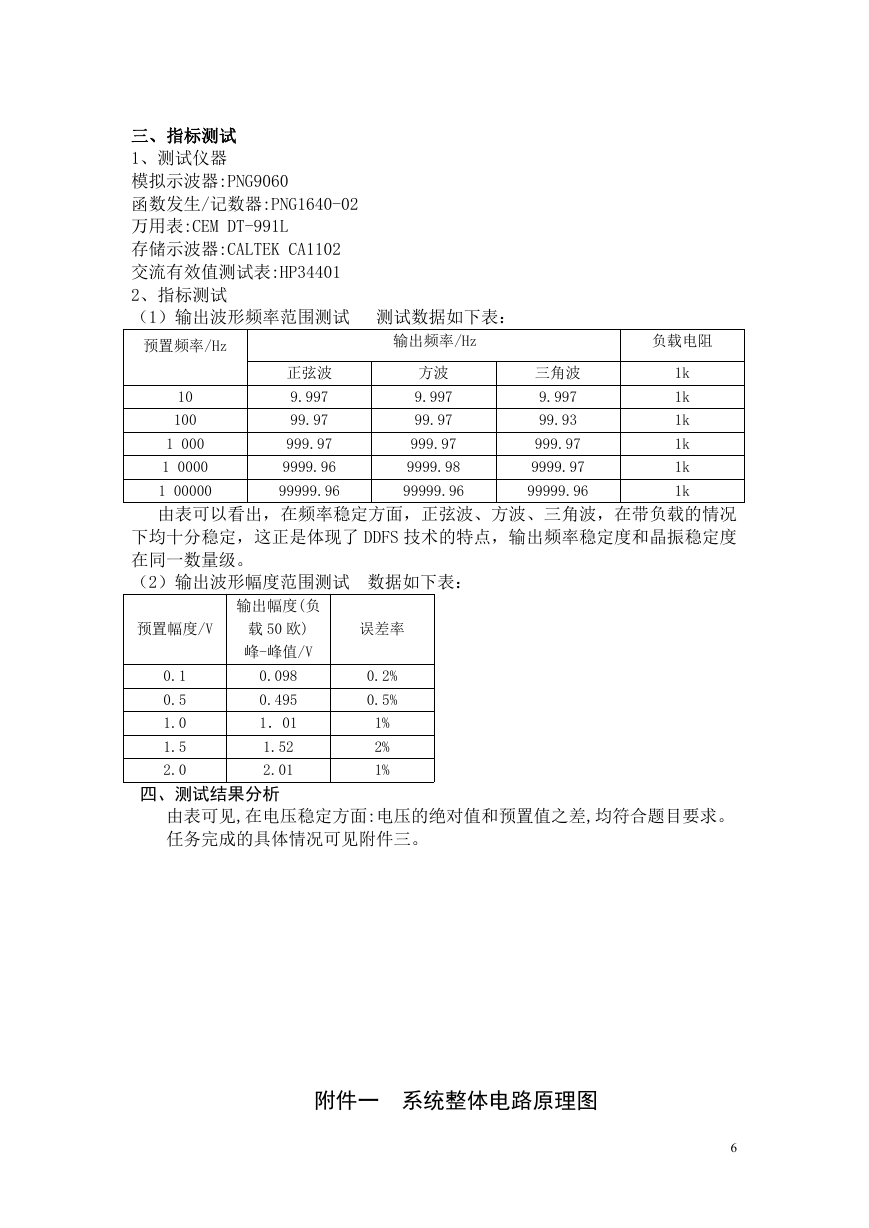

(1)输出波形频率范围测试 测试数据如下表:

预置频率/Hz

输出频率/Hz

负载电阻

10

100

1 000

1 0000

正弦波

9.997

99.97

999.97

9999.96

方波

9.997

99.97

999.97

9999.98

三角波

9.997

99.93

999.97

9999.97

1k

1k

1k

1k

1k

99999.96

99999.96

1 00000

由表可以看出,在频率稳定方面,正弦波、方波、三角波,在带负载的情况

下均十分稳定,这正是体现了 DDFS 技术的特点,输出频率稳定度和晶振稳定度

在同一数量级。

(2)输出波形幅度范围测试 数据如下表:

99999.96

1k

预置幅度/V

输出幅度(负

载 50 欧)

峰-峰值/V

0.1

0.5

1.0

1.5

2.0

0.098

0.495

1.01

1.52

2.01

四、测试结果分析

误差率

0.2%

0.5%

1%

2%

1%

由表可见,在电压稳定方面:电压的绝对值和预置值之差,均符合题目要求。

任务完成的具体情况可见附件三。

附件一 系统整体电路原理图

6

�

SINGEL

DAC0832LCJ

1

2

3

4

5

6

7

8

JP3

P

P1

DI7

DI6

DI5

DI4

DI3

DI2

DI1

DI0

13

14

15

16

4

5

6

7

GND

10

GND

3

XFER

17 WR2

18

WR1

2

CS

1

VREF

8

U1

IOUT2

IOUT1

RFB

ILE

VDD

12

11

9

19

20

0.1uF

C1

+5

-12

4

1

3

2

8

+12

8

2

6

5

4

7

U3B

TL082

1

TL082

U3A

A1360

U4

50

R4

C3432

U2

10K

R2

-12

100K

R3

1N4148

D2

1N4148

D1

10K

R1

+12

7

3

1

2

3 4

5

6

8

LT1253

U6

P

P1

2

1

RP1

4.7K-2W

Header 3

1

2

3

JP1

1N4148

D2

DC5V-SHG

5

NPN2

R3

6

R1

1

K2

100K

100K

9012

Q1

N

10K

P

R5

N

2

N

P

10K

N

1

R6

9012

Q2

SIN

1K

R4

1K

R4

-12

4

3

2

1

7

8

6

5

+12

1N4148

LT1253

U4

+5

12

JP2

Header 2

R6

D1

5

6

1

2

DC5V-SHG

4

3

K1

NPN1

5K

R2

20P

C5

2

4

3

+5

100

A

2

A

1

A

3

DGND

SN74LS244N

10

19

1

17

15

13

11

8

6

4

2

GND

2OE

1OE

2A4

2A3

2A2

2A1

1A4

1A3

1A2

1A1

U3

2Y4

2Y3

2Y2

2Y1

1Y4

1Y3

1Y2

1Y1

VCC

3

5

7

9

12

14

16

18

20

+5

10uF

C6

0.1UF

C4

DGND

+5

有源晶振

GND

CLK

NC

VCC

U1

2

1

3

4

+5

DGND

0.1UF

C1

AD9833_BIG

MCLK

DGND

CAP

VDD

COMP

SDATA

SCLK

FSYNC

AGND

VOUT

DGND

5

4

3

2

1

0.1UF

C3

U2

DGND

6

7

8

9

10

SIN

C2

0.1UF

R1

10K

1

2

3

4

5

6

7

8

9

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

V

S

S

V

D

D

V

O

R

S

/

R

W

E

D

B

0

D

B

1

D

B

2

D

B

3

D

B

4

D

B

5

D

B

6

D

B

7

P

S

B

N

C

R

S

T

V

O

U

T

L

E

D

K

L

E

D

A

12864

+5

20P

20P

AT89S51

GND

XTAL2

XTAL1

C8

20

18

6M

Y1

C7

+5

附件三 任务完成的具体情况

VCC

16

MAX232CPE

U1

D Connector 9

1

6

2

7

3

8

4

9

5

11

10

J3

10uF

C5

10uF

C4

10uF

C3

10uF

C2

2

6

15

5

4

3

1

V1+

V-

GND

C2-

C2+

C1-

C1+

U4

R2OUT

T2IN

9

10

R1OUT

T1IN

R1IN

T1OUT

R2IN

T2OUT

12

11

13

14

8

7

+5

Header 9

A1

A2

A3

A4

A5

A6

A7

A8

1

2

3

4

5

6

7

8

9

JP5

7

D8

D7

D6

D5

B8

B7

B6

B5

B4

B3

B2

B1

Header 9

9

8

7

6

5

4

3

2

1

(A15)P2.7

(A14)P2.6

(A13)P2.5

(A12)P2.4

(A11)P2.3

(A10)P2.2

(A9)P2.1

(A8)P2.0

PSEN

ALE/PROG

P3.7(RD)

P3.6(WR)

P3.5(T1)

P3.4(T0)

(AD7)P0.7

(AD6)P0.6

(AD5)P0.5

(AD4)P0.4

(AD3)P0.3

(AD2)P0.2

(AD1)P0.1

(AD0)P0.0

EA/VPP

28

27

26

25

24

23

22

21

29

30

17

16

15

14

32

33

34

35

36

37

38

39

31

S18

10K

R4

D1

D2

D3

D4

C8

C7

C6

C5

C4

C3

C2

19

+5

10uF

C6

9

10

11

12

13

8

7

6

5

4

3

2

RST

(RXD)P3.0

(TXD)P3.1

P3.2(INT0)

P3.3(INT1)

P1.7(SCK)

P1.6(MISO)

P1.5(MOSI)

P1.4

P1.3

P1.2

P1.1

�

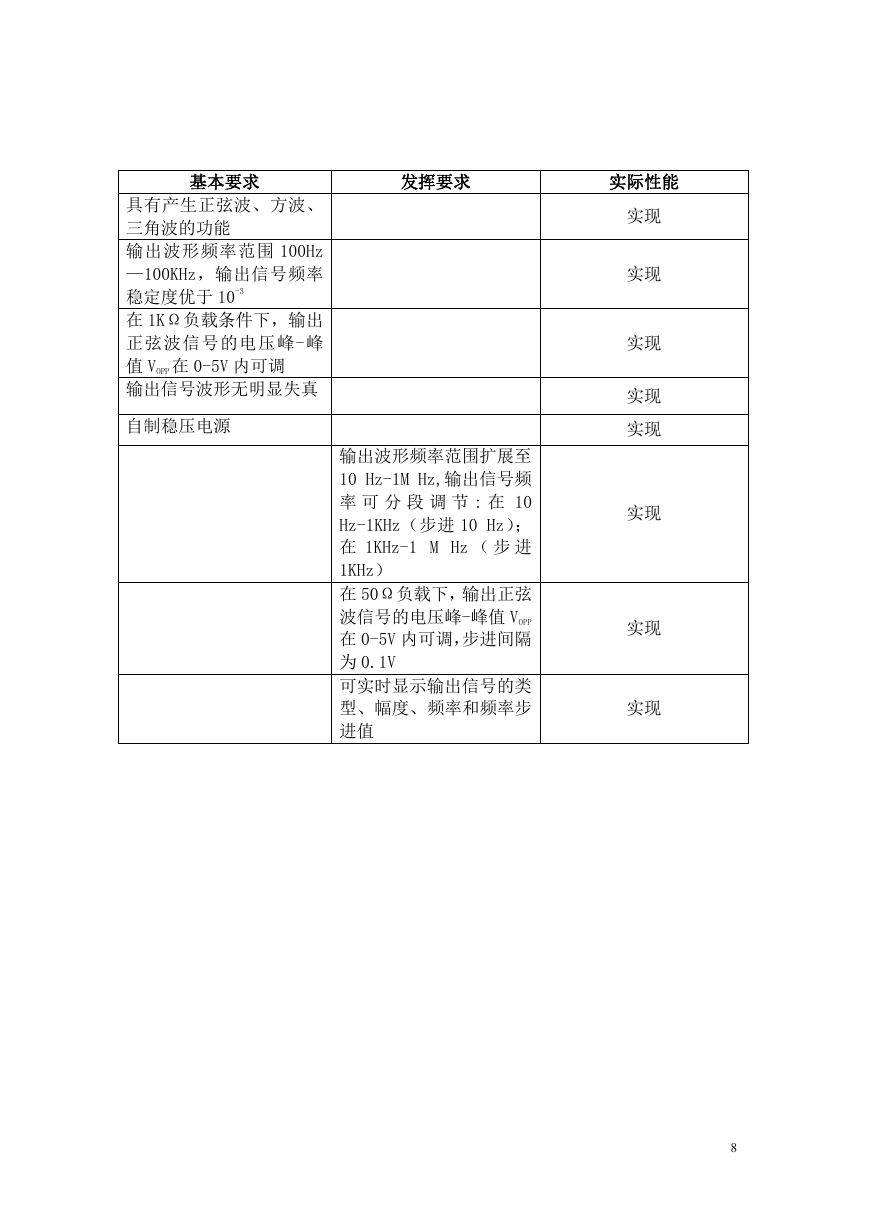

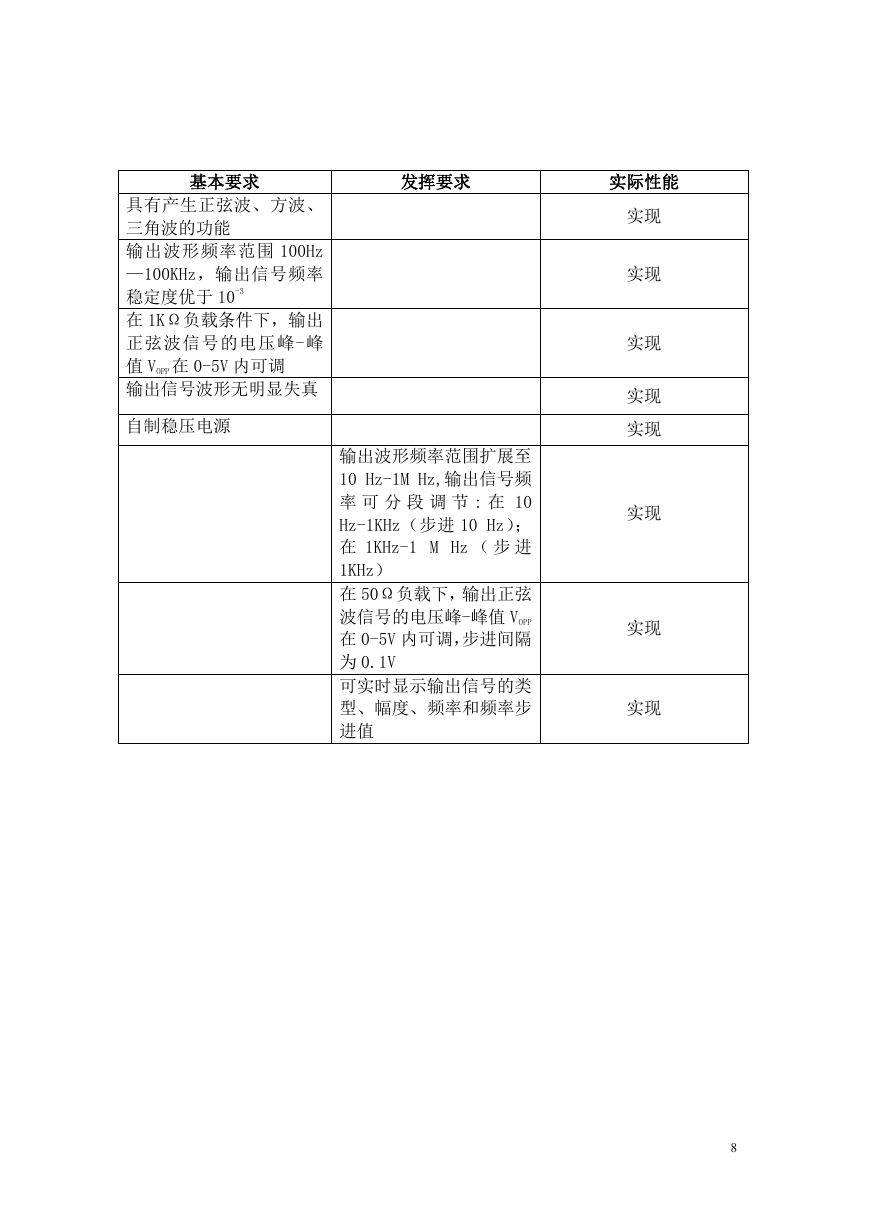

基本要求

发挥要求

实际性能

具有产生正弦波、方波、

三角波的功能

输出波形频率范围 100Hz

—100KHz,输出信号频率

稳定度优于 10-3

在 1KΩ负载条件下,输出

正弦波信号的电压峰-峰

值 VOPP 在 0-5V 内可调

输出信号波形无明显失真

自制稳压电源

输出波形频率范围扩展至

10 Hz-1M Hz,输出信号频

率 可 分 段 调 节 : 在 10

Hz-1KHz(步进 10 Hz);

在 1KHz-1 M Hz ( 步 进

1KHz)

在 50Ω负载下,输出正弦

波信号的电压峰-峰值 VOPP

在 0-5V 内可调,步进间隔

为 0.1V

可实时显示输出信号的类

型、幅度、频率和频率步

进值

实现

实现

实现

实现

实现

实现

实现

实现

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc