DesignWare DW_ahb_icm Databook

DW_ahb_icm – Product Code

1.14a

June 2014

�

DesignWare DW_ahb_icm Databook

Copyright Notice and Proprietary Information Notice

© 2014 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the

property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in

accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or

translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of

Synopsys, Inc., or as expressly provided by the license agreement.

Destination Control Statement

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals

of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and

to comply with them.

Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS

MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A

PARTICULAR PURPOSE.

Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at

http://www.synopsys.com/Company/Pages/Trademarks.aspx.

All other product or company names may be trademarks of their respective owners.

Synopsys, Inc.

700 E. Middlefield Road

Mountain View, CA 94043

www.synopsys.com

2

SolvNet

DesignWare.com

Synopsys, Inc.

1.14a

June 2014

�

DesignWare DW_ahb_icm Databook

Contents

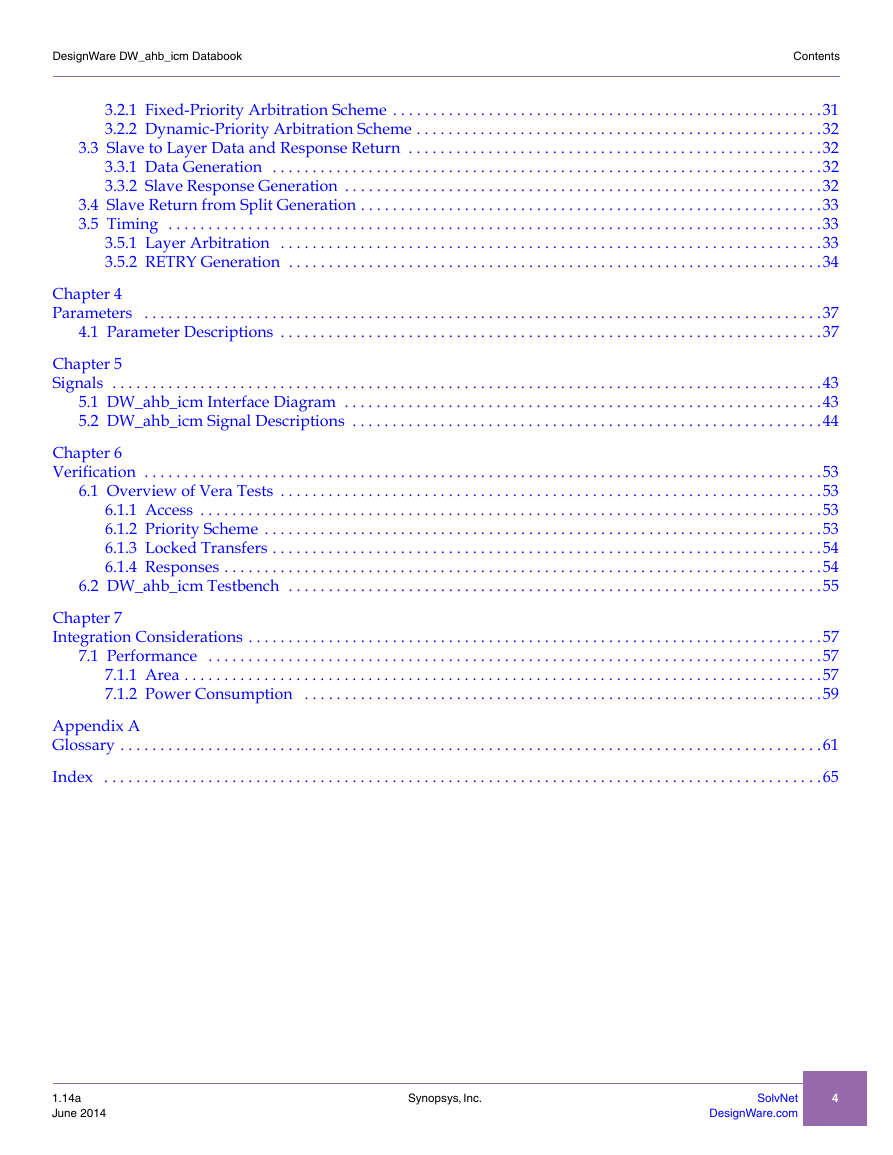

Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Preface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Chapter 1

Product Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.1 DesignWare System Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.2 General Product Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.2.1 DW_ahb_icm Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.4 Standards Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

1.5 Verification Environment Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

1.6 Licenses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

1.7 Where To Go From Here . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Chapter 2

Building and Verifying a Component or Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

2.1 Setting up Your Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

2.2 Overview of the coreConsultant Configuration and Integration Process . . . . . . . . . . . . . . . . . . . . . . . . . .18

2.2.1 coreConsultant Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

2.2.2 Configuring the DW_ahb_icm within coreConsultant . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

2.2.3 Creating Gate-Level Netlists within coreConsultant . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

2.2.4 Verifying the DW_ahb_icm within coreConsultant . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

2.2.5 Running Leda on Generated Code with coreConsultant . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

2.3 Overview of the coreAssembler Configuration and Integration Process . . . . . . . . . . . . . . . . . . . . . . . . . .21

2.3.1 coreAssembler Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

2.3.2 Configuring the DW_ahb_icm within a Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

2.3.3 Creating Gate-Level Netlists within coreAssembler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.3.4 Verifying the DW_ahb_icm within coreAssembler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.3.5 Running Leda on Generated Code with coreAssembler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.4 Database Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.4.1 Design/HDL Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.4.2 Synthesis Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2.4.3 Verification Reference Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Chapter 3

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.1 Input Stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

3.2 Select Arbitration and Layer Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

1.14a

June 2014

Synopsys, Inc.

SolvNet

DesignWare.com

3

�

DesignWare DW_ahb_icm Databook

Contents

3.2.1 Fixed-Priority Arbitration Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

3.2.2 Dynamic-Priority Arbitration Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

3.3 Slave to Layer Data and Response Return . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

3.3.1 Data Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

3.3.2 Slave Response Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

3.4 Slave Return from Split Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3.5 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3.5.1 Layer Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3.5.2 RETRY Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Chapter 4

Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

4.1 Parameter Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Chapter 5

Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

5.1 DW_ahb_icm Interface Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

5.2 DW_ahb_icm Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Chapter 6

Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

6.1 Overview of Vera Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

6.1.1 Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

6.1.2 Priority Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

6.1.3 Locked Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

6.1.4 Responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

6.2 DW_ahb_icm Testbench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Chapter 7

Integration Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

7.1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

7.1.1 Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

7.1.2 Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Appendix A

Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

1.14a

June 2014

Synopsys, Inc.

SolvNet

DesignWare.com

4

�

DesignWare DW_ahb_icm Databook

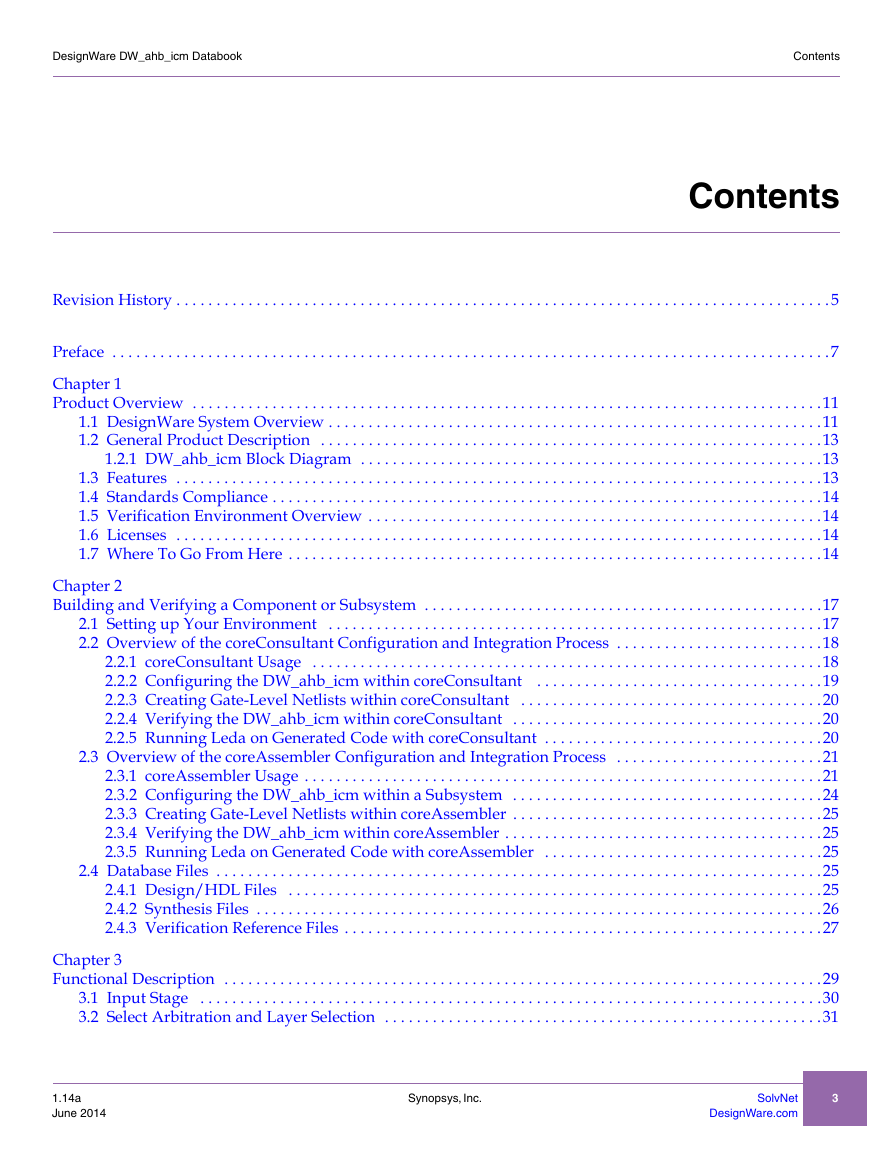

Revision History

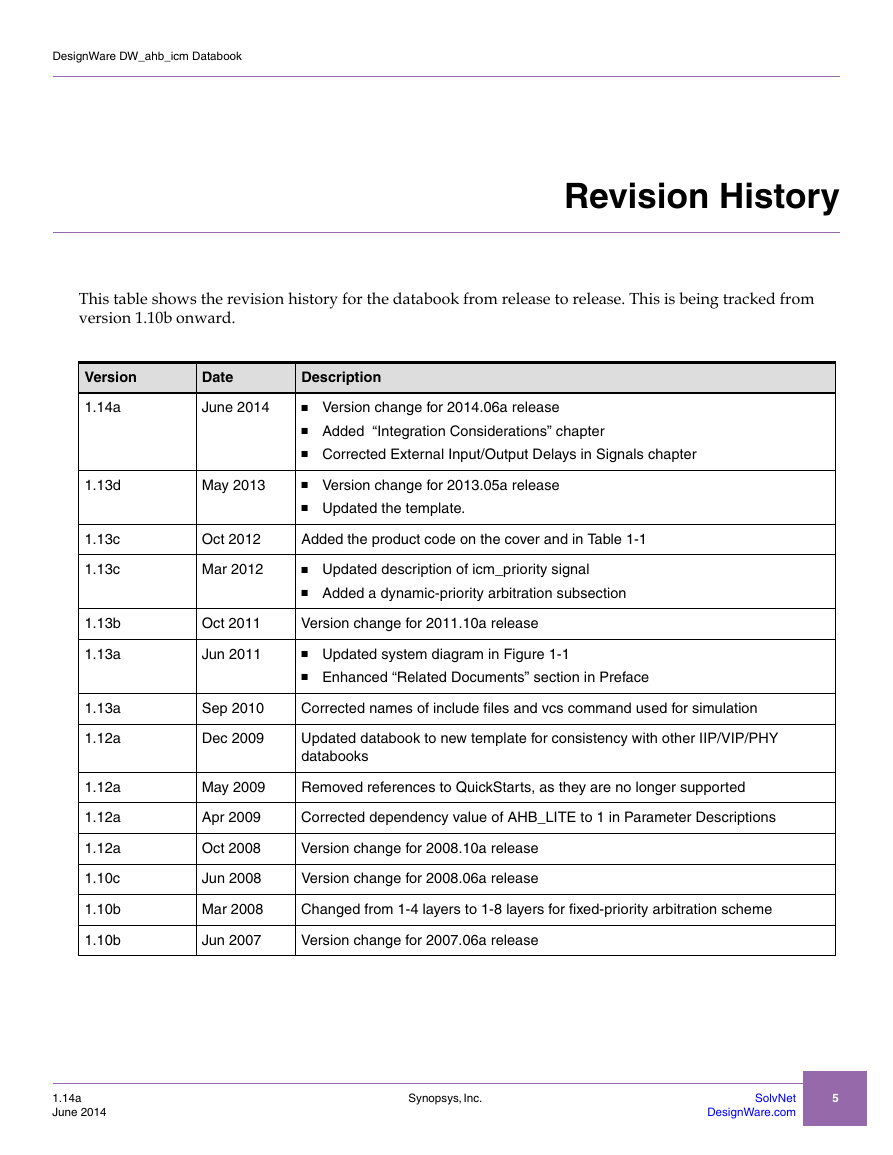

This table shows the revision history for the databook from release to release. This is being tracked from

version 1.10b onward.

Version

Date

Description

1.14a

June 2014

■ Version change for 2014.06a release

■ Added “Integration Considerations” chapter

■ Corrected External Input/Output Delays in Signals chapter

1.13d

May 2013

■ Version change for 2013.05a release

■ Updated the template.

1.13c

1.13c

1.13b

1.13a

1.13a

1.12a

1.12a

1.12a

1.12a

1.10c

1.10b

1.10b

Oct 2012

Added the product code on the cover and in Table 1-1

Mar 2012

■ Updated description of icm_priority signal

■ Added a dynamic-priority arbitration subsection

Oct 2011

Version change for 2011.10a release

Jun 2011

■ Updated system diagram in Figure 1-1

■ Enhanced “Related Documents” section in Preface

Sep 2010

Corrected names of include files and vcs command used for simulation

Dec 2009

Updated databook to new template for consistency with other IIP/VIP/PHY

databooks

May 2009

Removed references to QuickStarts, as they are no longer supported

Apr 2009

Corrected dependency value of AHB_LITE to 1 in Parameter Descriptions

Oct 2008

Version change for 2008.10a release

Jun 2008

Version change for 2008.06a release

Mar 2008

Changed from 1-4 layers to 1-8 layers for fixed-priority arbitration scheme

Jun 2007

Version change for 2007.06a release

1.14a

June 2014

Synopsys, Inc.

SolvNet

DesignWare.com

5

�

Revision History

DesignWare DW_ahb_icm Databook

6

SolvNet

DesignWare.com

Synopsys, Inc.

1.14a

June 2014

�

DesignWare DW_ahb_icm Databook

Preface

This databook provides information about the DesignWare AHB Multi-layer Interconnection Matrix (ICM)

peripheral, referred to as the DW_ahb_icm throughout the remainder of this databook. The DW_ahb_icm

conforms to the AMBA Specification, Revision 2.0 from ARM.

The information in this databook includes a functional description, signal and parameter descriptions,

programming interface, and detailed information about the operation of the DW_ahb_icm. Also provided

are an overview of the component testbench, a description of the tests that are run to verify the

DW_ahb_icm, and synthesis information for the component.

Organization

The chapters of this databook are organized as follows:

■ Chapter 1, “Product Overview” provides a system overview, a component block diagram, basic

features, and an overview of the verification environment.

■ Chapter 2, “Building and Verifying a Component or Subsystem” introduces you to using the

DW_ahb_icm within the coreAssembler and coreConsultant tools.

■ Chapter 3, “Functional Description” describes the functional operation of the DW_ahb_icm.

■ Chapter 4, “Parameters” identifies the configurable parameters supported by the DW_ahb_icm.

■ Chapter 5, “Signals” provides a list and description of the DW_ahb_icm signals.

■ Chapter 6, “Verification” provides information on verifying the configured DW_ahb_icm.

■ Chapter 7, “Integration Considerations” provides performance hardware configuration parameters

that affect the performance of the DW_ahb_icm.

■ Appendix A, “Glossary” provides a glossary of general terms.

Related Documentation

■ Using DesignWare Library IP in coreAssembler – Contains information on getting started with using

DesignWare SIP components for AMBA 2 and AMBA 3 AXI components within coreTools

coreAssembler User Guide – Contains information on using coreAssembler

coreConsultant User Guide – Contains information on using coreConsultant

■

■

To see a complete listing of documentation within the DesignWare Synthesizable Components for AMBA 2,

refer to the Guide to Documentation for DesignWare Synthesizable Components for AMBA 2 and AMBA 3 AXI.

1.14a

June 2014

Synopsys, Inc.

SolvNet

DesignWare.com

7

�

Preface

Web Resources

DesignWare DW_ahb_icm Databook

■ DesignWare IP product information: http://www.designware.com

■ Your custom DesignWare IP page: http://www.mydesignware.com

■ Documentation through SolvNet: http://solvnet.synopsys.com (Synopsys password required)

■

Synopsys Common Licensing (SCL): http://www.synopsys.com/keys

Customer Support

To obtain support for your product:

■

First, prepare the following debug information, if applicable:

❑

❑

For environment setup problems or failures with configuration, simulation, or synthesis that

occur within coreConsultant or coreAssembler, use the following menu entry:

File > Build Debug Tar-file

Check all the boxes in the dialog box that apply to your issue. This menu entry gathers all the

Synopsys product data needed to begin debugging an issue and writes it to the file

/debug.tar.gz.

For simulation issues outside of coreConsultant or coreAssembler:

■ Create a waveforms file (such as VPD or VCD)

■

■

Identify the hierarchy path to the DesignWare instance

Identify the timestamp of any signals or locations in the waveforms that are not understood

■ Then, contact Support Center, with a description of your question and supplying the above

information, using one of the following methods:

❑

For fastest response, use the SolvNet website. If you fill in your information as explained below,

your issue is automatically routed to a support engineer who is experienced with your product.

The Sub Product entry is critical for correct routing.

Go to http://solvnet.synopsys.com/EnterACall and click on the link to enter a call.

Provide the requested information, including:

■

■

Product: DesignWare Library IP

Sub Product: AMBA

■ Tool Version:

■

■

Problem Type:

Priority:

■ Title: DW_ahb_icm

■ Description: For simulation issues, include the timestamp of any signals or locations in

waveforms that are not understood

After creating the case, attach any debug files you created in the previous step.

8

SolvNet

DesignWare.com

Synopsys, Inc.

1.14a

June 2014

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc