2012年 1O月 15日

第 35卷 第 2O期

现 代 电子技 术

M odern Electronics Technique

0 ct.2012

V01.35 No.20

FPGA与 DSP在二维 FFT变换应用中的对 比研究

陈路 林 ,许 骏 ,柳 光 乾 ,杨 画桔 ,许 光

(中 国科 学 院 国家 天文 台 云南 天 文 台 ,云 南 昆 明 650011)

摘 要 :二 维 FFT 变换 是 实 时 图像 处 理 中 最常 用的 算 法 ,对 它 的 计 算机 实现 有 很 多研 究 。在 此 采 用 VHDL 语 言 在 FP—

GA 上 实现 了二 维 FFT 算 法 ,同 时采 用 c语 言 在 DSP上 实现 了相 同 的 算 法 。通 过 实验 结 果 对 比分 析 ,对 两 种 平 台做 比较 ,从

而 了 解 实 时 图像 处 理 在 2种 不 同 平 台上 的 效 率 。 实验 结 果 分析 表 明 ,FPGA 在 执 行 时 间 、功耗 和 资 源 消耗 方 面优 于传 统 的

DSP,但 DSP 的 开 发 周 期 和 开 发 难 度 远 远 小 于 FPGA 。

关键 词 :二 维 FFT;FPGA;VHDL;DSP

中 图 分 类 号 :TN919—34

文献 标 识 码 :A

文章 编 号 :1004—373X(2012)20—0080—04

Contrast research on FPGA and DSP in application Of 2D—FFT

CHEN L lin,XU Jun,LIU Ouang—quan,YANG Hua-ju,XU Guang

(National Astronomical Observatories/Yunnan Observatory,Chinese Academy of Sciences,Kunming 650011,China)

Abstract:2D-FFT is the most commonly used algorithm in real—time image processing.There are many studies on its

computer realization.2D-FFT algorithm was implemented on FPGA with VHDL language. M eanwhile,the same algorithm

w as achieved on D SP with C language. By com paring and analyzing the experim ental results,the efficiency of real—tim e im age

processing in tWO different platforms was understood.The experimental results show that FPGA is more superior to tradition—

al DSP in time execution,power dissipation and hardware utilization,but the difficulty and development cycle of DSP is far

less than that of FPG A .

Keywords:2D-FFT ;FPG A ; V H DL ;DSP

0 引 言

1 二 维 FFT 变 换 理 论

正 在建设 的极 大 光学 和 红 外 望远 镜 无 不 采 用拼 接

一 个 N×M 图像 ,(z, )的二 维 FFT 定 义为 :

镜 面 、主动光 学 、自适 应 光 学作 为其 核 心技 术 。为 实现

共 相 ,必须 展开对 精确 控制 技术 的研究 ,在计 算技 术上 ,

一

M _ 1

l

F(

一

e。j

(1)

这 些控 制都 表现 为 大矩 阵 的 高 速运 算 。基 于下 一代 望

式 中 :U一0,1,2,… ,M 一1;V一0,1,2,… ,N一1。

远镜 主镜 控制技 术对 高速 和并行 实 时处理 的要求 ,在此

二维 的 FFT变换 可 以分解 为多个 一维 的傅 里 叶变

认 为 FPGA 和 DSP芯片是 合适 的选 择 。本 文通 过具体

换 ,则 改式 等 同于 :

的算法 来 初步测 试对 比和分 析 二者 的性能 ,为诸 如拼 接

镜 面 望远镜 这种 多输 入 多输 出 的精 确 、高速 、实 时 主

F(【,, )一

, 。j

M -1

一

镜控 制系 统提供 技术 基础 。

式 中 U一0,1,2,… ,M 一 1。

考虑 到二维 FFT在 图像 处 理场 合 的 广 泛 应 用 ,可

以利 用它 来 快 速 实 现 图 像 相 关 、快 速 卷 积 以及 目标 跟

踪 ,因此它 在天 文 上 有很 广 泛 的 应用 。但 它 运 算 量 大 ,

使用 通用 的微处 理 器来 实 现难 以满 足 信 号 实 时处 理 的

要求 ,本 文对 二维 FFT变 换 在 两种 不 同平 台 上 的应 用

进行 研究 ,通过 实验 分 析 ,比较 了两 种 平 台 上 实现 二 维

F(x, )一 1∑ f(x,y)e Ⅱ‘

(2)

~ 一 1

’ y= 0

式 中 V一0,1,2,… ,N — l。

式 (1),(2)表 明 :一 个 N×M 的二 维 FFT可 以通过

先 进行 N 次一 维 FFT(行 )变换 ,然后 再进 行另 )bM 次

一 维 FFT(列 )变换来 计算 ,即所谓 的行 列分解 法口]。

FFT 的处理性 能 和 开发 难 度 ,并 对 比和 分 析 FPGA 与

2 FPGA 与 DSP的简单 对 比

DSP各 自的优缺 点 ,未 来 设 计 的系 统 能 根 据 具 体 要 求

将二 者结 合起 来使 用 。

收 稿 日期 :2012-06—21

现场可 编程 门阵列 (FPGA)有 很 强 的灵 活 性 ,其 内

部 的具体逻 辑 功能可 以根据 需要 进行 配 置 ,对 电路 的修

改 和维护很 方 便 。FPGA 芯 片 中 的每 个 逻 辑 门在 每个

基 金 项 目 :国 家 自然 科学 基 金资 助项 目(10873034)

时钟 周期 都 同时进行 着某 种逻辑 运算 ,它 非常适 合 于开

�

第 2O期

陈路林 ,等 :FPGA与 DSP在二 维 FFT变 换应 用中 的对 比研究

81

发 并 行 计 算 应 用 。随 着 EDA 技 术 和 微 电子 技 术 的进

完 成 许多 以前 仅 能在 DSP上 实 现 的算 法 ,并 且 已 开始

步 ,FPGA 的 时 钟 延 时 可 达 到 ns级 ;加 上 FPGA 内嵌

集 成 一 些 专 用 的 DSP 功 能 。从 2000年 开 始 至 今 ,

硬 件 资源 的增 加 ,硬 件 电路 的并 行 工 作 方 式 ,使 FPGA

FPGA提供 的 DSP性 能 已经提 高 了 16倍 之 多 ,达 到每

在 超 高速 、实 时信 号 处理 、嵌 入 式 系 统 设计 等领 域 有

秒 500千 兆 次 乘 法一累 加 操 作 (GMACS),在 相 同时 期

非常 广泛 的应 用前 景 。 目前 ,FPGA 的容量 已经跨过 了

内,数 字信 号处 理 器 的性 能 只 从 1.6 GMACS提 高 到

百万 门级 ,这 使 得 FPGA 成 为解 决 系 统 级 设 计 的重 要

了 8 GM Aca[4]。

选 择 方 案 之 一 _2j。

DSP是一 种 专 门用 于 数 字 信 号 处 理 的微 处 理 器 ,

3 实 验 具 体 实 现 和 结 果

其 基 本结 构包 括 哈佛结 构 、流 水 线 操 作 、专 用 的硬 件 3.1 实验 所 用硬件 平 台介 绍

乘 法 器 、特殊 的 DSP指令 以及 快 速 的指 令周 期 等 。这

本实 验 FPGA 使用 Xilinx Spartan一3AN 系 列 的大

些 结 构特 点使 得 DSP芯 片可 以实 现快 速 的 DSP运 算 , 容量 芯 片 XC3S4ooAN,Spartan一3AN 是 Xilinx面 向低

并 使 大部 分运 算 能够 在 很 短 的 时 间 内完成 。DSP的关 成本 应用 的产 品 ,同它 的上一 代 产 品 Spartan-3A 相 比 ,

键 优 势包 括其 对 于新型 及 复杂算 法 的更短 的 开发 时间 , Spartan一3AN 改变 了 闪存配 置方式 ,提 高 了容量 和安全

以及 能够 运行 多种 算法 的灵 活 性¨3]。但 DSP受 到 串行 性[E]。XC3S400AN 逻辑 门 数 为 40万 门 ,片 内集 成 了

指令 流 的限制 ,超过 几 MHz的 采 样 率 ,一 个 DSP只 能 20个 18×18的 硬 件 乘 法 器 模 块 以及 4个 DCM 模 块

完 成 对数 据简 单 的运算 ,在运 算效 率 、执行 速度 等方 面 等 ,并 且 在具 体实 现 时 使 用 FFT IP核 ,这样 可 以 降低

有 时 还不 能完 全满 足工 程 的需要 ,特别 是对 于 大量 复杂 开发 周期 和难 度 ]。详 细 资料 参 见 该 芯 片 的 dataShe一

运 算 的实 时应 用方 面 。

et,表 1是 Spartan一3AN 系 列 FPGA 芯 片 的 基 本

随 着 FPGA 技 术 的 发 展 ,先 进 的 FPGA 已 经 能 够 属 性 _7]。

表 1 Spartan-3AN 系列 FPGA 芯 片 的 基 本 属 性

Device

System Equivalent

L0gk

cLBS

ices

Distributed Block

/k

Cells

/Kb

/Kb

X C3S50A N

50

1 584

1 76

704

XC3S200AN 200

4 032

448

1 792

XC3S400AN 400

8 064

869

3 584

XC3S700AN 700

13 248

l 472

5 888

1l

28

56

92

RAM

RAM M ulDed

te d DCM

lie

… … …

ica

lip

M axim um Maxim um Bitstream T 。 .

s

UI/soer D

I/O I/0 Pairs /K … … …

I

ffere nti

i

/0 P

S

/

a。

s

ize

K

b

144

195

311

64

90

427

1 168

142

1 842

372

165

2 669

1

4

4

8

XC3SI400AN 1 400

25 344

2 816

11 264

176

5O2

227

4 644

l6

本 实 验 DSP部 分 使用 购买 的 C6713DSP开发 板 ,

为 方便测试 和分 析 ,本设 计 基 于 FFT IP核 实 现 了一 个

此 开发 板上 有一 个 C6713DSP。C6713DSP是 一款 具 有

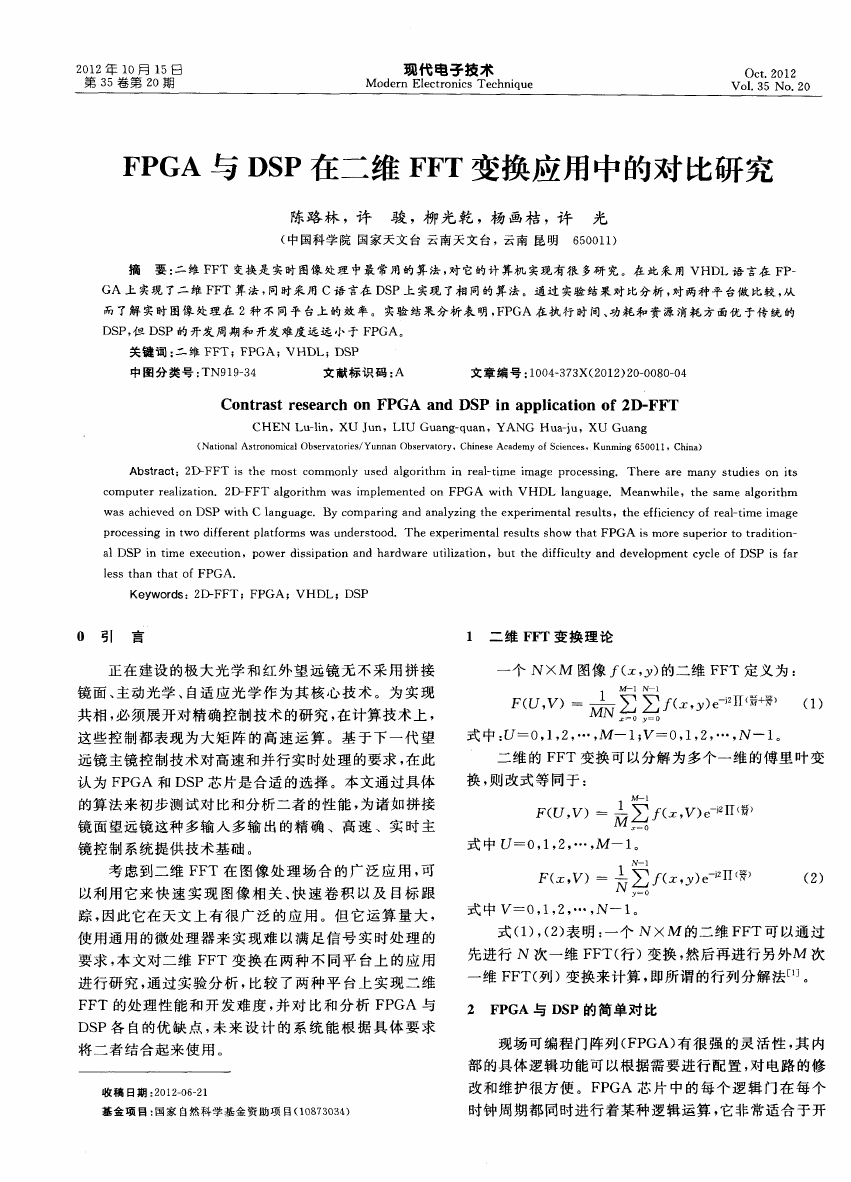

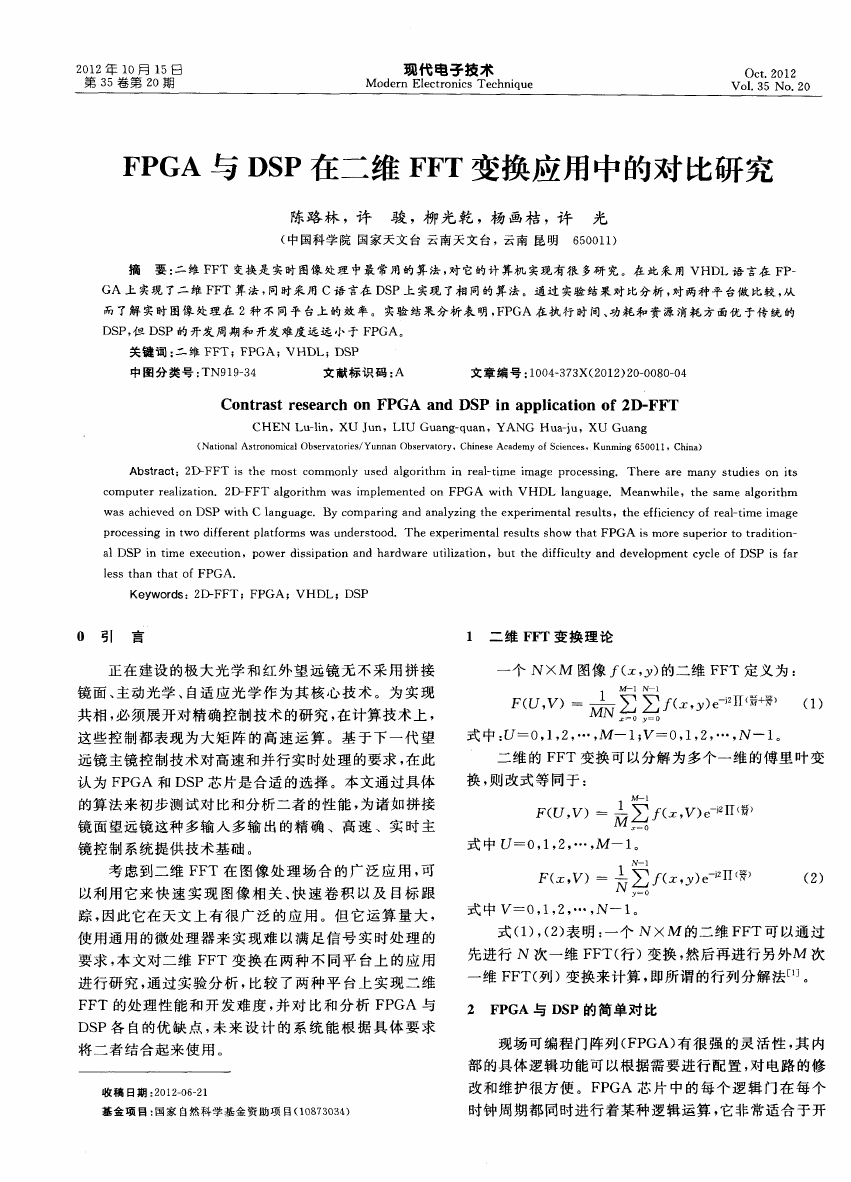

16×16点 的 FFT,具体实现状 态转移 图如 图 2所 示 。

高 速 浮点运 算 能力 的 TI 6000系列 芯 片 ,它使 用 2级 缓

存 的架 构 、具 有 强大 的 和 多样 化 的外 设 集 ,最 高 运 算 速

度达 到 1 350 MFLOPS,并 具 有 双 路 定 点/浮点 型 乘 数

高达 4.5亿 次乘 法 累加 操 作 ,片 内有 64 KB高 速缓 存 。

此外 开 发 板 上 还 集 成 了一 条 4 M × 16 b,100 MHz的

SDRAM ,需 要处 理 的数据 放 在这个 SDRAM 内 。

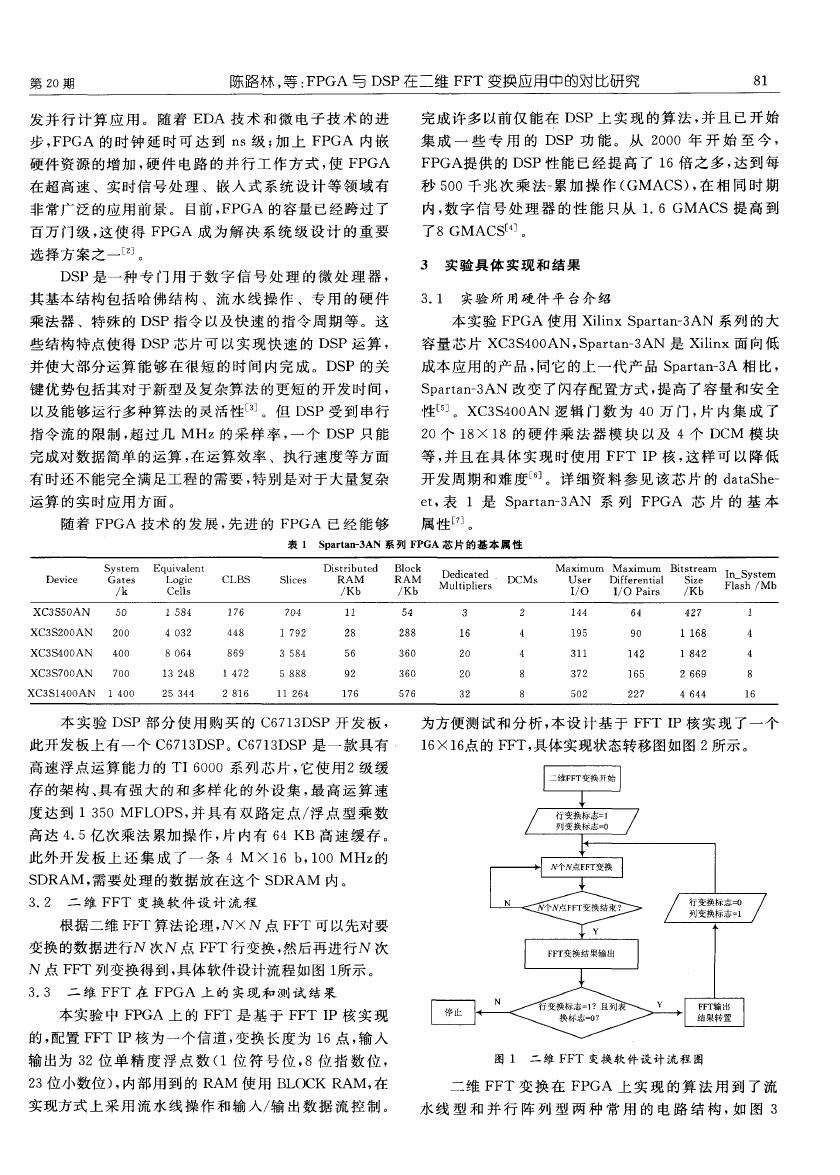

3.2 二 维 FFT 变换 软 件 设 计 流 程

根据二 维 FFT算法论 理 ,NXN 点 FFT可 以先对 要

变换 的数 据进行N 次 N 点 FFT行 变换 ,然后再 进行 N 次

N 点 FFT列 变换得 到 ,具 体软件设计 流程如 图 1所示 。

3.3 二 维 FFT 在 FPGA 上 的 实 现 和 测 试 结 果

本实验 中 FPGA 上 的 FFT是 基 于 FFT IP核 实 现

的 ,配置 FFT IP核为 一个 信 道 ,变 换 长度 为 16点 ,输入

输 出为 32位 单 精 度 浮 点 数 (1位 符 号 位 ,8位 指 数 位 ,

图 1 二 维 FFT 变 换软 件 设 计 流 程 图

23位小 数位 ),内部 用 到 的 RAM 使 用 BLOCK RAM,在

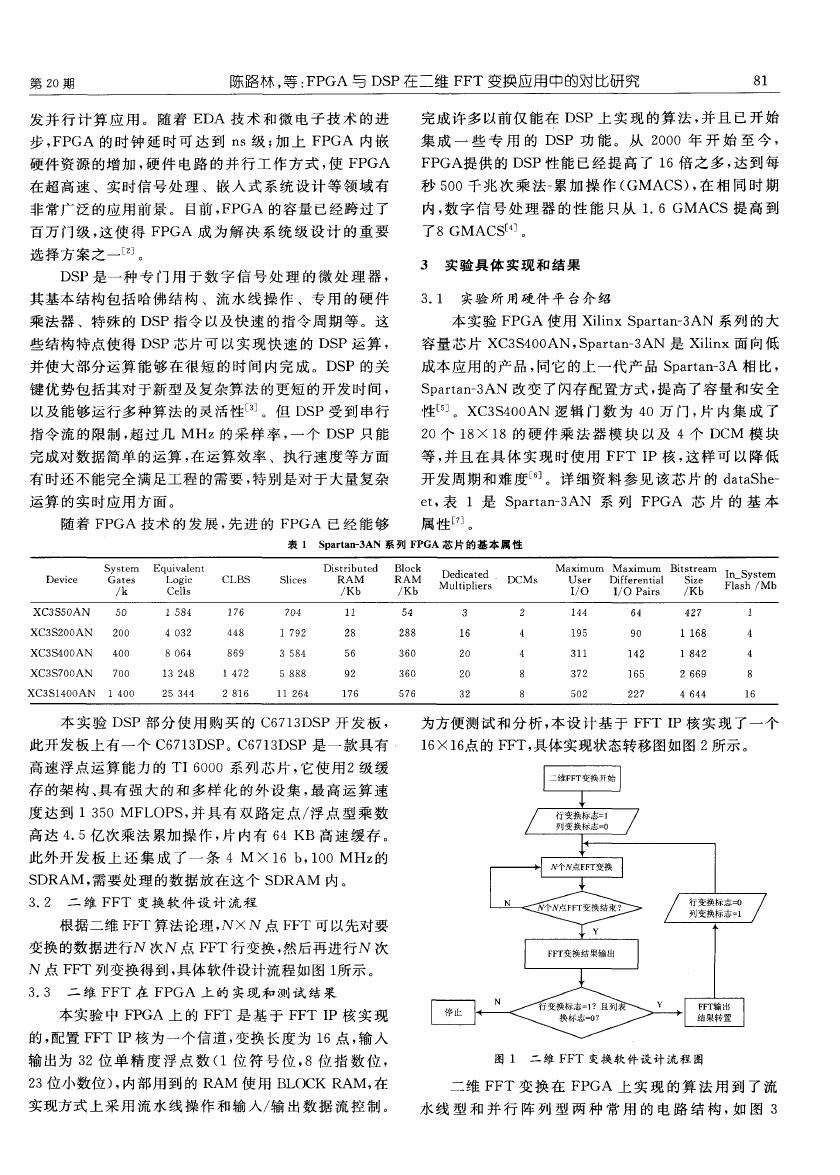

二维 FFT 变换 在 FPGA 上 实 现 的 算 法 用 到 了流

实现方式 上 采 用 流 水 线 操 作 和输 入/输 出 数据 流控 制 。

水 线 型 和 并 行 阵 列 型 两 种 常 用 的 电 路 结 构 ,如 图 3

�

82

所 不 。

现代 电子 技术

2012年第 35卷

射存 储器 空 间的数 据搬 移 。C6713的 片外存 储 空 间大 ,

在流 水线 型 结 构 中 ,一 个 任 务 被 分 解 成 多个 子 任

可 以存放 大量 数据 和 中 间结 果 ,但 访 问速度 慢 ;片 内存

务 ,由多 个子 电路依 次 完成 ,多组 数 据 依 次 流进 流 水 线

储 空 间小 (仅 64 KB),但 访 问 速度 快 ,可 以实 现 小 点数

电路 ,同时进行 不 同阶段 的计 算 ,如 图 3(a)所 示 。忽 略

FFT。鉴 于此 把需要 处理 的二 维数据 放在 片外 ,在 片 内

首批 数据 进入 流水 线 的延 时 ,流水线 型 电路处 理数 据 的

存 储器 完成 一维 FFT,利 用 DMA 实现 片 内与片 外存储

用 时等 于所有 子任 务 中最 长 的用 时[8]。

器 之 间的数 据交换 。

图 2 基 于 F’FI’IP 核 的 二 维 FF I 实 现 状 态 转 移 图

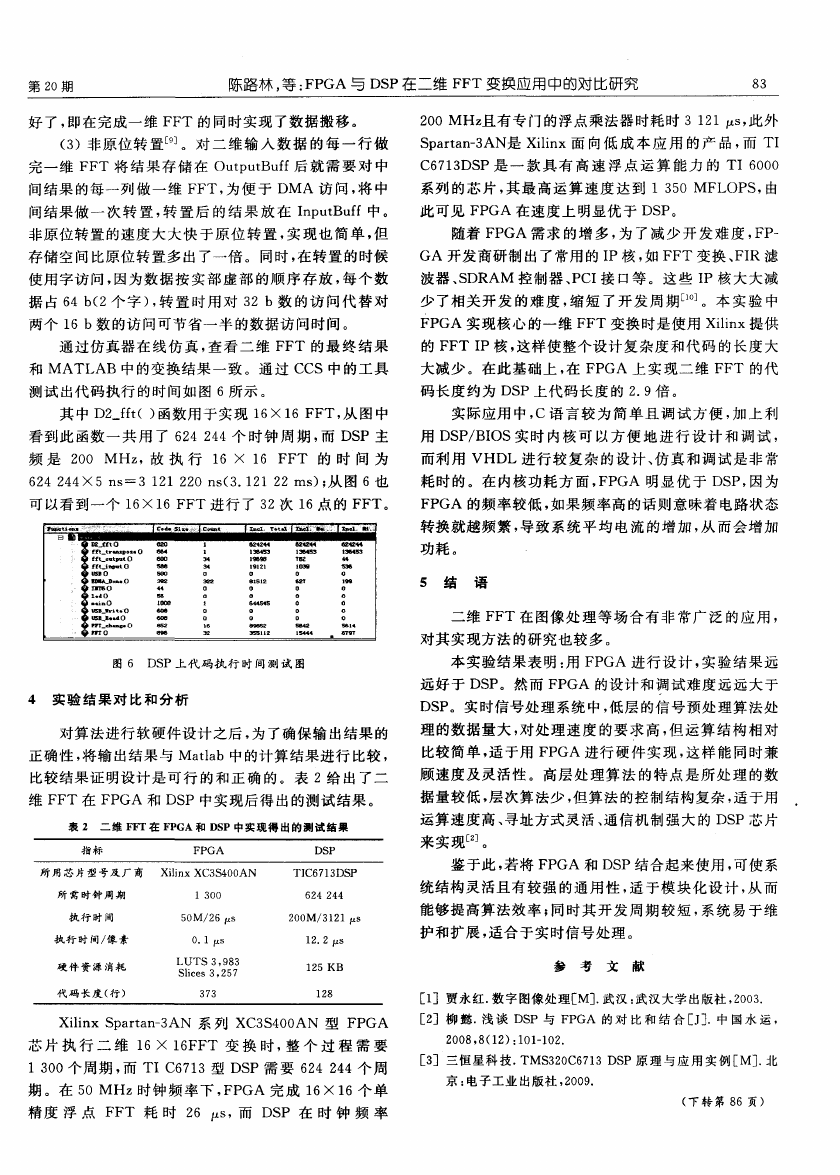

(2)使用 乒乓 缓 冲技 术 在完 成一 维 FFT 的 同 时并

图 4 二 维 F I、在 FPGA 上 实 现 的 功 能 仿 真

在并 行阵列 型 电路 中 ,多组 并行 排列 的子 电路 同时

接收数 据 的 多 个 部 分 进 行 并 行 计 算 ,如 图 3(b)所 示 。

并行 阵列 型 电路 中的子 电路可 以是 简单 的组合 电路 ,也

可 以是复 杂 的时序 电路 ,如 果 受 逻 辑 资源 的 限制 ,无 法

同 时处理 全部 数据 ,也可 依次 处理部 分数 据 。

匝卜 卜-_

—

—@

【a】流水线型电路

行实 现数 据搬 移 。使 用 DMA通 道可 以在 CPU 后 台传

输数 据 ,但 如 果 一 维 FFT 和 DMA 同 时访 问相 同 的 片

内存 储 器时就 会产 生冲 突 ,为 避免 这种情 况 发生就 使 用

如 图 5所 示 的乒乓缓 冲技术 。

L(堕 — 习

(b)并 行 阵 列 型 电 路

图 3 流 水 线 型 电 路 和 并 行 阵 列 型 电 路

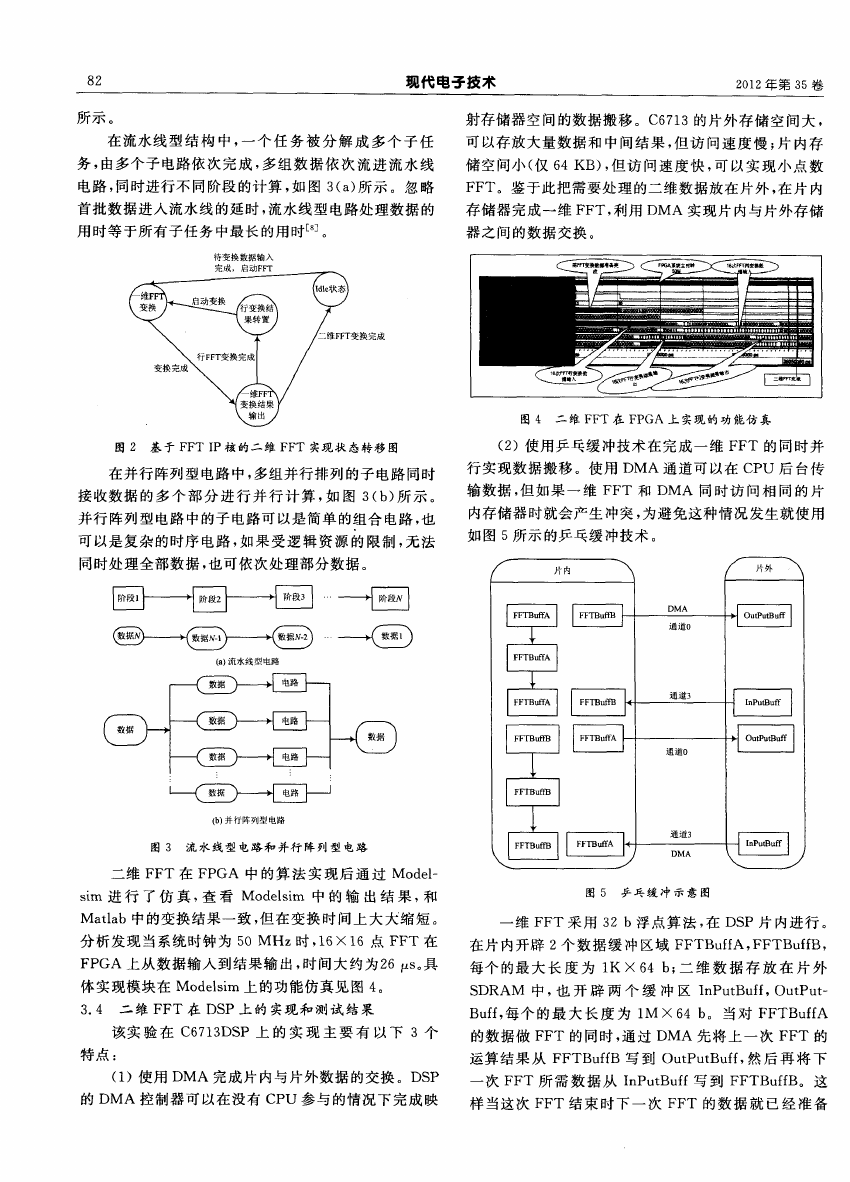

二维 FFT在 FPGA 中 的算 法 实 现 后 通 过 Model—

sim 进 行 了 仿 真 ,查 看 Modelsim 中 的 输 出 结 果 ,和

图 5 乒 乓 缓 冲 示 意 图

Matlab中 的变 换结 果一 致 ,但 在变 换 时 问上 大 大缩 短 。

一 维 FFT采 用 32 b浮点 算 法 ,在 DSP片 内进 行 。

分 析发 现 当系统 时钟 为 50 MHz时 ,16×16点 FFT在

在 片内开辟 2个 数 据 缓 冲 区域 FFTBuffA,FFTBuffB,

FPGA 上从数 据输 入 到结果 输 出 ,时间 大 约为 26 s。具

每个 的最 大 长 度 为 1K×64 b;二 维 数 据 存 放 在 片 外

体 实现 模块 在 Modelsim 上 的功能 仿真 见 图 4。

3.4 二 维 FFT 在 DSP 上 的 实现 和 测 试 结 果

该实 验 在 C6713DSP上 的 实 现 主 要 有 以下 3个

特 点 :

(1)使用 DMA 完成 片 内与片 外数据 的交 换 。DSP

的 DMA 控制 器可 以在 没有 CPU参 与 的情况 下完 成 映

SDRAM 中 ,也 开 辟 两 个 缓 冲 区 InPutBuf{,OutPut—

Buff,每 个 的最 大 长 度 为 1M × 64 b。当 对 FFTBuffA

的数据 做 FFT 的 同时 ,通 过 DMA 先将 上 一 次 FFT 的

运算 结果 从 FFTBuffB写 到 OutPutBuff,然 后 再 将 下

一 次 FFT所 需 数 据 从 InPutBuff写 到 FFTBuffB。 这

样 当这 次 FFT 结束 时下 一 次 FFT 的 数 据 就 已 经 准 备

�

第 20期

陈路林 ,等 :FPGA与 DSP在二 维 FFT变换 应 用中 的对 比研究

83

好 了 ,即在完 成一 维 FFT 的同时 实现 了数 据搬 移 。

200 MHz且 有专 门 的浮点 乘法 器时耗 时 3 121 s,此 外

(3)非 原位转 置_g]。对 二 维 输 入 数 据 的每 一 行 做

Spartan一3AN是 Xilinx面 向 低 成 本 应 用 的 产 品 ,而 TI

完一 维 FFT将 结 果 存 储 在 OutputBuff后 就需 要 对 中

C6713DSP是 一 款 具 有 高 速 浮 点 运 算 能 力 的 TI 6000

间结 果 的每一 列 做一 维 FFT,为 便 于 DMA 访 问 ,将 中

系列 的芯 片 ,其最 高 运 算 速度 达 到 1 350 MFLOPS,由

间结 果做 一 次 转 置 ,转 置 后 的结 果 放 在 InputBuff中 。

此 可见 FPGA在 速度 上 明显优 于 DSP。

非原 位转 置 的速度 大 大 快 于 原位 转 置 ,实 现也 简 单 ,但

随着 FPGA 需 求 的增 多 ,为 了 减 少 开 发 难 度 ,FP—

存 储 空 间 比原 位转 置多 出了一倍 。同时 ,在转 置 的时候

GA 开 发商研 制 出 了常用 的 IP核 ,如 FFT变 换 、FIR滤

使用 字访 问 ,因为 数据 按 实 部 虚 部 的顺 序存 放 ,每 个 数

波 器 、SDRAM 控 制器 、PCI接 口等 。这 些 IP核大 大 减

据 占 64 b(2个 字 ),转 置 时用 对 32 b数 的访 问代 替 对

少 了相关 开 发 的难 度 ,缩 短 了开 发 周 期 l_】 。本 实 验 中

两个 16 b数 的访 问可 节省一 半 的数据 访 问时 间 。

FPGA实 现核 心 的一维 FFT变 换 时是使 用 Xilinx提 供

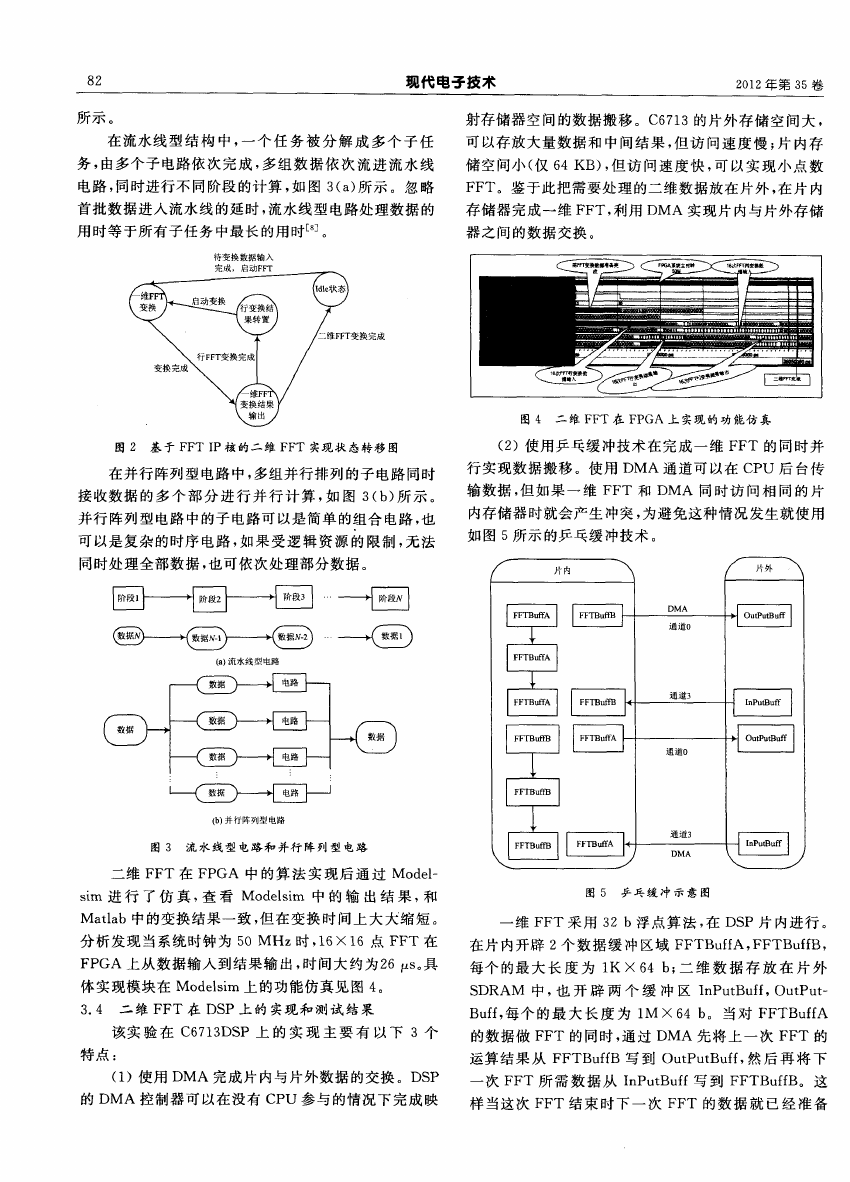

通过 仿 真器 在 线仿 真 ,查看 二 维 FFT 的最 终 结果

的 FFT IP核 ,这样 使整 个设 计 复杂 度 和代 码 的 长度 大

和 MATLAB中 的变换结 果 一致 。通 过 CCS中的 工 具

大 减少 。在 此基 础上 ,在 FPGA 上 实 现二 维 FFT 的代

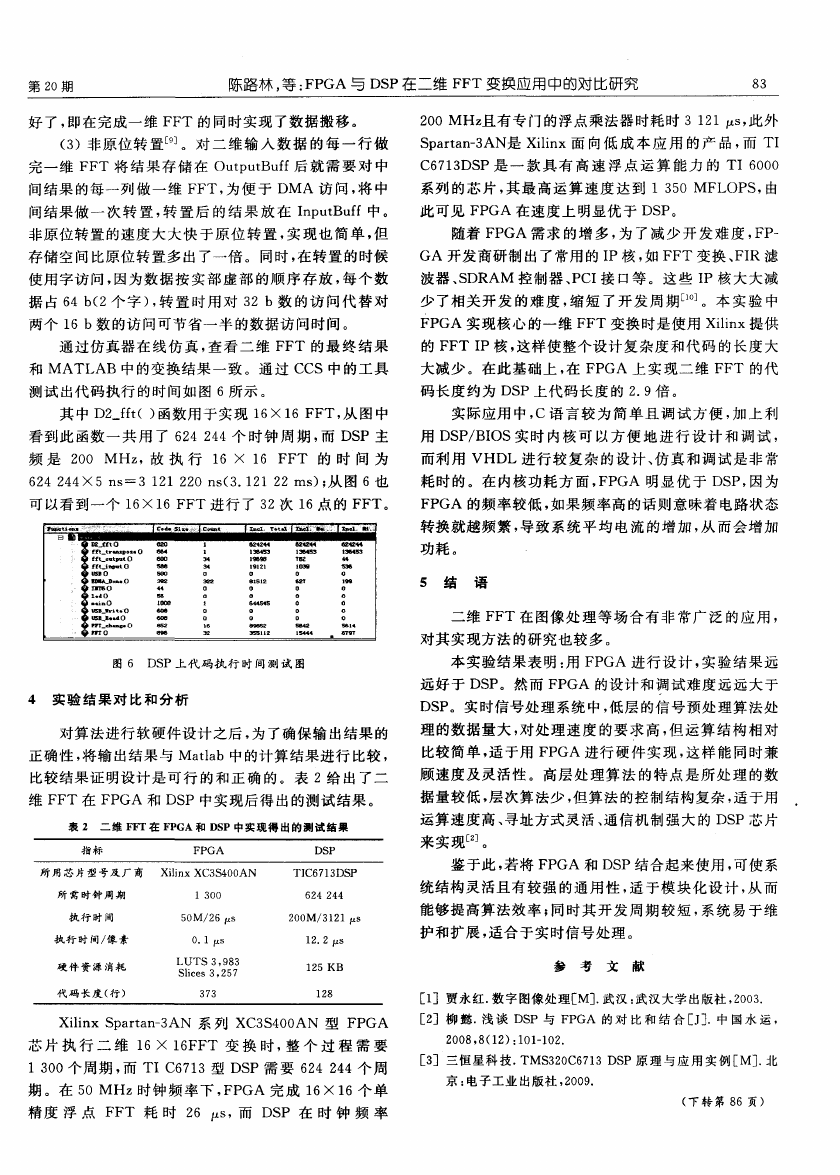

测试 出代 码 执行 的时 间如 图 6所示 。

码 长度 约为 DSP上代码 长度 的 2.9倍 。

其 中 D2一fft()函数 用于 实现 16×16 FFT,从 图 中

实 际应 用 中 ,c语 言较 为 简 单 且 调 试 方 便 ,加 上 利

看到 此 函数 一 共 用 了 624 244个 时 钟 周 期 ,而 DSP主

用 DSP/BIOS实 时 内核 可 以 方便 地 进 行 设 计 和 调试 ,

频 是 200 MHz,故 执 行 16× 16 FFT 的 时 间 为

而 利用 VHDL进 行 较 复杂 的设计 、仿 真和 调 试是 非 常

624 244× 5 ms一 3 121 220 ns(3.121 22 ms);从 图 6也

耗 时 的 。在 内核 功耗 方 面 ,FPGA 明显优 于 DSP,因为

可 以看 到一个 16×16 FFT进 行 了 32次 16点 的 FFT。

FPGA 的频 率较低 ,如果频 率高 的话则 意 味着 电路状 态

转换 就越 频 繁 ,导 致 系统 平 均 电 流 的增 加 ,从 而会 增 加

功 耗 。

5 结 语

二维 FFT在 图像 处 理 等场 合 有 非 常 广 泛 的应 用 ,

对其 实 现方 法 的研 究 也较 多 。

图 6 DSP 上 代 码 执 行 时 间 测 试 图

本 实验结 果表 明 :用 FPGA 进 行 设 计 ,实 验结 果 远

4 实 验 结 果 对 比 和 分 析

远好 于 DSP。然 而 FPGA 的设 计 和调 试难 度 远远 大 于

DSP。实 时信号 处理 系统 中 ,低 层 的信 号 预处 理算 法 处

对算 法进 行 软硬件 设计 之后 ,为 了确 保输 出结 果 的

理 的数据 量 大 ,对 处 理速 度 的要 求 高 ,但运 算 结 构 相 对

正确 性 ,将 输 出结 果与 Matlab中 的计 算结 果 进行 比较 ,

比较 简单 ,适 于用 FPGA 进行 硬件 实 现 ,这 样 能 同时兼

比较 结果 证 明设计 是 可 行 的 和 正确 的 。表 2给 出 了二

顾 速度及 灵 活性 。高 层处 理 算 法 的特 点是 所 处 理 的数

维 FFT在 FPGA 和 DSP中实现 后得 出 的测试 结果 。

据量 较低 ,层 次算 法少 ,但算 法 的控制 结构 复杂 ,适于用

表 2 二 维 FFT在 FPGA 和 DSP中 实 现 得 出 的 测 试 结 果

运算 速度 高 、寻址方 式灵 活 、通信 机制 强 大 的 DSP芯 片

来 实现 J。

鉴 于此 ,若 将 FPGA 和 DSP结合 起来 使用 ,可使 系

统结 构灵 活且 有较 强 的通 用 性 ,适 于模 块 化设 计 ,从 而

能够 提高 算法 效率 ;同时 其 开发 周 期 较 短 ,系 统 易 于维

护和 扩展 ,适合 于实 时信 号处 理 。

参 考 文 献

[1] 贾 永 红 .数 字 图像 处 理 [M].武 汉 :武 汉 大 学 出版 社 ,2003.

Xilinx Spartan一3AN 系 列 XC3S400AN 型 FPGA

[2] 柳 懿 .浅 谈 DSP 与 FPGA 的 对 比 和 结 合 [J].中 国 水 运 ,

芯 片 执 行 二 维 16× 16FFT 变 换 时 ,整 个 过 程 需 要

2008,8(12):i01-102.

1 300个周 期 ,而 TI C6713型 DSP需 要 624 244个 周

期 。在 50 MHz时 钟频 率 下 ,FPGA 完 成 16×16个 单

精 度 浮 点 FFT 耗 时 26 s,而 DSP 在 时 钟 频 率

[3] 三 恒 星 科 技 .TMS320C6713 DSP 原 理 与 应 用 实 例 [M].北

京 :电子 工 业 出版 社 ,2009.

(下转 第 86页 )

�

86

等相 关信 息 ;

现代 电子技 术

一ddq) 8一奇

2012年第 35卷

1 9 8 7 6 5 4 3 21 0

¨¨ ¨∞ 叭0

¨

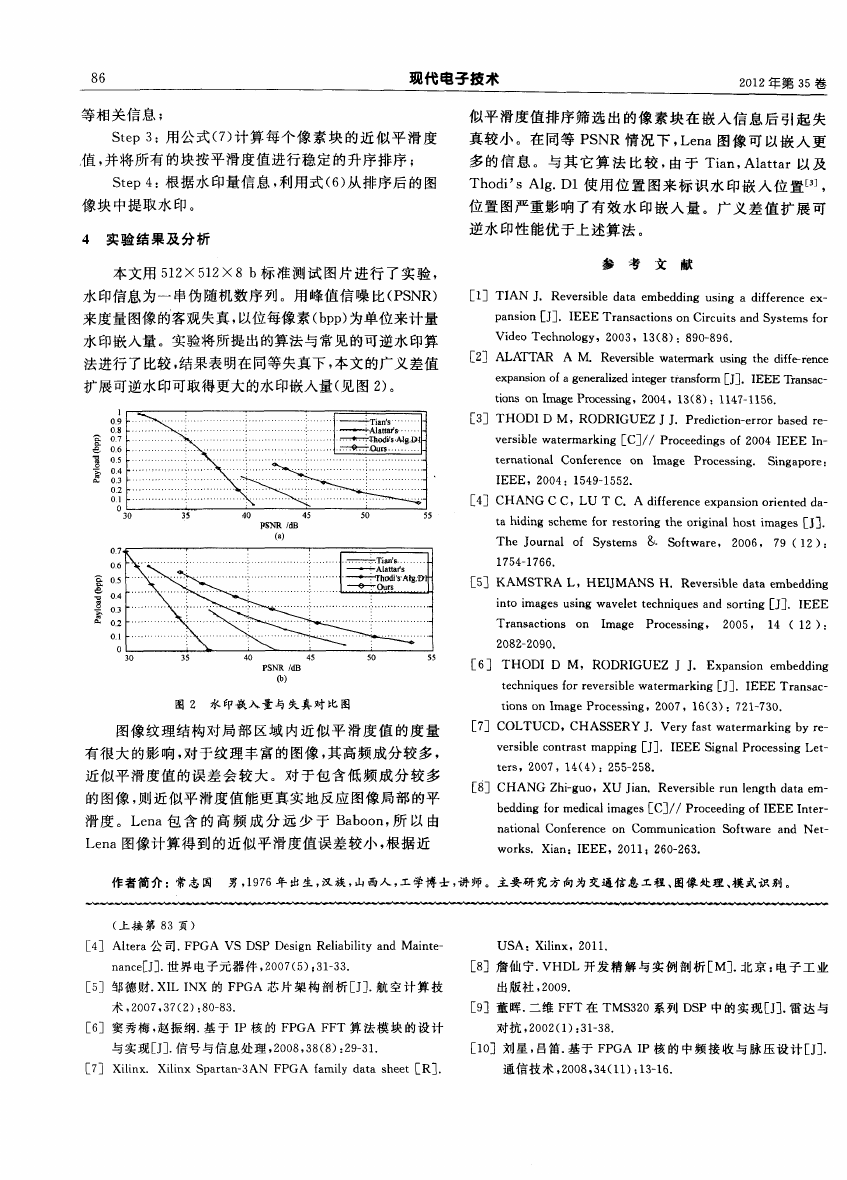

似平 滑度值 排序 筛选 出 的像 素块 在 嵌 入 信 息后 引起 失

¨ ∞ ¨ 0

Step 3:用公 式 (7)计 算每 个 像 素块 的近 似 平 滑度

真较小 。在 同等 PSNR情 况 下 ,Lena图像 可 以嵌 入 更

值 ,并将 所有 的块按 平滑度 值进 行稳定 的 升序排 序 ;

多 的信 息 。与 其 它算 法 比较 ,由于 Tian,Alattar以及

Step 4:根据水 印量信 息 ,利用式 (6)从 排序 后 的图

Thodi’s Alg.D1使 用 位 置 图来 标 识 水 印 嵌 入 位 置Ⅲ ,

像 块 中提取水 印 。

4 实验 结果及分 析

位置 图严重 影 响 了有效 水 印 嵌 入量 。广 义差 值 扩 展 可

逆水 印性 能优 于上述 算法 。

本文用 512×512×8 b标 准测 试 图 片进 行 了实 验 ,

参 考 文 献

水 印信息 为一 串伪 随机数 序列 。用峰值 信 噪 比(PSNR)

[1] TIAN J.Reversible data embedding using a difference ex—

来度量 图像 的客观失真 ,以位每像 素(bpp)为单位来计 量

pansion[J].IEEE Transactions on Circuits and Systems for

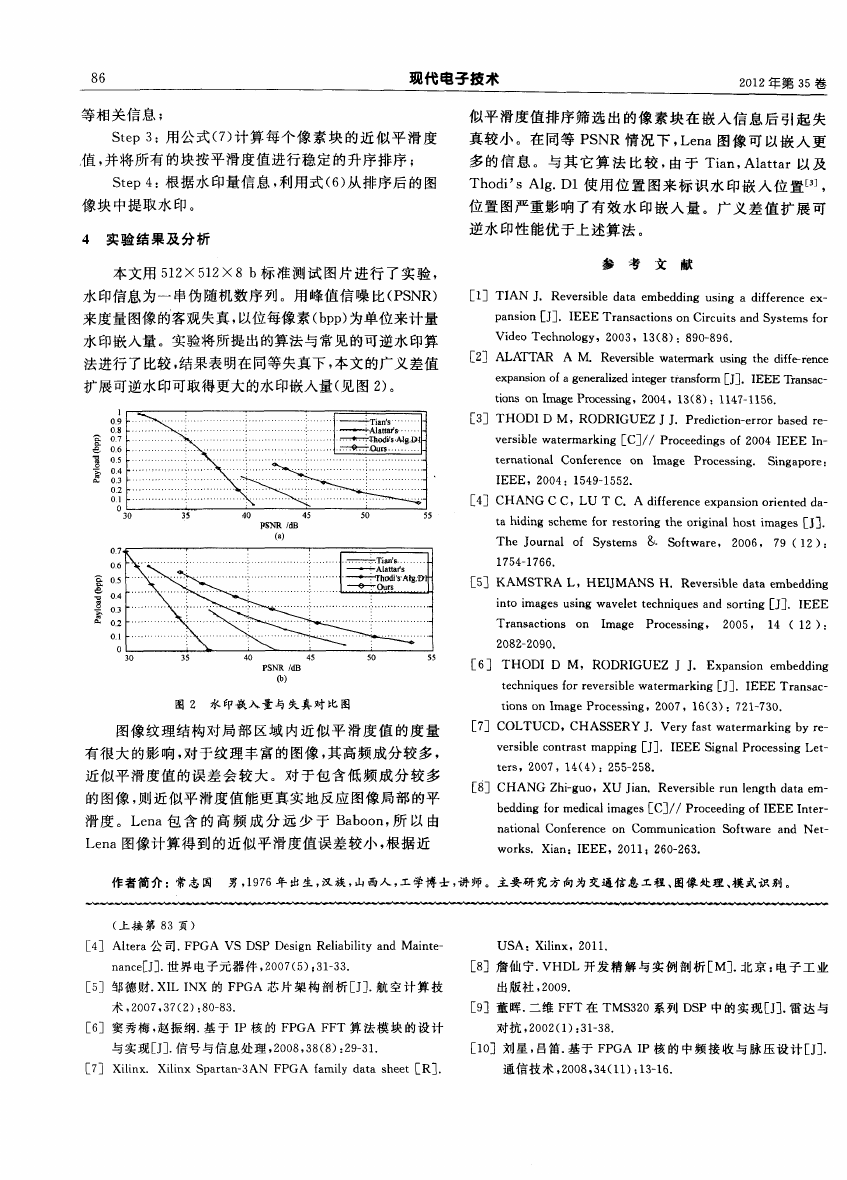

水 印嵌入量 。实验将所提 出的算法 与常见 的可逆水 印算

法进 行了 比较 ,结果表 明在 同等失真下 ,本 文 的广义 差值

扩展可逆水印可取得更 大的水 印嵌 入量(见 图 2)。

._、

\

、

:

Tian's

l_

一 Alat~tt's l·

\

\

:

— …一一l-

。

30

35

、 0

\

\ f、\

、‘

\

.

4o

. ’、

.

\

45

f

r

f

’ 、

f

50

—

55

pSNR ,mj

(a)

e

g

蕾

Video T echnology,2003, 13(8):890—896

.

[2] ALATTAR A M Reversible watermark using the diffe-rence

expansion of a generalized integer t/'ansform [J].IEEE Transac—

tions on Image Processing,2004,13(8):1147—1156.

[3] THODI D M,RODRIGUEZ J J.Prediction-error based re—

versible watermarking[c]//Proceedings of 2004 IEEE In—

ternational Conference on Im age Processing. Singapore:

IEEE, 2004:1549—1552.

[4] CHANG C C,LU T C.A difference expansion oriented da—

ta hiding scheme for restoring the original host images[J].

The Journal of Systems & Software, 2006, 79 (12):

1754-1766.

[5] KAMSlTRA L,HEIJMANS H.Reversible data embedding

into images using wavelet techniques and sorting[J].IEEE

Transactions on Image Processing, 2005, 14 (12):

2082—2090.

[6] THODI D M ,RODRIGUEZ J J. Expansion embedding

techniques for reversible watermarking[J].IEEE Transac—

图 2 水 印 嵌 入 量 与 失 真 对 比 图

tions on Image Processing,2007,16(3):721—730.

图像纹 理结 构对局 部 区 域 内近 似 平 滑度 值 的度 量

[7] COLTUCD,CHASSERY J.Very fast watermarking by re—

有 很大 的影 响 ,对 于纹理 丰富 的图像 ,其高频 成分较 多 ,

近似平 滑度 值 的误差 会 较大 。对 于包 含低 频 成 分 较多

的图像 ,则 近似平 滑度值 能更 真实地 反应 图像局部 的平

滑度 。Lena包 含 的 高 频 成 分 远 少 于 Baboon,所 以 由

versible contrast mapping[J].IEEE Signal Processing Let—

ters,2007,14(4):255—258.

[8] CHANG Zhi—guo,XU Jian.Reversible run length data am—

bedding for medical images It]//Proceeding of IEEE Inter—

national Conference on Communication Software and Net—

Lena图像 计算 得到 的近似 平滑度 值误差 较小 ,根据 近

works.Xian:IEEE,201 1 l 260—263.

作 者 简 介 :常 志 国 男 ,1976年 出生 ,汉族 ,山 西人 ,工 学 博 士 ,讲 师 。主要 研 究 方 向 为 交通 信 息工 程 、图像 处理 、模 式 识 别 。

(上 接 第 83页 )

[4]

Altera公 司 .FPGA VS DSP Design Reliability

and M ainte

USA:Xilinx,2011.

nanceEJ].世 界 电 子元 器 件 ,2007(5);31—33.

[8] 詹 仙 宁 .VHDL开 发 精 解 与 实 例 剖 析 [M].北 京 :电 子 工 业

[5]

邹德 财.XIL INX 的 FPGA 芯 片 架 构 剖 析 [J].

航 空 计 算 技

出版 社 ,2009.

术 ,2007,37(2):8O一83.

[9] 董 晖 .二 维 FFT 在 TMS320系 列 DSP 中 的实 现 [J].雷 达 与

[6] 窦 秀 梅 ,赵 振 纲 .基 于 IP核 的 FPGA FFT 算 法 模 块 的设 计

对 抗 ,2002(1):31-38.

与实 现 [J].信 号 与 信息 处 理 ,2008,38(8):29—31.

[1O] 刘 星 ,吕笛 .基 于 FPGA IP核 的 中频 接 收 与 脉 压 设 计 [J].

[7] Xilinx.Xitinx Spartan-3AN FPGA family data sheet[R].

通 信 技 术 ,2008,34(11):I3—16.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc