Declaration

Contents

Revision History

1 Introduction

1.1 Overview

1.2 Feature

2 Functional Block

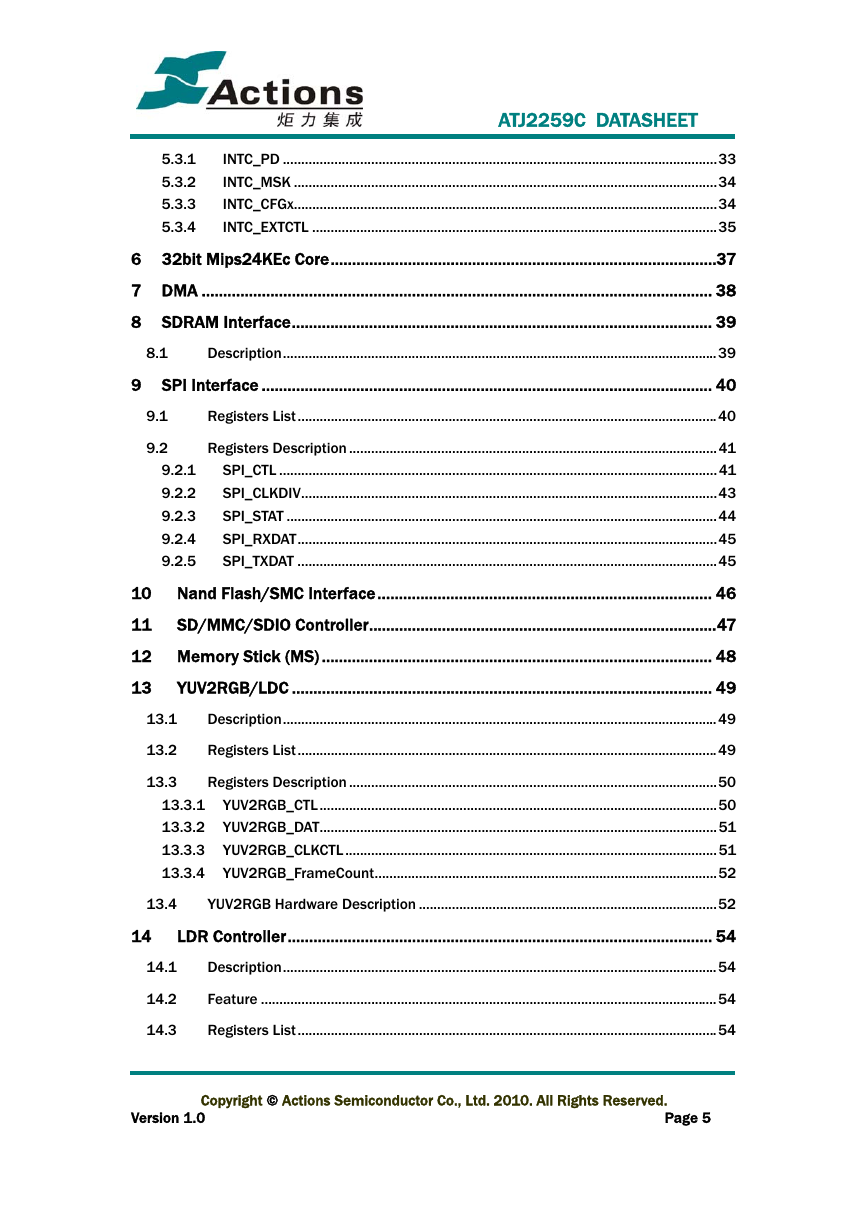

3 PMU/DC-DC Converter

3.1 Description

3.2 Registers List

3.3 Registers Description

3.3.1 PMU_CTL

3.3.2 PMU_LRADC

3.3.3 PMU_CHG

4 CMU/HOSC, RTC/LOSC/Watch Dog, Time Count

4.1 CMU/HOSC

4.1.1 Registers List

4.1.2 Registers Description

4.1.2.1 CMU_UARTxCLK

4.1.2.2 CMU_FMCLK

4.1.2.3 CMU_DEVCLKEN

4.1.2.4 CMU_DEVRST

4.2 RTC/LOSC/Watch Dog, Timer 0, 1

4.2.1 Description

4.2.1.1 2HZ

4.2.1.2 Calendar

4.2.1.3 Alarm

4.2.1.4 Watch Dog

4.2.1.5 TIMER0/1

4.2.2 Registers List

4.2.3 Registers Description

4.2.3.1 RTC_CTL

4.2.3.2 RTC_DHMS

4.2.3.3 RTC_YMD

4.2.3.4 RTC_DHMSALM

4.2.3.5 RTC_YMDALM

4.2.3.6 RTC_WDCTL

4.2.3.7 RTC_T0CTL

4.2.3.8 RTC_T0

4.2.3.9 RTC_T1CTL

4.2.3.10 RTC_T1

5 Interrupt Controller

5.1 Description

5.1.1 Interrupt Sources

5.1.2 External Interrupt Sources

5.2 Registers Lists

5.3 Registers Description

5.3.1 INTC_PD

5.3.2 INTC_MSK

5.3.3 INTC_CFGx

5.3.4 INTC_EXTCTL

6 32bit Mips24KEc Core

7 DMA

8 SDRAM Interface

8.1 Description

9 SPI Interface

9.1 Registers List

9.2 Registers Description

9.2.1 SPI_CTL

9.2.2 SPI_CLKDIV

9.2.3 SPI_STAT

9.2.4 SPI_RXDAT

9.2.5 SPI_TXDAT

10 Nand Flash/SMC Interface

11 SD/MMC/SDIO Controller

12 Memory Stick (MS)

13 YUV2RGB/LDC

13.1 Description

13.2 Registers List

13.3 Registers Description

13.3.1 YUV2RGB_CTL

13.3.2 YUV2RGB_DAT

13.3.3 YUV2RGB_CLKCTL

13.3.4 YUV2RGB_FrameCount

13.4 YUV2RGB Hardware Description

14 LDR Controller

14.1 Description

14.2 Feature

14.3 Registers List

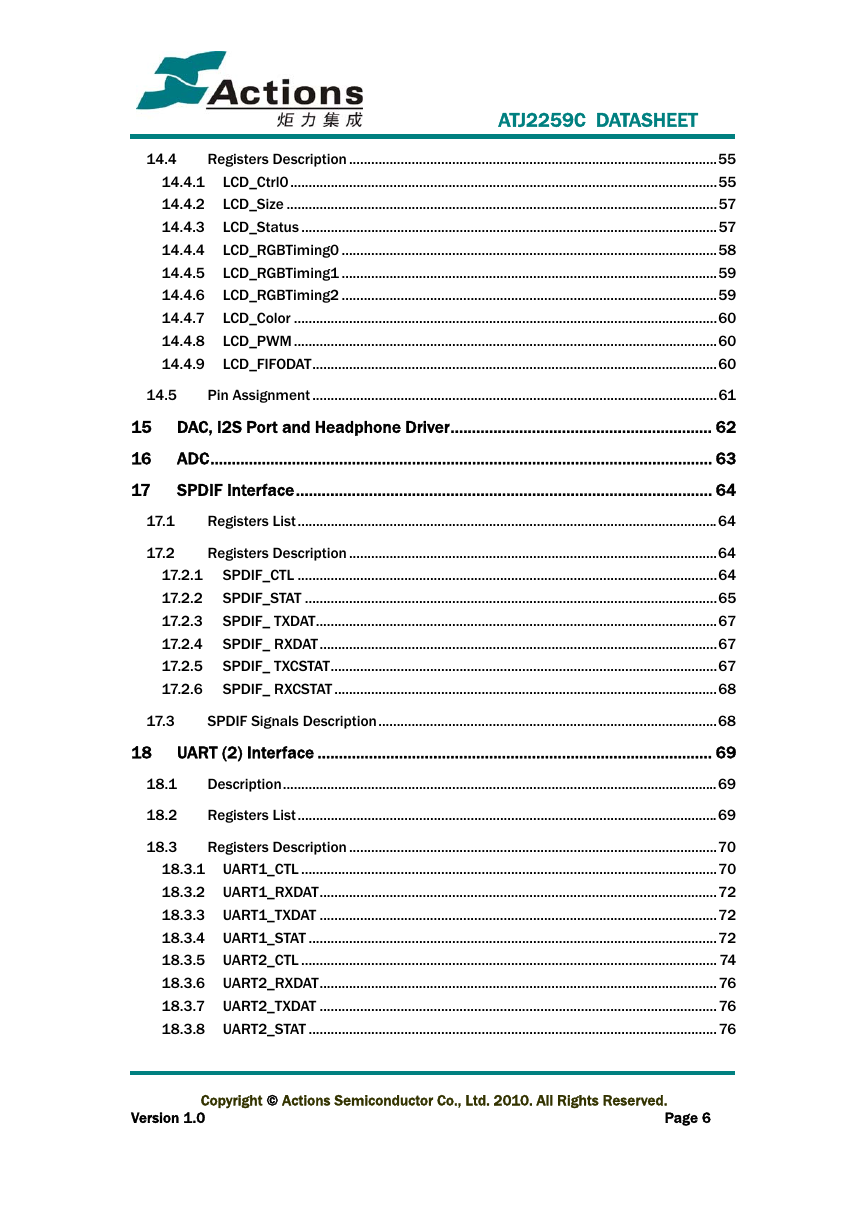

14.4 Registers Description

14.4.1 LCD_Ctrl0

14.4.2 LCD_Size

14.4.3 LCD_Status

14.4.4 LCD_RGBTiming0

14.4.5 LCD_RGBTiming1

14.4.6 LCD_RGBTiming2

14.4.7 LCD_Color

14.4.8 LCD_PWM

14.4.9 LCD_FIFODAT

14.5 Pin Assignment

15 DAC, I2S Port and Headphone Driver

16 ADC

17 SPDIF Interface

17.1 Registers List

17.2 Registers Description

17.2.1 SPDIF_CTL

17.2.2 SPDIF_STAT

17.2.3 SPDIF_ TXDAT

17.2.4 SPDIF_ RXDAT

17.2.5 SPDIF_ TXCSTAT

17.2.6 SPDIF_ RXCSTAT

17.3 SPDIF Signals Description

18 UART (2) Interface

18.1 Description

18.2 Registers List

18.3 Registers Description

18.3.1 UART1_CTL

18.3.2 UART1_RXDAT

18.3.3 UART1_TXDAT

18.3.4 UART1_STAT

18.3.5 UART2_CTL

18.3.6 UART2_RXDAT

18.3.7 UART2_TXDAT

18.3.8 UART2_STAT

18.4 UART Signals Description

19 IR Interface

19.1 Description

19.2 Registers List

19.3 Registers Description

19.3.1 IR_PL

19.3.2 IR_RBC

20 I2C (2) Interface

20.1 Description

20.2 Registers List

20.3 Registers Decription

20.3.1 I2Cx_CTL

20.3.2 I2Cx_CLKDIV

20.3.3 I2Cx_STAT

20.3.4 I2Cx_ADDR

20.3.5 I2Cx_DAT

20.4 I2C Signals Description

21 Key Scan

21.1 Description

21.2 Registers List

21.3 Key Scan Registers Description

21.3.1 KEY_CTL

21.3.2 KEY_DAT0

21.3.3 KEY_DAT1

21.3.4 KEY_DAT2

21.3.5 KEY_DAT3

22 GPIO_MFP

22.1 Description

22.1.1 Uart/IR/I2C/SPI/SPDIF

22.1.2 GPIO/Function Pin

22.1.3 RGB/Function Pin

22.1.4 Pad with Build-in Resistance

22.2 Registers List

22.3 Registers Description

22.3.1 GPIO_AOUTEN

22.3.2 GPIO_AINEN

22.3.3 GPIO_ADAT

22.3.4 GPIO_BOUTEN

22.3.5 GPIO_BINEN

22.3.6 GPIO_BDAT

22.3.7 GPIO_MFCTL1

22.3.8 GPIO_MFCTL2

22.3.9 PAD_DRV

23 Electrical Characteristics

23.1 Absolute Maximum Ratings

23.2 DC Characteristics

23.3 AC Characteristics

23.3.1 AC Test Input Waveform

23.3.2 AC Test Output Measuring Points

23.4 Reset Parameter

23.5 Initialization Parameter

23.6 PMU

23.6.1 DC/DC Operates Voltage

23.6.2 System Standby Dissipation

23.6.3 LRADC

23.7 GPIO Interface Parameter

23.8 Ordinary ROM Parameter

23.9 External System Bus Parameter

23.10 Bus Operation

23.11 SPI Parameter

23.12 SPDIF Interface Parameter

23.13 I2C Interface Parameter

23.14 A/D Converter Characteristics

23.15 D/A Converter Characteristics

23.16 Headphone Driver Characteristics

23.17 LCM Driver Parameter

23.17.1 LDC LCM Driver Parameter

23.17.2 LDR LCM Driver Parameter

23.18 CMOS Sensor Timing (same with BT601)

23.19 Encoder IF

23.20 Decoder IF (BT656, BT601)

23.21 NAND Flash IF

23.22 SD/MMC IF

23.23 MS IF

23.24 SDRAM IF

24 Pin Definition

24.1 Pin Sort by Pin Number

24.2 ATJ2259C Pin Definition

25 ATJ2259C Package Drawing

26 Appendix

26.1 Acronym and Abbreviations

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc