课后答案网 您最真诚的朋友

www.hackshp.cn网团队竭诚为学生服务,免费提供各门课后答案,不用积分,甚至不用注

册,旨在为广大学生提供自主学习的平台!

课后答案网:www.hackshp.cn

视频教程网:www.efanjy.com

PPT课件网:www.ppthouse.com

课后答案网 www.hackshp.cn课后答案网:www.hackshp.cn若侵犯了您的版权利益,敬请来信告知! www.hackshp.cn�

SOLUTIONS MANUAL

COMPUTER ORGANIZATION AND

DESIGNING FOR PERFORMANCE

ARCHITECTURE

SEVENTH EDITION

WILLIAM STALLINGS

Copyright 2005: William Stallings

课后答案网 www.hackshp.cn课后答案网:www.hackshp.cn若侵犯了您的版权利益,敬请来信告知! www.hackshp.cn�

© 2005 by William Stallings

All rights reserved. No part of this document may

be reproduced, in any form or by any means, or

posted on the Internet, without permission in

writing from the author.

-2-

课后答案网 www.hackshp.cn课后答案网:www.hackshp.cn若侵犯了您的版权利益,敬请来信告知! www.hackshp.cn�

NOTICE

This manual contains solutions to all of the review questions and

homework problems in Computer Organization and Architecture,

Seventh Edition. If you spot an error in a solution or in the wording of a

problem, I would greatly appreciate it if you would forward the

information via email to ws@shore.net. An errata sheet for this manual,

if needed, is available at WilliamStallings.com

W.S.

-3-

课后答案网 www.hackshp.cn课后答案网:www.hackshp.cn若侵犯了您的版权利益,敬请来信告知! www.hackshp.cn�

TABLE OF CONTENTS

Computer Evolution and Performance.....................................................5

Chapter 2:

Computer Function and Interconnection.................................................9

Chapter 3:

Cache Memory............................................................................................14

Chapter 4:

Internal Memory ........................................................................................27

Chapter 5:

External Memory........................................................................................33

Chapter 6:

Input/Output .............................................................................................37

Chapter 7:

Operating System Support .......................................................................43

Chapter 8:

Computer Arithmetic ................................................................................48

Chapter 9:

Instruction Sets: Characteristics and Functions.....................................61

Chapter 10:

Instruction Sets: Addressing Modes and Formats ................................72

Chapter 11:

Processor Structure and Function............................................................77

Chapter 12:

Reduced Instruction Set Computers (RISCs).........................................83

Chapter 13:

Instruction-Level Parallelism and Superscalar Processors ..................87

Chapter 14:

Chapter 15:

The IA-64 Architecture..............................................................................93

Control Unit Operation.............................................................................97

Chapter 16:

Chapter 17: Microprogrammed Control....................................................................100

Chapter 18:

Parallel Processing ...................................................................................103

Appendix A: Number Systems......................................................................................112

Appendix B: Digital Logic..............................................................................................113

-4-

课后答案网 www.hackshp.cn课后答案网:www.hackshp.cn若侵犯了您的版权利益,敬请来信告知! www.hackshp.cn�

COMPUTER EVOLUTION AND

CHAPTER 2

PERFORMANCE

AA NSWERS TO

NSWERS TO QQ U E S T I O N S

U E S T I O N S

2.1 In a stored program computer, programs are represented in a form suitable for

storing in memory alongside the data. The computer gets its instructions by reading

them from memory, and a program can be set or altered by setting the values of a

portion of memory.

2.2 A main memory, which stores both data and instructions: an arithmetic and logic

unit (ALU) capable of operating on binary data; a control unit, which interprets the

instructions in memory and causes them to be executed; and input and output

(I/O) equipment operated by the control unit.

2.3 Gates, memory cells, and interconnections among gates and memory cells.

2.4 Moore observed that the number of transistors that could be put on a single chip

was doubling every year and correctly predicted that this pace would continue into

the near future.

2.5 Similar or identical instruction set: In many cases, the same set of machine

instructions is supported on all members of the family. Thus, a program that

executes on one machine will also execute on any other. Similar or identical

operating system: The same basic operating system is available for all family

members. Increasing speed: The rate of instruction execution increases in going

from lower to higher family members. Increasing Number of I/O ports: In going

from lower to higher family members. Increasing memory size: In going from

lower to higher family members. Increasing cost: In going from lower to higher

family members.

2.6 In a microprocessor, all of the components of the CPU are on a single chip.

AA NSWERS TO

NSWERS TO PP R O B L E M S

R O B L E M S

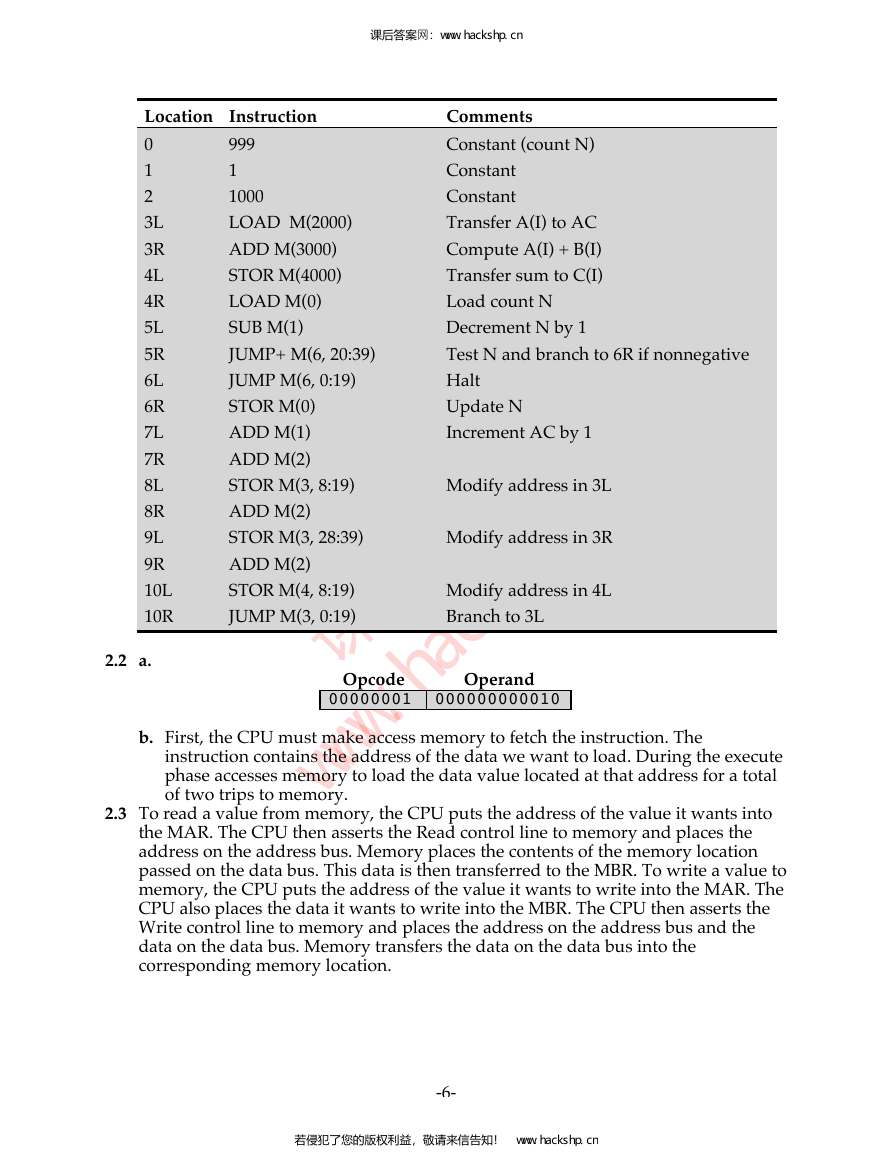

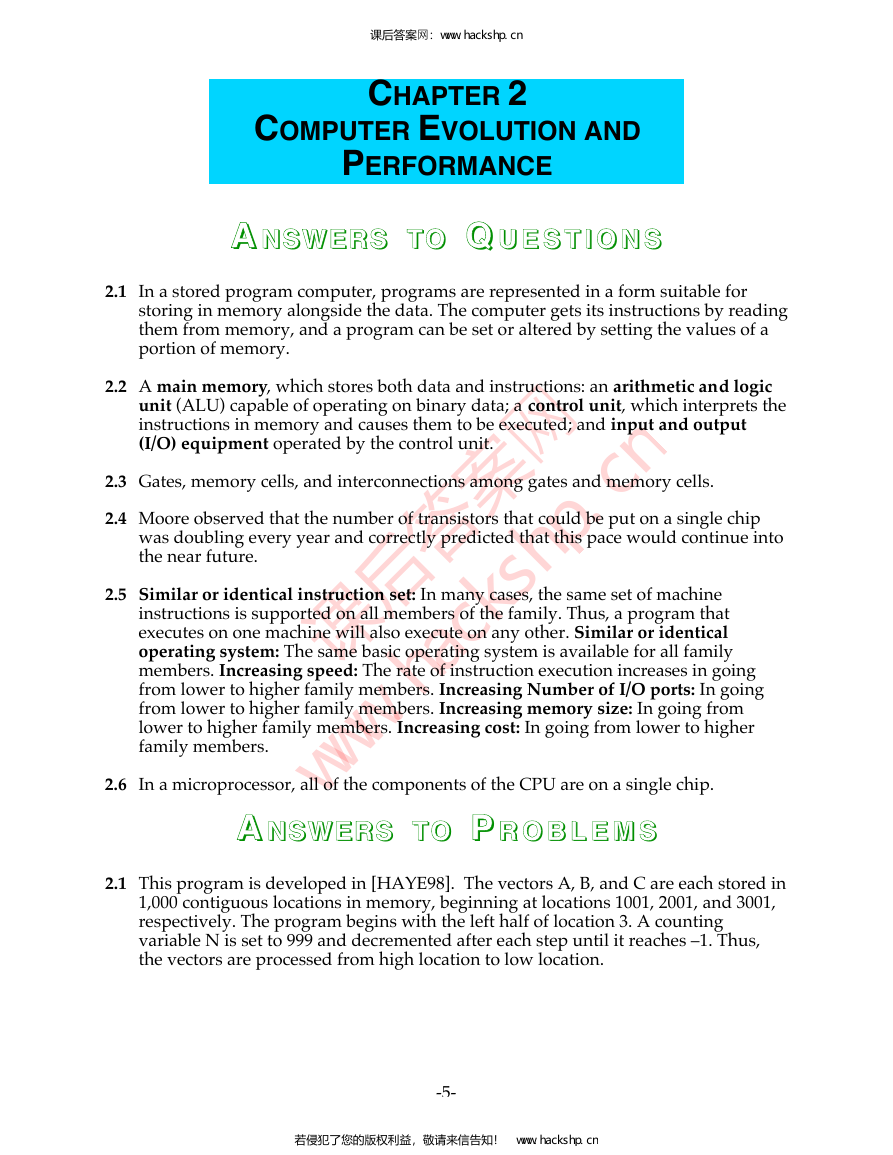

2.1 This program is developed in [HAYE98]. The vectors A, B, and C are each stored in

1,000 contiguous locations in memory, beginning at locations 1001, 2001, and 3001,

respectively. The program begins with the left half of location 3. A counting

variable N is set to 999 and decremented after each step until it reaches –1. Thus,

the vectors are processed from high location to low location.

-5-

课后答案网 www.hackshp.cn课后答案网:www.hackshp.cn若侵犯了您的版权利益,敬请来信告知! www.hackshp.cn�

Location Instruction

0

1

2

3L

3R

4L

4R

5L

5R

6L

6R

7L

7R

8L

8R

9L

9R

10L

10R

999

1

1000

LOAD M(2000)

ADD M(3000)

STOR M(4000)

LOAD M(0)

SUB M(1)

JUMP+ M(6, 20:39)

JUMP M(6, 0:19)

STOR M(0)

ADD M(1)

ADD M(2)

STOR M(3, 8:19)

ADD M(2)

STOR M(3, 28:39)

ADD M(2)

STOR M(4, 8:19)

JUMP M(3, 0:19)

Comments

Constant (count N)

Constant

Constant

Transfer A(I) to AC

Compute A(I) + B(I)

Transfer sum to C(I)

Load count N

Decrement N by 1

Test N and branch to 6R if nonnegative

Halt

Update N

Increment AC by 1

Modify address in 3L

Modify address in 3R

Modify address in 4L

Branch to 3L

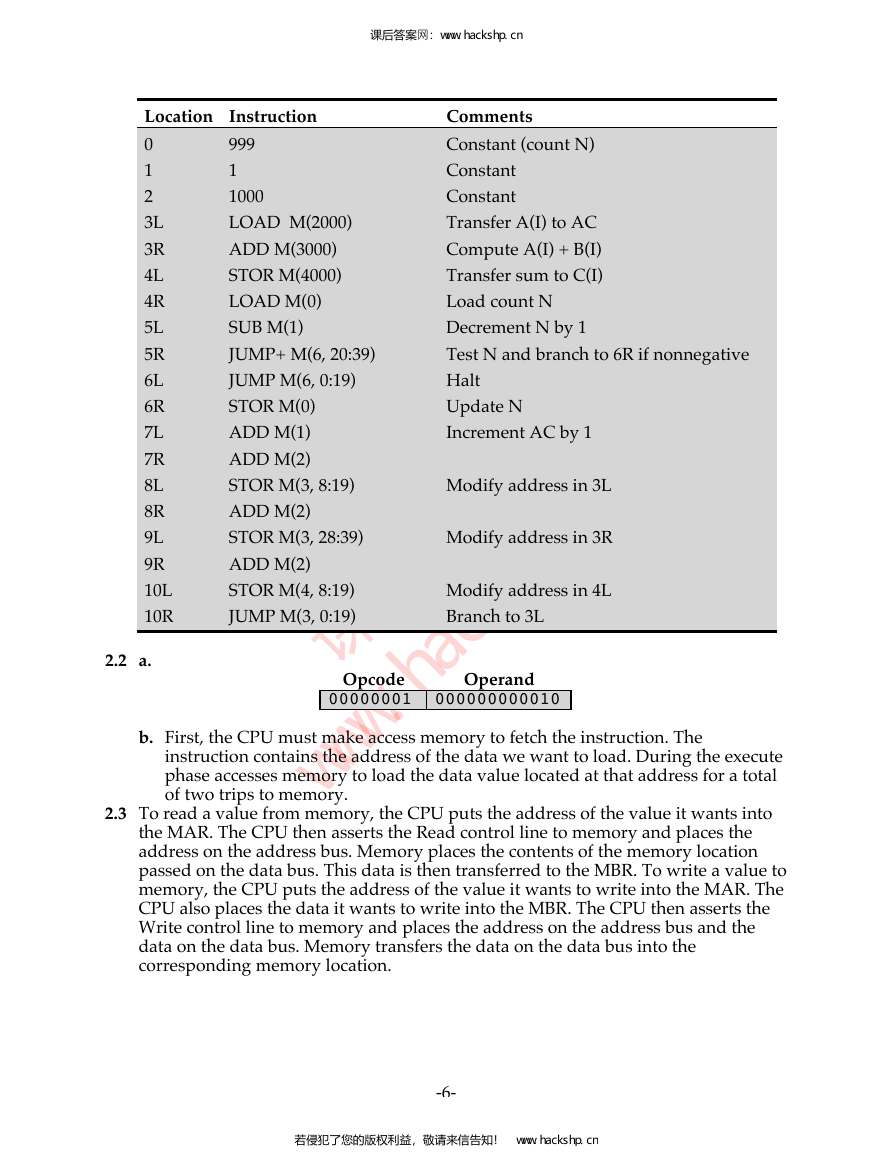

2.2 a.

Opcode

00000001

Operand

000000000010

b. First, the CPU must make access memory to fetch the instruction. The

instruction contains the address of the data we want to load. During the execute

phase accesses memory to load the data value located at that address for a total

of two trips to memory.

2.3 To read a value from memory, the CPU puts the address of the value it wants into

the MAR. The CPU then asserts the Read control line to memory and places the

address on the address bus. Memory places the contents of the memory location

passed on the data bus. This data is then transferred to the MBR. To write a value to

memory, the CPU puts the address of the value it wants to write into the MAR. The

CPU also places the data it wants to write into the MBR. The CPU then asserts the

Write control line to memory and places the address on the address bus and the

data on the data bus. Memory transfers the data on the data bus into the

corresponding memory location.

-6-

课后答案网 www.hackshp.cn课后答案网:www.hackshp.cn若侵犯了您的版权利益,敬请来信告知! www.hackshp.cn�

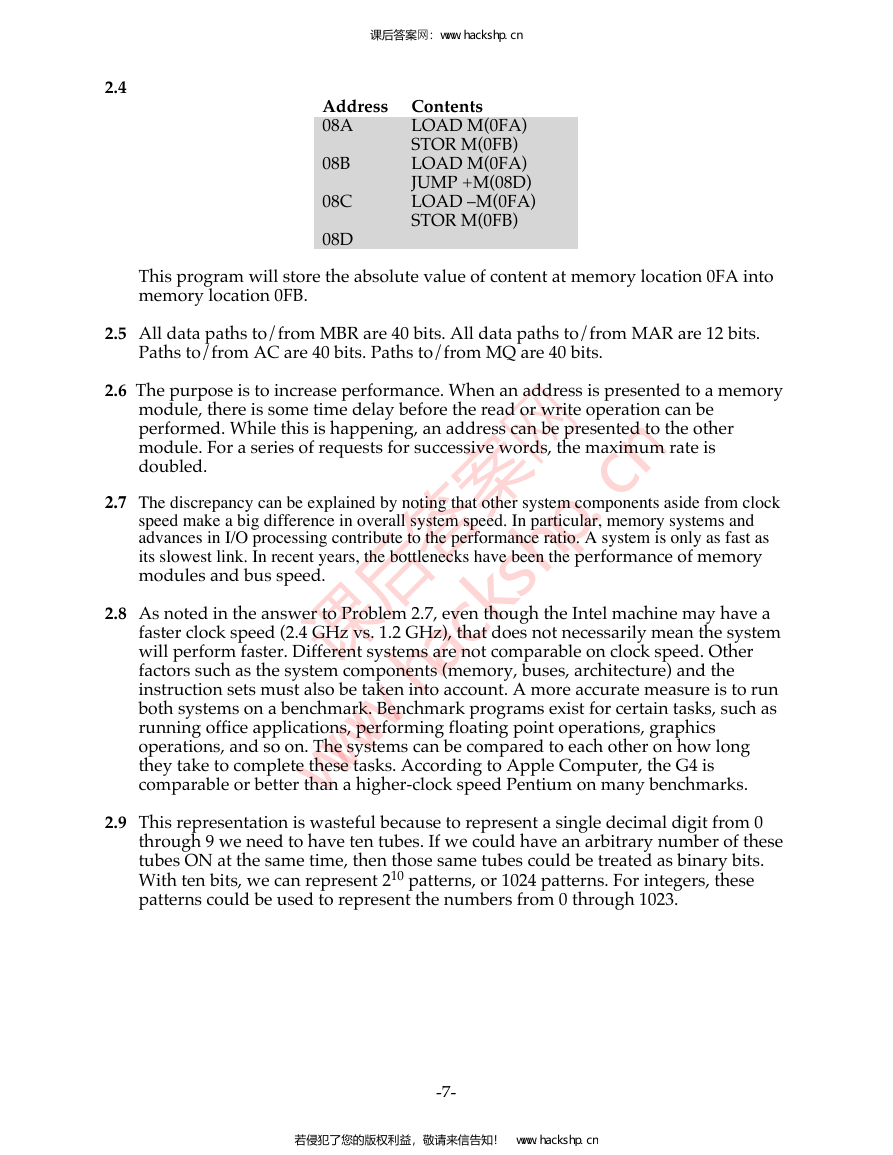

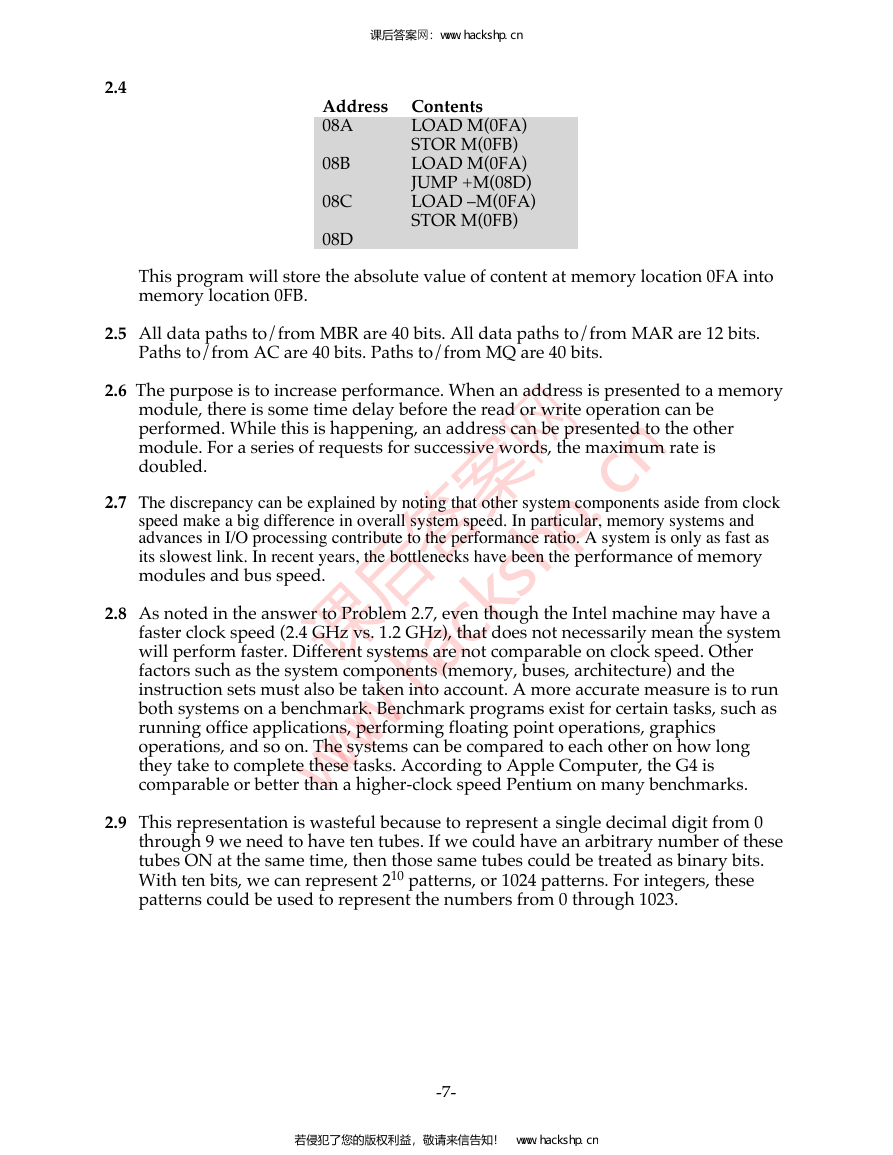

2.4

Address Contents

08A

08B

08C

08D

LOAD M(0FA)

STOR M(0FB)

LOAD M(0FA)

JUMP +M(08D)

LOAD –M(0FA)

STOR M(0FB)

This program will store the absolute value of content at memory location 0FA into

memory location 0FB.

2.5 All data paths to/from MBR are 40 bits. All data paths to/from MAR are 12 bits.

Paths to/from AC are 40 bits. Paths to/from MQ are 40 bits.

2.6 The purpose is to increase performance. When an address is presented to a memory

module, there is some time delay before the read or write operation can be

performed. While this is happening, an address can be presented to the other

module. For a series of requests for successive words, the maximum rate is

doubled.

2.7 The discrepancy can be explained by noting that other system components aside from clock

speed make a big difference in overall system speed. In particular, memory systems and

advances in I/O processing contribute to the performance ratio. A system is only as fast as

its slowest link. In recent years, the bottlenecks have been the performance of memory

modules and bus speed.

2.8 As noted in the answer to Problem 2.7, even though the Intel machine may have a

faster clock speed (2.4 GHz vs. 1.2 GHz), that does not necessarily mean the system

will perform faster. Different systems are not comparable on clock speed. Other

factors such as the system components (memory, buses, architecture) and the

instruction sets must also be taken into account. A more accurate measure is to run

both systems on a benchmark. Benchmark programs exist for certain tasks, such as

running office applications, performing floating point operations, graphics

operations, and so on. The systems can be compared to each other on how long

they take to complete these tasks. According to Apple Computer, the G4 is

comparable or better than a higher-clock speed Pentium on many benchmarks.

2.9 This representation is wasteful because to represent a single decimal digit from 0

through 9 we need to have ten tubes. If we could have an arbitrary number of these

tubes ON at the same time, then those same tubes could be treated as binary bits.

With ten bits, we can represent 210 patterns, or 1024 patterns. For integers, these

patterns could be used to represent the numbers from 0 through 1023.

-7-

课后答案网 www.hackshp.cn课后答案网:www.hackshp.cn若侵犯了您的版权利益,敬请来信告知! www.hackshp.cn�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc