Power Converter Design Using the Saber Simulator

A Step-By-Step Guide to the Design of a

Two-Switch, Voltage-Mode, Forward Converter

Using the Saber Simulator

1.0 Scope of Document

2.0 Specifications

2.1 Input Specifications

2.2 Output Specifications

2.3 Other Specifications

3.0 Step-By-Step Design Process

3.1 Open Loop Design

3.1.1 Define the Duty Cycle and Turns Ratio of the Transformer

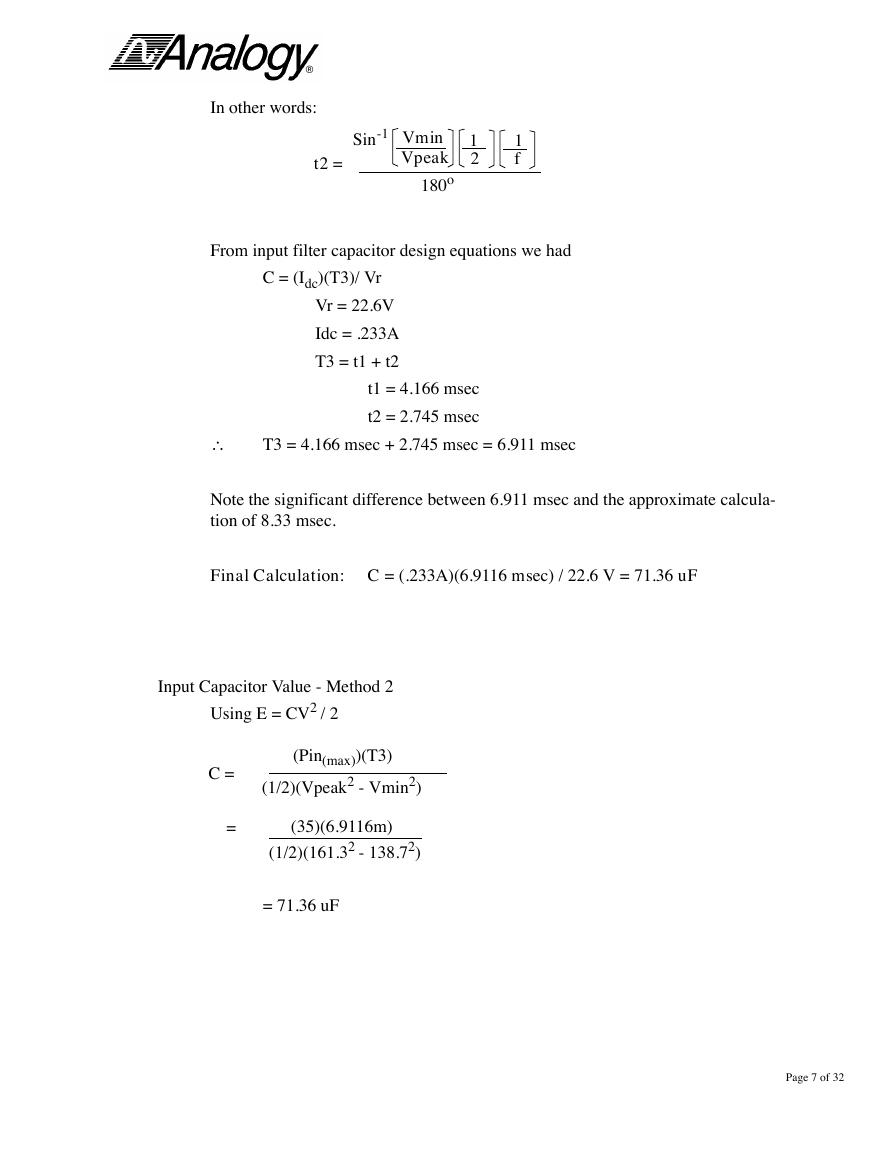

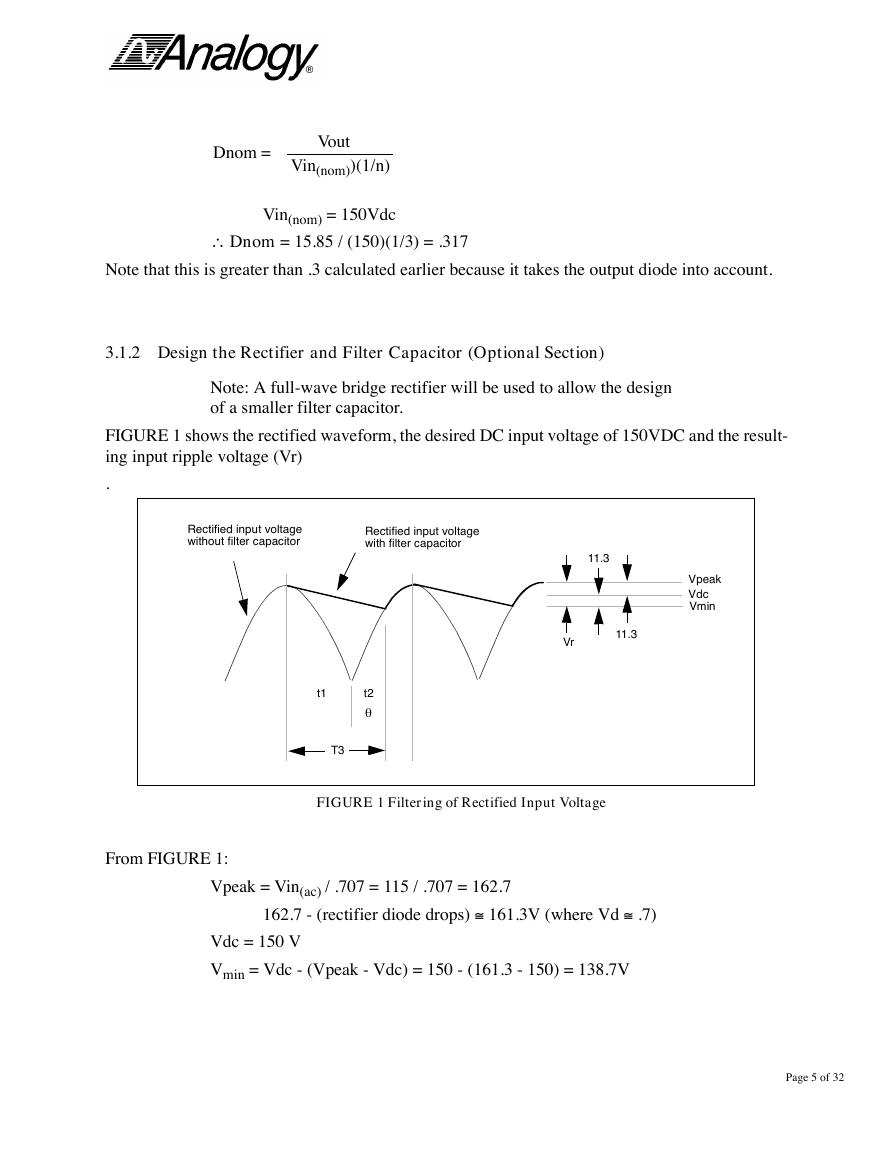

3.1.2 Design the Rectifier and Filter Capacitor (Optional Section)

FIGURE 1 Filtering of Rectified Input Voltage

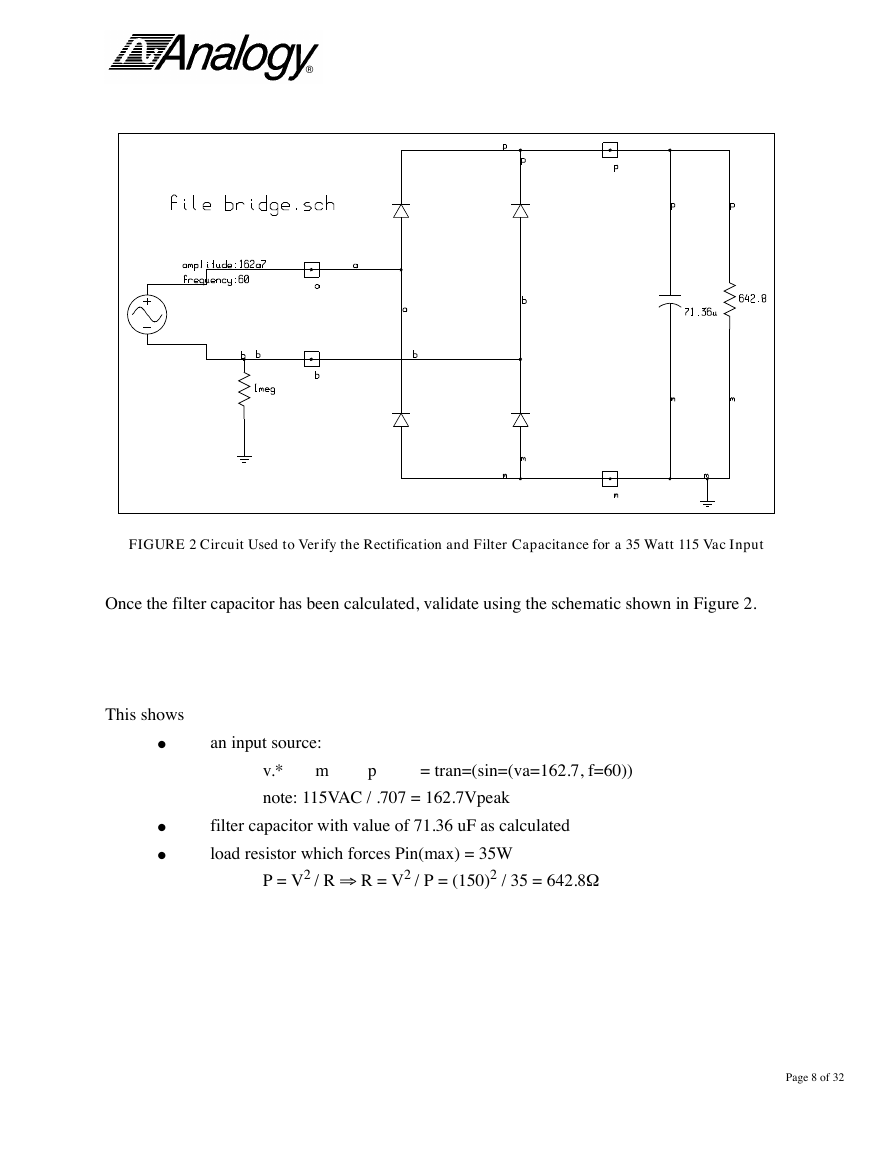

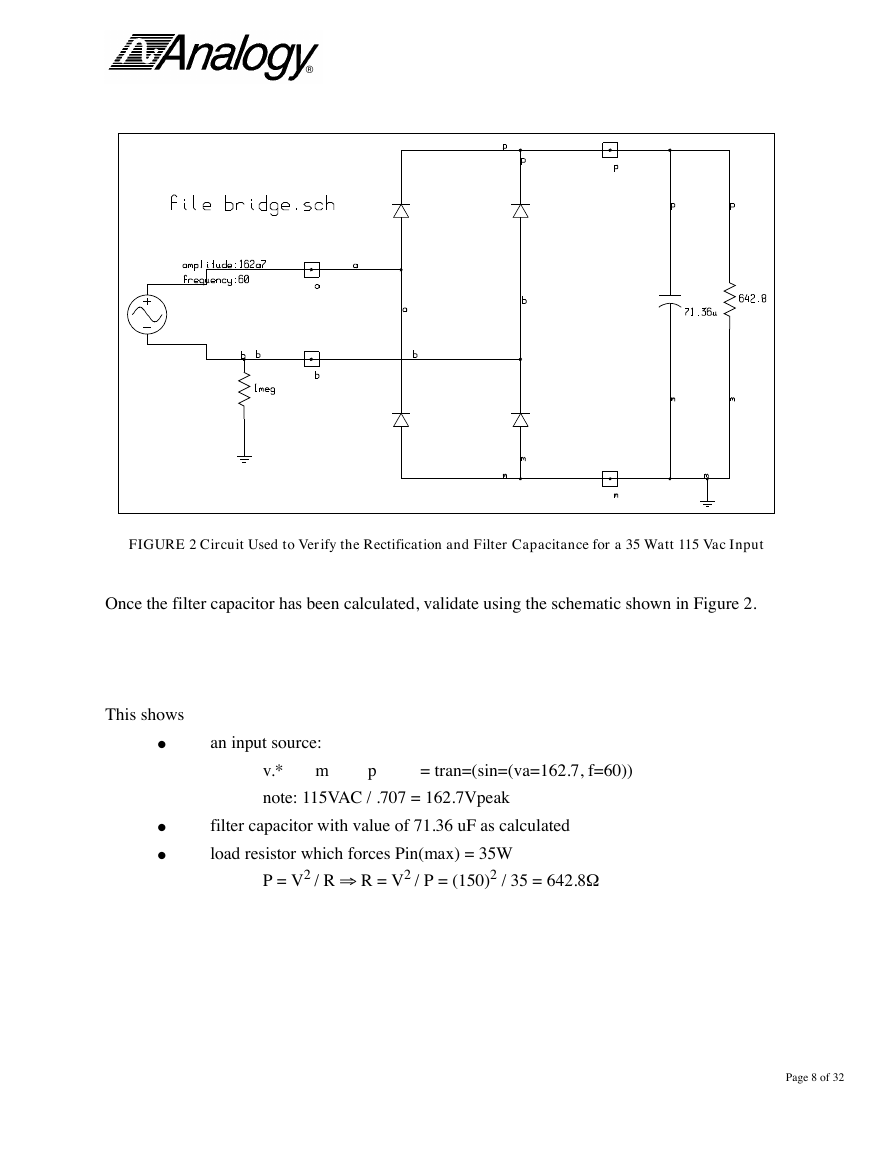

FIGURE 2 Circuit Used to Verify the Rectification and Filter Capacitance for a 35 Watt 115 Vac Input

3.1.2.1 Validate the Rectifier and Filter Capacitor using Saber

FIGURE 3 Voltage Across the Input Filter Capacitor

3.1.3 Output Filter Design

3.1.3.1 Inductor Design

FIGURE 4 Current through the Filter Inductor

FIGURE 5 Current Through Filter Inductor

3.1.3.2 Capacitor Design

3.1.4 Validate the Open Loop Design using Saber

FIGURE 6 Open Loop Configuration of the Forward Converter

FIGURE 7 Open Loop Simulation Results

FIGURE 8 Inductor Ripple Current

FIGURE 9 Output Ripple voltage

3.2 Compensator Design using an Averaged Model

FIGURE 10 Averaged Configuration of the Forward Converter

3.2.1 Validate the Averaged Model using Saber

FIGURE 11 Averaged Model vs. Switching Circuit

FIGURE 12 Inductor Current (Switching vs. Averaged)

FIGURE 13 Output Voltage (Switching vs. Averaged)

3.2.2 Open-Loop AC Analysis

FIGURE 14 Phase/Gain plot of the Control-to-Output transfer function

3.2.3 Designing the Compensation Circuit

FIGURE 15 Type 10 Compensation Network

3.2.4 Validate the Compensator Design using Saber

FIGURE 16 Phase/Gain plot (Post Compensator Design)

3.2.5 Validate the Closed Loop Parameters using Saber

FIGURE 17 Output Voltage

FIGURE 18 Duty Cycle and Control Voltage as solved by the system

3.3 Modulator Design and Closed Loop Simulation

FIGURE 19 Close Loop Configuration of the Forward Converter

FIGURE 20 Modulation Circuit Waveforms

3.3.1 Validate the Modulator Design using Saber

FIGURE 21 Validation of the Modulation Circuitry

FIGURE 22 Mixed Digital and Analog Waveforms of the Modulator

3.3.2 Validate the Closed Loop Design using Saber

FIGURE 23 Closed Loop Simulation using the Switching Circuitry

FIGURE 24 Duty cycle le results from the measurement model

3.4 Final Component Level Design

FIGURE 25 Component Level Design/Modeling of the Forward Converter

FIGURE 26 Error Amplifier’s inverting input & output, and ramp waveform from the 1825 PWM model

FIGURE 27 Output voltage and filer Inductor current waveforms

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc