版本信息:

版本

REV2019

时间

04/01/2019

Artix FPGA 修炼秘籍 DDR MIG (AXI4)

MA703FA-35T

电子版自学资料

常州一二三电子科技有限公司

溧阳米联电子科技有限公司

版权所有

米联客(MSXBO)04QQ 群:516869816

米联客(MSXBO)03QQ 群:543731097

米联客(MSXBO)02QQ 群:86730608

米联客(MSXBO)01QQ 群:34215299

�

常州一二三/溧阳米联电子科技有限公司 米联客 (MS XBO)www.osrc.cn Artix 修炼秘籍 2019 版 FDMA(AXI4)高级应用

版本

时间

描述

Rev2019

2019-04-01

首次更新,更新 AXI 自定义 MSXBO_FDMA 关于 DDR 读写测试,

视频缓存方案的 5 个例子。

第 2 页 共 54 页

�

常州一二三/溧阳米联电子科技有限公司 米联客 (MS XBO)www.osrc.cn Artix 修炼秘籍 2019 版 FDMA(AXI4)高级应用

感谢您使用米联客 Artix7 系列开发板,以及配套教程。本教程使用自定义AXI4 IP MSXBO_FDMA

对DDR进行读写控制。MSXBO_FDMA是基于AXI4封装的DMA控制器,可以非常方便地用于FPGA的

MIG控制器和ZYNQ上并实现对ZYNQ PS 或者PL的DDR进行读写控制。和官方的DMA以及VDMA相比,

FDMA具备无需驱动程序,只要会FP GA就能读写DDR的简单方便性。

软件版本:VIVADO2017.4

版权声明:

本手册版权归常州一二三电子科技有限公司/溧阳米联电子科技有限公司所有,并保留一切权利,

未经我司书面授权,擅自摘录或者修改本手册部分或者全部内容,我司有权追究其法律责任。

免费获取资料、答疑解惑到米联客(MSXBO) 官方论坛 www.osrc.cn

扫描以下二维码注册论坛:www.osrc.cn

获取最新产品发布、资料更新、技术焦点 关注 米联客 MSXBO 微信公众号

微信公众平台:米联客 MSXBO

第 3 页 共 54 页

�

常州一二三/溧阳米联电子科技有限公司 米联客 (MS XBO)www.osrc.cn Artix 修炼秘籍 2019 版 FDMA(AXI4)高级应用

目录

Artix FPGA 修炼秘籍 DDR MIG (AXI4) MA703FA-35T ....................................................................................... 1

CH01 基于 FDMA 内存读写测试........................................................................................................................... 5

1.1 概述 ........................................................................................................................................................ 5

1.2 基于 FDMA 搭建的 BD 工程 .................................................................................................................... 5

1.3 Setp By Step 搭建 FPGA BD 工程 .............................................................................................................. 6

1.4 编写 FDMA 测试代码 ............................................................................................................................ 20

1.5 测试代码状态机分析 .............................................................................................................................. 24

1.6 测试结果 ............................................................................................................................................... 25

CH02 基于 FDMA 实现多缓存视频构架 .............................................................................................................. 27

2.1 概述 ...................................................................................................................................................... 27

2.2 基于 FDMA 搭建的 BD 工程 .................................................................................................................. 27

2.3 基于 FDMA 多缓存视频构架 fdma_controller........................................................................................... 29

2.4 代码叠层结构 ........................................................................................................................................ 30

2.5 fdma_controller ....................................................................................................................................... 30

2.6 sensor_data_gen ...................................................................................................................................... 36

2.7 vga_lcd_driver.v...................................................................................................................................... 42

2.8 硬件连线 ............................................................................................................................................... 44

2.9 测试结果 ............................................................................................................................................... 44

CH03 基于 FDMA 实现 HDMI 视频输入输出 ...................................................................................................... 46

3.1 概述 ...................................................................................................................................................... 46

3.2 基于 FDMA 搭建的 BD 工程 .................................................................................................................. 46

3.3 基于 FDMA 多缓存视频构架 fdma_controller........................................................................................... 46

3.4 代码叠层结构 ........................................................................................................................................ 47

3.5 硬件连线 ............................................................................................................................................... 48

3.6 测试结果 ............................................................................................................................................... 48

CH04 基于 FDMA 实现 OV5640 摄像头视频采集 ................................................................................................ 49

4.1 概述 ...................................................................................................................................................... 49

4.2 基于 FDMA 搭建的 BD 工程 .................................................................................................................. 49

4.3 基于 FDMA 多缓存视频构架 fdma_controller........................................................................................... 49

4.4 代码叠层结构 ........................................................................................................................................ 50

4.5 摄像头安装 ............................................................................................................................................ 51

4.6 测试结果 ............................................................................................................................................... 51

CH05 基于 FDMA 实现 OV7725 摄像头视频采集 ................................................................................................ 52

5.1 概述 ...................................................................................................................................................... 52

5.2 基于 FDMA 搭建的 BD 工程 .................................................................................................................. 52

4.3 基于 FDMA 多缓存视频构架 fdma_controller........................................................................................... 52

5.4 代码叠层结构 ........................................................................................................................................ 53

5.5 摄像头安装 ............................................................................................................................................ 53

5.6 测试结果 ............................................................................................................................................... 54

第 4 页 共 54 页

�

常州一二三/溧阳米联电子科技有限公司 米联客 (MS XBO)www.osrc.cn Artix 修炼秘籍 2019 版 FDMA(AXI4)高级应用

CH01 基于 FDMA 内存读写测试

软件版本:VIVADO2017.4

操作系统:WIN10 64bit

硬件平台:ARTIX系列

米联客(MSXBO)论坛:www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问!!

1.1 概 述

FDMA 是 MSXBO(米联客的)基于 AXI4 总线协议定制的一个 DMA 控制器。有了这个 IP 我们可以统一

实现用 FPGA 代码直接读写 PL 的 DDR 或者 ZYNQ PS 的 DDR。

如果用过 ZYNQ 的都知道,要直接操作 PS 的 DDR 通常是 DMA 或者 VDMA,然而用过 XILINX 的 DMA IP

和 VDMA IP,总有一种遗憾,那就是不够灵活,还需要对寄存器配置,真是麻烦。对于我们搞 FPGA

的人来说,最喜欢直接了当,直接用 FPGA 代码搞定。现在 XILINX 的总线接口是 AXI4 总线,那么熟

练自定义 AXI4 IP 挂到总线上就非常方便了。基于这个目的,本小编定义了一个基于 AXI4 FULL MASTER

的 IP,暂且取名为 MSXBO_FDMA。

通过这个 IP 我们可以方便地进行 AXI4 FULL MASTER 的操作,比如我们经常要读写 DDR,那么只

要挂到 AXI4 总线上就可以利用这个 IP 实现。

以下是小编展示了一种在 XC7A35T FPGA 上的读写测试方案。

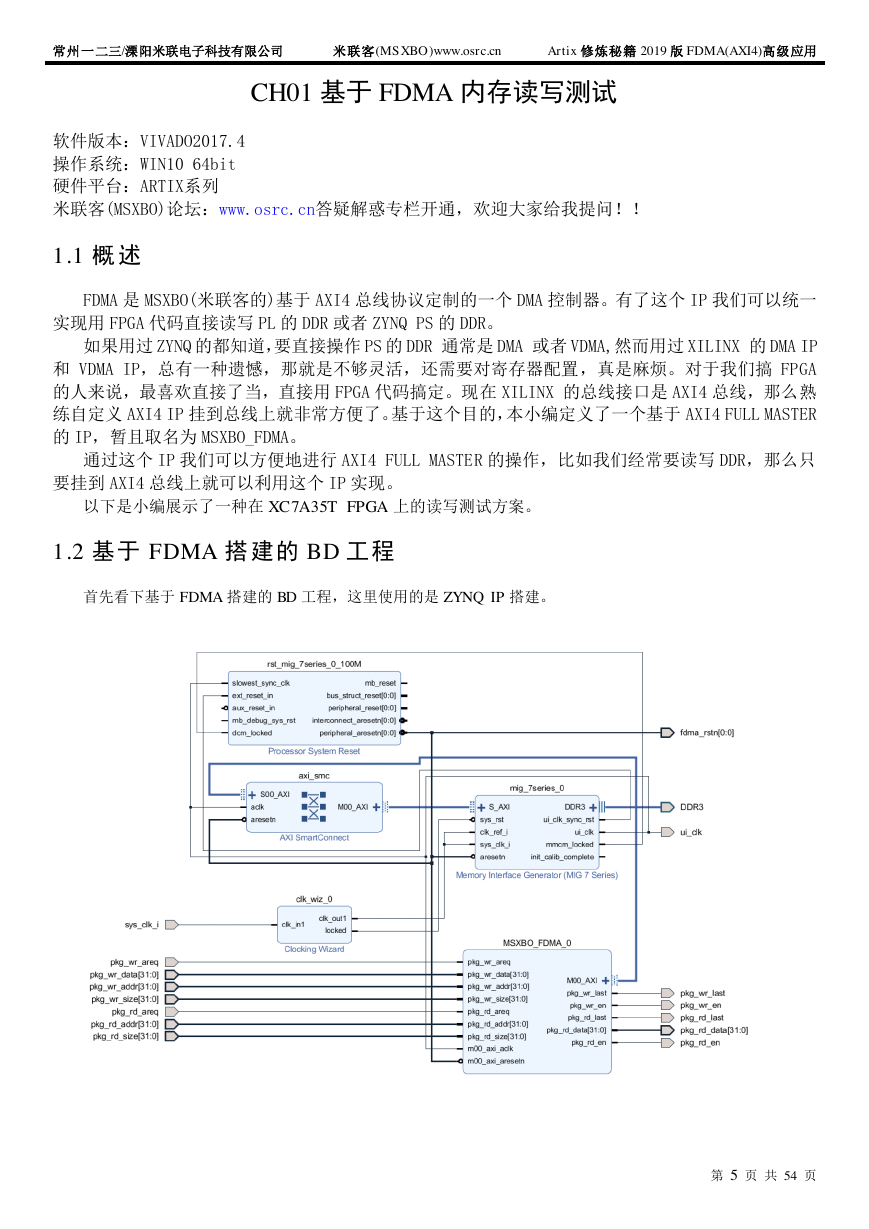

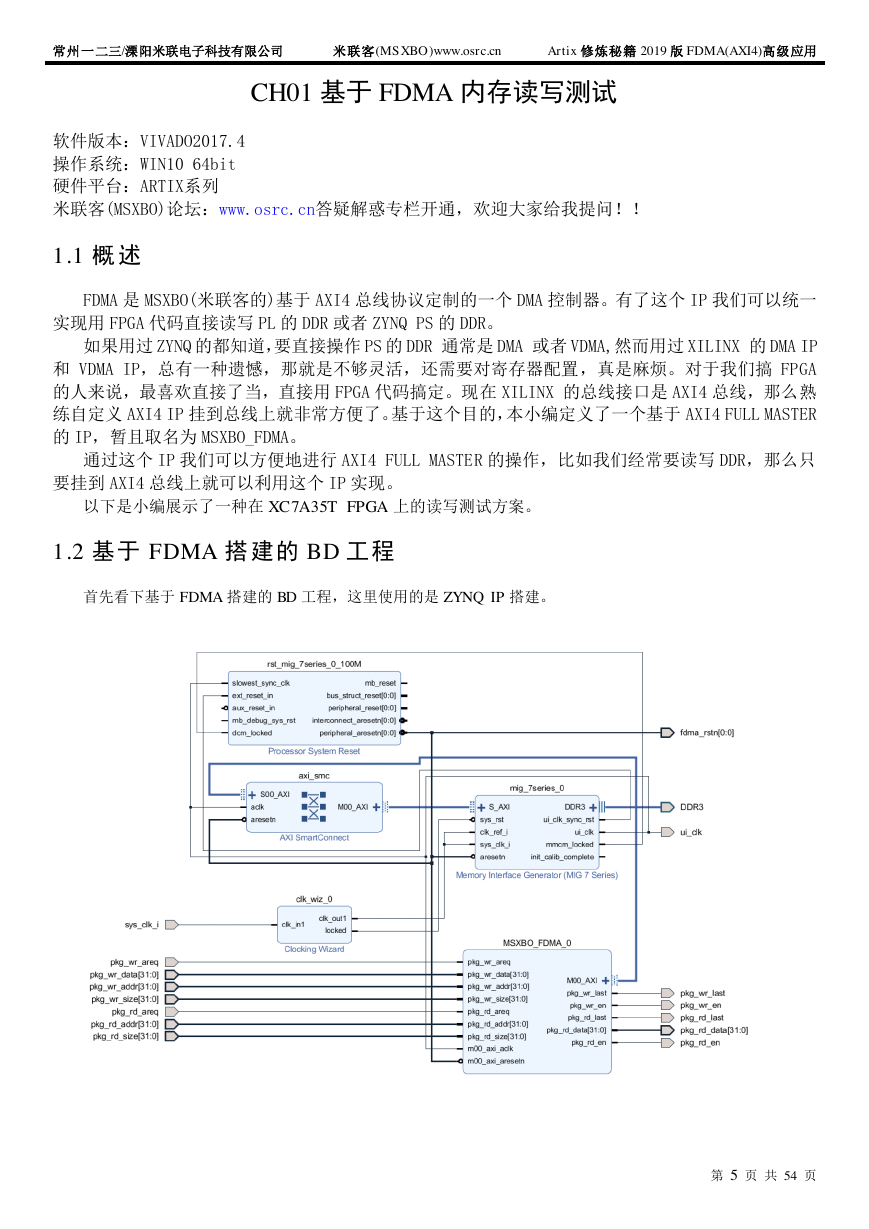

1.2 基于 FDMA 搭 建的 BD 工程

首先看下基于 FDMA 搭建的 BD 工程,这里使用的是 ZYNQ IP 搭建。

第 5 页 共 54 页

�

常州一二三/溧阳米联电子科技有限公司 米联客 (MS XBO)www.osrc.cn Artix 修炼秘籍 2019 版 FDMA(AXI4)高级应用

1.3 Setp By Step 搭 建 FPGA BD 工 程

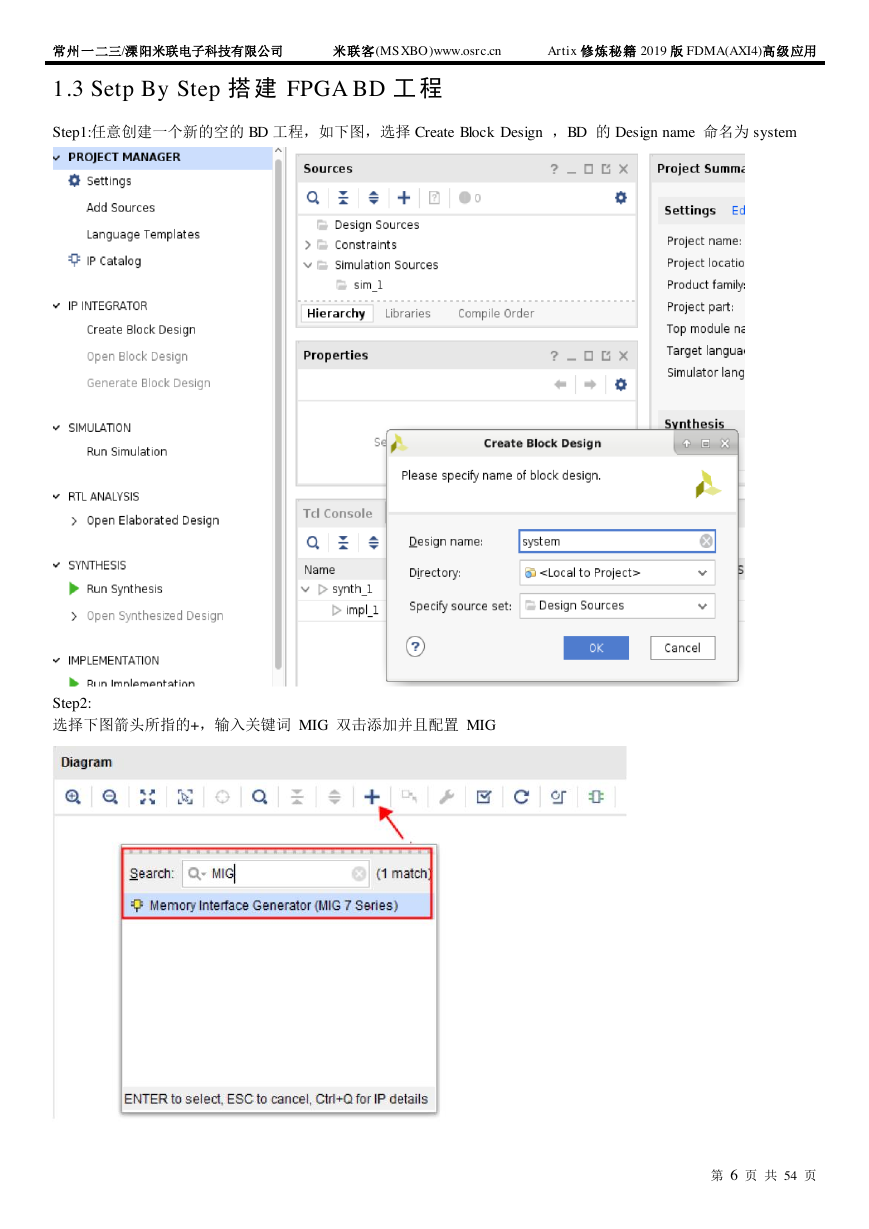

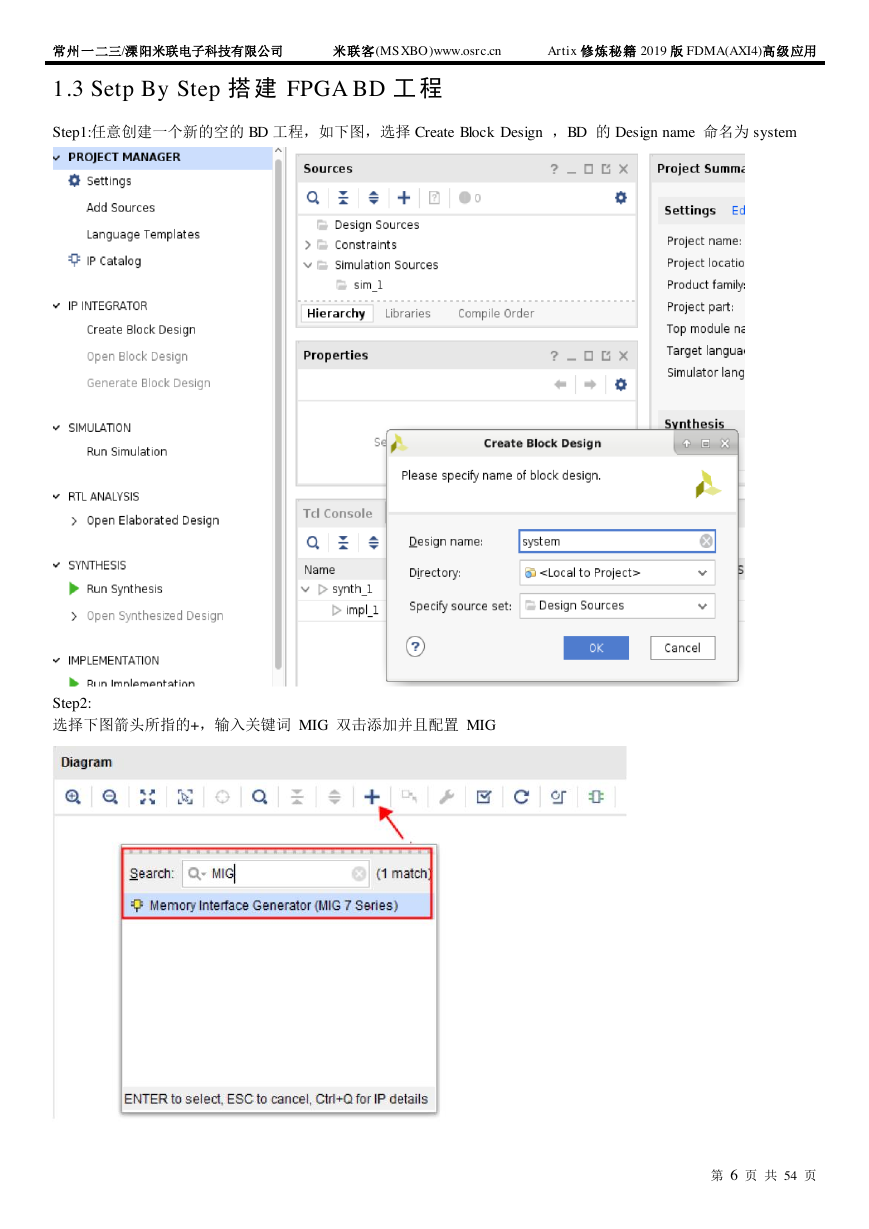

Step1:任意创建一个新的空的 BD 工程,如下图,选择 Create Block Design ,BD 的 Design name 命名为 system

Step2:

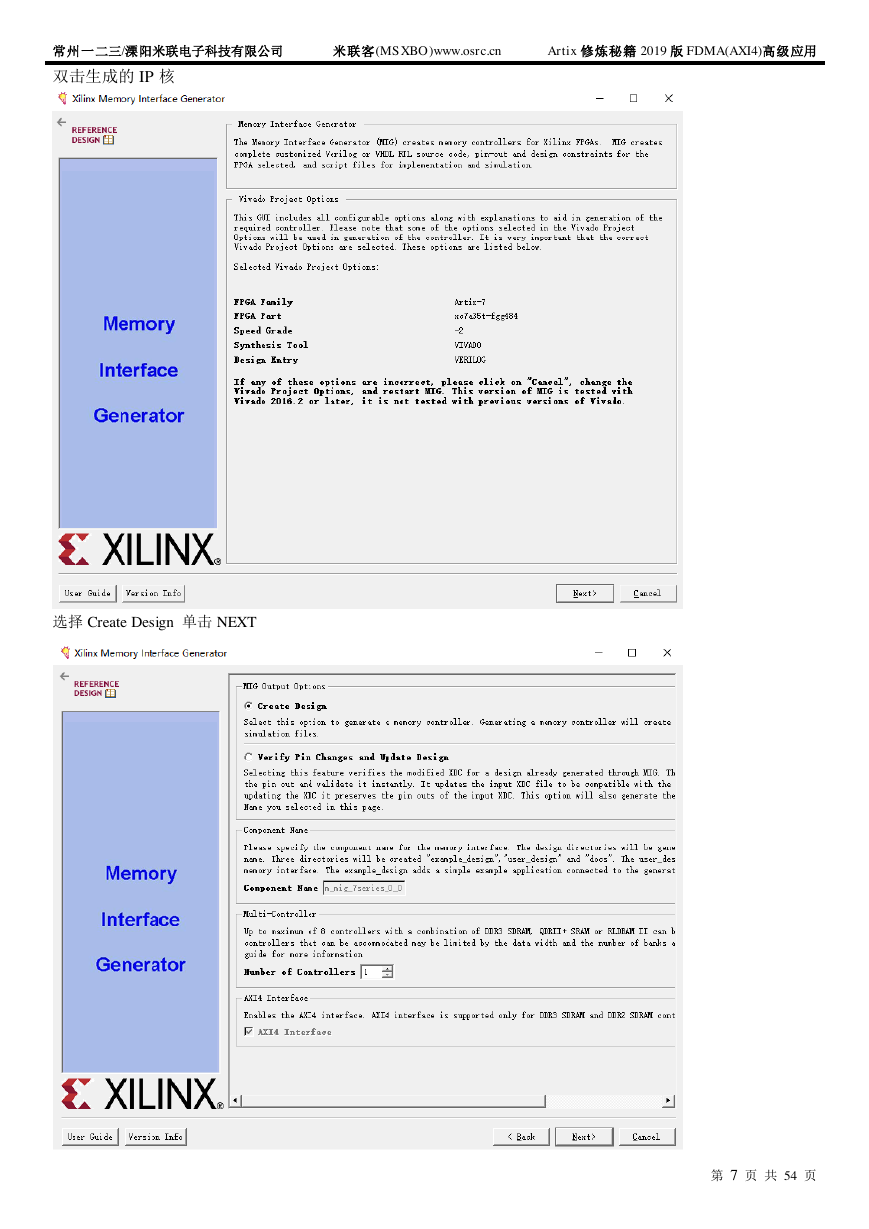

选择下图箭头所指的+,输入关键词 MIG 双击添加并且配置 MIG

第 6 页 共 54 页

�

常州一二三/溧阳米联电子科技有限公司 米联客 (MS XBO)www.osrc.cn Artix 修炼秘籍 2019 版 FDMA(AXI4)高级应用

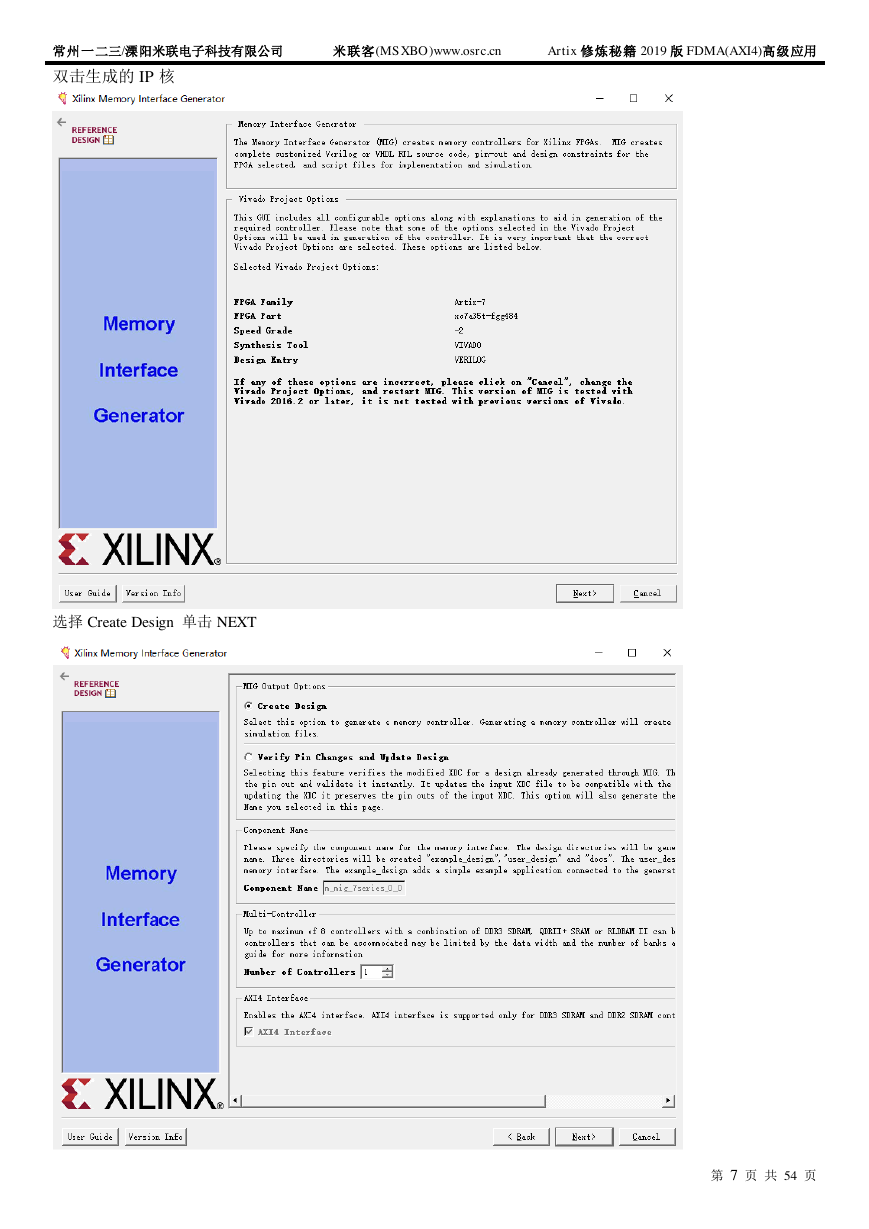

双击生成的 IP 核

选择 Create Design 单击 NEXT

第 7 页 共 54 页

�

常州一二三/溧阳米联电子科技有限公司 米联客 (MS XBO)www.osrc.cn Artix 修炼秘籍 2019 版 FDMA(AXI4)高级应用

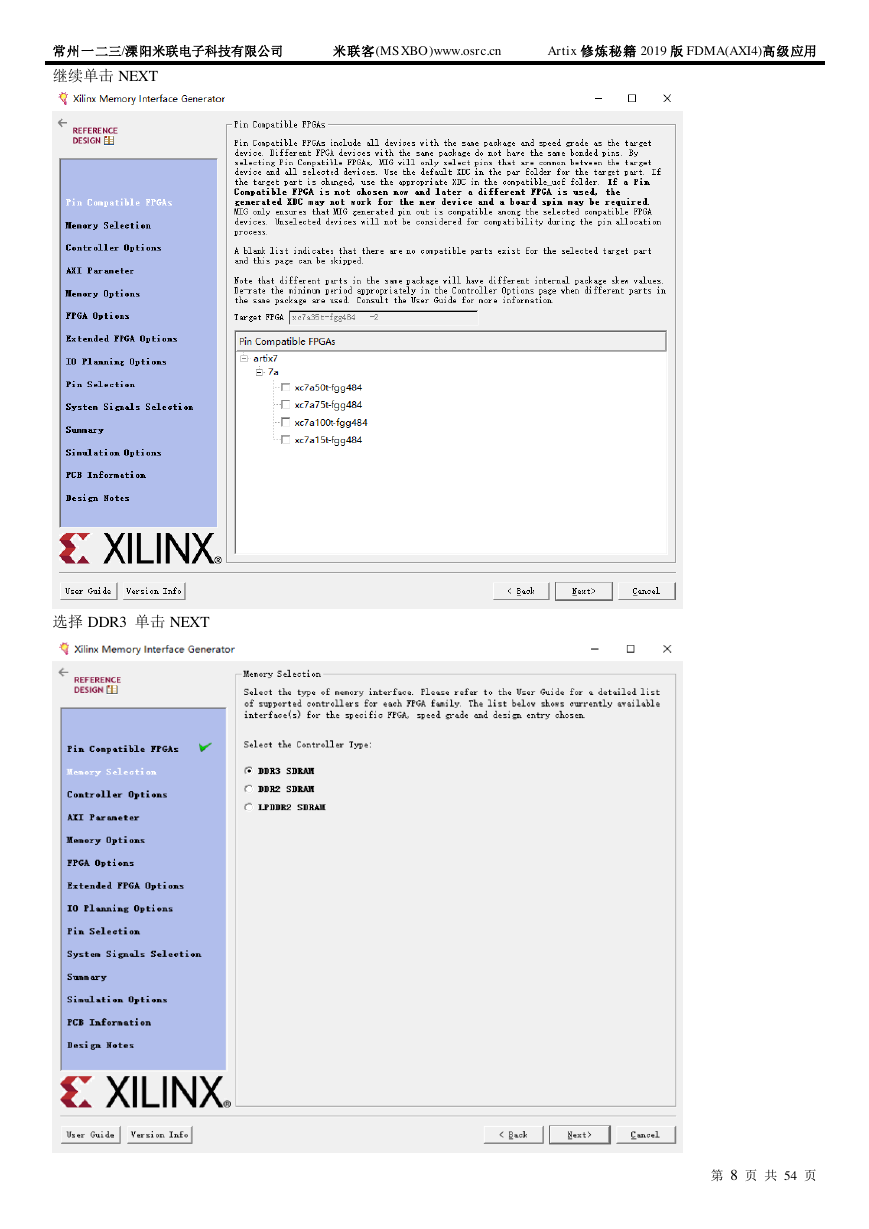

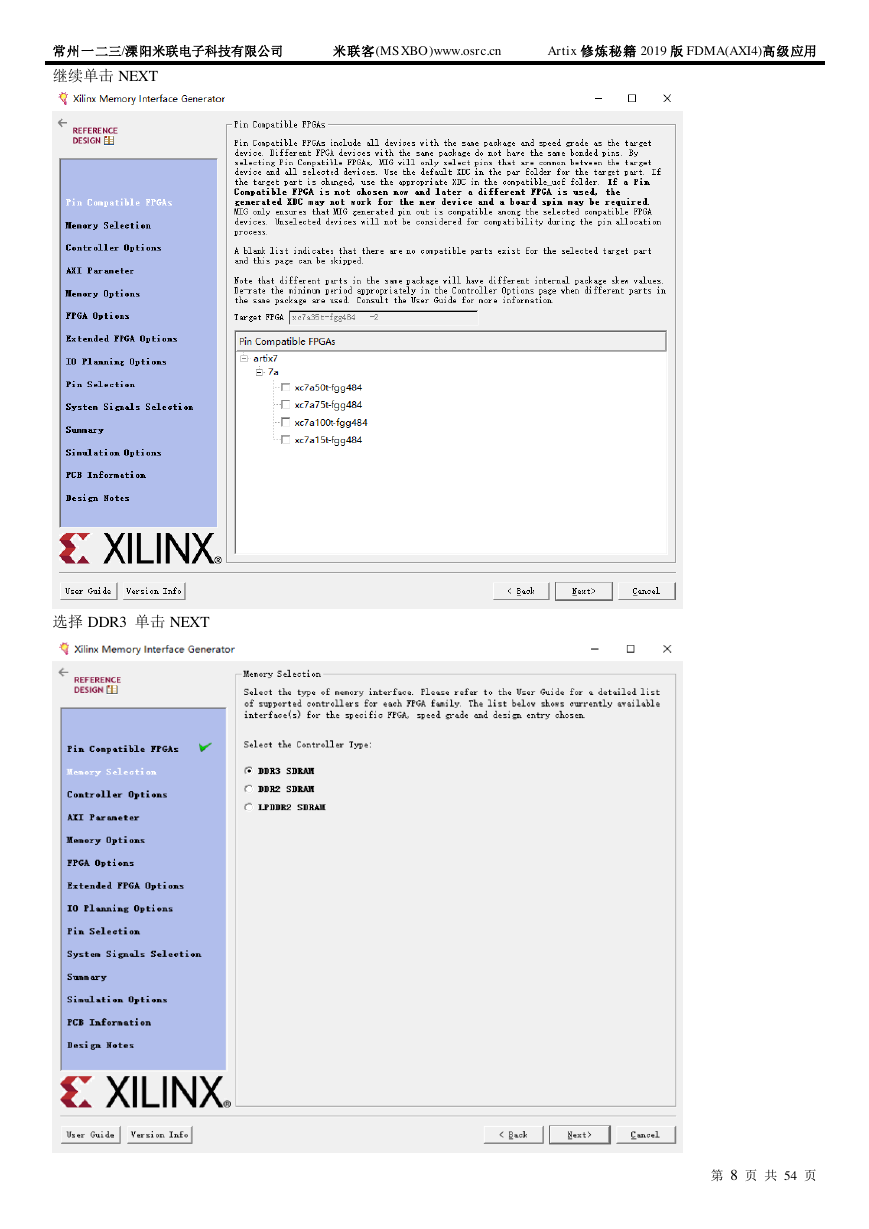

继续单击 NEXT

选择 DDR3 单击 NEXT

第 8 页 共 54 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc