101 条 Verilog 和 SystemVerilog 设计陷阱

Verilog and SystemVerilog Gotchas:101 Common

Coding Errors and How to Avoid Them(2007)

洋文馆

2014 年 3 月 10 日

�

感谢

To my wonderful wife, LeeAnn, and my children, Ammon, Tamara, Hannah, Sethand Samuel-thank you for your

patience during the many long hours and late nights you tolerated while this book was being written.

1

StuSutherland

Portland, Oregon

To my wife and sweetheart GeriJean, andmychildren, Sara, Kirsten, Adam, Alex, Dillan, Donnelle, GrantandGina-

thanks to each of you for the patience you have had with me as I have dealt with debugging many of these gotchas

on designs over the years.

DonMills

Chandler, Arizona

著者介绍

Mr. Stuart Sutherland is a member of the IEEE 1800 working group that oversees both the Verilog and SystemVer-

ilog standards. He has been involved with the definition of the Verilog standard since its inception in 1993, and

the SystemVerilog standard sinceworkbegan in 200I. In addition, Stuart is the technical editor of the official IEEE

Verilog and SystemVerilog Language Reference Manuals (LRMs). Stuart is an independent Verilog consultant,

specializing in providing comprehensive expert training on the Verilog HDL, SystemVerilog and PLI. Stuart is a

co-author of the books ”SystemVerilog for Design”, ”Verilog-2001: A Guide to the New Features in the Verilog

Hardware Description Language” and is the author of ”The Verilog PLl Handbook”, as well as the popular ”Verilog

HDL Quick Reference Guide” and”Verilog PLl Quick Reference Guide”.He has also authored a number of techni-

cal papers on Verilog and SystemVerilog, which are available at www.sutherland-hdl.com/papers. You can contact

Stuart at stuart@sutherland-hdl.com.

visit the author’s web page at www.sutherland-hdl.com

Mr.Don Mills has been involved in ASIC design since 1986. During that time, he has worked on more than 30

ASIC projects. Don started using top-down design methodology in 1991 (Synopsys Design Compiler 1.2). Don

has developed and implemented top-down ASIC design flows at several companies. His specialty is integrat-

ing tools and automating the flow. Don works for Microchip Technology Inc. as an internal SystemVerilog and

Verilog consultant. Don is a member of the IEEE Verilog and System Verilog committees that are working on

language issues and enhancements. Don has authored and co-authored numerous papers, such as ”SystemVer-

ilog Assertions are for Design Engineers Too!” and ”RTL Coding Styles that Yield Simulation and Synthesis Mis-

matches”. Copies of these papers can be found at www.lcdm-eng.com.Mr. Mills can be reached at mills@lcdm-

eng.comordon.mills@microchip.com.

visit the author’s web page at www.lcdm-eng.com

致谢

The authors express their sincere appreciation to the contributions of several Verilog and SystemVerilog experts.

Chris Spear of Synopsys, Inc. suggested several of the verification related gotchas, provided the general de-

scriptions of these gotchas, and ran countless tests for us.

Shalom Bresticker of Intel also suggested several gotchas.

Jonathan Bromley of Doulos, Ltd., Clifford Cummings of Sunburst Design, Tom Fitzpatrick of Mentor Graphics,

Steve Golson of Trilobyte Systems, Gregg Lahti of Microchip Technology, Inc. and Chris Spear of Synopsys, Inc.

provided thorough technical reviews of this book, and offered invaluable comments on how to improve th egotcha

descriptions.

�

Steve Golson of Trilobyte Systems provided a wonderful foreword to this book Lastly, we acknowledge and ex-

press our gratitude to our wives, LeeAnn Sutherland and Geri Jean Mills, for meticulously reviewing this book for

grammar and punctuation. If any such errata remain in the book, it could only be due to changes we made after

their reviews.

2

�

目录

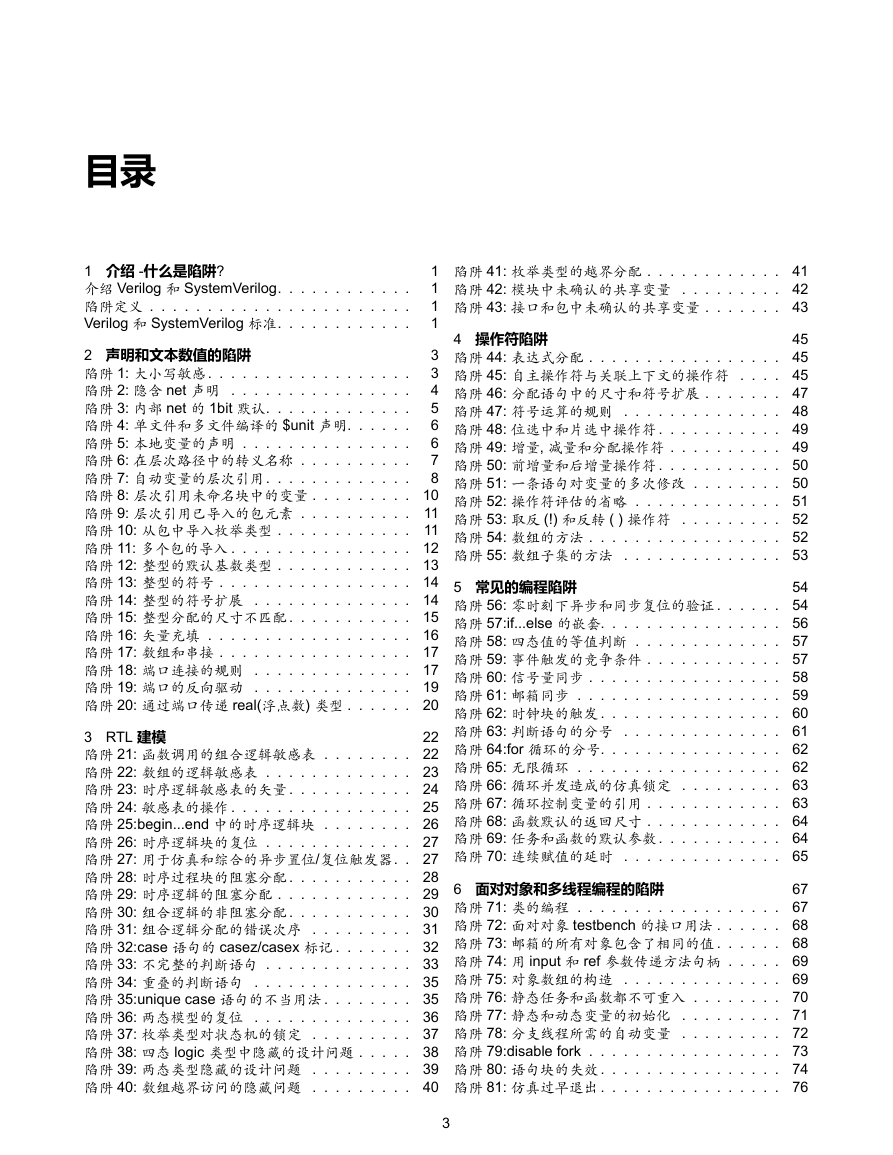

1 介绍 -什么是陷阱?

介绍 Verilog 和 SystemVerilog. . . . . . . . . . . .

陷阱定义 . . . . . . . . . . . . . . . . . . . . . . .

Verilog 和 SystemVerilog 标准. . . . . . . . . . . .

1

1

1

1

3

2 声明和文本数值的陷阱

3

陷阱 1: 大小写敏感. . . . . . . . . . . . . . . . . .

4

陷阱 2: 隐含 net 声明 . . . . . . . . . . . . . . . .

5

陷阱 3: 内部 net 的 1bit 默认. . . . . . . . . . . . .

6

陷阱 4: 单文件和多文件编译的 $unit 声明. . . . . .

6

陷阱 5: 本地变量的声明 . . . . . . . . . . . . . . .

7

陷阱 6: 在层次路径中的转义名称 . . . . . . . . . .

8

陷阱 7: 自动变量的层次引用. . . . . . . . . . . . .

陷阱 8: 层次引用未命名块中的变量 . . . . . . . . . 10

陷阱 9: 层次引用已导入的包元素 . . . . . . . . . . 11

陷阱 10: 从包中导入枚举类型 . . . . . . . . . . . . 11

陷阱 11: 多个包的导入 . . . . . . . . . . . . . . . . 12

陷阱 12: 整型的默认基数类型 . . . . . . . . . . . . 13

陷阱 13: 整型的符号 . . . . . . . . . . . . . . . . . 14

陷阱 14: 整型的符号扩展 . . . . . . . . . . . . . . 14

陷阱 15: 整型分配的尺寸不匹配 . . . . . . . . . . . 15

陷阱 16: 矢量充填 . . . . . . . . . . . . . . . . . . 16

陷阱 17: 数组和串接 . . . . . . . . . . . . . . . . . 17

陷阱 18: 端口连接的规则 . . . . . . . . . . . . . . 17

陷阱 19: 端口的反向驱动 . . . . . . . . . . . . . . 19

陷阱 20: 通过端口传递 real(浮点数) 类型 . . . . . . 20

3 RTL 建模

22

陷阱 21: 函数调用的组合逻辑敏感表 . . . . . . . . 22

陷阱 22: 数组的逻辑敏感表 . . . . . . . . . . . . . 23

陷阱 23: 时序逻辑敏感表的矢量 . . . . . . . . . . . 24

陷阱 24: 敏感表的操作 . . . . . . . . . . . . . . . . 25

陷阱 25:begin...end 中的时序逻辑块 . . . . . . . . 26

陷阱 26: 时序逻辑块的复位 . . . . . . . . . . . . . 27

陷阱 27: 用于仿真和综合的异步置位/复位触发器. . 27

陷阱 28: 时序过程块的阻塞分配 . . . . . . . . . . . 28

陷阱 29: 时序逻辑的阻塞分配 . . . . . . . . . . . . 29

陷阱 30: 组合逻辑的非阻塞分配 . . . . . . . . . . . 30

陷阱 31: 组合逻辑分配的错误次序 . . . . . . . . . 31

陷阱 32:case 语句的 casez/casex 标记 . . . . . . . 32

陷阱 33: 不完整的判断语句 . . . . . . . . . . . . . 33

陷阱 34: 重叠的判断语句 . . . . . . . . . . . . . . 35

陷阱 35:unique case 语句的不当用法 . . . . . . . . 35

陷阱 36: 两态模型的复位 . . . . . . . . . . . . . . 36

陷阱 37: 枚举类型对状态机的锁定 . . . . . . . . . 37

陷阱 38: 四态 logic 类型中隐藏的设计问题 . . . . . 38

陷阱 39: 两态类型隐藏的设计问题 . . . . . . . . . 39

陷阱 40: 数组越界访问的隐藏问题 . . . . . . . . . 40

陷阱 41: 枚举类型的越界分配 . . . . . . . . . . . . 41

陷阱 42: 模块中未确认的共享变量 . . . . . . . . . 42

陷阱 43: 接口和包中未确认的共享变量 . . . . . . . 43

4 操作符陷阱

45

陷阱 44: 表达式分配 . . . . . . . . . . . . . . . . . 45

陷阱 45: 自主操作符与关联上下文的操作符 . . . . 45

陷阱 46: 分配语句中的尺寸和符号扩展 . . . . . . . 47

陷阱 47: 符号运算的规则 . . . . . . . . . . . . . . 48

陷阱 48: 位选中和片选中操作符 . . . . . . . . . . . 49

陷阱 49: 增量, 减量和分配操作符 . . . . . . . . . . 49

陷阱 50: 前增量和后增量操作符 . . . . . . . . . . . 50

陷阱 51: 一条语句对变量的多次修改 . . . . . . . . 50

陷阱 52: 操作符评估的省略 . . . . . . . . . . . . . 51

陷阱 53: 取反 (!) 和反转 ( ) 操作符 . . . . . . . . . 52

陷阱 54: 数组的方法 . . . . . . . . . . . . . . . . . 52

陷阱 55: 数组子集的方法 . . . . . . . . . . . . . . 53

5 常见的编程陷阱

54

陷阱 56: 零时刻下异步和同步复位的验证 . . . . . . 54

陷阱 57:if...else 的嵌套. . . . . . . . . . . . . . . . 56

陷阱 58: 四态值的等值判断 . . . . . . . . . . . . . 57

陷阱 59: 事件触发的竞争条件 . . . . . . . . . . . . 57

陷阱 60: 信号量同步 . . . . . . . . . . . . . . . . . 58

陷阱 61: 邮箱同步 . . . . . . . . . . . . . . . . . . 59

陷阱 62: 时钟块的触发 . . . . . . . . . . . . . . . . 60

陷阱 63: 判断语句的分号 . . . . . . . . . . . . . . 61

陷阱 64:for 循环的分号. . . . . . . . . . . . . . . . 62

陷阱 65: 无限循环 . . . . . . . . . . . . . . . . . . 62

陷阱 66: 循环并发造成的仿真锁定 . . . . . . . . . 63

陷阱 67: 循环控制变量的引用 . . . . . . . . . . . . 63

陷阱 68: 函数默认的返回尺寸 . . . . . . . . . . . . 64

陷阱 69: 任务和函数的默认参数 . . . . . . . . . . . 64

陷阱 70: 连续赋值的延时 . . . . . . . . . . . . . . 65

6 面对对象和多线程编程的陷阱

67

陷阱 71: 类的编程 . . . . . . . . . . . . . . . . . . 67

陷阱 72: 面对对象 testbench 的接口用法 . . . . . . 68

陷阱 73: 邮箱的所有对象包含了相同的值 . . . . . . 68

陷阱 74: 用 input 和 ref 参数传递方法句柄 . . . . . 69

陷阱 75: 对象数组的构造 . . . . . . . . . . . . . . 69

陷阱 76: 静态任务和函数都不可重入 . . . . . . . . 70

陷阱 77: 静态和动态变量的初始化 . . . . . . . . . 71

陷阱 78: 分支线程所需的自动变量 . . . . . . . . . 72

陷阱 79:disable fork . . . . . . . . . . . . . . . . . 73

陷阱 80: 语句块的失效 . . . . . . . . . . . . . . . . 74

陷阱 81: 仿真过早退出 . . . . . . . . . . . . . . . . 76

3

�

目录

4

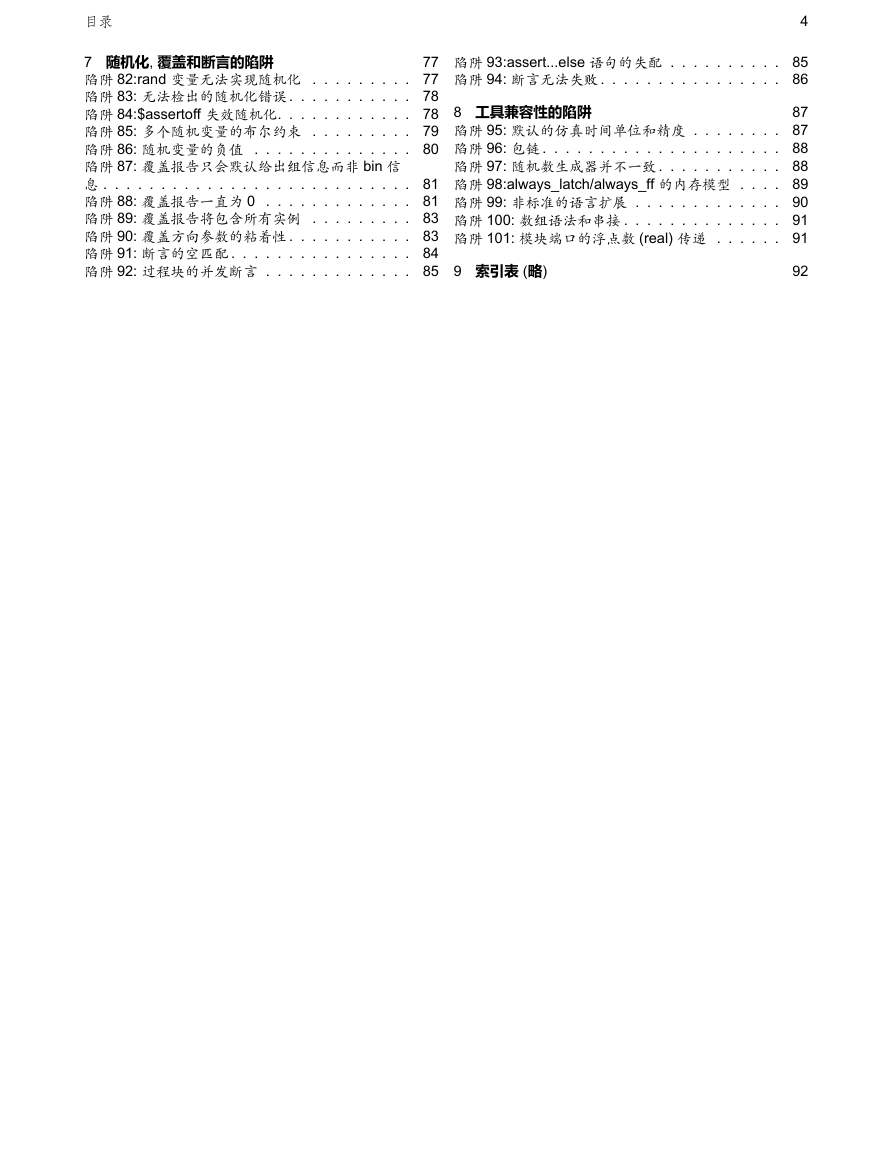

7 随机化, 覆盖和断言的陷阱

77

陷阱 82:rand 变量无法实现随机化 . . . . . . . . . 77

陷阱 83: 无法检出的随机化错误 . . . . . . . . . . . 78

陷阱 84:$assertoff 失效随机化. . . . . . . . . . . . 78

陷阱 85: 多个随机变量的布尔约束 . . . . . . . . . 79

陷阱 86: 随机变量的负值 . . . . . . . . . . . . . . 80

陷阱 87: 覆盖报告只会默认给出组信息而非 bin 信

息 . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

陷阱 88: 覆盖报告一直为 0 . . . . . . . . . . . . . 81

陷阱 89: 覆盖报告将包含所有实例 . . . . . . . . . 83

陷阱 90: 覆盖方向参数的粘着性 . . . . . . . . . . . 83

陷阱 91: 断言的空匹配 . . . . . . . . . . . . . . . . 84

陷阱 92: 过程块的并发断言 . . . . . . . . . . . . . 85

陷阱 93:assert...else 语句的失配 . . . . . . . . . . 85

陷阱 94: 断言无法失败 . . . . . . . . . . . . . . . . 86

87

8 工具兼容性的陷阱

陷阱 95: 默认的仿真时间单位和精度 . . . . . . . . 87

陷阱 96: 包链 . . . . . . . . . . . . . . . . . . . . . 88

陷阱 97: 随机数生成器并不一致 . . . . . . . . . . . 88

陷阱 98:always_latch/always_ff 的内存模型 . . . . 89

陷阱 99: 非标准的语言扩展 . . . . . . . . . . . . . 90

陷阱 100: 数组语法和串接 . . . . . . . . . . . . . . 91

陷阱 101: 模块端口的浮点数 (real) 传递 . . . . . . 91

9 索引表 (略)

92

�

目录

序

5

有些人喜欢收集棒球卡片, 老的车辆杂志, 或是橡皮小鸭. 但我喜欢收集 Verilog 书籍.

从 1989 年那个三孔活页夹中保存的 Gateway VERILOG-XL Reference Manual Version I.5a 复印本开始, 那时

的 Verilog 很简单, 其中只包含了一种过程赋值 (那时的语言并没有包含非阻塞赋值), 它很难让我们相信有一天能够

使用它来设计芯片, 我们可以在 VAX 或是昂贵的 Apollo 工作站上进行仿真.

从那开始我购买了相当多的 Verilog 书籍, 其中包含了少量的综合书籍, 还有一份介绍硬件描述语言历史的文

本, 其中的一小部分介绍了 VHDL, 这些书籍中大部分都是关于 Verilog.

但有趣的是, 我并没有花很多时间来阅读它们, 它们只是被搁置在书架上, 我承认书架上摆满了关于 Verilog 的

书籍时, 是一件令人骄傲的事情, 但目光如炬的参观者能发现它们都是全新的从未被阅读过, 拥有未使用过和未阅读

过的书籍都是无意义的.

另一方面让我沮丧, 从这些书籍中只能找到很少一部分, 对于工程师有价值的内容, 我能否找到一本需天天使

用的书籍, 有利于我入门以及在工作中及时参阅.

Stu 和 Don 编写的就是这样一本书, 了解这些技巧我花费了很多年的时间, 其中内容甚至让我怀疑, 自己是否

了解 Verilog, 在这本能提供帮助和有价值的书籍中, 给出的一些知识点都是经过提炼的, 相信你不会感到沮丧.

如果你是一个老手, 验证这些技巧也需通过相当困难的方式, 但你可笑着对自己说:” 好的, 我找到它了.”.

如果你是新手, 快点跟随两位专家开始学习吧, 不要犹豫快点来参加两位绅士提供的一次培训课程, 我保证你

不会遗憾.

我最喜欢的陷阱是第 65 条: 循环是无限的, 为什么? 可以构建一个调试它的环境, 相信我, 如果建模错误会引

发芯片损坏时, 你就不会忘记错误为什么会出现? 可惜这本书我没有早点遇到, 无疑你是幸运的, 把这本书放在手边,

经常参阅, 它可帮助你解决所有的模型编译和项目设计的困难.

Steve Golson

Trilobyte Systems

http://www.trilobyte.com

�

介绍 -什么是陷阱?

本章将定义什么是陷阱, 为什么编程语言会容忍陷阱, 为了扩充你的知识面, 本章还将提供 Verilog 和 SystemVerilog

标准的简明历史, 如下:

介绍 Verilog 和 SystemVerilog

陷阱的定义

Verilog 和 SystemVerilog 标准的简明描述

介绍 Verilog 和 SystemVerilog

术语 Verilog 和 SystemVerilog 有时让人困惑, 因为在工业界中它们的用法并不一致, 在本书中,Verilog 和 Sys-

temVerilog 的用途如下:

Verilog 是一种硬件描述语言 (HDL), 也就是一种数字硬件模型设计的特殊语言, 并可在受限的情况下, 编写测

SystemVerilog 是 Verilog HDL 的一个扩展集合, 主要用于更复杂的大型设计的建模和验证, 但 SystemVerilog

试程序对模型进行验证.

并不是一个完整的语言, 目前需要在 Verilog 的基础上使用.

陷阱定义

程序化的陷阱可视为一种语言特性, 由于滥用引发的不可预期的操作, 并使硬件设计中包含极度危险的故障,C 语言

中有一个类似的经典示例, 条件表达式中的赋值, 如下:

i f

/ / 陷阱! 会将 15 赋给 day

( day=15)

do_mid_month_payroll ;

1

2

因此编程者都会使用 if(a==b) 来替代 if(a=b), 其结果当然不同,C 语言陷阱并不包含一个语法错误, 并且代码也是合

法的, 只是代码无法给出所需的结果, 如果产品上市后依然包含了这些代码错误, 那么这个简单错误将对产品造成严

重的影响.

同其他的编程语言一样,Verilog 和 SystemVerilog 中也会包含陷阱, 它们在语义上是正确的, 但并不能得到预期

和需要的结果,Verilog 和 SystemVerilog 中包含陷阱的主要原因如下:

Verilog 和 SystemVerilog 使用了 C 和 C++ 语言的通用语法和语义, 在继承这些语言的强大优势的同时也继

承了它们的陷阱, 比如上例.

继承了 C 和 C++ 陷阱:

弱类型操作:

Verilog 和 SystemVerilog 是一种弱类型语言, 操作可在任意类型上执行, 基于语言规则需要小心处理执行操

作, 如果设计者或验证工程师无法理解这些语言规则, 将出现非预期的结果.

无法对设计质量进行评判:

在 Verilog 和 SystemVerilog 中, 工程师需建模和验证设计工作的正确性, 有时合法的模型硬件并不能工作, 为

了让模型设计能够正常工作, 语言必须允许一些无意的建模错误.

Verilog 和 SystemVerilog 标准

Verilog 是一种硬件描述语言的国际标准, 官方标准为 IEEE Std 1364-2005 Verilog LanguageReferenceManual

(LRM), 通常被称为 Verilog-2005,Verilog 标准中定义了描述数据逻辑行为的一组丰富的程序化建模结构, 最早的

Verilog 出现在 1984 年, 它是为了满足 80 年代中期工程师们的需要, 用于当时 3 微米下 50,000 门的 IC 设计, 由于

设计尺寸和技术的变化,Verilog 需要加入新的需求, 它的第一个 IEEE 标准为 IEEE Std 1364-1995,2001 年 IEEE 给

出了新标准 IEEE Std 1364-2001, 并增强了部分功能, 例如矢量类型的有符号运算的综合, 以及可重入任务和函数,

6

�

1. 介绍 -什么是陷阱?

7

在 2005 年 IEEE 又更新了 Verilog 标准, 在这个版本中并未加入新的建模方式, 所有的增强模式并入到了一个新的

标准中, 即 SystemVerilog.

SystemVerilog 标准即是 Verilog-2005 的扩展, 也就是 IEEE Std 1800-2005,SystemVerilog Language Reference

Manual, 又被称为 SystemVerilog-2005, 它可用于编写尺寸和复杂度逐步增加的可综合模型, 同时也可用于验证

数百万门的设计,SystemVerilog 在 Verilog 中加入了来自 SUPERLOG,VERA C,C++,VHDL 等语言的特性, 以及

OVA 和 PSL 断言,SystemVerilog 首先是由 Accellera 开发的, 它是一个电子设计公司和 EDA 工具公司的联盟,

在 2002 年,Accellera 发布了一个预备版本, 被称为 SystemVerilog 3.0, 分别在 2003 和 2004 年,Accellera 发布了

SystemVerilog 3.1 和 3.1a 版本, 最后的版本已捐献给 IEEE.

IEEE 的原始意图是想将 Accellera SystemVerilog 整合到 Verilog 标准中, 由于 EDA 公司的要求,IEEE 决定将

SystemVerilog 包含在不同的文档中, 使得 EDA 公司能够更容易地在 Verilog 工具实现一个扩展集合.

Verilog 和 SystemVerilog 的官方标准如下:

IEEE 1364-2005 standardfor the Verilog Hardware Description Language”, IEEE, Pascataway, NewJersey,

IEEE 1800-2005 standardfor the SystemVerilog Hardware Description and Verification Language”,IEEE, Pas-

2002. ISBN 978-1-4020-7089-1.

cataway, NewJersey, 2001. ISBN 0-7381-4811-3.

包含 Verilog 和 SystemVerilog 更多细节的书籍如下:

by Springer, Boston, MA,2002, ISBN 978-1-4020-7089-1.

land. Published by Springer, Boston, MA, 2002, ISBN 978-0-7923-7568-5.

”The Verilog Hardware Description Language, 5th edition”, by Donald Thomas andPhilipMoorby. Published

”Verilog-2001: A Guide to the New Features in the Verilog Hardware Description Language”, by Stuart Suther-

”SystemVerilog for Design: A Guide to Using SystemVerilog for Hardware Design and Modeling, Second

Edition”, by Stuart Sutherland, Simon Davidmann andPeterFlake. Published by Springer, Boston, MA,2006,

ISBN 978-0-387-33399-1.

”SystemVerilogfor Verification: A Guide toLearning the Testbench Language Features”, by Chris Spear. Pub-

lished by Springer, Boston, MA, 2006, ISBN 978-0-387-27036-4.

当然还有其他一些好书, 无法一一给出.

在本书编写时,IEEE 已开始将 Verilog 整合 SystemVerilog 中, 以创建一种单独的语言, 到时 Verilog 将被弃用,

并会使用 SystemVerilog 作为统一的硬件设计和验证语言.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc