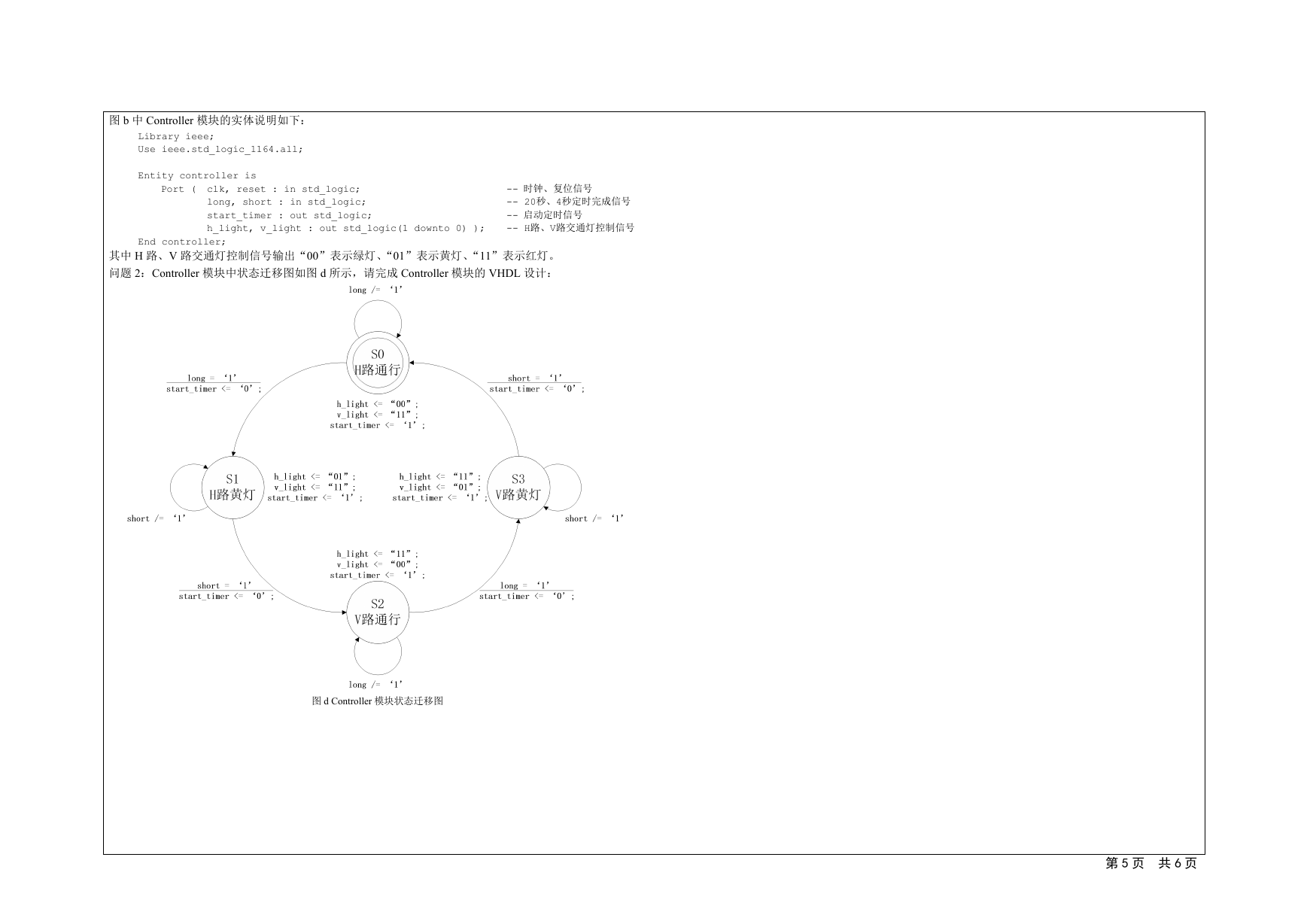

山东大学电子设计自动化试卷

5. 下面对利用原理图输入设计方法进行数字电路系统设计,那一种说法是不正确的______。

A. 原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计;

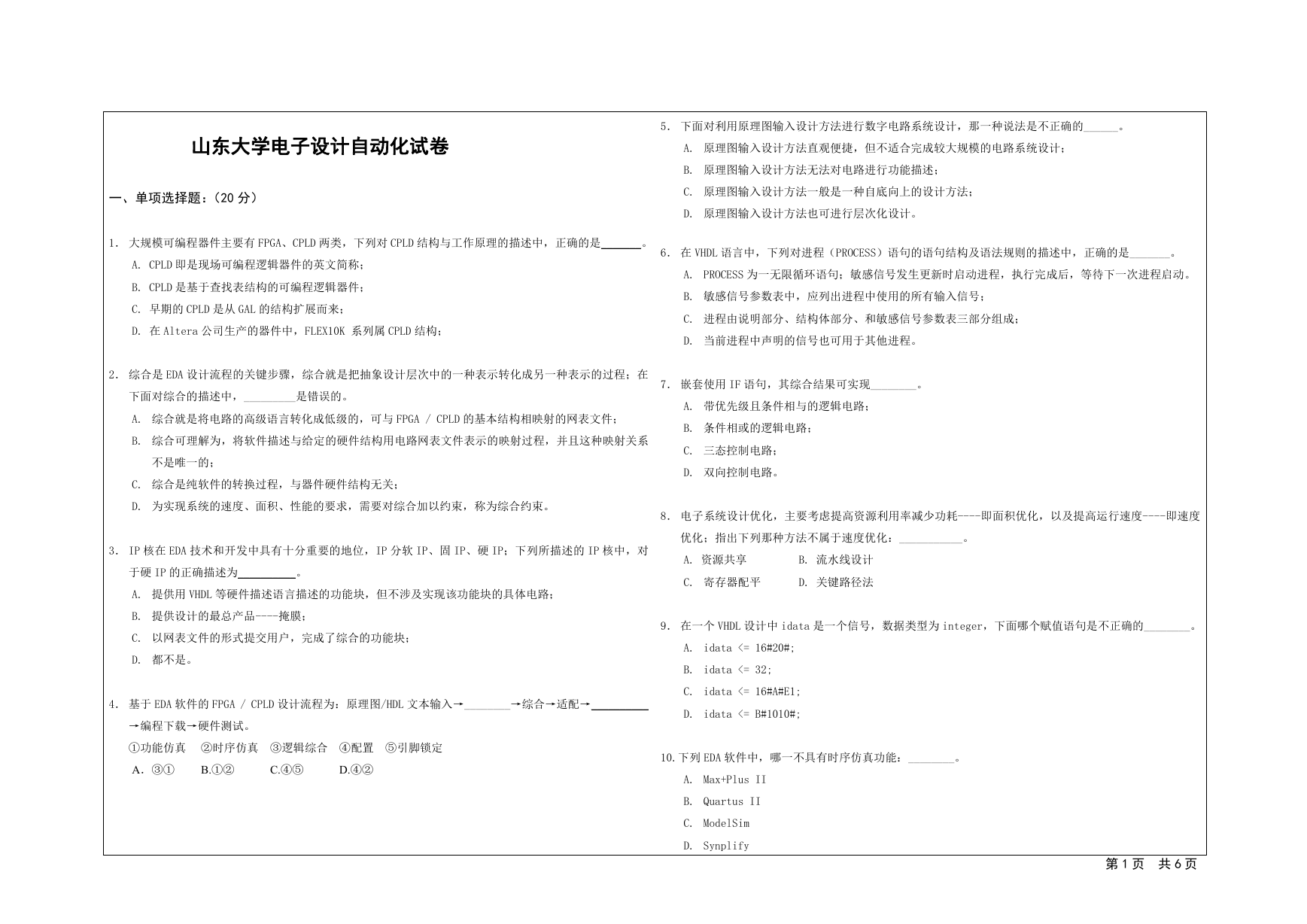

一、单项选择题:(20 分)

1. 大规模可编程器件主要有 FPGA、CPLD 两类,下列对 CPLD 结构与工作原理的描述中,正确的是_______。

A. CPLD 即是现场可编程逻辑器件的英文简称;

B. CPLD 是基于查找表结构的可编程逻辑器件;

C. 早期的 CPLD 是从 GAL 的结构扩展而来;

D. 在 Altera 公司生产的器件中,FLEX10K 系列属 CPLD 结构;

2. 综合是 EDA 设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在

下面对综合的描述中,_________是错误的。

A. 综合就是将电路的高级语言转化成低级的,可与 FPGA / CPLD 的基本结构相映射的网表文件;

B. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系

不是唯一的;

C. 综合是纯软件的转换过程,与器件硬件结构无关;

D. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束。

B. 原理图输入设计方法无法对电路进行功能描述;

C. 原理图输入设计方法一般是一种自底向上的设计方法;

D. 原理图输入设计方法也可进行层次化设计。

6. 在 VHDL 语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确的是_______。

A. PROCESS 为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动。

B. 敏感信号参数表中,应列出进程中使用的所有输入信号;

C. 进程由说明部分、结构体部分、和敏感信号参数表三部分组成;

D. 当前进程中声明的信号也可用于其他进程。

7. 嵌套使用 IF 语句,其综合结果可实现________。

A. 带优先级且条件相与的逻辑电路;

B. 条件相或的逻辑电路;

C. 三态控制电路;

D. 双向控制电路。

8. 电子系统设计优化,主要考虑提高资源利用率减少功耗----即面积优化,以及提高运行速度----即速度

3. IP 核在 EDA 技术和开发中具有十分重要的地位,IP 分软 IP、固 IP、硬 IP;下列所描述的 IP 核中,对

于硬 IP 的正确描述为__________。

A. 提供用 VHDL 等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路;

优化;指出下列那种方法不属于速度优化:___________。

A. 资源共享

B. 流水线设计

C. 寄存器配平

D. 关键路径法

B. 提供设计的最总产品----掩膜;

C. 以网表文件的形式提交用户,完成了综合的功能块;

D. 都不是。

4. 基于 EDA 软件的 FPGA / CPLD 设计流程为:原理图/HDL 文本输入→________→综合→适配→__________

→编程下载→硬件测试。

①功能仿真 ②时序仿真 ③逻辑综合 ④配置 ⑤引脚锁定

A.③①

B.①②

C.④⑤

D.④②

9. 在一个 VHDL 设计中 idata 是一个信号,数据类型为 integer,下面哪个赋值语句是不正确的________。

A. idata <= 16#20#;

B. idata <= 32;

C. idata <= 16#A#E1;

D. idata <= B#1010#;

10.下列 EDA 软件中,哪一不具有时序仿真功能:________。

A. Max+Plus II

B. Quartus II

C. ModelSim

D. Synplify

第 1 页 共 6 页

�

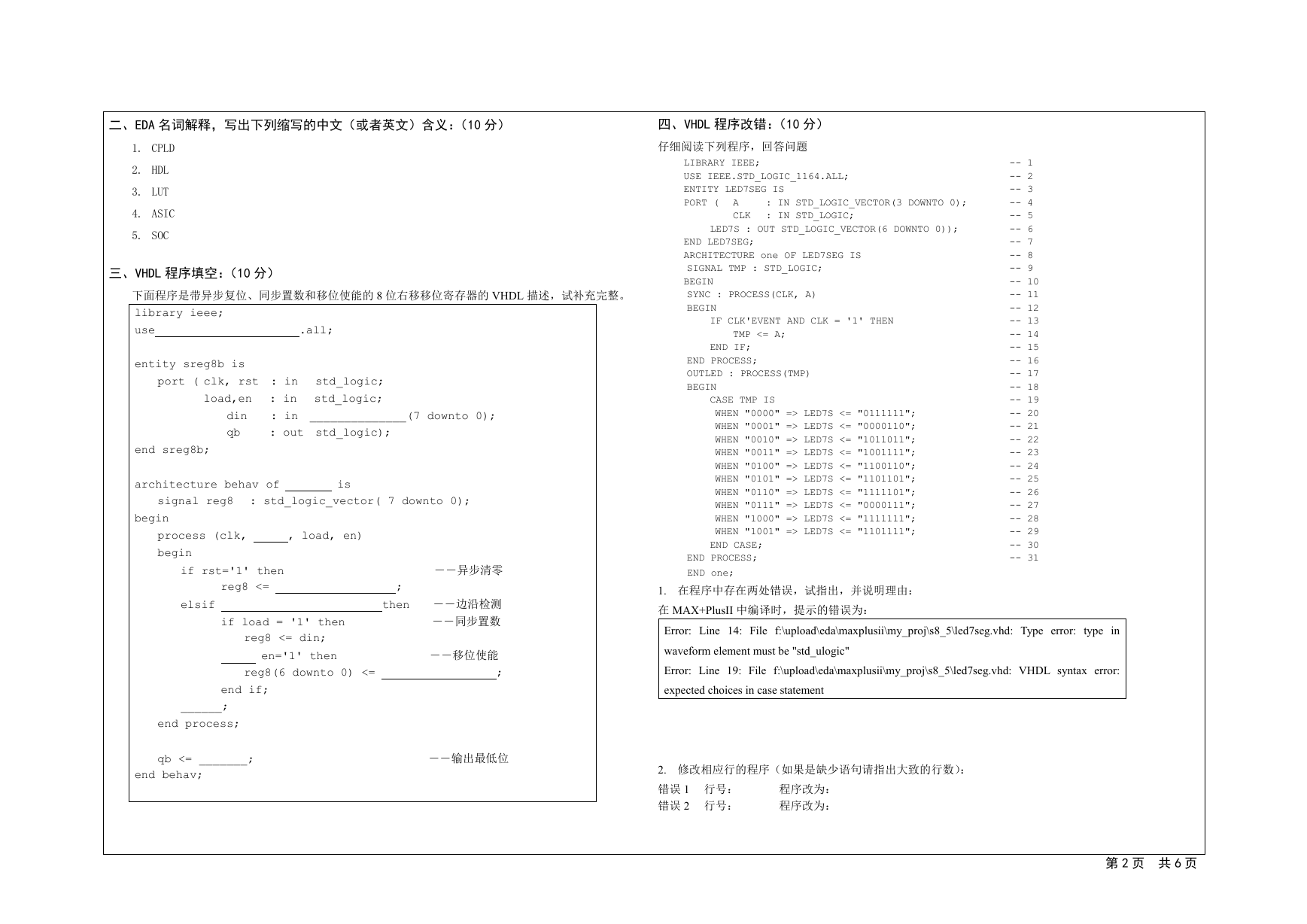

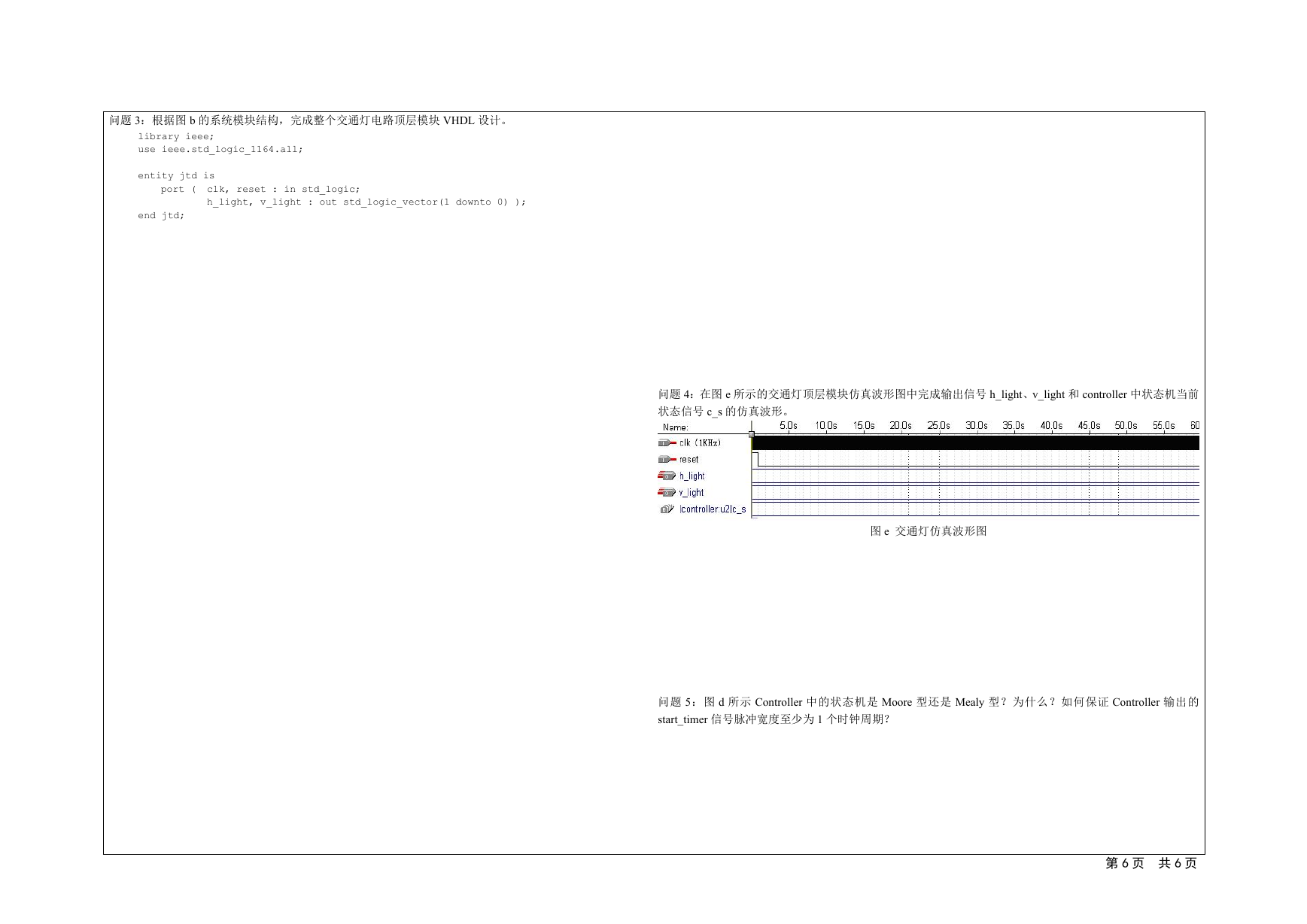

二、EDA 名词解释,写出下列缩写的中文(或者英文)含义:(10 分)

1. CPLD

2. HDL

3. LUT

4. ASIC

5. SOC

三、VHDL 程序填空:(10 分)

下面程序是带异步复位、同步置数和移位使能的 8 位右移移位寄存器的 VHDL 描述,试补充完整。

library ieee;

use

.all;

entity sreg8b is

port ( clk, rst : in

: in

: in ______________(7 downto 0);

: out std_logic);

load,en

din

qb

std_logic;

std_logic;

end sreg8b;

architecture behav of

is

signal reg8

: std_logic_vector( 7 downto 0);

;

then

――异步清零

――边沿检测

――同步置数

――移位使能

;

, load, en)

begin

process (clk,

begin

if rst='1' then

reg8 <=

elsif

if load = '1' then

reg8 <= din;

en='1' then

reg8(6 downto 0) <=

end if;

______;

end process;

四、VHDL 程序改错:(10 分)

仔细阅读下列程序,回答问题

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LED7SEG IS

PORT (

A

CLK

: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

: IN STD_LOGIC;

LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END LED7SEG;

ARCHITECTURE one OF LED7SEG IS

SIGNAL TMP : STD_LOGIC;

BEGIN

SYNC : PROCESS(CLK, A)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN

TMP <= A;

END IF;

END PROCESS;

OUTLED : PROCESS(TMP)

BEGIN

CASE TMP IS

WHEN "0000" => LED7S <= "0111111";

WHEN "0001" => LED7S <= "0000110";

WHEN "0010" => LED7S <= "1011011";

WHEN "0011" => LED7S <= "1001111";

WHEN "0100" => LED7S <= "1100110";

WHEN "0101" => LED7S <= "1101101";

WHEN "0110" => LED7S <= "1111101";

WHEN "0111" => LED7S <= "0000111";

WHEN "1000" => LED7S <= "1111111";

WHEN "1001" => LED7S <= "1101111";

END CASE;

END PROCESS;

END one;

-- 1

-- 2

-- 3

-- 4

-- 5

-- 6

-- 7

-- 8

-- 9

-- 10

-- 11

-- 12

-- 13

-- 14

-- 15

-- 16

-- 17

-- 18

-- 19

-- 20

-- 21

-- 22

-- 23

-- 24

-- 25

-- 26

-- 27

-- 28

-- 29

-- 30

-- 31

1. 在程序中存在两处错误,试指出,并说明理由:

在 MAX+PlusII 中编译时,提示的错误为:

Error: Line 14: File f:\upload\eda\maxplusii\my_proj\s8_5\led7seg.vhd: Type error:

waveform element must be "std_ulogic"

Error: Line 19: File f:\upload\eda\maxplusii\my_proj\s8_5\led7seg.vhd: VHDL syntax error:

expected choices in case statement

type in

qb <= _______;

end behav;

――输出最低位

2. 修改相应行的程序(如果是缺少语句请指出大致的行数):

错误 1 行号:

错误 2 行号:

程序改为:

程序改为:

第 2 页 共 6 页

�

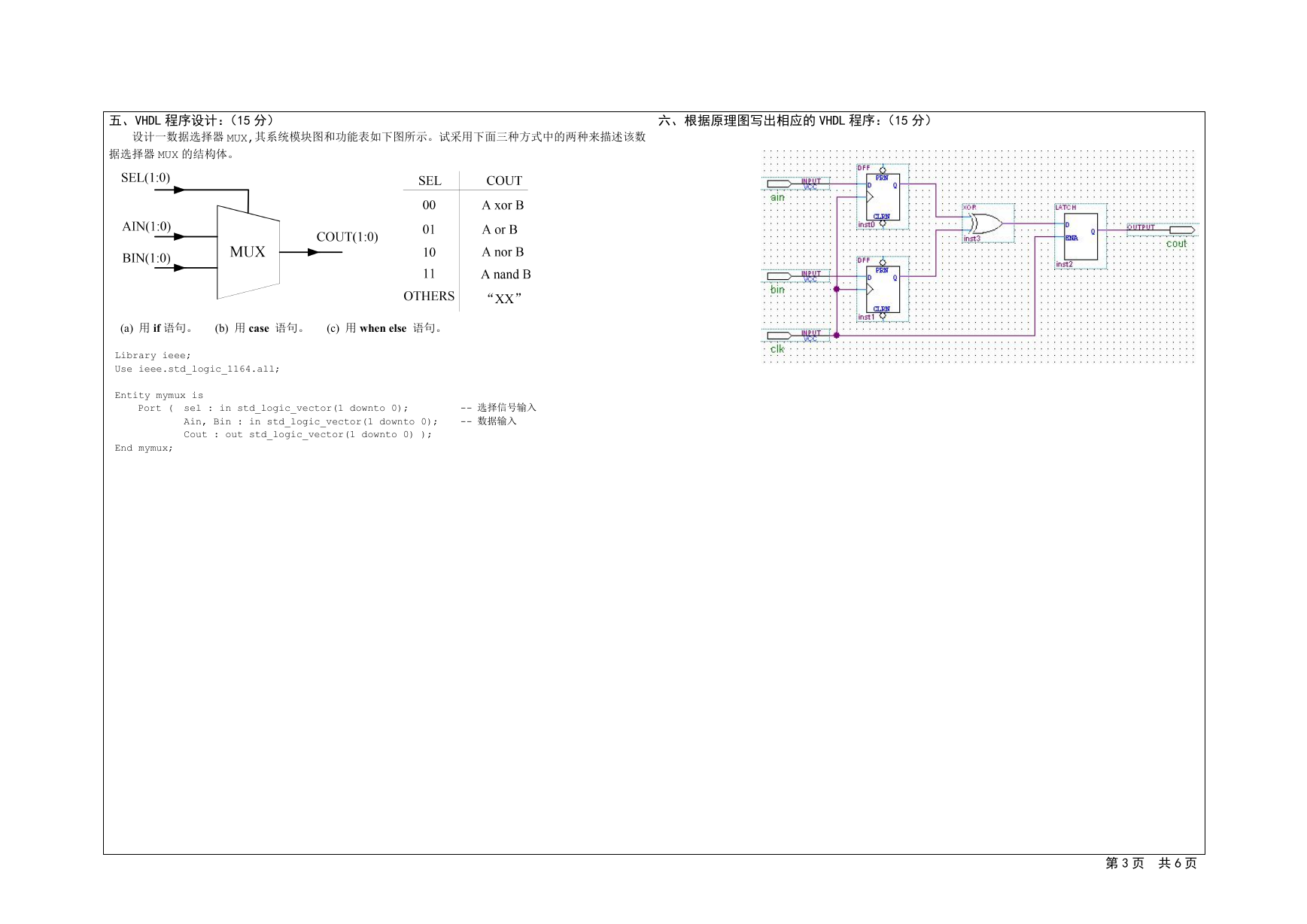

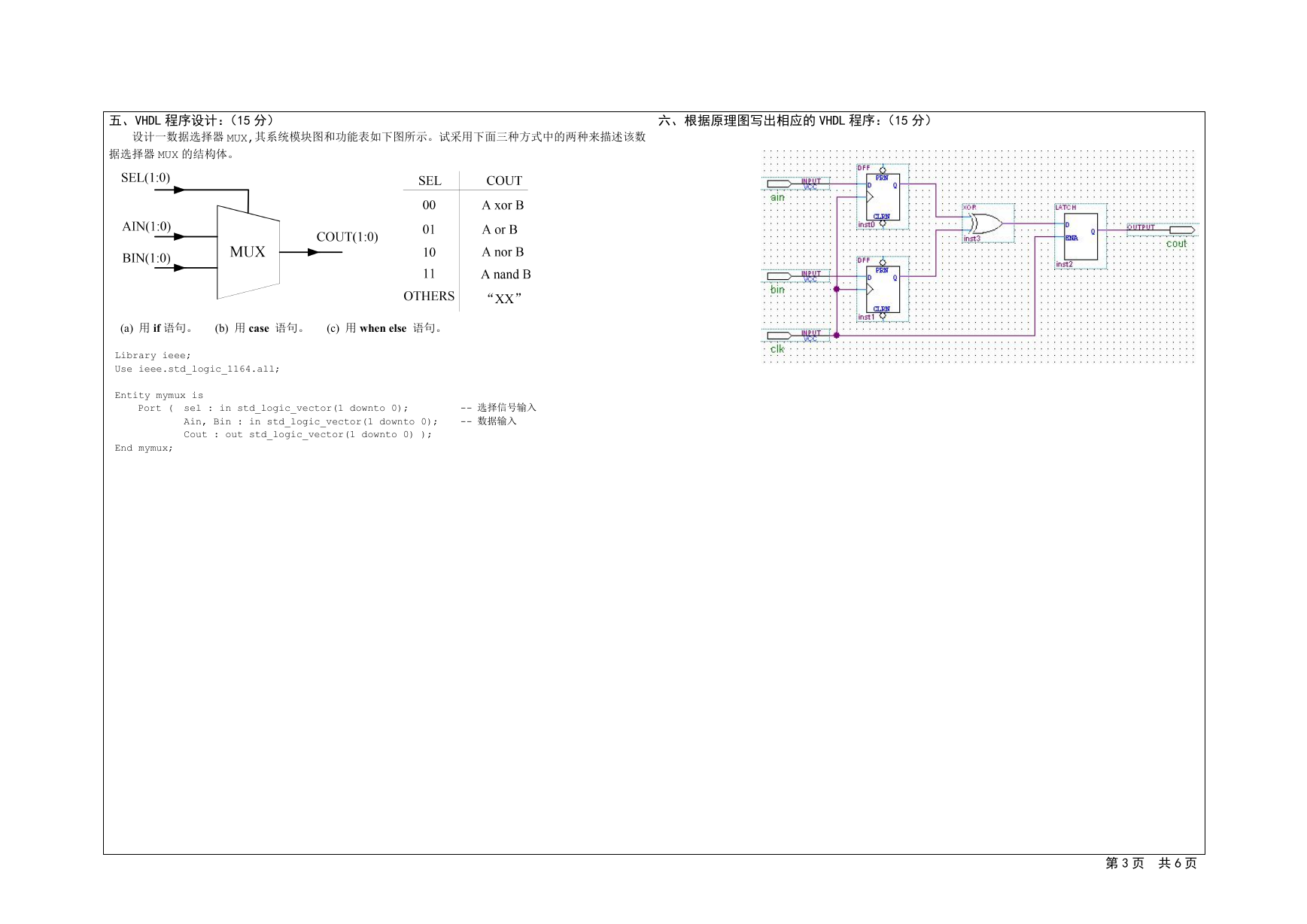

五、VHDL 程序设计:(15 分)

六、根据原理图写出相应的 VHDL 程序:(15 分)

设计一数据选择器 MUX,其系统模块图和功能表如下图所示。试采用下面三种方式中的两种来描述该数

据选择器 MUX 的结构体。

(a) 用 if 语句。 (b) 用 case 语句。 (c) 用 when else 语句。

Library ieee;

Use ieee.std_logic_1164.all;

Entity mymux is

End mymux;

Port ( sel : in std_logic_vector(1 downto 0);

Ain, Bin : in std_logic_vector(1 downto 0);

Cout : out std_logic_vector(1 downto 0) );

-- 选择信号输入

-- 数据输入

第 3 页 共 6 页

�

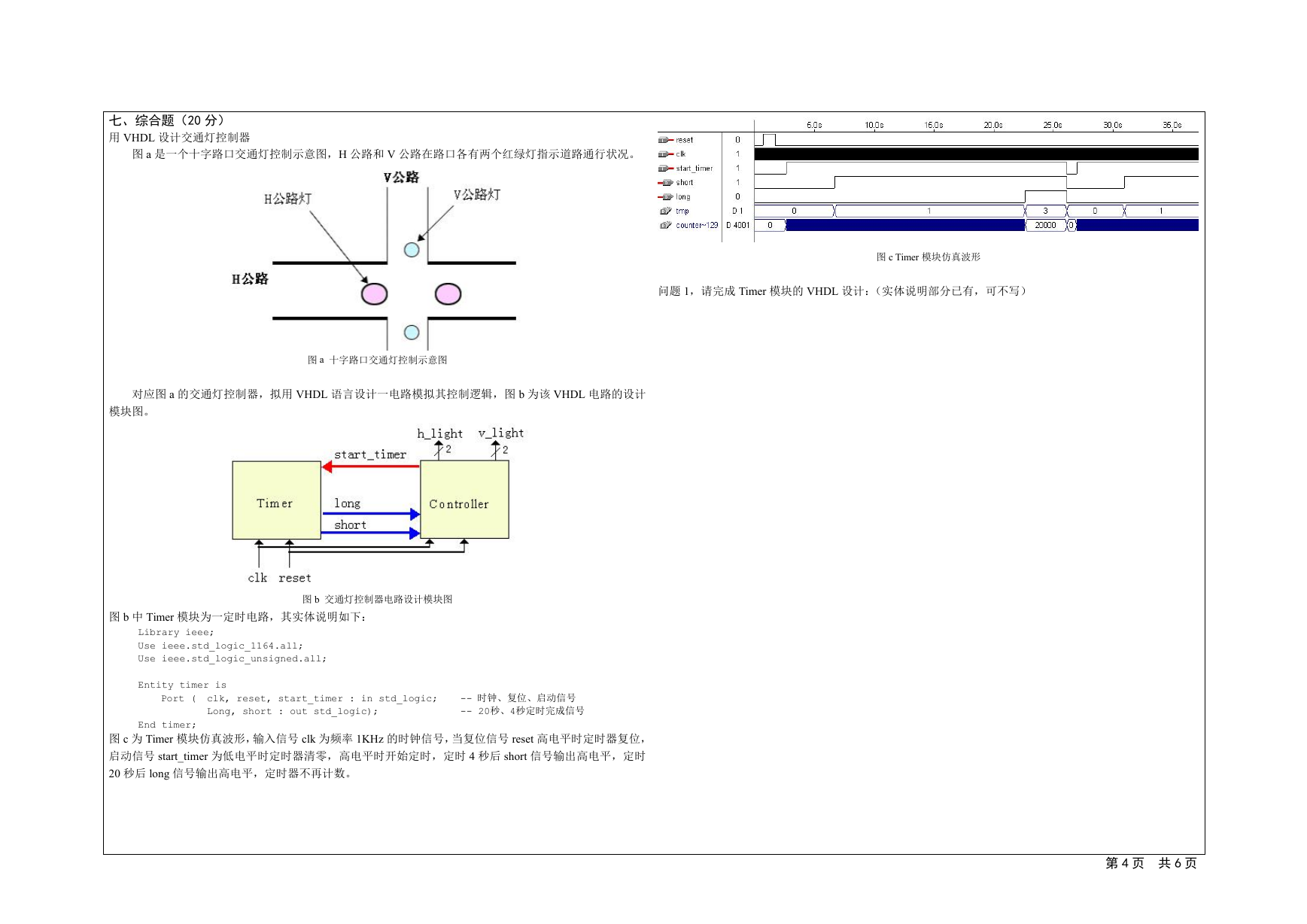

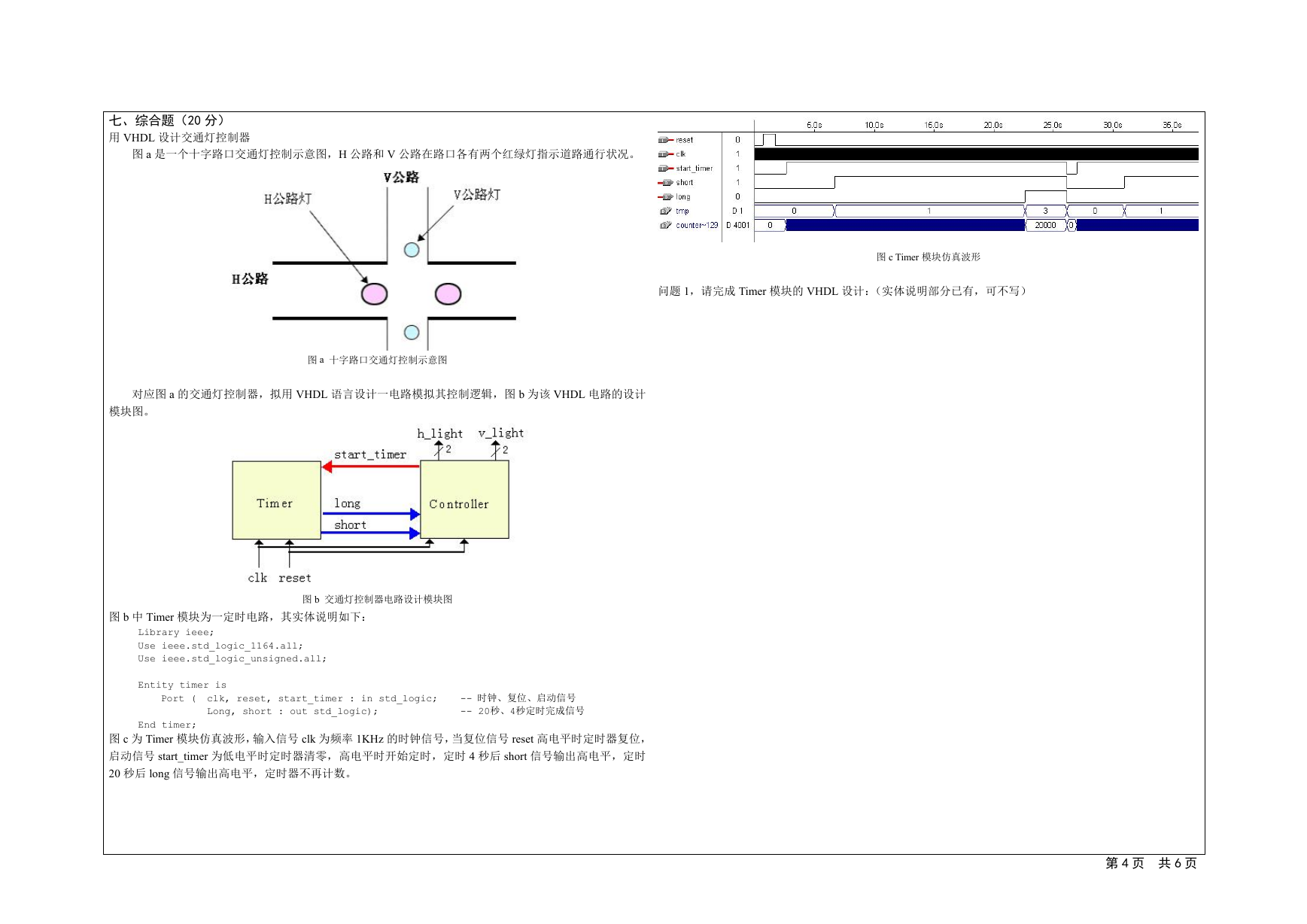

七、综合题(20 分)

用 VHDL 设计交通灯控制器

图 a 是一个十字路口交通灯控制示意图,H 公路和 V 公路在路口各有两个红绿灯指示道路通行状况。

问题 1,请完成 Timer 模块的 VHDL 设计:(实体说明部分已有,可不写)

图 c Timer 模块仿真波形

图 a 十字路口交通灯控制示意图

对应图 a 的交通灯控制器,拟用 VHDL 语言设计一电路模拟其控制逻辑,图 b 为该 VHDL 电路的设计

模块图。

图 b 交通灯控制器电路设计模块图

图 b 中 Timer 模块为一定时电路,其实体说明如下:

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

Port ( clk, reset, start_timer : in std_logic;

Long, short : out std_logic);

-- 时钟、复位、启动信号

-- 20秒、4秒定时完成信号

Entity timer is

End timer;

图 c 为 Timer 模块仿真波形,输入信号 clk 为频率 1KHz 的时钟信号,当复位信号 reset 高电平时定时器复位,

启动信号 start_timer 为低电平时定时器清零,高电平时开始定时,定时 4 秒后 short 信号输出高电平,定时

20 秒后 long 信号输出高电平,定时器不再计数。

第 4 页 共 6 页

�

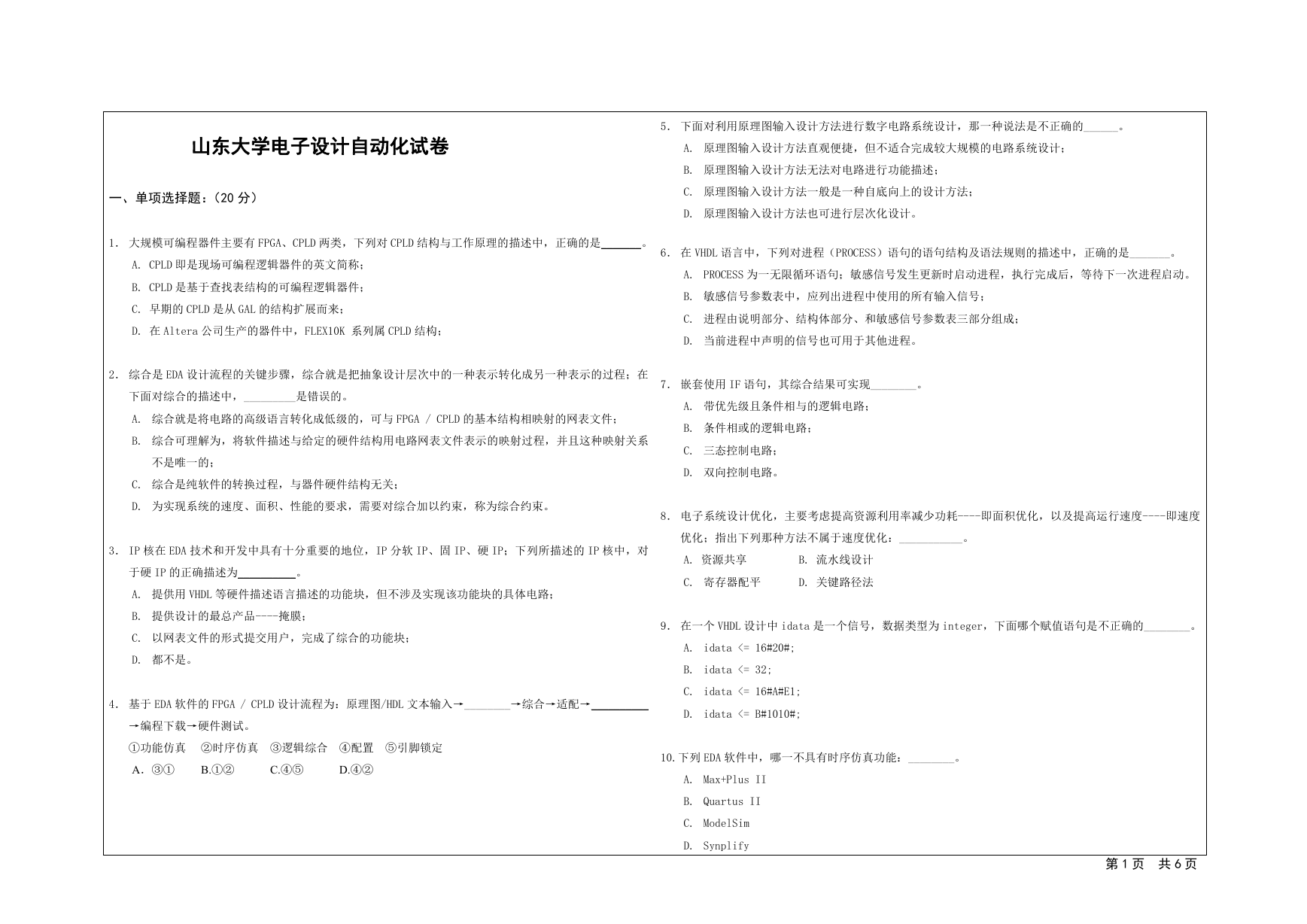

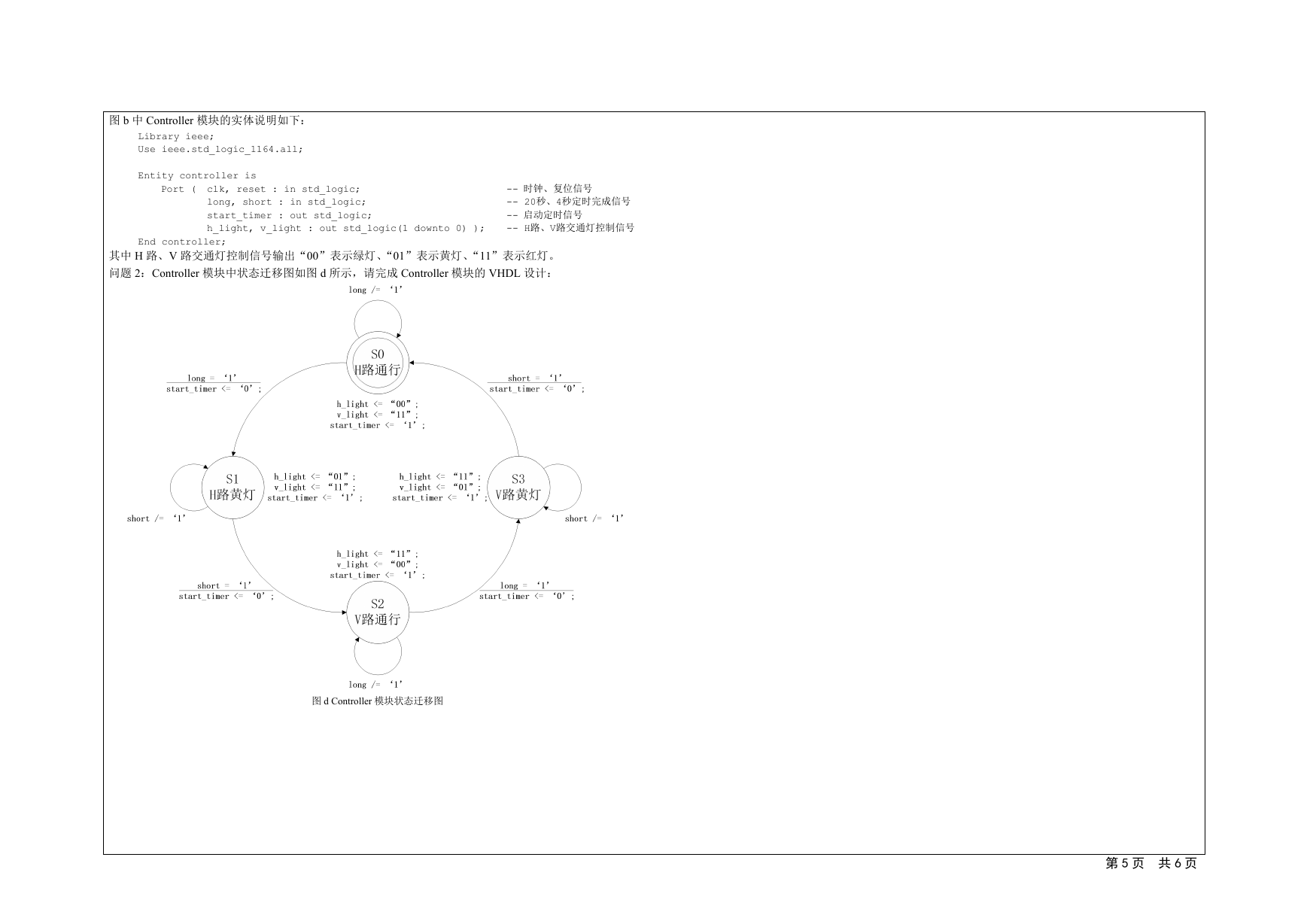

图 b 中 Controller 模块的实体说明如下:

Library ieee;

Use ieee.std_logic_1164.all;

Entity controller is

Port ( clk, reset : in std_logic;

long, short : in std_logic;

start_timer : out std_logic;

h_light, v_light : out std_logic(1 downto 0) );

-- 时钟、复位信号

-- 20秒、4秒定时完成信号

-- 启动定时信号

-- H路、V路交通灯控制信号

End controller;

其中 H 路、V 路交通灯控制信号输出“00”表示绿灯、“01”表示黄灯、“11”表示红灯。

问题 2:Controller 模块中状态迁移图如图 d 所示,请完成 Controller 模块的 VHDL 设计:

图 d Controller 模块状态迁移图

第 5 页 共 6 页

�

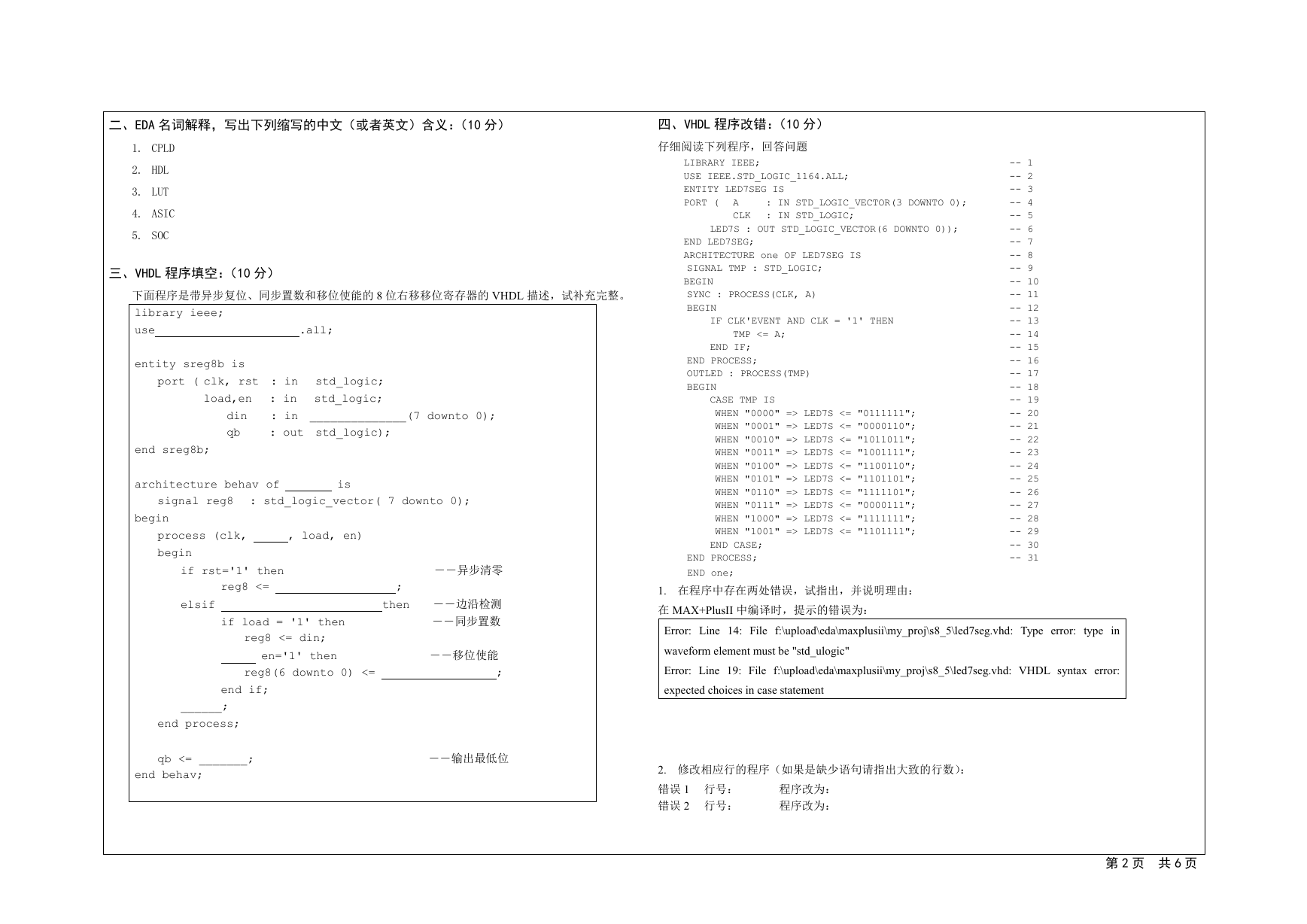

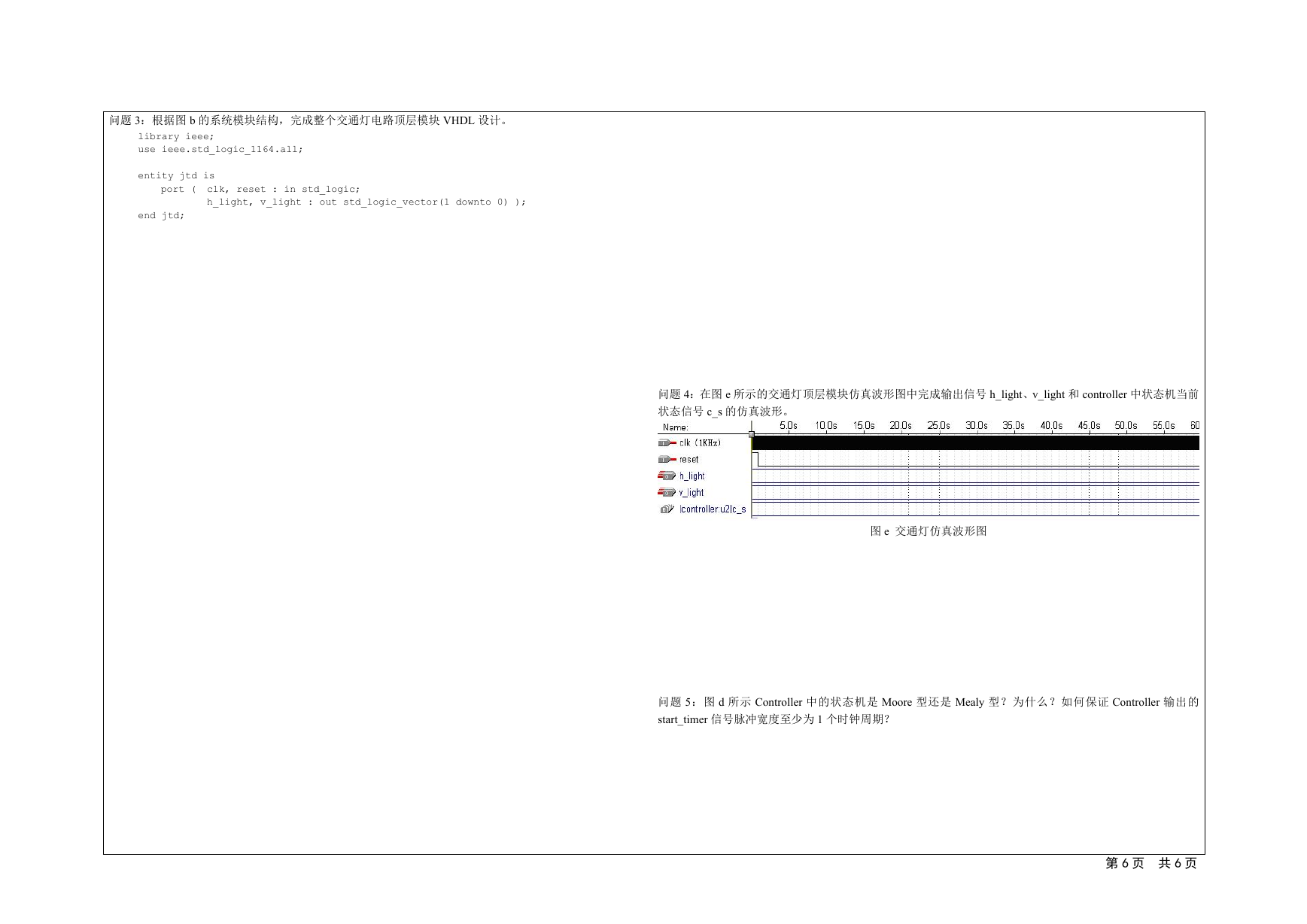

问题 3:根据图 b 的系统模块结构,完成整个交通灯电路顶层模块 VHDL 设计。

library ieee;

use ieee.std_logic_1164.all;

entity jtd is

port ( clk, reset : in std_logic;

h_light, v_light : out std_logic_vector(1 downto 0) );

end jtd;

问题 4:在图 e 所示的交通灯顶层模块仿真波形图中完成输出信号 h_light、v_light 和 controller 中状态机当前

状态信号 c_s 的仿真波形。

图 e 交通灯仿真波形图

问题 5:图 d 所示 Controller 中的状态机是 Moore 型还是 Mealy 型?为什么?如何保证 Controller 输出的

start_timer 信号脉冲宽度至少为 1 个时钟周期?

第 6 页 共 6 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc