CV520

非接触式 IC 卡读写芯片

1. 介绍

2. 概述

这份文件描述的是非接触式 IC 卡读写芯片 CV520 的功能和电气规格。

注意: CV520 支持 MIFARE 的所有变体:MIFARE Mini , MIFARE 1K, MIFARE 4K,

MIFARE Ultralight, MIFARE DESFire EV1 和带有射频识别的 MIFARE。在本文件中为了通

俗易懂, MIFARE Mini, MIFARE 1K, MIFARE 4K, MIFARE Ultralight, MIFARE DESFire

EV1 和 MIFARE PLUS 系列产品,统称为 MIFARE.

CV520 是应用于 13.56MHz 非接触式通信中高集成度读写卡系列芯片中的一员,支持

ISO/IEC 14443 TypeA 和 MIFARE®通信协议。

其内部发送器部分可驱动读写器天线与 ISO 14443A/MIFARE®卡 及应答器的通信,无需其

它的电路。接收器部分提供一个稳定高效的解调和解码电路, 用于处理 ISO14443A 兼容

的应答器信号。数字部分处理 ISO14443A 帧和错误检测(奇偶&CRC)。

MF CV520 支持 MF1xxS20,MF1xxS70 和 MF1xxS50 等系列产品。MF CV520 支持

MIFARE®更高速的非接触式通信,双向数据传输速率高达 828kbit/s。

支持以下主机接口:

• 串行外设接口 (SPI)

3. 功能特性

高集成度的调制解调电路;

采用少量外部器件,即可将输出驱动级接至天线;

支持 ISO/IEC 14443 TypeA 和 MIFARE®通信协议;

达到100mm的读写距离,读写距离取决于天线的大小和调制;

支持MF1xxS20,MF1xxS70和MF1xxS50的读写加密;

支持 ISO 14443A 高达848kbit/s传输速率的通信;

支持MFIN/MFOUT;

�

MF CV520

Contactless reader IC

NXP&HUASHI Semiconductors

支持的主机接口:

-最高到10Mbit/s 的 SPI 接口;

64 字节的发送和接收 FIFO 缓冲区;

灵活的中断模式;

低功耗下硬件复位;

具备软件掉电模式;

可编程定时器;

内部振荡器,连接 27.12MHz 的晶体;

2.5~3.6V 的低电压低功耗设计;

具备 CRC 和奇偶校验功能;

可编程的I/O管脚;

内部自检;

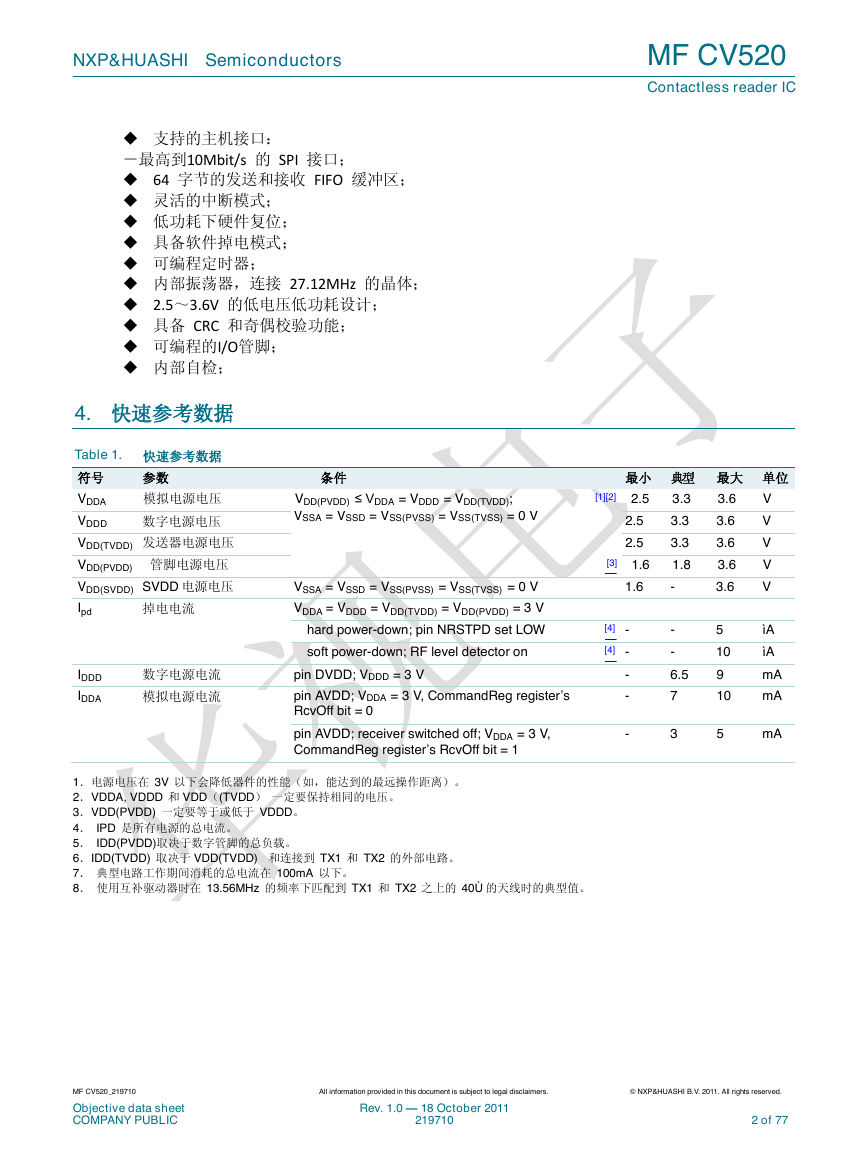

4. 快速参考数据

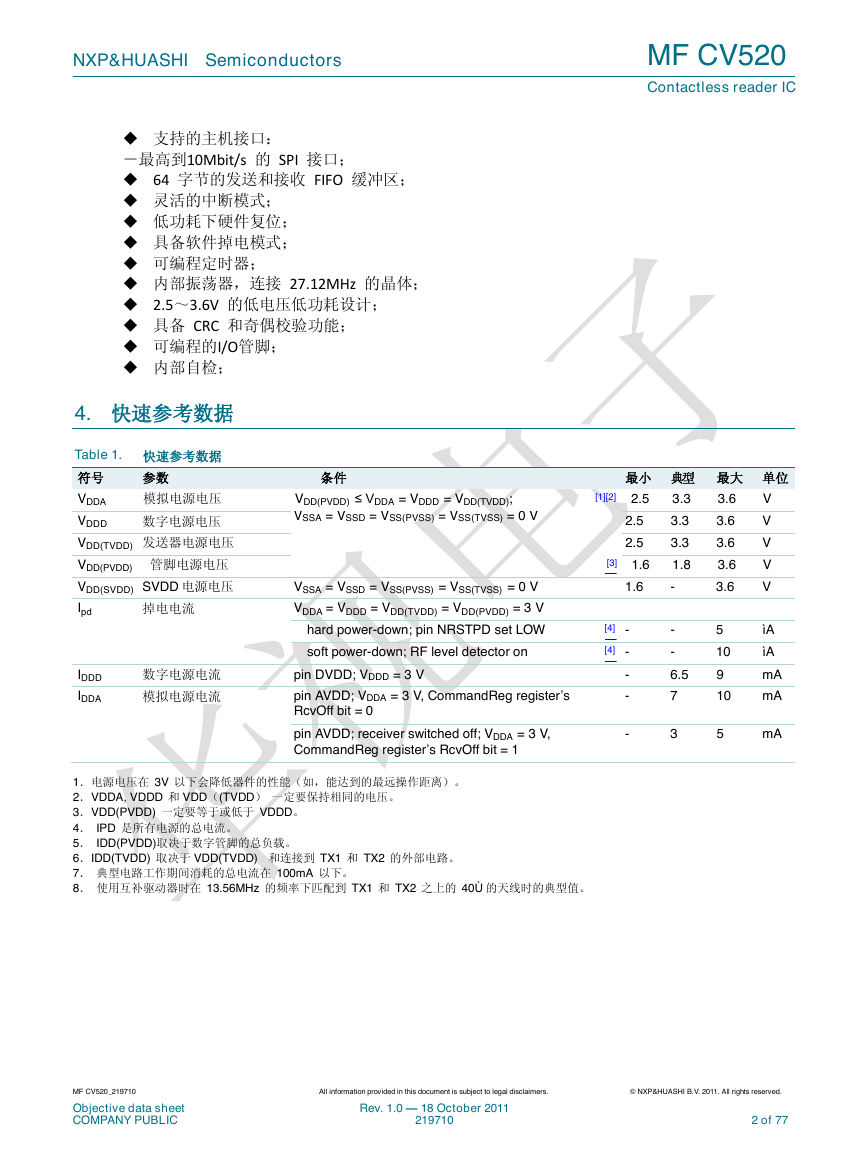

Table 1.

快速参考数据

符号

VDDA

参数

模拟电源电压

数字电源电压

VDDD

VDD(TVDD) 发送器电源电压

VDD(PVDD) 管脚电源电压

VDD(SVDD) SVDD 电源电压

Ipd

掉电电流

IDDD

IDDA

数字电源电流

模拟电源电流

条件

VDD(PVDD) ≤ VDDA = VDDD = VDD(TVDD);

VSSA = VSSD = VSS(PVSS) = VSS(TVSS) = 0 V

VSSA = VSSD = VSS(PVSS) = VSS(TVSS) = 0 V

VDDA = VDDD = VDD(TVDD) = VDD(PVDD) = 3 V

hard power-down; pin NRSTPD set LOW

soft power-down; RF level detector on

pin DVDD; VDDD = 3 V

pin AVDD; VDDA = 3 V, CommandReg register’s

RcvOff bit = 0

pin AVDD; receiver switched off; VDDA = 3 V,

CommandReg register’s RcvOff bit = 1

最小 典型 最大 单位

[1][2] 2.5

3.3

2.5

2.5

3.3

3.3

[3] 1.6

1.8

1.6

[4] -

[4] -

-

-

-

-

-

-

6.5

7

3

3.6

3.6

3.6

3.6

3.6

5

10

9

10

V

V

V

V

V

ìA

ìA

mA

mA

5

mA

1.电源电压在 3V 以下会降低器件的性能(如,能达到的最远操作距离)。

2.VDDA, VDDD 和 VDD((TVDD) 一定要保持相同的电压。

3.VDD(PVDD) 一定要等于或低于 VDDD。

4. IPD 是所有电源的总电流。

5. IDD(PVDD)取决于数字管脚的总负载。

6.IDD(TVDD) 取决于 VDD(TVDD) 和连接到 TX1 和 TX2 的外部电路。

7. 典型电路工作期间消耗的总电流在 100mA 以下。

8. 使用互补驱动器时在 13.56MHz 的频率下匹配到 TX1 和 TX2 之上的 40Ù 的天线时的典型值。

MF CV520_219710

Objective data sheet

COMPANY PUBLIC

All information provided in this document is subject to legal disclaimers.

© NXP&HUASHI B.V. 2011. All rights reserved.

Rev. 1.0 — 18 October 2011

219710

2 of 77

�

NXP&HUASHI Semiconductors

MF CV520

Contactless reader IC

5. 订购信息

Table 2. 订购信息

芯片种类

封装

名称

描述

版本

MF CV52001HN1/TRAYBM[1] HVQFN32 热特性较强且厚度非常薄的扁平四方形;无引线;32 个引脚;芯

SOT617-1

片尺寸为 5×5×0.85mm

[1] 5 个工作日内交货

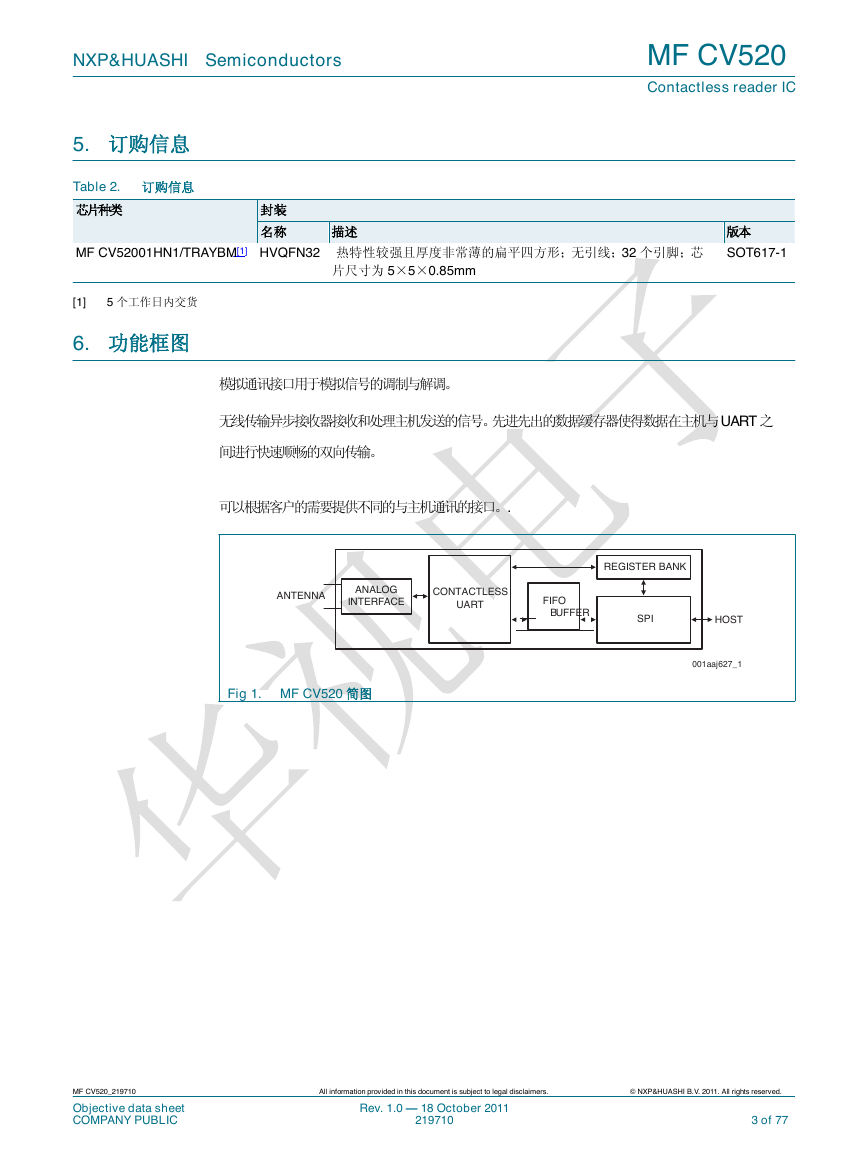

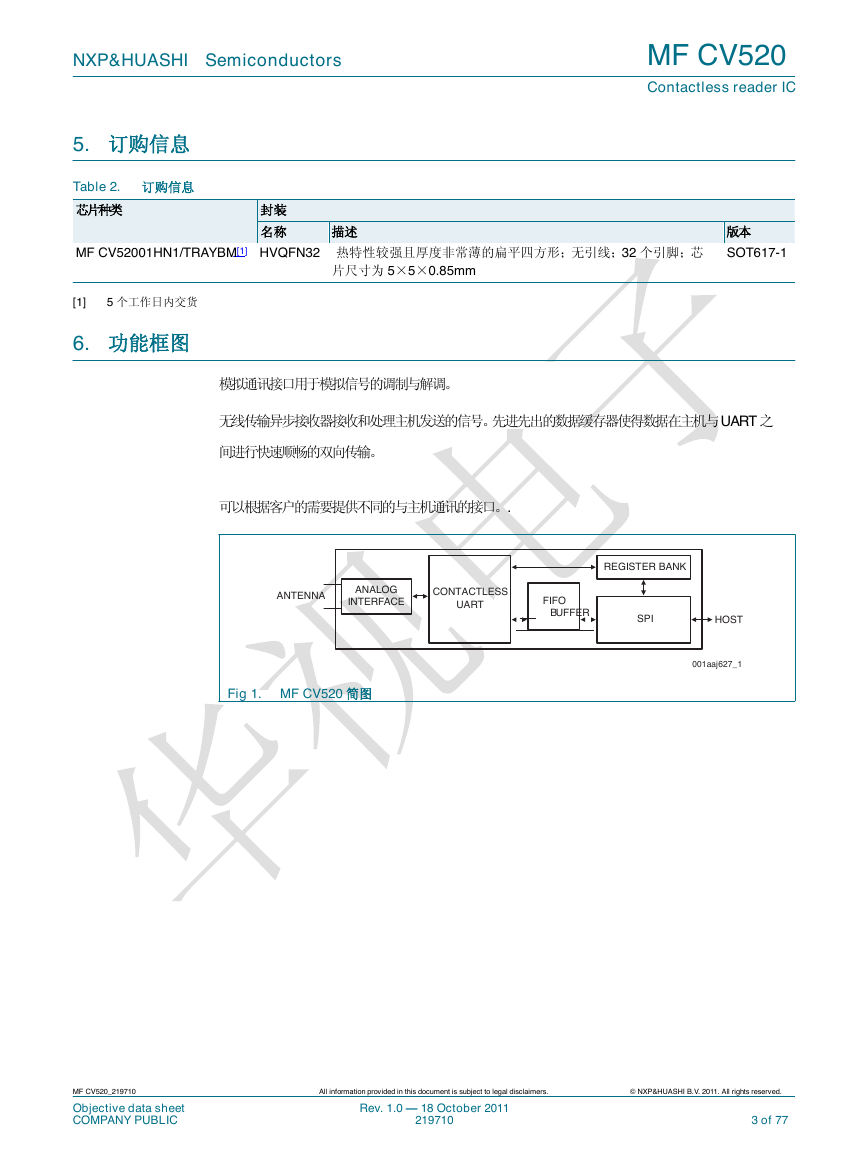

6. 功能框图

模拟通讯接口用于模拟信号的调制与解调。

无线传输异步接收器接收和处理主机发送的信号。先进先出的数据缓存器使得数据在主机与UART 之

间进行快速顺畅的双向传输。

可以根据客户的需要提供不同的与主机通讯的接口。.

REGISTER BANK

ANTENNA

ANALOG

INTERFACE

Fig 1. MF CV520 简图

CONTACTLESS

UART

FIFO

BUFFER

SPI

HOST

001aaj627_1

MF CV520_219710

Objective data sheet

COMPANY PUBLIC

All information provided in this document is subject to legal disclaimers.

© NXP&HUASHI B.V. 2011. All rights reserved.

Rev. 1.0 — 18 October 2011

219710

3 of 77

�

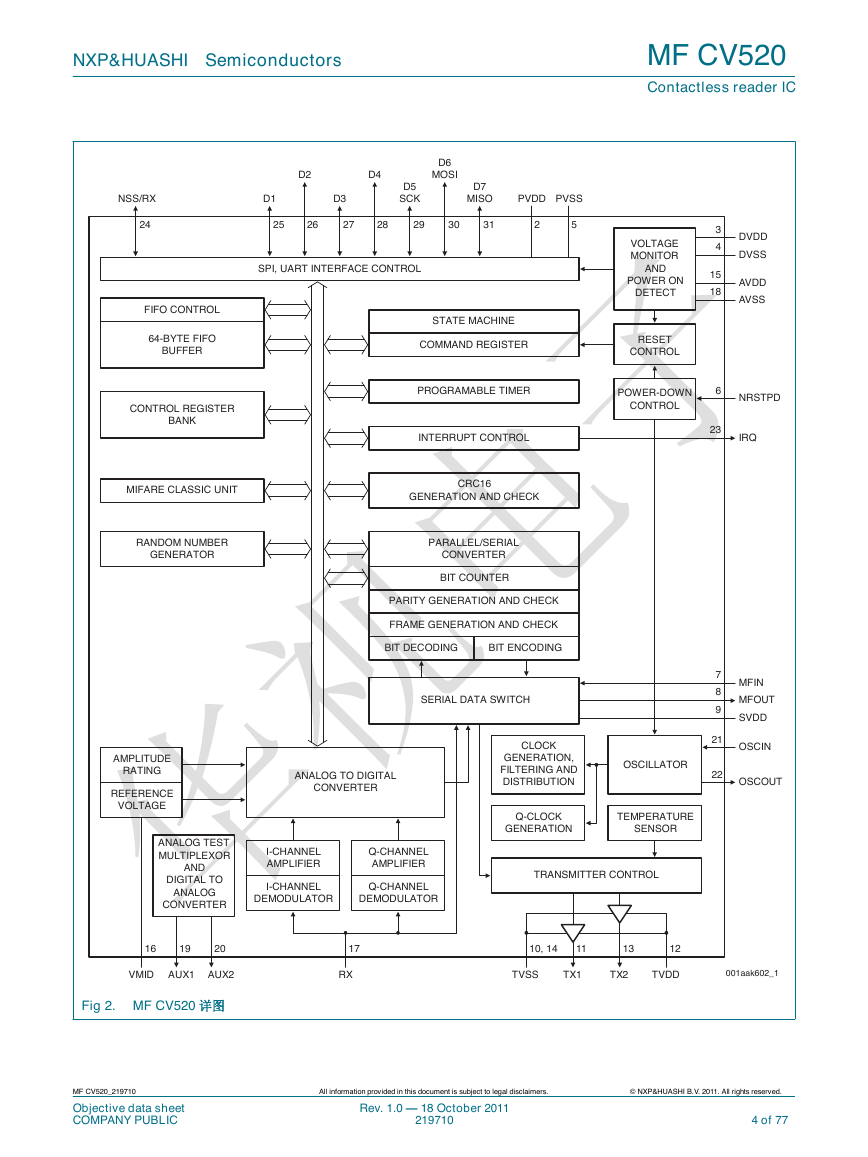

MF CV520

Contactless reader IC

VOLTAGE

MONITOR

AND

POWER ON

DETECT

RESET

CONTROL

POWER-DOWN

CONTROL

3

4

15

18

6

23

DVDD

DVSS

AVDD

AVSS

NRSTPD

IRQ

NXP&HUASHI Semiconductors

NSS/RX

24

D2

D1

D3

D4

D5

SCK

D6

MOSI

D7

MISO

25

26

27

28

29

30

31

PVDD

2

PVSS

5

FIFO CONTROL

64-BYTE FIFO

BUFFER

CONTROL REGISTER

BANK

SPI, UART INTERFACE CONTROL

STATE MACHINE

COMMAND REGISTER

PROGRAMABLE TIMER

INTERRUPT CONTROL

MIFARE CLASSIC UNIT

CRC16

GENERATION AND CHECK

RANDOM NUMBER

GENERATOR

PARALLEL/SERIAL

CONVERTER

BIT COUNTER

PARITY GENERATION AND CHECK

FRAME GENERATION AND CHECK

BIT DECODING

BIT ENCODING

SERIAL DATA SWITCH

AMPLITUDE

RATING

REFERENCE

VOLTAGE

ANALOG TO DIGITAL

CONVERTER

ANALOG TEST

MULTIPLEXOR

AND

DIGITAL TO

ANALOG

CONVERTER

I-CHANNEL

AMPLIFIER

Q-CHANNEL

AMPLIFIER

I-CHANNEL

Q-CHANNEL

DEMODULATOR

DEMODULATOR

CLOCK

GENERATION,

FILTERING AND

DISTRIBUTION

Q-CLOCK

GENERATION

OSCILLATOR

TEMPERATURE

SENSOR

TRANSMITTER CONTROL

7

8

9

21

22

MFIN

MFOUT

SVDD

OSCIN

OSCOUT

16

19

20

VMID AUX1 AUX2

17

RX

10, 14

11

13

12

TVSS

TX1

TX2

TVDD

001aak602_1

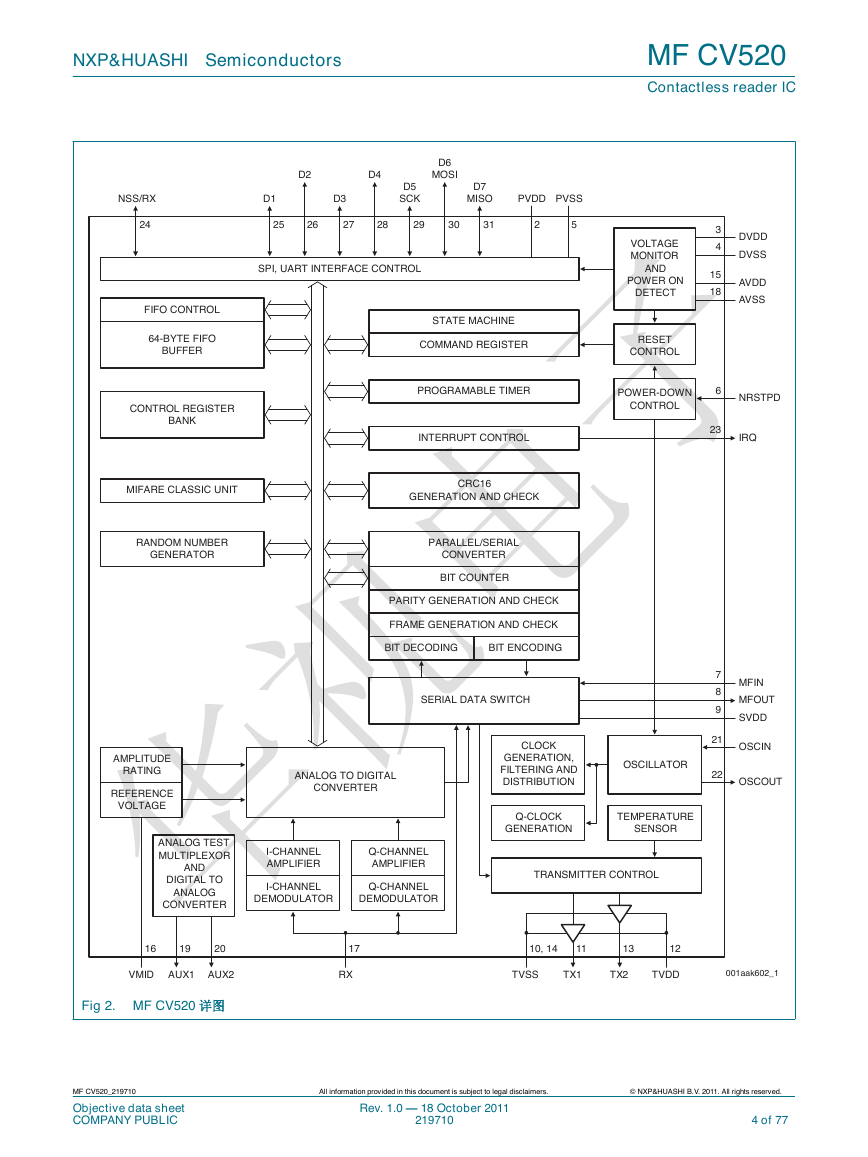

Fig 2. MF CV520 详图

MF CV520_219710

All information provided in this document is subject to legal disclaimers.

© NXP&HUASHI B.V. 2011. All rights reserved.

Objective data sheet

COMPANY PUBLIC

Rev. 1.0 — 18 October 2011

219710

4 of 77

�

NXP&HUASHI Semiconductors

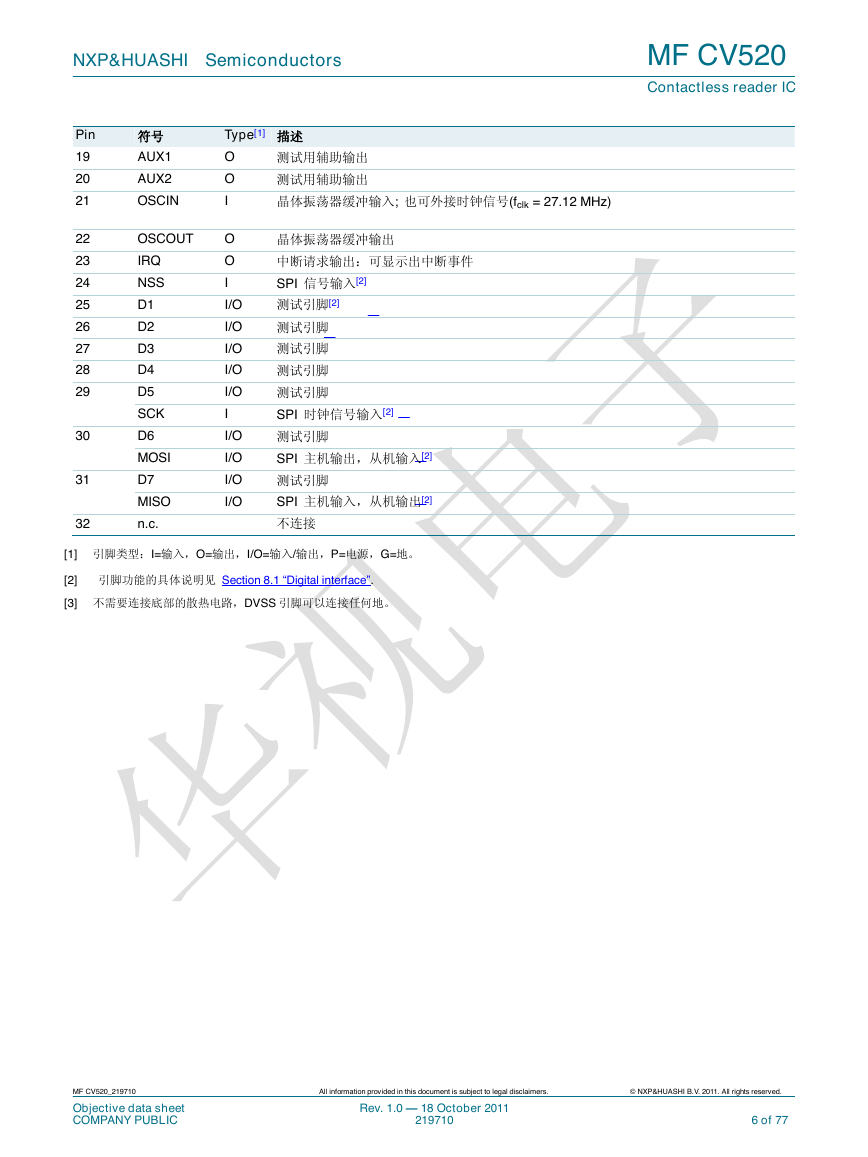

7. 引脚信息

I

O

S

M

7

D

/

1

3

.

c

.

n

2

3

n.c.

PVDD

DVDD

DVSS

PVSS

NRSTPD

MFIN

MFOUT

1

2

3

4

5

6

7

8

I

S

O

M

6

D

/

0

3

K

C

S

5

D

/

9

2

4

D

8

2

3

D

7

2

2

D

6

2

1

D

5

2

MF CV520

MF CV520

Contactless reader IC

24

NSS

23

22

21

20

19

18

17

IRQ

OSCOUT

OSCIN

AUX2

AUX1

AVSS

RX

001aaj819_1

9

D

D

V

S

0

1

S

S

V

T

1

1

1

X

T

2

1

3

1

4

1

5

1

6

1

2

X

T

D

D

V

T

S

S

V

T

D

D

V

A

I

D

M

V

Transparent top view

Fig 3. HVQFN32 (SOT617-1)引脚配置

Type[1] 描述

不连接

P

P

G

G

I

I

O

P

G

O

P

O

G

P

P

I

G

引脚电源电压

数字部分电源电压

数字地[3]

引脚电源地

复位与掉电输入:

掉电:低电平触发;内部灌电流关闭,晶体振荡器停振,输入引脚从外部总线上断开。

复位:上升沿触发。

MIFARE 信号输入

MIFARE 信号输出

MFIN 和 MFOUT 引脚电源

发送器电源地

天线驱动器

发送器电源电压

天线驱动器

发送器电源地

模拟部分电源电压

内部参考电压

RF 信号输入

模拟部分电源地

7.1 引脚描述

Table 3. 引脚描述

Pin

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

符号

n.c.

PVDD

DVDD

DVSS

PVSS

NRSTPD

MFIN

MFOUT

SVDD

TVSS

TX1

TVDD

TX2

TVSS

AVDD

VMID

RX

AVSS

MF CV520_219710

Objective data sheet

COMPANY PUBLIC

All information provided in this document is subject to legal disclaimers.

© NXP&HUASHI B.V. 2011. All rights reserved.

Rev. 1.0 — 18 October 2011

219710

5 of 77

�

NXP&HUASHI Semiconductors

MF CV520

Contactless reader IC

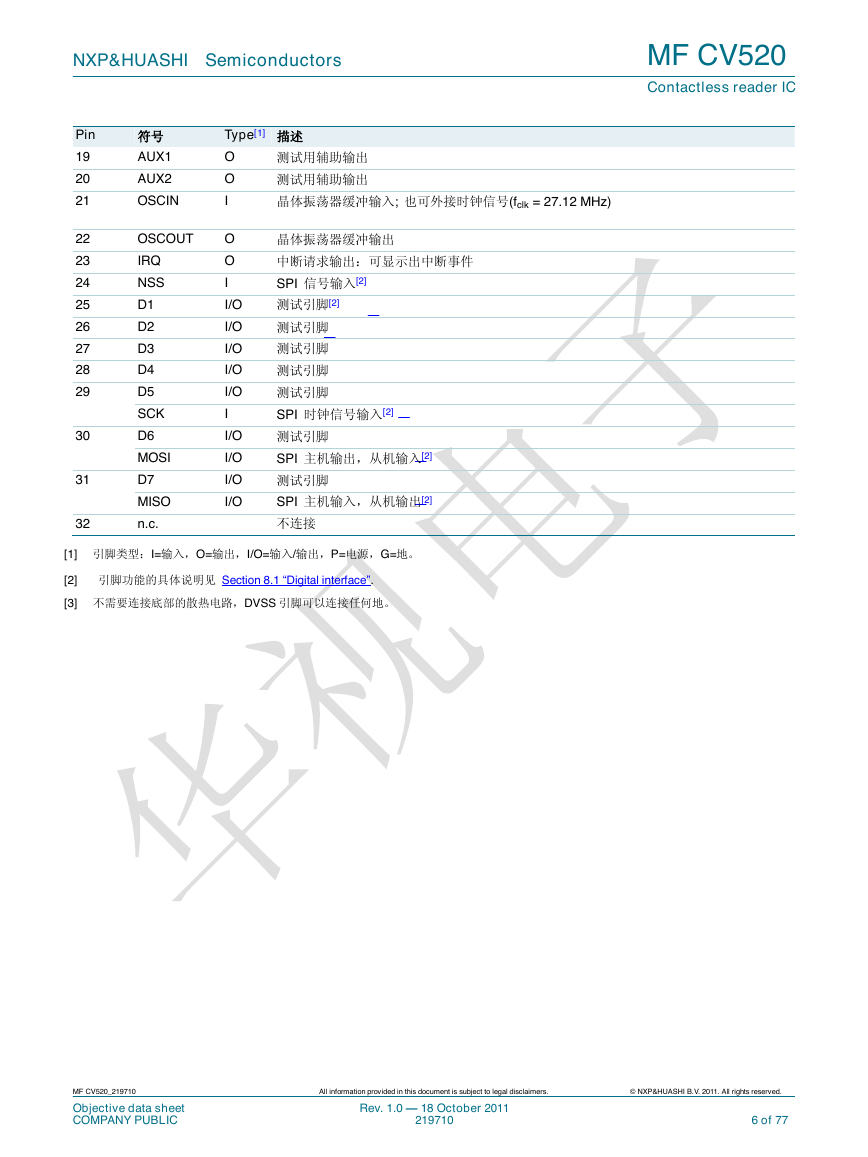

Pin

19

20

21

22

23

24

25

26

27

28

29

30

31

32

符号

AUX1

AUX2

OSCIN

OSCOUT

IRQ

NSS

D1

D2

D3

D4

D5

SCK

D6

MOSI

D7

MISO

n.c.

Type[1] 描述

O

O

I

O

O

I

I/O

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

测试用辅助输出

测试用辅助输出

晶体振荡器缓冲输入; 也可外接时钟信号(fclk = 27.12 MHz)

晶体振荡器缓冲输出

中断请求输出:可显示出中断事件

SPI 信号输入[2]

测试引脚[2]

测试引脚

测试引脚

测试引脚

测试引脚

SPI 时钟信号输入[2]

测试引脚

SPI 主机输出,从机输入[2]

测试引脚

SPI 主机输入,从机输出[2]

不连接

[1] 引脚类型:I=输入,O=输出,I/O=输入/输出,P=电源,G=地。

[2] 引脚功能的具体说明见 Section 8.1 “Digital interface”.

[3] 不需要连接底部的散热电路,DVSS 引脚可以连接任何地。

MF CV520_219710

Objective data sheet

COMPANY PUBLIC

All information provided in this document is subject to legal disclaimers.

© NXP&HUASHI B.V. 2011. All rights reserved.

Rev. 1.0 — 18 October 2011

219710

6 of 77

�

NXP&HUASHI Semiconductors

8. 功能描述

MF CV520

Contactless reader IC

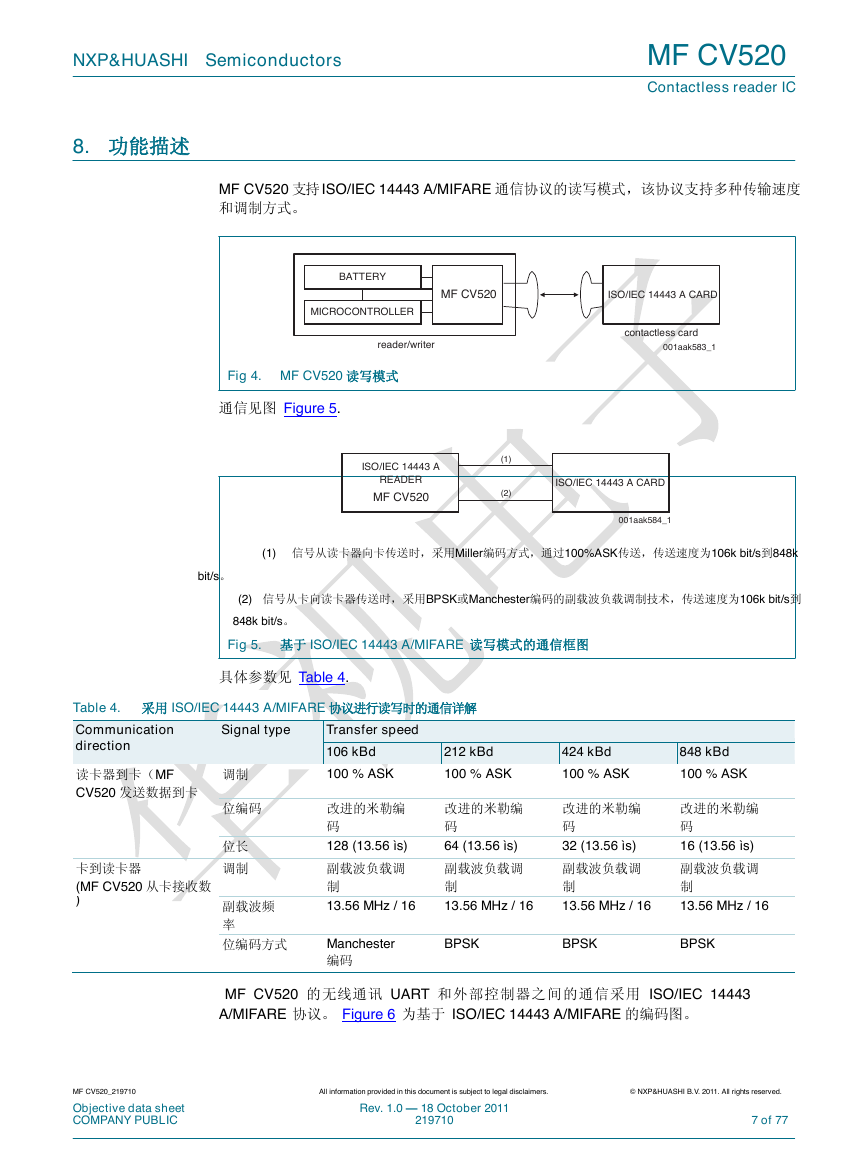

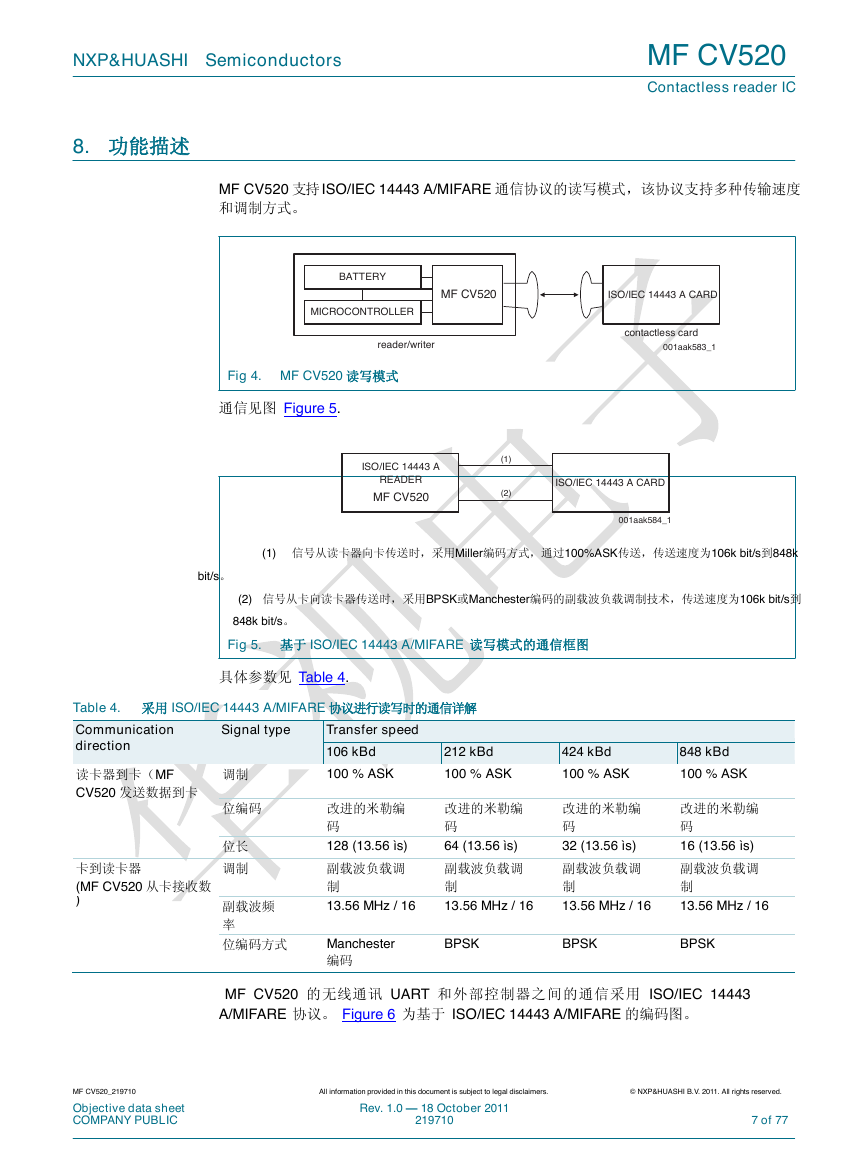

MF CV520 支持 ISO/IEC 14443 A/MIFARE 通信协议的读写模式,该协议支持多种传输速度

和调制方式。

BATTERY

MICROCONTROLLER

reader/writer

MF CV520

ISO/IEC 14443 A CARD

contactless card

001aak583_1

Fig 4. MF CV520 读写模式

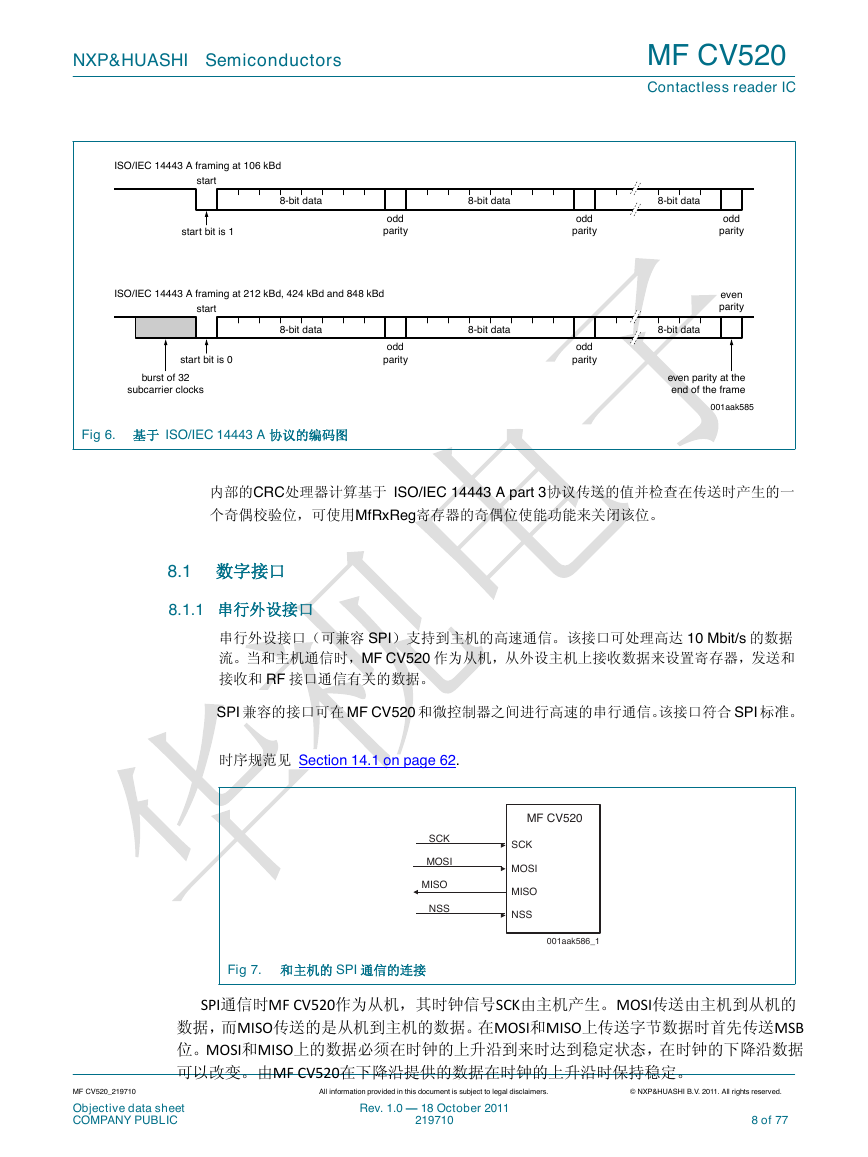

通信见图 Figure 5.

ISO/IEC 14443 A

READER

MF CV520

(1)

(2)

ISO/IEC 14443 A CARD

001aak584_1

(1) 信号从读卡器向卡传送时,采用Miller编码方式,通过100%ASK传送,传送速度为106k bit/s到848k

bit/s。

(2) 信号从卡向读卡器传送时,采用BPSK或Manchester编码的副载波负载调制技术,传送速度为106k bit/s到

848k bit/s。

Fig 5. 基于 ISO/IEC 14443 A/MIFARE 读写模式的通信框图

具体参数见 Ta ble 4.

Table 4. 采用 ISO/IEC 14443 A/MIFARE 协议进行读写时的通信详解

Communication

direction

Signal type

Transfer speed

读卡器到卡(MF

CV520 发送数据到卡

卡)卡卡)

调制

位编码

卡到读卡器

(MF CV520 从卡接收数

)

据

位长

调制

副载波频

率

位编码方式

106 kBd

212 kBd

424 kBd

848 kBd

100 % ASK

100 % ASK

100 % ASK

100 % ASK

改进的米勒编

码

128 (13.56 ìs)

副载波负载调

制

13.56 MHz / 16

Manchester

编码

改进的米勒编

码

64 (13.56 ìs)

改进的米勒编

码

32 (13.56 ìs)

改进的米勒编

码

16 (13.56 ìs)

副载波负载调

制

13.56 MHz / 16

副载波负载调

制

13.56 MHz / 16

副载波负载调

制

13.56 MHz / 16

BPSK

BPSK

BPSK

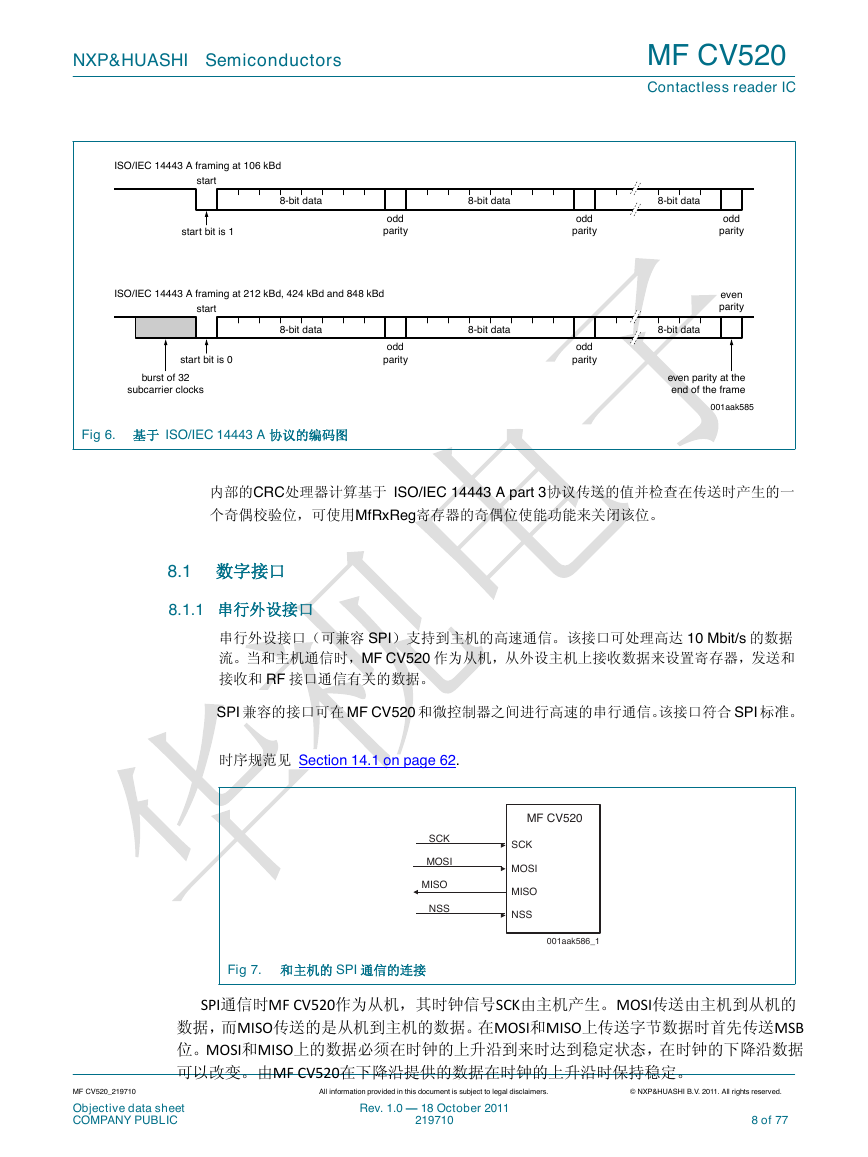

MF CV520 的无线通讯 UART 和外部控制器之间的通信采用 ISO/IEC 14443

A/MIFARE 协议。 Figure 6 为基于 ISO/IEC 14443 A/MIFARE 的编码图。

MF CV520_219710

All information provided in this document is subject to legal disclaimers.

© NXP&HUASHI B.V. 2011. All rights reserved.

Objective data sheet

COMPANY PUBLIC

Rev. 1.0 — 18 October 2011

219710

7 of 77

�

NXP&HUASHI Semiconductors

MF CV520

Contactless reader IC

ISO/IEC 14443 A framing at 106 kBd

start

8-bit data

8-bit data

8-bit data

start bit is 1

odd

parity

odd

parity

ISO/IEC 14443 A framing at 212 kBd, 424 kBd and 848 kBd

start

odd

parity

even

parity

start bit is 0

burst of 32

subcarrier clocks

8-bit data

8-bit data

8-bit data

odd

parity

odd

parity

even parity at the

end of the frame

001aak585

Fig 6. 基于 ISO/IEC 14443 A 协议的编码图

内部的CRC处理器计算基于 ISO/IEC 14443 A part 3协议传送的值并检查在传送时产生的一

个奇偶校验位,可使用MfRxReg寄存器的奇偶位使能功能来关闭该位。

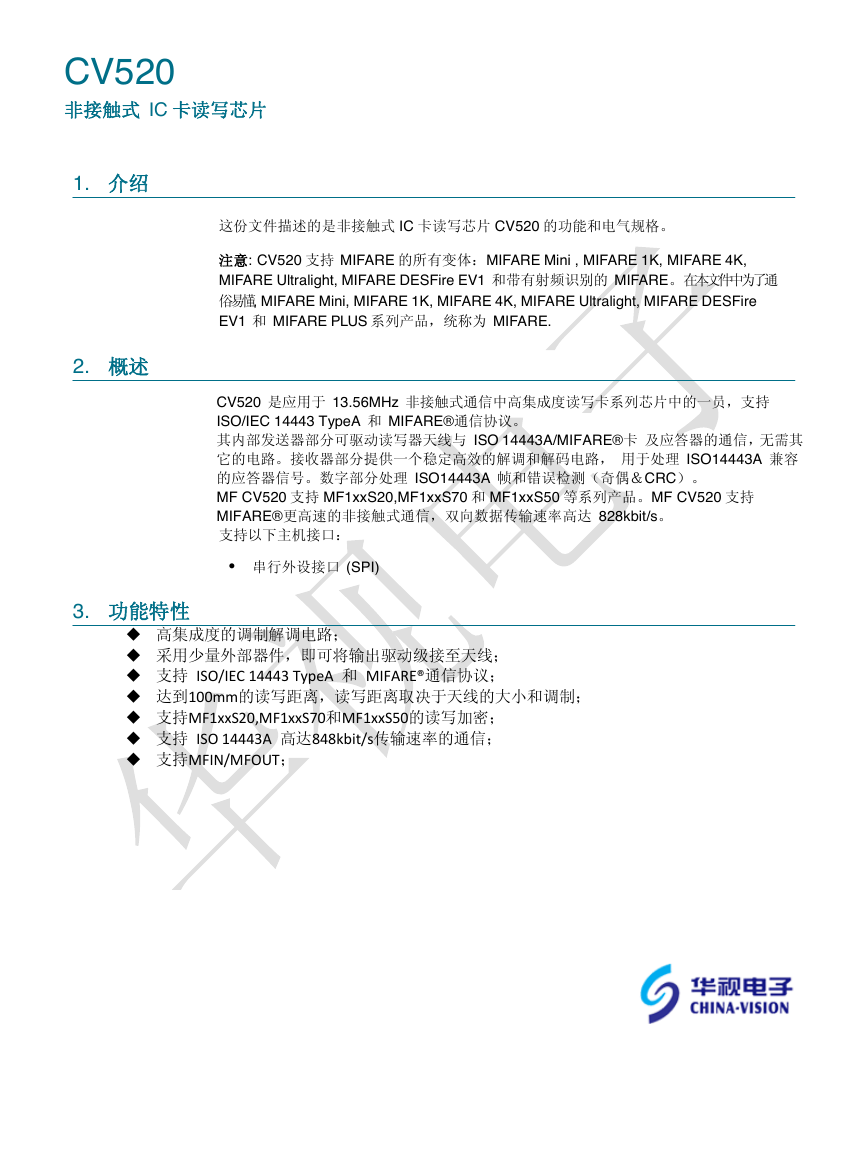

8.1 数字接口

8.1.1 串行外设接口

串行外设接口(可兼容 SPI)支持到主机的高速通信。该接口可处理高达 10 Mbit/s 的数据

流。当和主机通信时,MF CV520 作为从机,从外设主机上接收数据来设置寄存器,发送和

接收和 RF 接口通信有关的数据。

SPI 兼容的接口可在 MF CV520 和微控制器之间进行高速的串行通信。该接口符合 SPI 标准。

时序规范见 Section 14.1 on page 62.

MF CV520

SCK

MOSI

MISO

NSS

SCK

MOSI

MISO

NSS

001aak586_1

Fig 7. 和主机的 SPI 通信的连接

SPI通信时MF CV520作为从机,其时钟信号SCK由主机产生。MOSI传送由主机到从机的

数据,而MISO传送的是从机到主机的数据。在MOSI和MISO上传送字节数据时首先传送MSB

位。MOSI和MISO上的数据必须在时钟的上升沿到来时达到稳定状态,在时钟的下降沿数据

可以改变。由MF CV520在下降沿提供的数据在时钟的上升沿时保持稳定。

MF CV520_219710

All information provided in this document is subject to legal disclaimers.

© NXP&HUASHI B.V. 2011. All rights reserved.

Objective data sheet

COMPANY PUBLIC

Rev. 1.0 — 18 October 2011

219710

8 of 77

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc