南京工程学院

工程基础实验与训练中心

本科课程设计说明书(论文)

题 目: 实现 0~999 任意进制计数器及数码管显示

自动化系统集成

学 号

专 业:

班 级:

学生姓名:

指导教师:

起迄日期:

2018/12/18-2019/1/1

设计地点:

工 程 中 心 C4 0 2

�

目录

1、设计任务及要求 ........................................ 2

1.1 设计任务 ............................................. 2

1.2 设计要求 ............................................. 2

2、设计内容 .............................................. 2

2.1 设计总体功能简介 ..................................... 2

2.2 计时模块功能 ......................................... 2

2.3 显示模块功能 ......................................... 2

2.4 逻辑模块功能 ......................................... 2

3、设计及实现方法 ........................................ 3

3.1 计时模块设计方法 ..................................... 4

3.2 显示模块设计方法 ..................................... 7

4、调试及运行结果 ........................................ 9

4.1 计时模块调试及运行结果 ............................... 9

4.2 显示模块调试及运行结果 .............................. 11

4.3 系统总体调试及运行结果 .............................. 13

5、设计总结 ............................................. 15

5.1 设计中的问题、原因分析及解决方法 .....................15

5.2 设计方案的优缺点 .................................... 15

5.3 心得体会 ............................................ 16

1

�

1、设计任务及要求

1.1 设计任务

利用 VHDL 语言,实现 0~999 任意进制 8421BCD 计数器,并将计数器输出的

8421BCD 进行共阳数码管显示。

1.2 设计要求

指标一:计数器具有同步置数功能、异步清零功能.

指标二:8421BCD 码 7 段译码部分可以参见 74LS48 功能

指标三:译码输出后驱动的数码管为共阳极数码管

2、设计内容

2.1 设计总体功能简介

设计具有同步置数、异步清零功能的计数器.用 8421BCD 码驱动 7 段译码器,

译码输出后驱动共阳极数码管进行计数。

2.2 计时模块功能

1、同步计数

2、异步清零

3、可实现任意进制计数

2.3 显示模块功能

1、三个共阳七段数码管显示

2.4 逻辑模块功能

1、判断计数器当前值是否为 0,若不为 0,进行清零为计数做准备。

2、在计数的过程中,判断是否有溢出,如若溢出要进行进位处理。

3、进位时发出提示。

2

�

3、设计及实现方法

CLK 为时钟脉冲信号,CO1,CO2,CO3 分别对应计数器 1,2,3 的进位信号,EN

为使能端(置 1 有效),CLR 为清零端(置 0 清零)Y1,Y2,Y3 分别对应计数器

1,2,3 的输出结果,A,B,C 为个位,十位,百位的数码管。

总体思路:首先提供一个时钟脉冲信号 CLK 给个位计数器 1,EN 给高电平,

CLR 给高电平,CO1 再接入十位计数器 2 的 CLK 端,CO2 再接入百位计数器 3 的

CLK 端,起到级联作用。再将个、十、百位计数器的输出端与 CLR 相与,作用是

异步清零,实现任意进制的效果。流程图如图 1。

图 1

3

�

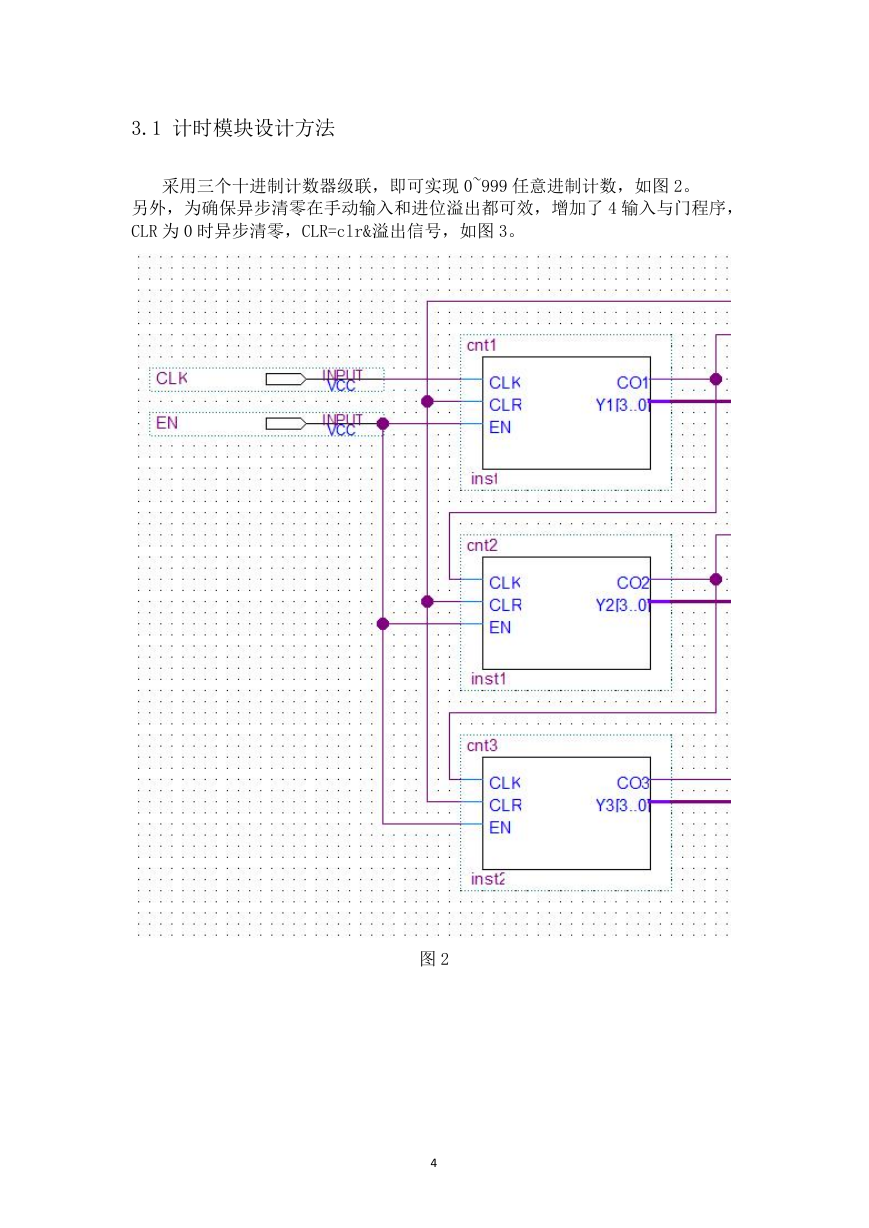

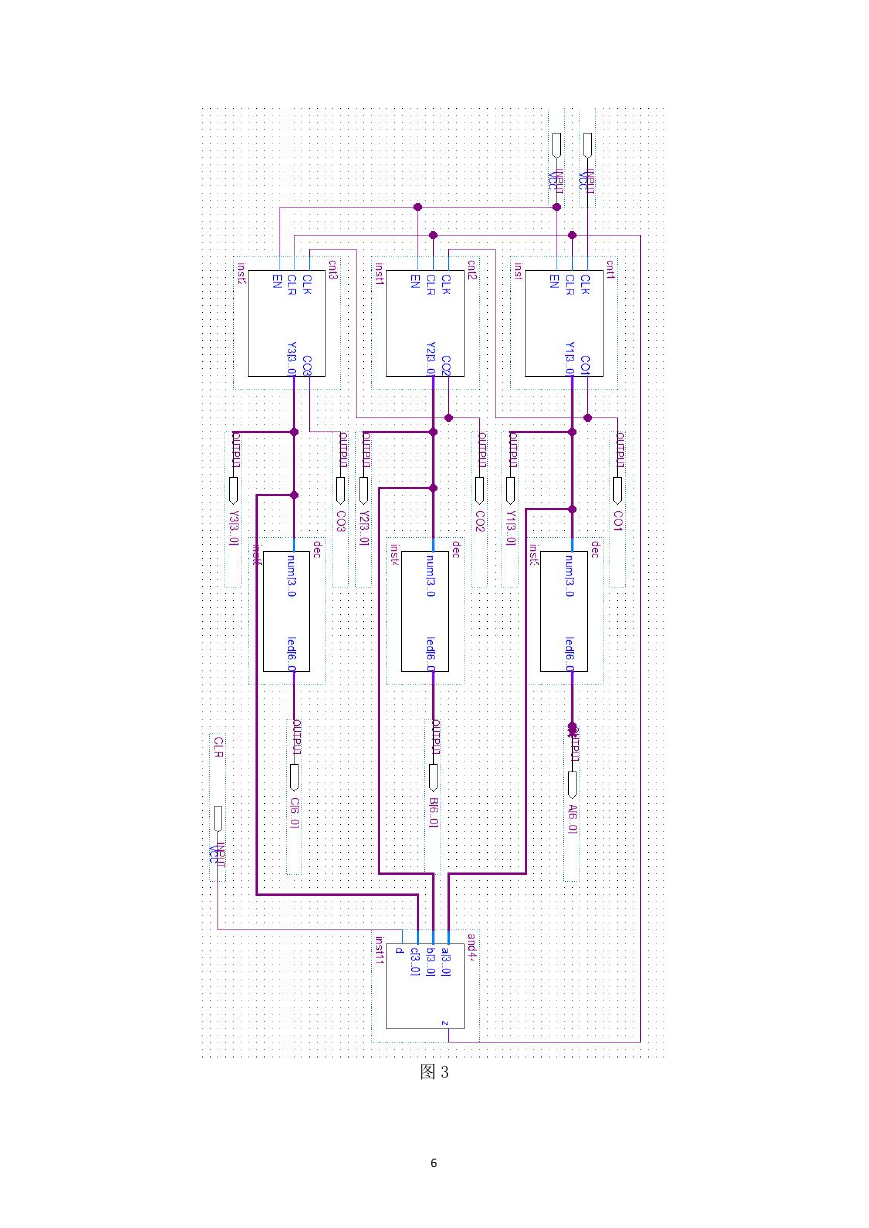

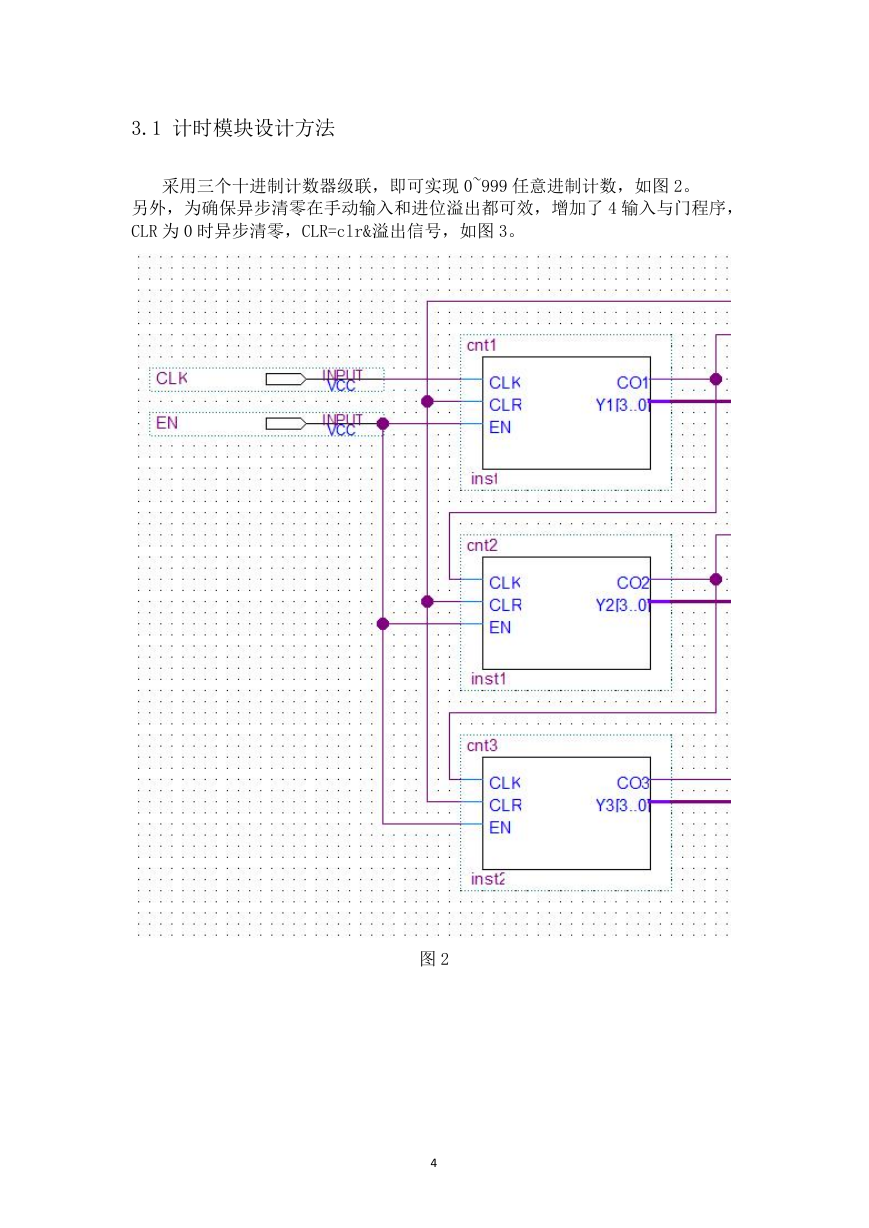

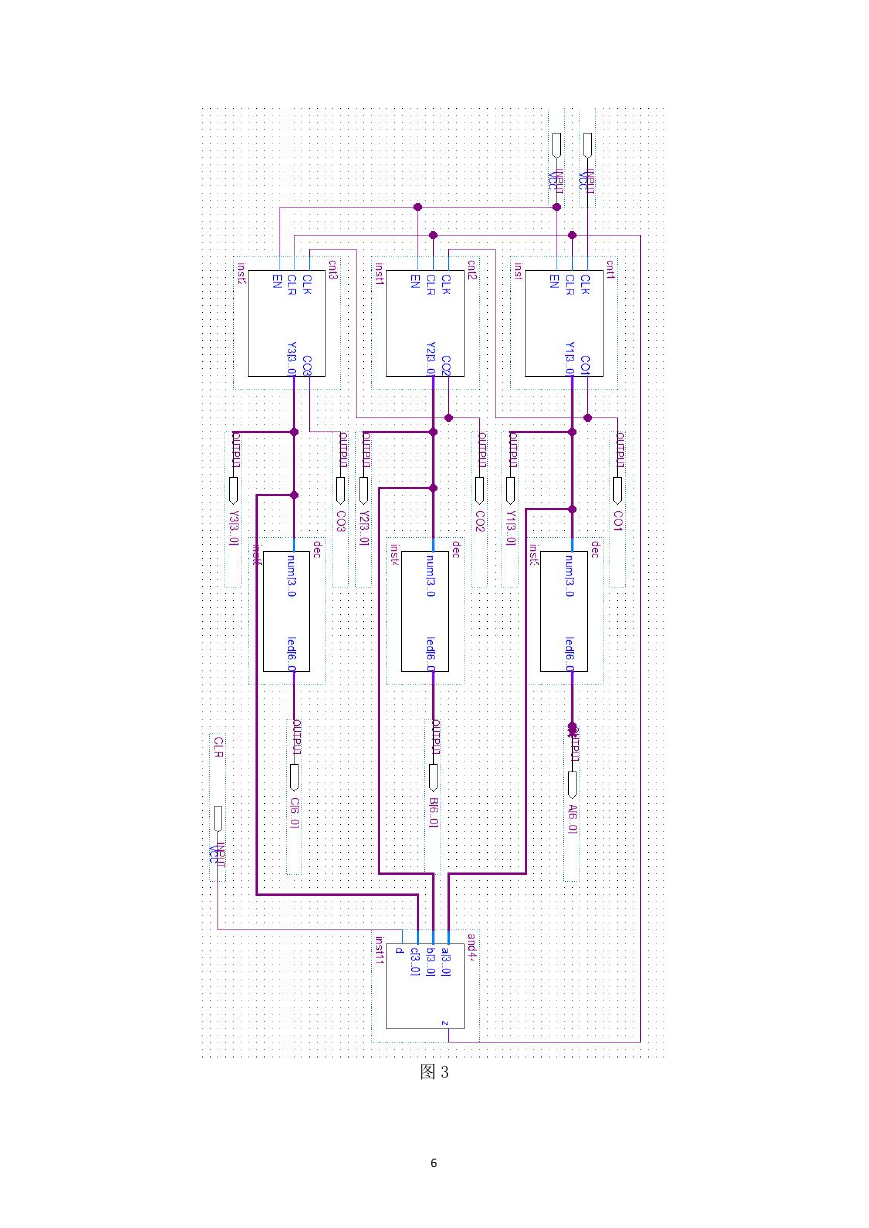

3.1 计时模块设计方法

采用三个十进制计数器级联,即可实现 0~999 任意进制计数,如图 2。

另外,为确保异步清零在手动输入和进位溢出都可效,增加了 4 输入与门程序,

CLR 为 0 时异步清零,CLR=clr&溢出信号,如图 3。

图 2

4

�

--十进制计数器代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY cnt1 IS

PORT(

CLK,CLR,EN:IN BIT;

CO1: OUT BIT;

Y1:

OUT INTEGER RANGE 0 TO 999);

END cnt1;

architecture RT of cnt1 is

signal Q:INTEGER RANGE 0 TO 999;

BEGIN

PROCESS(CLK)

BEGIN

IF(CLR='0')

THEN

Q<=0;

ELSIF(CLK'EVENT AND CLK='1')THEN

IF(EN='1') THEN

IF Q=9 THEN

--单个数码管最高

所能达的数值

CO1<='1';

Q<=0;

ELSE

Q<=Q+1;

CO1<='0';

END IF;

END IF;

END IF;

Y1<=Q ;

END PROCESS;

END RT;

5

�

图 3

6

�

--四输入与门程序

library ieee;

use ieee.std_logic_1164.all;

entity and44 is

port (a,b,c:in std_logic_vector(3 downto 0);

--a:个位,b:十位,c:百位

d:in bit;

--d:输入的 clr

z:out bit);

--最终输入的 clr,1 为计数,0 为清零

end and44;

architecture one of and44 is

begin

process(a,b,c)

begin

IF a="0000" and

b="0000" and c="0010" then

输入您所需的进制(a:个位,b:十位,c:百位)

z<='0';

--当达到该进制时,异步清零

ELSE z<=d;

否则为 1,异步清零即输入的 clr

end If;

end process;

end one;

--

--

3.2 显示模块设计方法待添加

将之前三个计数器的输出结果接入各对应的数码管输入端,如图 4。

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc